| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AD210 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

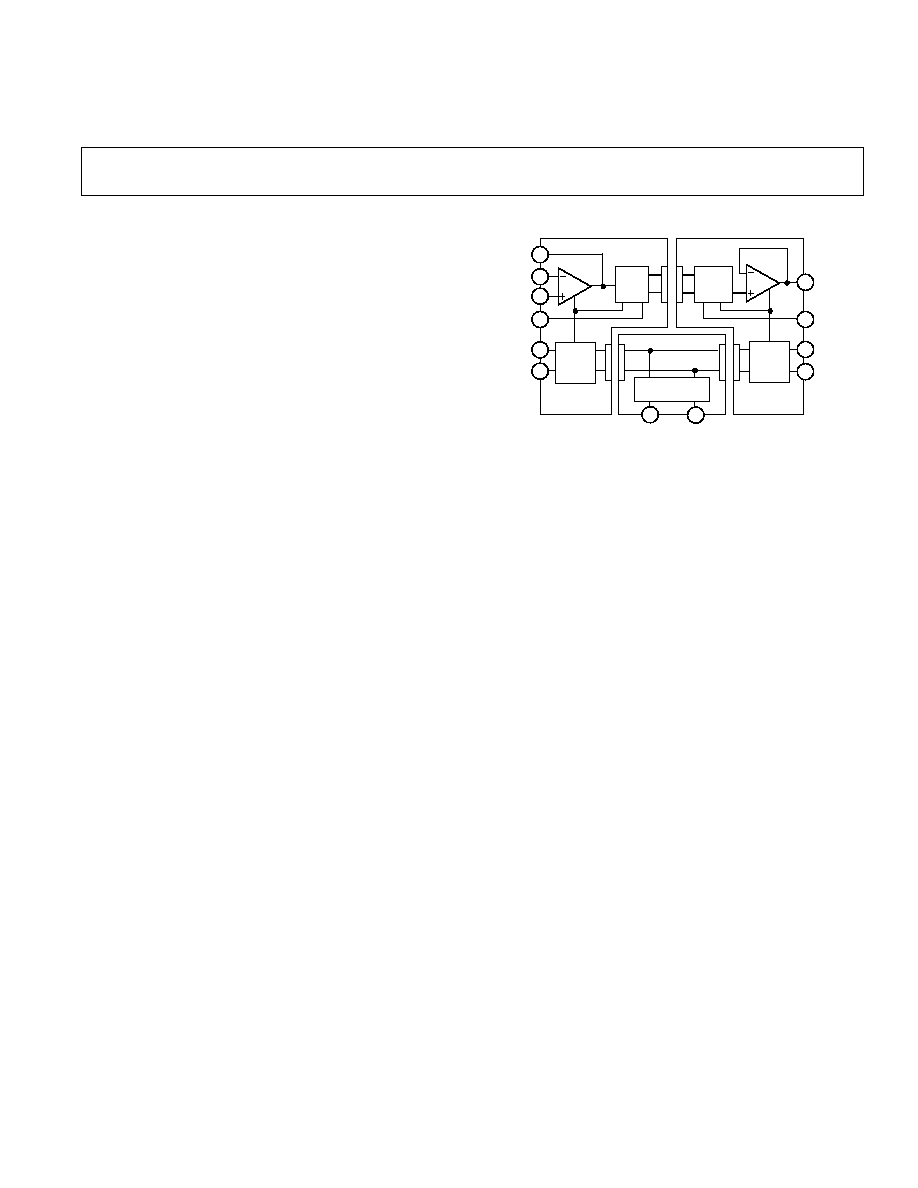

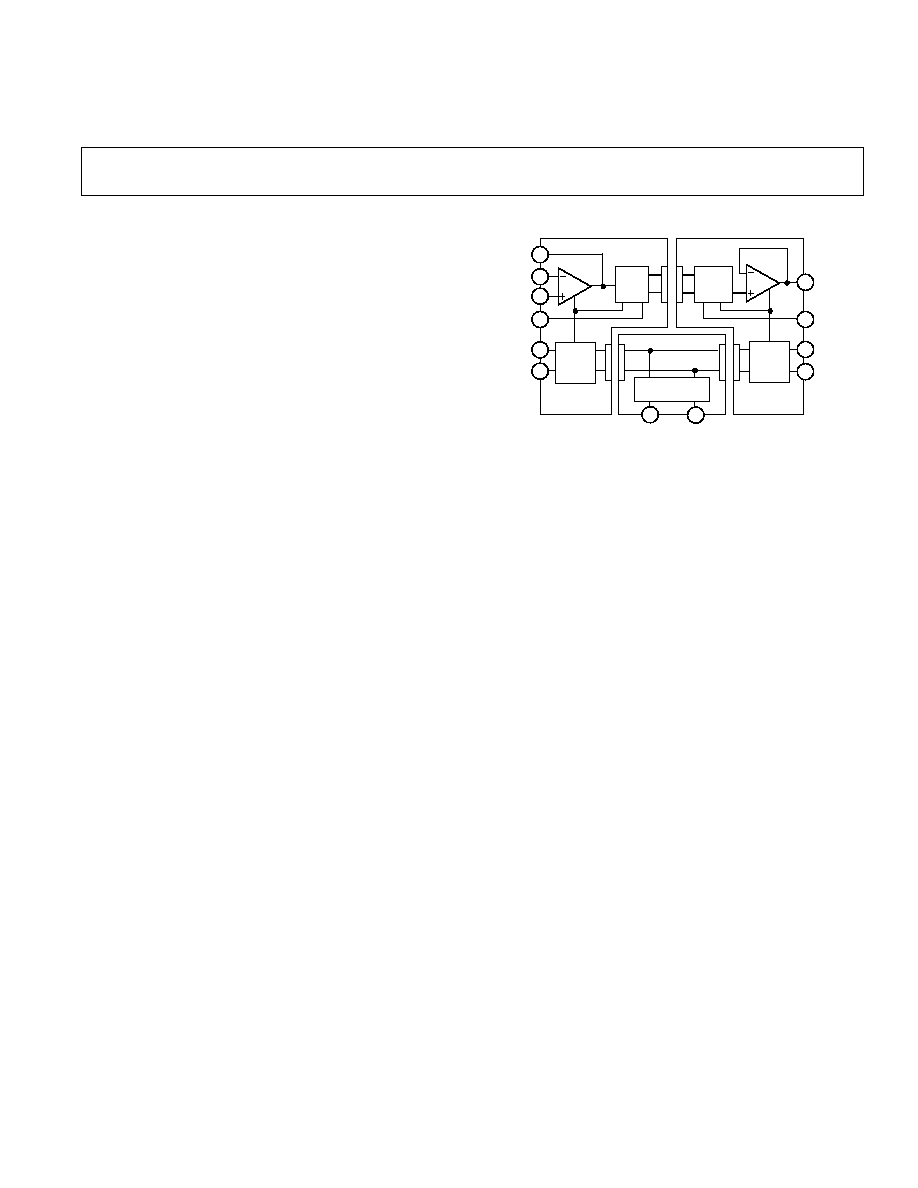

FUNCTIONAL BLOCK DIAGRAM

INPUT

POWER

SUPPLY

19

14

15

16

17

18

V

O

30

29

T2

POWER

POWER

OSCILLATOR

INPUT

OUTPUT

MOD

DEMOD

FILTER

1

2

OUTPUT

POWER

SUPPLY

3

4

O

COM

+V

OSS

≠V

OSS

AD210

PWR COM

PWR

T3

T1

≠V

ISS

+V

ISS

I

COM

+IN

≠IN

FB

a

Precision, Wide Bandwidth

3-Port Isolation Amplifier

AD210*

FEATURES

High CMV Isolation: 2500 V rms Continuous

3500 V Peak Continuous

Small Size: 1.00" 2.10" 0.350"

Three-Port Isolation: Input, Output, and Power

Low Nonlinearity: 0.012% max

Wide Bandwidth: 20 kHz Full-Power (≠3 dB)

Low Gain Drift: 25 ppm/ C max

High CMR: 120 dB (G = 100 V/V)

Isolated Power: 15 V @ 5 mA

Uncommitted Input Amplifier

APPLICATIONS

Multichannel Data Acquisition

High Voltage Instrumentation Amplifier

Current Shunt Measurements

Process Signal Isolation

GENERAL DESCRIPTION

The AD210 is the latest member of a new generation of low

cost, high performance isolation amplifiers. This three-port,

wide bandwidth isolation amplifier is manufactured with sur-

face-mounted components in an automated assembly process.

The AD210 combines design expertise with state-of-the-art

manufacturing technology to produce an extremely compact

and economical isolator whose performance and abundant user

features far exceed those offered in more expensive devices.

The AD210 provides a complete isolation function with both

signal and power isolation supplied via transformer coupling in-

ternal to the module. The AD210's functionally complete de-

sign, powered by a single +15 V supply, eliminates the need for

an external DC/DC converter, unlike optically coupled isolation

devices. The true three-port design structure permits the

AD210 to be applied as an input or output isolator, in single or

multichannel applications. The AD210 will maintain its high

performance under sustained common-mode stress.

Providing high accuracy and complete galvanic isolation, the

AD210 interrupts ground loops and leakage paths, and rejects

common-mode voltage and noise that may other vise degrade

measurement accuracy. In addition, the AD210 provides pro-

tection from fault conditions that may cause damage to other

sections of a measurement system.

PRODUCT HIGHLIGHTS

The AD210 is a full-featured isolator providing numerous user

benefits including:

High Common-Mode Performance:

The AD210 provides

2500 V rms (Continuous) and

±

3500 V peak (Continuous) common-

mode voltage isolation between any two ports. Low input

capacitance of 5 pF results in a 120 dB CMR at a gain of 100,

and a low leakage current (2

µ

A rms max @ 240 V rms, 60 Hz).

High Accuracy:

With maximum nonlinearity of

±

0.012% (B

Grade), gain drift of

±

25 ppm/

∞

C max and input offset drift of

(

±

10

±

30/G)

µ

V/

∞

C, the AD210 assures signal integrity while

providing high level isolation.

Wide Bandwidth:

The AD210's full-power bandwidth of

20 kHz makes it useful for wideband signals. It is also effective

in applications like control loops, where limited bandwidth

could result in instability.

Small Size:

The AD210 provides a complete isolation function

in a small DIP package just 1.00"

◊

2.10"

◊

0.350". The low

profile DIP package allows application in 0.5" card racks and

assemblies. The pinout is optimized to facilitate board layout

while maintaining isolation spacing between ports.

Three-Port Design:

The AD210's three-port design structure

allows each port (Input, Output, and Power) to remain inde-

pendent. This three-port design permits the AD210 to be used

as an input or output isolator. It also provides additional system

protection should a fault occur in the power source.

Isolated Power:

±

15 V @ 5 mA is available at the input and

output sections of the isolator. This feature permits the AD210

to excite floating signal conditioners, front-end amplifiers and

remote transducers at the input as well as other circuitry at the

output.

Flexible Input:

An uncommitted operational amplifier is pro-

vided at the input. This amplifier provides buffering and gain as

required and facilitates many alternative input functions as

required by the user.

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

REV. A

*Covered by U.S. Patent No. 4,703,283.

AD210 PIN DESIGNATIONS

Pin

Designation

Function

1

V

O

Output

2

O

COM

Output Common

3

+V

OSS

+Isolated Power @ Output

4

≠V

OSS

≠Isolated Power @ Output

14

+V

ISS

+Isolated Power @ Input

15

≠V

ISS

≠Isolated Power @ Input

16

FB

Input Feedback

17

≠IN

≠Input

18

I

COM

Input Common

19

+IN

+Input

29

Pwr Com

Power Common

30

Pwr

Power Input

AD210≠SPECIFICATIONS

(typical @ +25 C, and V

S

= +15 V unless otherwise noted)

Model

AD210AN

AD210BN

AD210JN

GAIN

Range

1 V/V ≠ 100 V/V

*

*

Error

±

2% max

±

1% max

*

vs. Temperature(0

∞

C to +70

∞

C)

+25 ppm/

∞

C max

*

*

(≠25

∞

C to +85

∞

C)

±

50 ppm/

∞

C max

*

*

vs. Supply Voltage

±

0.002%/V

*

*

Nonlinearity

1

±

0.025% max

±

0.012% max

*

INPUT VOLTAGE RATINGS

Linear Differential Range

±

10 V

*

*

Maximum Safe Differential Input

±

15 V

*

*

Max. CMV Input-to-Output

*

ac, 60 Hz, Continuous

2500 V rms

*

1500 V rms

dc, Continuous

±

3500 V peak

*

±

2000 V peak

Common-Mode Rejection

*

60 Hz, G = 100 V/V

*

R

S

500

Impedance Imbalance

120 dB

*

*

Leakage Current Input-to-Output

*

@ 240 V rms, 60 Hz

2

µ

A rms max

*

*

INPUT IMPEDANCE

Differential

l0

12

*

*

Common Mode

5 G

5 pF

*

*

INPUT BIAS CURRENT

Initial, @ +25

∞

C

30 pA typ (400 pA max)

*

*

vs. Temperature (0

∞

C to +70

∞

C)

10 nA max

*

*

(≠25

∞

C to +85

∞

C)

30 nA max

*

*

INPUT DIFFERENCE CURRENT

Initial, @ +25

∞

C

5 pA typ (200 pA max)

*

*

vs. Temperature(0

∞

C to + 70

∞

C)

2 nA max

*

*

(≠25

∞

C to +85

∞

C)

10 nA max

*

*

INPUT NOISE

Voltage (l kHz)

18 nV/

Hz

*

*

(10 Hz to 10 kHz)

4

µ

V rms

*

*

Current (1 kHz)

0.01 pA/

Hz

*

*

FREQUENCY RESPONSE

Bandwidth (≠3 dB)

*

G = 1 V/V

20 kHz

*

*

G = 100 V/V

15 kHz

*

*

Settling Time (

±

10 mV, 20 V Step)

*

G = 1 V/V

150

µ

s

*

*

G = 100 V/V

500

µ

s

*

*

Slew Rate (G = 1 V/V)

1 V/

µ

s

*

*

OFFSET VOLTAGE (RTI)

2

Initial, @ +25

∞

C

±

15

±

45/G) mV max

(

±

5

±

15/G) mV max

*

vs. Temperature (0

∞

C to +70

∞

C)

(

±

10

±

30/G)

µ

V/

∞

C

*

*

(≠25

∞

C to +85

∞

C)

(

±

10

±

50/G)

µ

V/

∞

C

*

*

RATED OUTPUT

3

Voltage, 2 k

Load

±

10 V min

*

*

Impedance

1

max

*

*

Ripple (Bandwidth = 100 kHz)

10 mV p-p max

*

*

ISOLATED POWER OUTPUTS

4

Voltage, No Load

±

15 V

*

*

Accuracy

±

10%

*

*

Current

±

5 mA

*

*

Regulation, No Load to Full Load

See Text

*

*

Ripple

See Text

*

*

POWER SUPPLY

Voltage, Rated Performance

+15 V dc

±

5%

*

*

Voltage, Operating

+15 V dc

±

10%

*

*

Current, Quiescent

50 mA

*

*

Current, Full Load ≠ Full Signal

80 mA

*

*

TEMPERATURE RANGE

Rated Performance

≠25

∞

C to +85

∞

C

*

*

Operating

≠40

∞

C to +85

∞

C

*

*

Storage

≠40

∞

C to +85

∞

C

*

*

PACKAGE DIMENSIONS

Inches

1.00

◊

2.10

◊

0.350

*

*

Millimeters

25.4

◊

53.3

◊

8.9

*

*

NOTES

*Specifications same as AD210AN.

1

Nonlinearity is specified as a % deviation from a best straight line..

2

RTI ≠ Referred to Input.

3

A reduced signal swing is recommended when both

±

V

ISS

and

±

V

OSS

supplies are fully

loaded, due to supply voltage reduction.

4

See text for detailed information.

_

Specifications subject to change without notice.

REV. A

≠2≠

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

AC1059 MATING SOCKET

CAUTION

ESD (electrostatic discharge) sensitive device. Elec-

trostatic charges as high as 4000 V readily accumu-

late on the human body and test equipment and can

discharge without detection. Although the AD210

features proprietary ESD protection circuitry, per-

manent damage may occur on devices subjected to

high energy electrostatic discharges. Therefore,

proper ESD precautions are recommended to avoid

performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

AD210

REV. A

≠3≠

INSIDE THE AD210

The AD210 basic block diagram is illustrated in Figure 1.

A +15 V supply is connected to the power port, and

±

15 V isolated power is supplied to both the input and

output ports via a 50 kHz carrier frequency. The uncom-

mitted input amplifier can be used to supply gain or buff-

ering of input signals to the AD210. The fullwave

modulator translates the signal to the carrier frequency for

application to transformer T1. The synchronous demodu-

lator in the output port reconstructs the input signal. A

20 kHz, three-pole filter is employed to minimize output

noise and ripple. Finally, an output buffer provides a low

impedance output capable of driving a 2 k

load.

INPUT

POWER

SUPPLY

19

14

15

16

17

18

V

O

30

29

T2

POWER

POWER

OSCILLATOR

INPUT

OUTPUT

MOD

DEMOD

FILTER

1

2

OUTPUT

POWER

SUPPLY

3

4

O

COM

+V

OSS

≠V

OSS

AD210

PWR COM

PWR

T3

T1

≠V

ISS

+V

ISS

I

COM

+IN

≠IN

FB

Figure 1. AD210 Block Diagram

USING THE AD210

The AD210 is very simple to apply in a wide range of ap-

plications. Powered by a single +15 V power supply, the

AD210 will provide outstanding performance when used

as an input or output isolator, in single and multichannel

configurations.

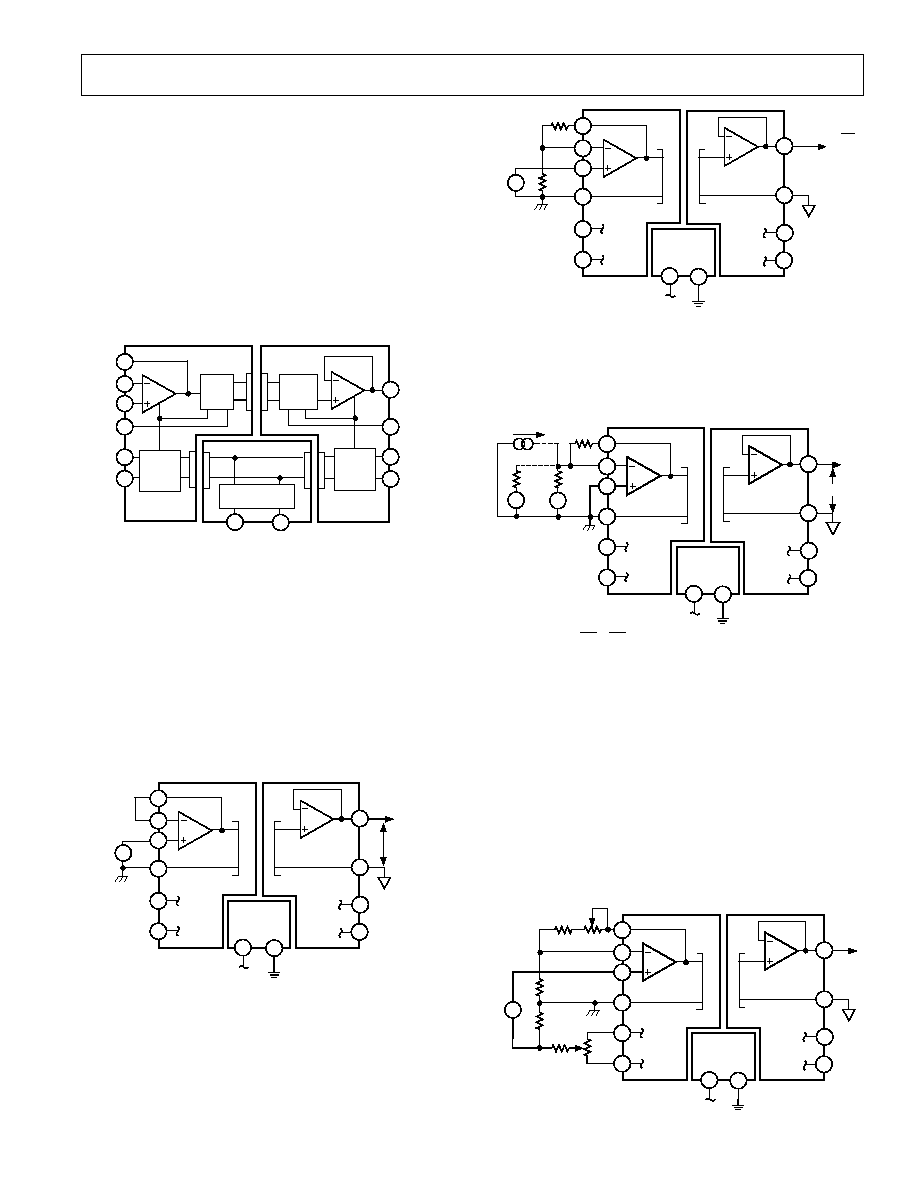

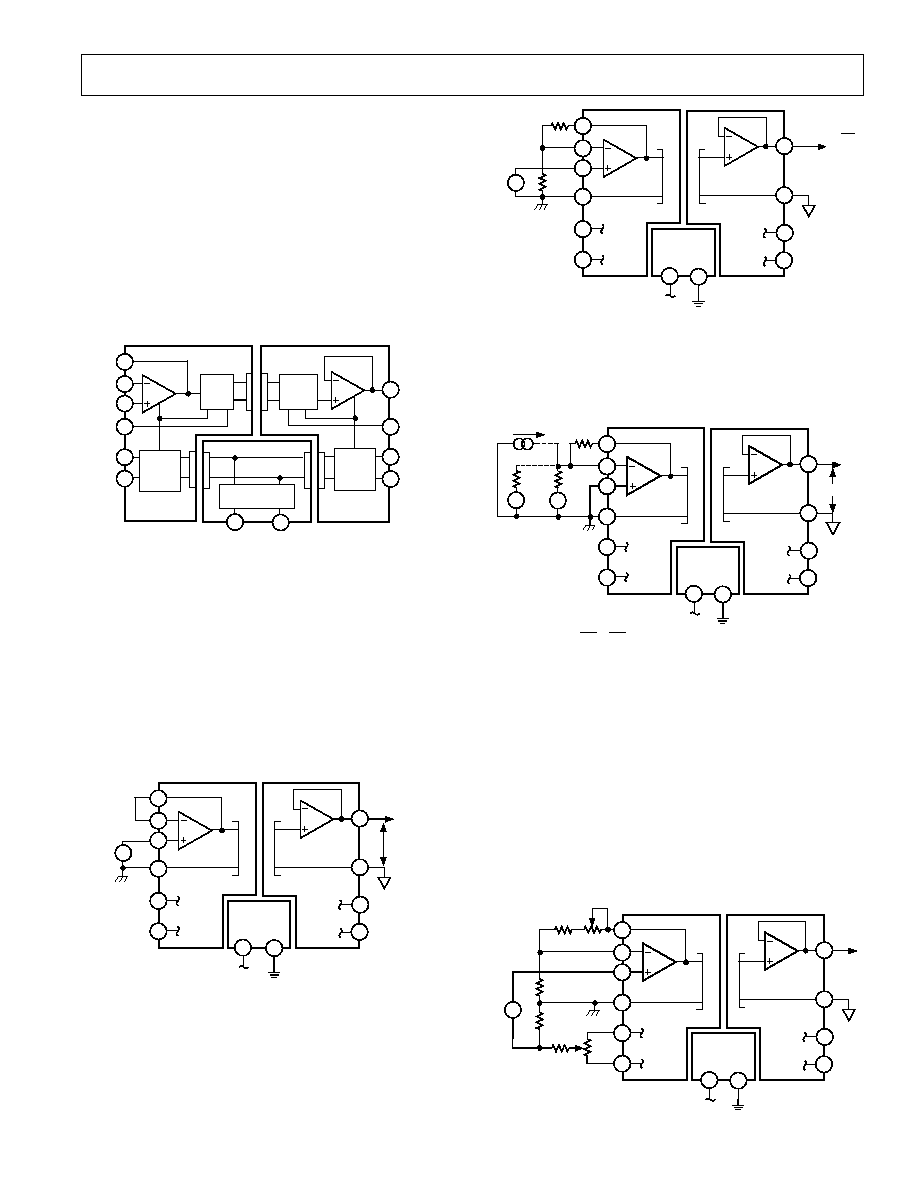

Input Configurations:

The basic unity gain configura-

tion for signals up to

±

10 V is shown in Figure 2. Addi-

tional input amplifier variations are shown in the following

figures. For smaller signal levels Figure 3 shows how to

obtain gain while maintaining a very high input impedance.

19

14

15

16

17

18

V

OUT

(

±

10V)

30

29

+V

OSS

V

SIG

±

10V

AD210

+V

ISS

≠V

ISS

+15V

2

3

4

≠V

OSS

1

V

OUT

Figure 2. Basic Unity Gain Configuration

The high input impedance of the circuits in Figures 2 and

3 can be maintained in an inverting application. Since the

AD210 is a three-port isolator, either the input leads or

the output leads may be interchanged to create the signal

inversion.

19

14

15

16

17

18

30

29

+V

OSS

V

SIG

AD210

+V

ISS

≠V

ISS

+15V

2

3

4

≠V

OSS

1

V

OUT

= V

SIG

1+

( )

R

F

R

G

R

G

R

F

Figure 3. Input Configuration for G > 1

Figure 4 shows how to accommodate current inputs or sum cur-

rents or voltages. This circuit configuration can also be used for

signals greater than

±

10 V. For example, a

±

100 V input span

can be handled with R

F

= 20 k

and R

S1

= 200 k

.

19

14

15

16

17

18

30

29

+V

OSS

AD210

+V

ISS

≠V

ISS

+15V

2

3

4

≠V

OSS

1

R

S1

I

S

V

S2

V

S1

R

S2

R

F

V

OUT

V

OUT

= ≠R

F

V

S1

R

S1

( )

V

S2

R

S2

+

+ I

S

+ ...

Figure 4. Summing or Current Input Configuration

Adjustments

When gain and offset adjustments are required, the actual cir-

cuit adjustment components will depend on the choice of input

configuration and whether the adjustments are to be made at

the isolator's input or output. Adjustments on the output side

might be used when potentiometers on the input side would

represent a hazard due to the presence of high common-mode

voltage during adjustment. Offset adjustments are best done at

the input side, as it is better to null the offset ahead of the gain.

Figure 5 shows the input adjustment circuit for use when the in-

put amplifier is configured in the noninverting mode. This offset

adjustment circuit injects a small voltage in series with the

19

15

16

17

18

30

29

+V

OSS

AD210

+V

ISS

≠V

ISS

+15V

2

3

4

≠V

OSS

R

G

HI

V

OUT

V

SIG

14

200

47.5k

5k

100k

50k

LO

GAIN

OFFSET

1

Figure 5. Adjustments for Noninverting Input

AD210

REV. A

≠4≠

low side of the signal source. This will not work if the source has

another current path to input common or if current flows in the

signal source LO lead. To minimize CMR degradation, keep the

resistor in series with the input LO below a few hundred ohms.

Figure 5 also shows the preferred gain adjustment circuit. The

circuit shows R

F

of 50 k

, and will work for gains of ten or

greater. The adjustment becomes less effective at lower gains

(its effect is halved at G = 2) so that the pot will have to be a

larger fraction of the total R

F

at low gain. At G = 1 (follower)

the gain cannot be adjusted downward without compromising

input impedance; it is better to adjust gain at the signal source

or after the output.

Figure 6 shows the input adjustment circuit for use when the

input amplifier is configured in the inverting mode. The offset

adjustment nulls the voltage at the summing node. This is pref-

erable to current injection because it is less affected by subse-

quent gain adjustment. Gain adjustment is made in the feedback

and will work for gains from 1 V/V to 100 V/V.

19

15

16

17

18

30

29

+V

OSS

AD210

+V

ISS

≠V

ISS

+15V

2

3

4

≠V

OSS

V

OUT

V

SIG

14

200

47.5k

5k

100k

GAIN

OFFSET

50k

R

S

1

Figure 6. Adjustments for Inverting Input

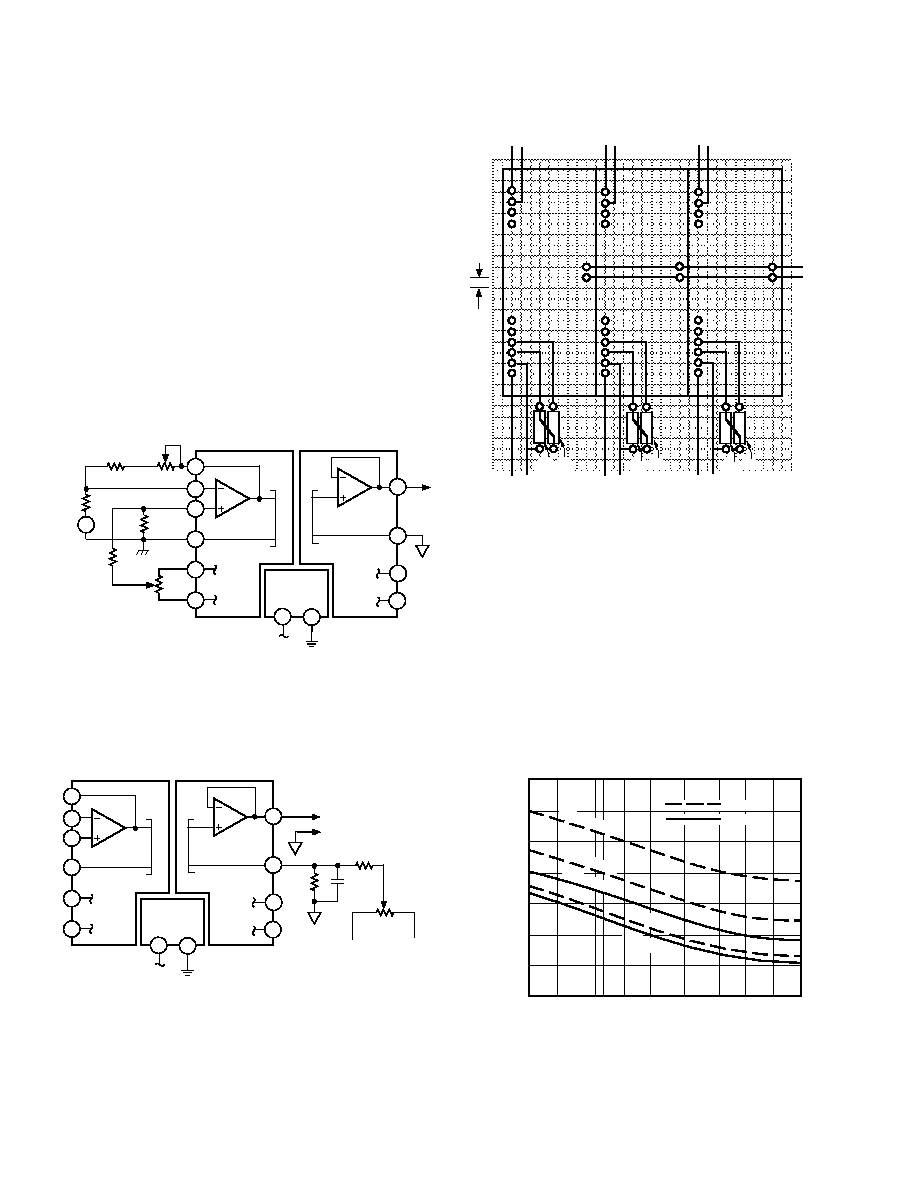

Figure 7 shows how offset adjustments can be made at the out-

put, by offsetting the floating output port. In this circuit,

±

15 V

would be supplied by a separate source. The AD210's output

amplifier is fixed at unity, therefore, output gain must be made

in a subsequent stage.

19

15

16

17

18

30

29

+V

OSS

AD210

+V

ISS

≠V

ISS

+15V

2

3

4

≠V

OSS

V

OUT

14

200

1

0.1µF

100k

OFFSET

50k

+15V

≠15V

Figure 7. Output-Side Offset Adjustment

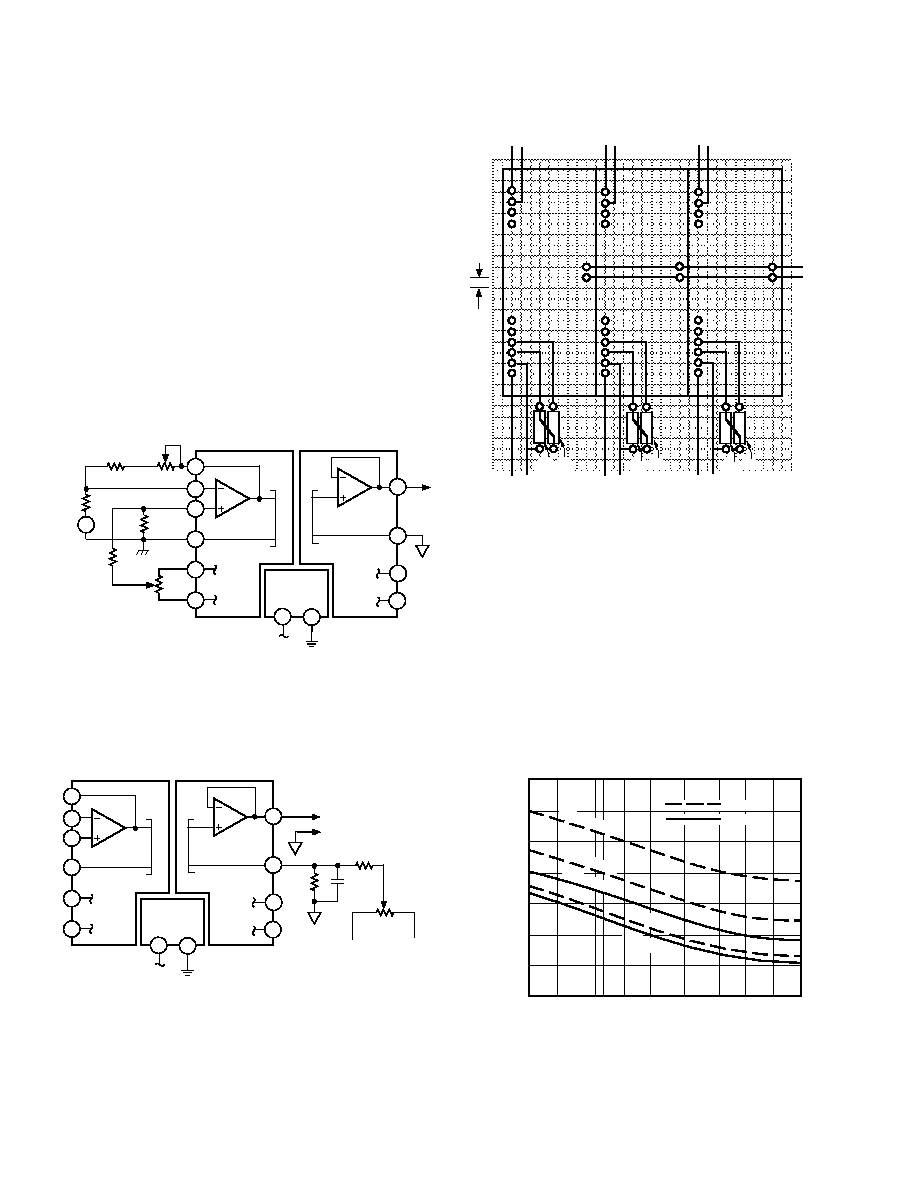

PCB

Layout for Multichannel Applications: The unique

pinout positioning minimizes board space constraints for multi-

channel applications. Figure 8 shows the recommended printed

circuit board layout for a noninverting input configuration with

gain.

R

F

R

G

R

F

R

G

R

F

R

G

POWER

CHANNEL INPUTS

1

2

3

0.1"

GRID

CHANNEL OUTPUTS

1

2

3

Figure 8. PCB Layout for Multichannel Applications with

Gain

Synchronization:

The AD210 is insensitive to the clock of an

adjacent unit, eliminating the need to synchronize the clocks.

However, in rare instances channel to channel pick-up may

occur if input signal wires are bundled together. If this happens,

shielded input cables are recommended.

PERFORMANCE CHARACTERISTICS

Common-Mode Rejection:

Figure 9 shows the common-

mode rejection of the AD210 versus frequency, gain and input

source resistance. For maximum common-mode rejection of

unwanted signals, keep the input source resistance low and care-

fully lay out the input, avoiding excessive stray capacitance at

the input terminals.

180

140

40

10 20 50 60 100 200 500 1k 2k 5k 10k

160

100

120

60

80

FREQUENCY ≠ Hz

R

LO

= 0

R

LO

= 500

R

LO

= 0

R

LO

= 10k

R

LO

= 10k

G = 100

G = 1

CMR ≠ dB

Figure 9. Common-Mode Rejection vs. Frequency

AD210

REV. A

≠5≠

+0.04

+0.03

+0.02

+0.01

0

≠0.01

≠0.02

≠0.03

≠0.04

≠10 ≠8 ≠6 ≠4 ≠2 0 +2 +4 +6 +8 +10

OUTPUT VOLTAGE SWING ≠ Volts

+8

+6

+4

+2

0

≠2

≠4

≠6

≠8

ERROR ≠ mV

ERROR ≠ %

Figure 12. Gain Nonlinearity Error vs. Output

0.01

0.009

0.008

0.007

0.006

0.005

0.004

0.003

0.002

0.001

0.000

100

90

80

70

60

50

40

30

20

10

0

0 2 4 6 8 10 12 14 16 18 20

TOTAL SIGNAL SWING ≠ Volts

ERROR ≠ % of Signal Swing

ERROR ≠ ppm of Signal Swing

Figure 13. Gain Nonlinearity vs. Output Swing

Gain vs. Temperature:

Figure 14 illustrates the AD210's

gain vs. temperature performance. The gain versus temperature

performance illustrated is for an AD210 configured as a unity

gain amplifier.

400

200

0

≠200

≠400

≠600

≠800

≠1000

≠1200

≠1400

≠1600

≠25 0 +25 +50 +70 +85

TEMPERATURE ≠

∞

C

GAIN ERROR ≠ ppm of Span

G = 1

Figure 14. Gain vs. Temperature

Phase Shift:

Figure 10 illustrates the AD210's low phase shift

and gain versus frequency. The AD210's phase shift and wide

bandwidth performance make it well suited for applications like

power monitors and controls systems.

60

20

≠80

100

100k

10k

1k

10

40

≠20

0

≠60

≠40

FREQUENCY ≠ Hz

0

≠20

≠40

≠60

≠80

≠100

≠120

≠140

PHASE SHIFT ≠ Degrees

GAIN ≠ dB

G = 1

G = 100

Figure 10. Phase Shift and Gain vs. Frequency

Input Noise vs. Frequency:

Voltage noise referred to the input

is dependent on gain and signal bandwidth. Figure 11 illustrates

the typical input noise in nV/

Hz

of the AD210 for a frequency

range from 10 to 10 kHz.

60

40

0

100

10k

1k

10

50

20

30

10

FREQUENCY ≠ Hz

NOISE ≠ nV/

Hz

Figure 11. Input Noise vs. Frequency

Gain Nonlinearity vs. Output:

Gain nonlinearity is defined as the

deviation of the output voltage from the best straight line, and is

specified as % peak-to-peak of output span. The AD210B provides

guaranteed maximum nonlinearity of

±

0.012% with an output span of

±

10 V. The AD210's nonlinearity performance is shown in Figure 12.

Gain Nonlinearity vs. Output Swing:

The gain nonlinearity

of the AD210 varies as a function of total signal swing. When

the output swing is less than 20 volts, the gain nonlinearity as a

fraction of signal swing improves. The shape of the nonlinearity

remains constant. Figure 13 shows the gain nonlinearity of the

AD210 as a function of total signal swing.