| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AD9632 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

Ultralow Distortion, Wide

Bandwidth Voltage Feedback Op Amps

AD9631/AD9632

These characteristics position the AD9631/AD9632 ideally for

driving flash as well as high resolution ADCs. Additionally, the

balanced high impedance inputs of the voltage feedback archi-

tecture allow maximum flexibility when designing active filters.

The AD9631 is offered in industrial (≠40

∞

C to +85

∞

C) and mili-

tary (≠55

∞

C to +125

∞

C) temperature ranges and the AD9632 in

industrial. Industrial versions are available in plastic DIP and

SOIC; MIL versions are packaged in cerdip.

≠30

≠130

100k

100M

10M

1M

10k

≠70

≠50

≠110

≠90

FREQUENCY ≠ Hz

HARMONIC DISTORTION ≠ dBc

V

O

= 2V p≠p

V

S

=

±

5V

R

L

= 500

2ND HARMONIC

3RD HARMONIC

Figure 1. AD9631 Harmonic Distortion vs. Frequency,

G = +1

FEATURES

Wide Bandwidth

AD9631, G = +1 AD9632, G = +2

Small Signal

320 MHz

250 MHz

Large Signal (4 V p-p) 175 MHz

180 MHz

Ultralow Distortion (SFDR), Low Noise

≠113 dBc typ @ 1 MHz

≠95 dBc typ @ 5 MHz

≠72 dBc typ @ 20 MHz

+46 dBm 3rd Order Intercept @ 25 MHz

7.0 nV/

Hz Spectral Noise Density

High Speed

Slew Rate 1300 V/

µ

s

Settling 16 ns to 0.01%, 2 V Step

±

3 V to

±

5 V Supply Operation

17 mA Supply Current

APPLICATIONS

ADC Input Driver

Differential Amplifiers

IF/RF Amplifiers

Pulse Amplifiers

Professional Video

DAC Current to Voltage

Baseband and Video Communications

Pin Diode Receivers

Active Filters/Integrators/Log Amps

PRODUCT DESCRIPTION

The AD9631 and AD9632 are very high speed and wide band-

width amplifiers. They are an improved performance alternative

to the AD9621 and AD9622. The AD9631 is unity gain stable.

The AD9632 is stable at gains of two or greater. Utilizing a

voltage feedback architecture, the AD9631/AD9632's excep-

tional settling time, bandwidth, and low distortion meet the

requirements of many applications which previously depended

on current feedback amplifiers. Its classical op amp structure

works much more predictably in many designs.

A proprietary design architecture has produced an amplifier that

combines many of the best characteristics of both current feed-

back and voltage feedback amplifiers. The AD9631 and

AD9632 exhibit exceptionally fast and accurate pulse response

(16 ns to 0.01%) as well as extremely wide small signal and

large signal bandwidth and ultralow distortion. The AD9631

achieves ≠72 dBc at 20 MHz and 320 MHz small signal and

175 MHz large signal bandwidths.

FUNCTIONAL BLOCK DIAGRAM

8-Pin Plastic Mini-DIP (N), Cerdip (Q),

and SO (R) Packages

1

2

3

4

8

7

6

5

AD9631/32

NC

≠INPUT

+INPUT

≠V

S

NC

+V

S

OUTPUT

NC

(Top View)

NC = NO CONNECT

≠2≠

AD9631A

AD9632A

Parameter

Conditions

Min

Typ

Max

Min

Typ Max

Units

DYNAMIC PERFORMANCE

Bandwidth (≠3 dB)

Small Signal

V

OUT

0.4 V p-p

220

320

180

250

MHz

Large Signal

1

V

OUT

= 4 V p-p

150

175

155

180

MHz

Bandwidth for 0.1 dB Flatness

V

OUT

= 300 mV p-p

9631, R

F

= 140

; 9632, R

F

= 425

130

130

MHz

Slew Rate, Average +/≠

V

OUT

= 4 V Step

1000 1300

1200 1500

V/

µ

s

Rise/Fall Time

V

OUT

= 0.5 V Step

1.2

1.4

ns

V

OUT

= 4 V Step

2.5

2.1

ns

Settling Time

To 0.1%

V

OUT

= 2 V Step

11

11

ns

To 0.01%

V

OUT

= 2 V Step

16

16

ns

HARMONIC/NOISE PERFORMANCE

2nd Harmonic Distortion

2 V p-p; 20 MHz, R

L

= 100

≠64

≠57

≠54

≠47

dBc

R

L

= 500

≠72

≠65

≠72

≠65

dBc

3rd Harmonic Distortion

2 V p-p; 20 MHz, R

L

= 100

≠76

≠69

≠74

≠67

dBc

R

L

= 500

≠81

≠74

≠81

≠74

dBc

3rd Order Intercept

25 MHz

+46

+41

dBm

Noise Figure

R

S

= 50

18

14

dB

Input Voltage Noise

1 MHz to 200 MHz

7.0

4.3

nV

Hz

Input Current Noise

1 MHz to 200 MHz

2.5

2.0

pA

Hz

Average Equivalent Integrated

Input Noise Voltage

0.1 MHz to 200 MHz

100

60

µ

V rms

Differential Gain Error (3.58 MHz)

R

L

= 150

0.03

0.06

0.02 0.04

%

Differential Phase Error (3.58 MHz)

R

L

= 150

0.02

0.04

0.02 0.04

Degree

Phase Nonlinearity

dc to 100 MHz

1.1

1.1

Degree

DC PERFORMANCE

2

,

R

L

= 150

Input Offset Voltage

3

3

10

2

5

mV

T

MIN

≠T

MAX

13

8

mV

Offset Voltage Drift

±

10

±

10

µ

V/

∞

C

Input Bias Current

2

7

2

7

µ

A

T

MIN

≠T

MAX

10

10

µ

A

Input Offset Current

0.1

3

0.1

3

µ

A

T

MIN

≠T

MAX

5

5

µ

A

Common-Mode Rejection Ratio

V

CM

=

±

2.5 V

70

90

70

90

dB

Open-Loop Gain

V

OUT

=

±

2.5 V

46

52

46

52

dB

T

MIN

≠T

MAX

40

40

dB

INPUT CHARACTERISTICS

Input Resistance

500

500

k

Input Capacitance

1.2

1.2

pF

Input Common-Mode Voltage Range

±

3.4

±

3.4

V

OUTPUT CHARACTERISTICS

Output Voltage Range, R

L

= 150

±

3.2

±

3.9

±

3.2

±

3.9

V

Output Current

70

70

mA

Output Resistance

0.3

0.3

Short Circuit Current

240

240

mA

POWER SUPPLY

Operating Range

±

3.0

±

5.0

±

6.0

±

3.0

±

5.0

±

6.0

V

Quiescent Current

17

18

16

17

mA

T

MIN

≠T

MAX

21

20

mA

Power Supply Rejection Ratio

T

MIN

≠T

MAX

50

60

56

66

dB

NOTES

1

See Max Ratings and Theory of Operation sections of data sheet.

2

Measured at A

V

= 50.

3

Measured with respect to the inverting input.

Specifications subject to change without notice.

(

±

V

S

=

±

5 V; R

LOAD

= 100

; A

V

= 1 (AD9631); A

V

= 2 (AD9632), unless otherwise noted)

REV. A

AD9631/AD9632≠SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

AD9631/AD9632

REV. A

≠3≠

ABSOLUTE MAXIMUM RATINGS

1

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12.6 V

Voltage Swing

◊

Bandwidth Product . . . . . . . . . . 550 V

◊

MHz

Internal Power Dissipation

2

Plastic Package (N) . . . . . . . . . . . . . . . . . . . . . . . . 1.3 Watts

Small Outline Package (R) . . . . . . . . . . . . . . . . . . . 0.9 Watts

Input Voltage (Common Mode) . . . . . . . . . . . . . . . . . . . .

±

V

S

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . .

±

1.2 V

Output Short Circuit Duration

. . . . . . . . . . . . . . . . . . . . . . Observe Power Derating Curves

Storage Temperature Range N, R . . . . . . . . . ≠65

∞

C to +125

∞

C

Operating Temperature Range (A Grade) . . . ≠ 40

∞

C to +85

∞

C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . +300

∞

C

NOTES

1

Stresses above those listed under "Absolute Maximum Ratings" may cause

permanent damage to the device. This is a stress rating only, and functional

operation of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

8-Pin Plastic Package:

JA

= 90

∞

C/Watt

8-Pin SOIC Package:

JA

= 140

∞

C/Watt

MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by these de-

vices is limited by the associated rise in junction temperature.

The maximum safe junction temperature for plastic encapsu-

lated devices is determined by the glass transition temperature

of the plastic, approximately +150

∞

C. Exceeding this limit tem-

porarily may cause a shift in parametric performance due to a

change in the stresses exerted on the die by the package. Exceed-

ing a junction temperature of +175

∞

C for an extended period can

result in device failure.

While the AD9631 and AD9632 are internally short circuit pro-

tected, this may not be sufficient to guarantee that the maxi-

mum junction temperature (+150

∞

C) is not exceeded under all

conditions. To ensure proper operation, it is necessary to ob-

serve the maximum power derating curves.

2.0

0

≠50 80

1.5

0.5

≠40

1.0

0

10

≠10

≠20

≠30

20 30 40 50 60 70

90

AMBIENT TEMPERATURE ≠

∞

C

MAXIMUM POWER DISSIPATION ≠ Watts

T

J

= +150

∞

C

8-PIN MINI-DIP PACKAGE

8-PIN SOIC PACKAGE

Figure 2. Plot of Maximum Power Dissipation vs.

Temperature

WARNING!

ESD SENSITIVE DEVICE

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although these devices feature proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

METALIZATION PHOTO

Dimensions shown in inches and (mm).

Connect Substrate to ≠V

S

.

0.046

(1.17)

3

+IN

4

≠V

S

6

OUT

≠IN

2

+V

S

7

AD9631

0.050 (1.27)

0.046

(1.17)

0.050 (1.27)

3

+IN

4

≠V

S

6

OUT

≠IN

2

+V

S

7

AD9632

ORDERING GUIDE

Temperature

Package

Package

Model

Range

Description Option*

AD9631AN

≠40C to +85

∞

C

Plastic DIP

N-8

AD9631AR

≠40

∞

C to +85

∞

C

SOIC

R-8

AD9631(SMD)

≠55

∞

C to +125

∞

C

Cerdip

Q-8

AD9631-EB

Evaluation

Board

AD9632AN

≠40

∞

C to +85

∞

C

Plastic DIP

N-8

AD9632AR

≠40

∞

C to +85

∞

C

SOIC

R-8

AD9632-EB

Evaluation

Board

*N = Plastic DIP; Q = Cerdip; R= SOIC (Small Outline Integrated Circuit).

AD9631/AD9632

REV. A

≠4≠

R

F

+V

S

PULSE

GENERATOR

R

L

= 100

≠V

S

V

IN

V

OUT

0.1

µ

F

10

µ

F

AD9631

3

2

7

6

0.1

µ

F

10

µ

F

4

T

R

/T

F

= 350ps

130

R

T

49.9

Figure 3. Noninverting Configuration, G = +1

Figure 4. Large Signal Transient Response; V

O

= 4 V p-p,

G = +1, R

F

= 250

Figure 5. Small Signal Transient Response;

V

O

= 400 mV p-p, G = +1, R

F

= 140

100

+V

S

≠V

S

0.1

µ

F

10

µ

F

AD9631

3

2

7

6

0.1

µ

F

10

µ

F

4

130

R

T

49.9

R

F

R

L

= 100

V

OUT

T

R

/T

F

= 350ps

PULSE

GENERATOR

V

IN

Figure 6. Inverting Configuration, G = ≠1

Figure 7. Large Signal Transient Response; V

O

= 4 V p-p,

G = ≠1, R

F

= R

IN

= 267

Figure 8. Small Signal Transient Response;

V

O

= 400 mV p-p, G = ≠1, R

F

= R

IN

= 267

AD9631≠Typical Characteristics

AD9631/AD9632

REV. A

≠5≠

R

F

PULSE

GENERATOR

+V

S

R

L

= 100

≠V

S

V

IN

V

OUT

0.1

µ

F

10

µ

F

AD9632

3

2

7

6

0.1

µ

F

10

µ

F

4

T

R

/T

F

= 350ps

R

IN

130

R

T

49.9

Figure 9. Noninverting Configuration, G = +2

Figure 10. Large Signal Transient Response; V

O

= 4 V p-p,

G = +2, R

F

= R

IN

= 422

Figure 11. Small Signal Transient Response;

V

O

= 400 mV p-p, G = +2, R

F

= R

IN

= 274

100

R

F

+V

S

R

L

= 100

≠V

S

V

OUT

0.1

µ

F

10

µ

F

AD9632

3

2

7

6

0.1

µ

F

10

µ

F

4

T

R

/T

F

= 350ps

V

IN

PULSE

GENERATOR

130

R

T

49.9

Figure 12. Inverting Configuration, G= ≠1

Figure 13. Large Signal Transient Response; V

O

= 4 V p-p,

G = ≠1, R

F

=

R

IN

= 422

, R

T

= 56.2

Figure 14. Small Signal Transient Response;

V

O

= 400 mV p-p, G = ≠1, R

F

= R

IN

= 267

,

R

T

= 61.9

AD9632≠Typical Characteristics

AD9631/AD9632

REV. A

≠6≠

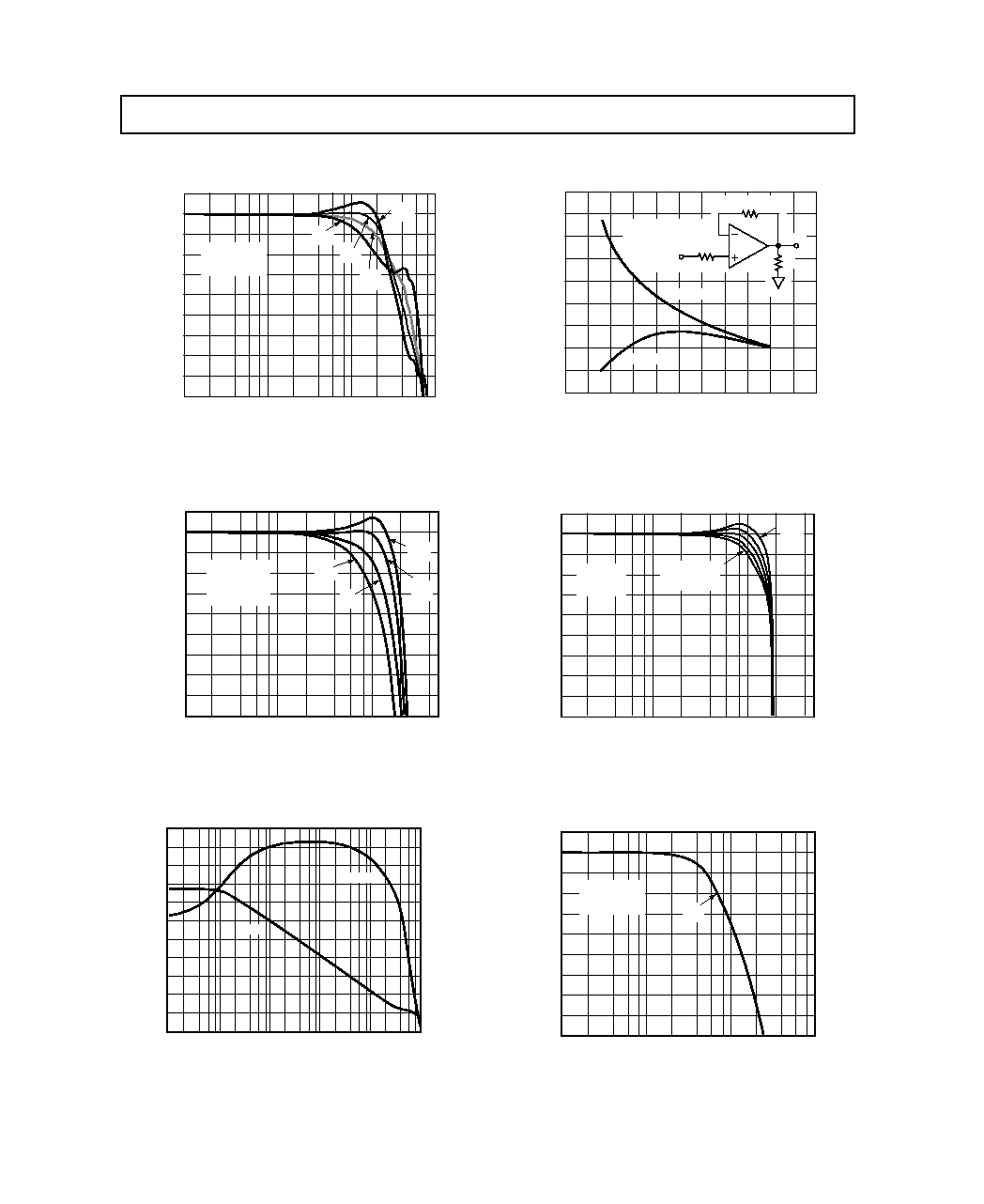

AD9631≠Typical Characteristics

1

≠4

≠9

1M

10M

1G

100M

≠5

≠6

≠7

≠8

≠3

≠2

≠1

0

FREQUENCY ≠ Hz

GAIN ≠ dB

V

S

=

±

5V

R

L

= 100

V

O

= 300mV p-p

R

F

150

R

F

100

R

F

200

R

F

50

Figure 15. AD9631 Small Signal Frequency Response

G = +1

0.1

≠0.4

≠0.9

1M

10M

500M

100M

≠0.5

≠0.6

≠0.7

≠0.8

≠0.3

≠0.2

≠0.1

0

FREQUENCY ≠ Hz

GAIN ≠ dB

V

S

=

±

5V

R

L

= 100

G = +1

Vo = 300mV p-p

R

F

120

R

F

140

R

F

150

R

F

100

Figure 16. AD9631 0.1 dB Flatness, N Package (for R

Package Add 20

to R

F

)

60

10

10k

100k

10M

1M

30

20

40

50

FREQUENCY ≠ Hz

GAIN ≠ dB

0

≠10

100M

1G

100

20

0

≠20

40

60

80

≠80

≠100

≠120

≠60

≠40

90

70

80

≠20

PHASE MARGIN ≠ Degrees

PHASE

GAIN

Figure 17. AD9631 Open-Loop Gain and Phase Margin vs.

Frequency, R

L

= 100

VALUE OF FEEDBACK RESISTOR (R

F

) ≠

≠3dB BANDWIDTH ≠ MHz

450

250

20

240

400

300

40

350

200

220

180

160

140

120

100

80

60

N PACKAGE

R PACKAGE

R

F

130

AD9631

V

S

=

±

5V

R

L

= 100

GAIN = +1

R

L

Figure 18. AD9631 Small Signal ≠3 dB Bandwidth vs. R

F

1

≠4

≠9

1M

10M

500M

100M

≠5

≠6

≠7

≠8

≠3

≠2

≠1

0

FREQUENCY ≠ Hz

OUTPUT ≠ dB

V

S

=

±

5V

V

O

= 4V p-p

R

L

= 100

R

F

250

R

F

= 50

TO

250

BY 50

Figure 19. AD9631 Large Signal Frequency Response,

G = +1

1

≠4

≠9

1M

10M

1G

100M

≠5

≠6

≠7

≠8

≠3

≠2

≠1

0

FREQUENCY ≠ Hz

GAIN ≠ dB

R

F

267

V

S

=

±

5V

R

L

= 100

V

O

= 300mV p-p

Figure 20. AD9631 Small Signal Frequency Response,

G = ≠1

AD9631/AD9632

REV. A

≠7≠

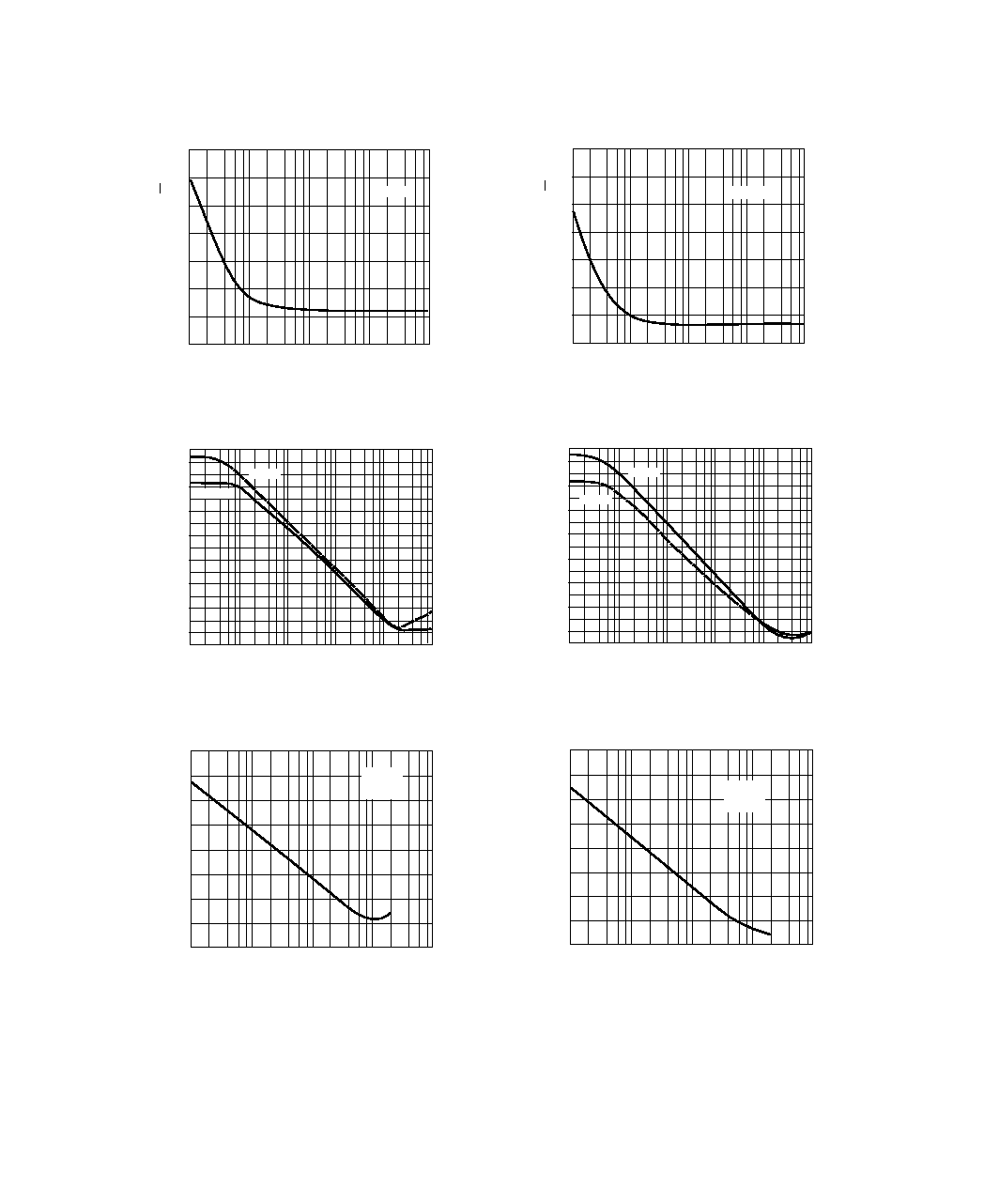

≠30

≠130

100k

100M

10M

1M

10k

≠70

≠50

≠110

≠90

FREQUENCY ≠ Hz

HARMONIC DISTORTION ≠ dBc

V

O

= 2V p-p

V

S

=

±

5V

R

L

= 500

G = +1

2ND HARMONIC

3RD HARMONIC

Figure 21. AD9631 Harmonic Distortion vs. Frequency,

R

L

= 500

≠30

≠130

100k

100M

10M

1M

10k

≠70

≠50

≠110

≠90

FREQUENCY ≠ Hz

V

O

= 2V p-p

V

S

=

±

5V

R

L

= 100

G = +1

2ND HARMONIC

3RD HARMONIC

HARMONIC DISTORTION ≠ dBc

Figure 22. AD9631 Harmonic Distortion vs. Frequency,

R

L

= 100

50

30

10

100

25

20

35

40

45

FREQUENCY ≠ MHz

INTERCEPT ≠ +dBm

60

55

20

40

80

60

Figure 23. AD9631 Third Order Intercept vs. Frequency

0.10

≠0.10

≠0.05

0.00

0.05

DIFF GAIN ≠ %

1st

2nd

3rd

4th

5th

6th

7th

8th

9th 10th 11th

0.05

≠0.05

0.00

0.10

DIFF PHASE ≠ Degrees ≠0.10

1st

2nd

3rd

4th

5th

6th

7th

8th

9th 10th 11th

Figure 24. AD9631 Differential Gain and Phase Error,

G = +2, R

L

= 150

0.3

≠0.3

0

≠0.2

0

≠0.1

0.2

0.1

80

60

40

20

SETTLING TIME ≠ ns

ERROR ≠ %

70

50

30

10

Figure 25. AD9631 Short-Term Settling Time, 2 V Step,

R

L

= 100

0.3

≠0.2

0.1

≠0.1

1

0

0.2

10

9

7

6

5

4

3

2

SETTLING TIME ≠ µs

ERROR ≠ %

8

0

Figure 26. AD9631 Long-Term Settling Time, 2 V Step,

R

L

= 100

AD9631/AD9632

REV. A

≠8≠

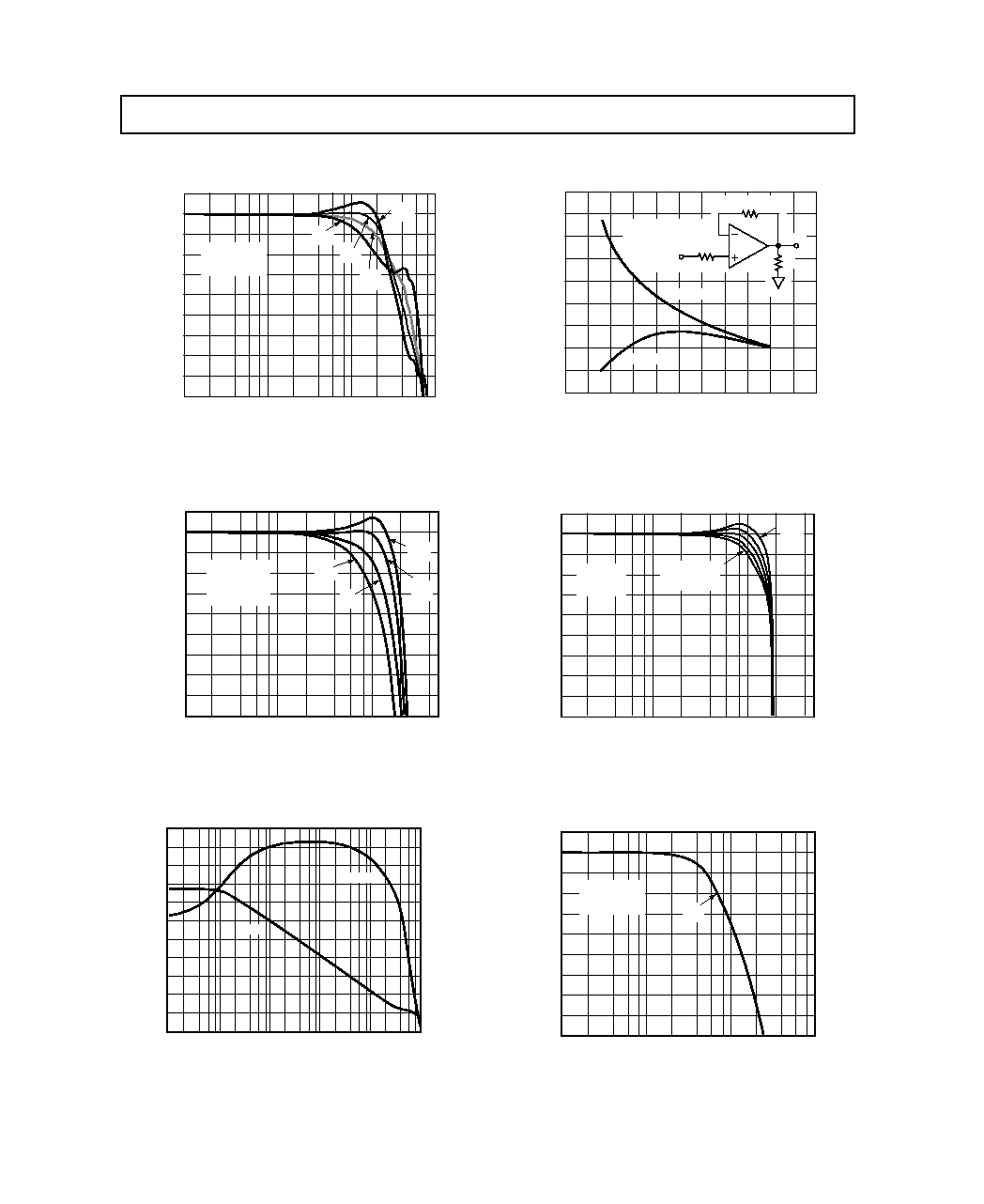

7

2

≠3

1M

10M

1G

100M

1

0

≠1

≠2

3

4

5

6

R

F

325

R

F

425

R

F

125

R

F

225

FREQUENCY ≠ Hz

GAIN ≠ dB

V

S

=

±

5V

R

L

= 100

V

O

= 300mV p-p

Figure 27. AD9632 Small Signal Frequency Response,

G = +2

0.1

≠0.4

≠0.9

1M

10M

100M

≠0.5

≠0.6

≠0.7

≠0.8

≠0.3

≠0.2

≠0.1

0

OUTPUT ≠ dB

R

F

375

R

F

425

R

F

275

R

F

325

FREQUENCY ≠ Hz

V

S

=

±

5V

R

L

= 100

G = +2

V

O

= 300mV p-p

Figure 28. AD9632 0.1 dB Flatness, N Package

(for R Package Add 20

to R

F

)

65

25

≠15

10k

100k

1G

100M

10M

1M

35

45

55

≠5

5

15

FREQUENCY ≠ Hz

60

20

30

40

50

≠10

0

10

A

OL

≠ dB

≠50

≠250

0

50

100

≠200

≠150

≠100

PHASE ≠ Degrees

GAIN

PHASE

Figure 29. AD9632 Open-Loop Gain and Phase Margin vs.

Frequency, R

L

= 100

200

150

100

250

300

350

550

500

450

400

350

300

250

200

150

VALUE OF R

F

,R

IN

≠

≠3dB BANDWIDTH ≠ MHz

N PACKAGE

R PACKAGE

V

S

=

±

5V

R

L

= 100

GAIN = +2

R

F

AD9632

R

L

R

IN

100

49.9

Figure 30. AD9632 Small Signal ≠3 dB Bandwidth

vs. R

F

, R

IN

7

2

≠3

1M

10M

500M

100M

1

0

≠1

≠2

3

4

5

6

FREQUENCY ≠ Hz

OUTPUT ≠ dB

R

F

525

R

F

125

TO

525

BY

100

V

S

=

±

5V

V

O

= 4V p-p

R

L

= 100

Figure 31. AD9632 Large Signal Frequency Response,

G = +2

1

≠4

≠9

1M

10M

1G

100M

≠5

≠6

≠7

≠8

≠3

≠2

≠1

0

FREQUENCY ≠ Hz

GAIN ≠ dB

V

S

=

±

5V

R

L

= 100

V

O

= 300mV p-p

R

F

, R

IN

267

Figure 32. AD9632 Small Signal Frequency Response,

G = ≠1

AD9632≠Typical Characteristics

AD9631/AD9632

REV. A

≠9≠

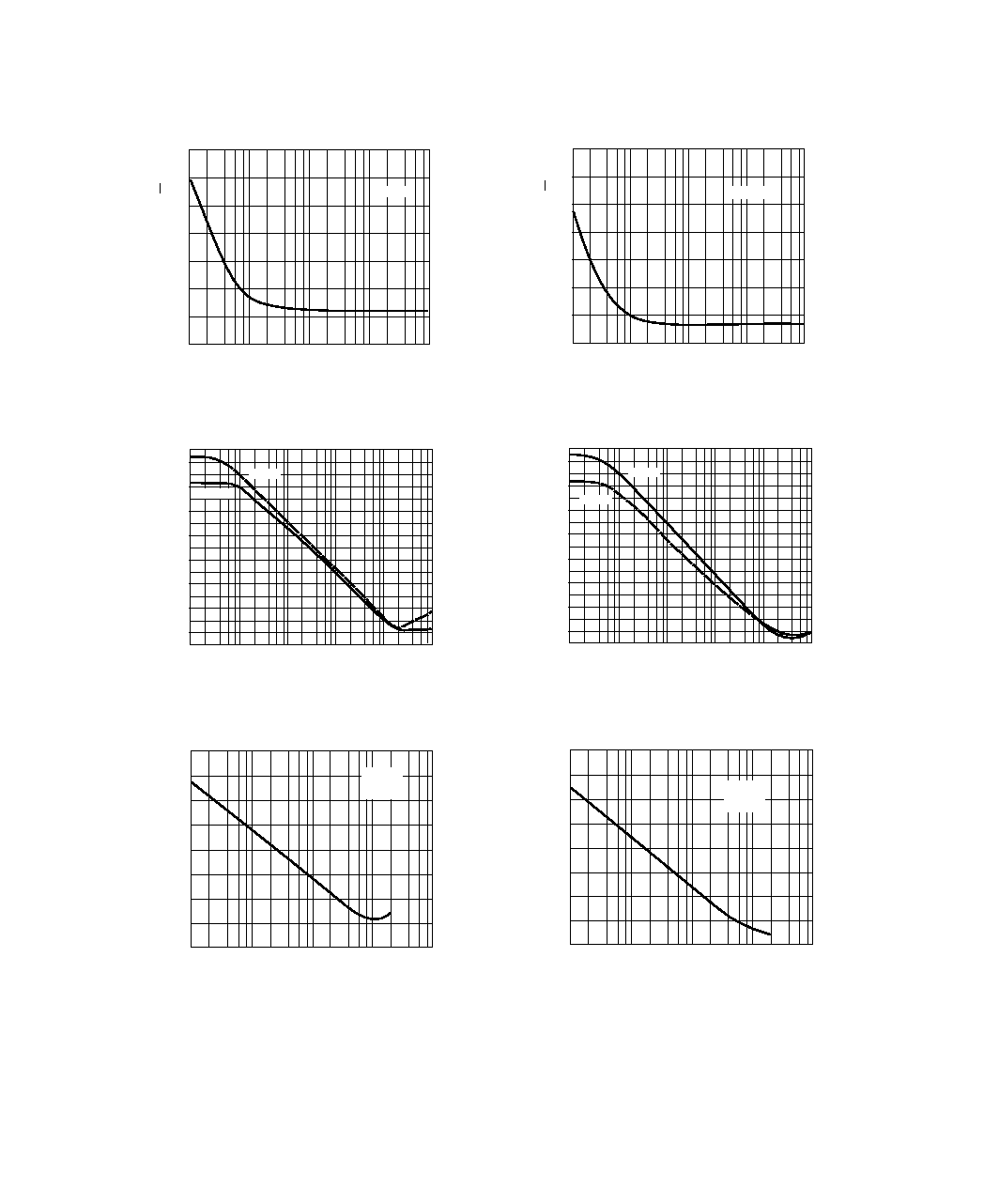

≠30

≠130

100k

100M

10M

1M

10k

≠70

≠50

≠110

≠90

FREQUENCY ≠ Hz

HARMONIC DISTORTION ≠ dBc

V

O

= 2V p-p

V

S

=

±

5V

R

L

= 500

G = +2

2ND HARMONIC

3RD HARMONIC

Figure 33. AD9632 Harmonic Distortion vs. Frequency,

R

L

= 500

≠30

≠130

100k

100M

10M

1M

10k

≠70

≠50

≠110

≠90

FREQUENCY ≠ Hz

HARMONIC DISTORTION ≠ dBc

V

O

= 2V p-p

V

S

=

±

5V

R

L

= 100

G = +2

2ND HARMONIC

3RD HARMONIC

Figure 34. AD9632 Harmonic Distortion vs. Frequency,

R

L

= 100

50

30

10

10

100

25

20

15

35

40

45

FREQUENCY ≠ MHz

INTERCEPT ≠ +dBm

Figure 35. AD9632 Third Order Intercept vs. Frequency

0.04

≠0.04

≠0.02

0.00

0.02

DIFF GAIN ≠ %

1st

2nd

3rd

4th

5th

6th

7th

8th

9th 10th 11th

0.02

≠0.02

0.00

0.04

DIFF PHASE ≠ Degrees ≠0.04

1st

2nd

3rd

4th

5th

6th

7th

8th

9th 10th 11th

Figure 36. AD9632 Differential Gain and Phase Error

G = +2, R

L

= 150

0.2

≠0.3

0

≠0.2

0

10

20

30

40

50

60

70

80

≠0.1

0.1

SETTLING TIME ≠ ns

ERROR ≠ %

Figure 37. AD9632 Short-Term Settling Time 2 V Step,

R

L

= 100

0.3

≠0.2

0.1

≠0.1

0

9

8

7

6

5

4

3

2

1

0

0.2

SETTLING TIME ≠ µs

ERROR ≠ %

10

Figure 38. AD9632 Long-Term Settling Time 2 V Step,

R

L

= 100

REV. A

≠10≠

24

18

3

100

100k

10k

1k

10

21

12

15

6

9

FREQUENCY ≠ Hz

V

S

=

±

5V

INPUT NOISE VOLTAGE ≠ nV/

Hz

Figure 39. AD9631 Noise vs. Frequency

80

70

60

50

40

30

20

10

0

75

65

55

45

35

25

15

5

10k

100k

1G

100M

10M

1M

FREQUENCY ≠ Hz

PSRR ≠ dB

≠PSRR

+PSRR

Figure 40. AD9631 PSRR vs. Frequency

100

90

80

70

60

50

40

30

20

100k

1G

100M

10M

1M

FREQUENCY ≠ Hz

CMRR ≠ dB

V

S

=

±

5V

V

CM

= 1V

R

L

= 100

Figure 41. AD9631 CMRR vs. Frequency

17

13

3

100

100k

10k

1k

10

15

9

11

5

7

FREQUENCY ≠ Hz

INPUT NOISE VOLTAGE ≠ nV/

Hz

V

S

=

±

5V

Figure 42. AD9632 Noise vs. Frequency

80

70

60

50

40

30

20

10

0

75

65

55

45

35

25

15

5

10k

100k

1G

100M

10M

1M

FREQUENCY ≠ Hz

PSRR ≠ dB

≠PSRR

+PSRR

Figure 43. AD9632 PSRR vs. Frequency

100

90

80

70

60

50

40

30

20

100k

1G

100M

10M

1M

FREQUENCY ≠ Hz

CMRR ≠ dB

V

S

=

±

5V

V

CM

= 1V

R

L

= 100

Figure 44. AD9632 CMRR vs. Frequency

AD9631/AD9632≠Typical Characteristics

AD9631/AD9632

REV. A

≠11≠

1000

10

0.01

100k

100M

10M

1M

10k

1

0.1

100

FREQUENCY ≠ Hz

R

OUT

≠

V

S

=

±

5V

GAIN = +1

Figure 45. AD9631 Output Resistance vs. Frequency

1000

10

0.01

100k

100M

10M

1M

10k

1

0.1

100

FREQUENCY ≠ Hz

R

OUT

≠

V

S

=

±

5V

GAIN = +2

Figure 46. AD9632 Output Resistance vs. Frequency

4.1

3.3

140

3.5

3.4

≠40

≠60

3.7

3.6

3.8

3.9

4.0

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

OUTPUT SWING ≠ Volts

V

S

=

±

5V

R

L

= 150

+V

OUT

|≠V

OUT

|

R

L

= 50

+V

OUT

|≠V

OUT

|

}

}

Figure 47. AD9631/AD9632 Output Swing vs. Temperature

1350

350

140

650

450

≠40

550

≠60

950

750

850

1050

1150

1250

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

OPEN-LOOP GAIN ≠ V/V

AD9632

AD9631

+A

OL

≠A

OL

+A

OL

≠A

OL

Figure 48. Open-Loop Gain vs. Temperature

76

56

140

62

58

≠40

60

≠60

68

64

66

70

72

74

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

PSRR ≠ ≠dB

AD9632

AD9631

AD9632

AD9631

≠PSRR

+PSRR

≠PSRR

+PSRR

Figure 49. PSRR vs. Temperature

≠98

≠86

140

≠92

≠88

≠40

≠90

≠60

≠96

≠94

120

80

60

40

100

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

CMRR ≠ ≠dB

≠CMRR

+CMRR

Figure 50. AD9631/AD9632 CMRR vs. Temperature

REV. A

≠12≠

AD9631/AD9632≠Typical Characteristics

21

14

140

17

15

≠40

16

≠60

20

18

19

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

SUPPLY CURRENT ≠ mA

AD9631

AD9632

AD9631

AD9632

±

6V

±

6V

±

5V

±

5V

Figure 51. Supply Current vs. Temperature

≠1.0

≠5.0

140

≠4.0

≠4.5

≠40

≠60

≠3.0

≠3.5

≠2.5

≠2.0

≠1.5

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

INPUT OFFSET VOLTAGE ≠ mV

AD9632

AD9631

V

S

=

±

5V

V

S

=

±

6V

V

S

=

±

5V

V

S

=

±

6V

Figure 52. Input Offset Voltage vs. Temperature

220

0

7

60

20

≠6

40

≠7

120

80

100

140

160

180

200

5

4

3

2

1

≠1

≠2

≠3

≠4

≠5

0

6

100

20

0

10

50

30

40

60

70

80

90

INPUT OFFSET VOLTAGE ≠ mV

COUNT

PERCENT

CUMULATIVE

3 WAFER LOTS

COUNT = 1373

FREQ. DIST

Figure 53. AD9631 Input Offset Voltage Distribution

250

180

140

210

190

≠40

200

≠60

240

220

230

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

SHORT CIRCUIT CURRENT ≠ mA

AD9631

AD9632

SINK

SOURCE

SINK

SOURCE

Figure 54. Short Circuit Current vs. Temperature

2.0

≠2.0

140

≠1.0

≠1.5

≠40

≠60

0.0

≠0.5

0.5

1.0

1.5

120

100

80

60

40

20

0

≠20

JUNCTION TEMPERATURE ≠

∞

C

INPUT BIAS CURRENT ≠ µA

AD9631

AD9632

+I

B

+I

B

≠I

B

≠I

B

Figure 55. Input Bias Current vs. Temperature

0

7

60

20

≠6

40

≠7

120

80

100

140

160

180

5

4

3

2

1

≠1

≠2

≠3

≠4

≠5

0

6

100

20

0

10

50

30

40

60

70

80

90

INPUT OFFSET VOLTAGE ≠ mV

COUNT

PERCENT

CUMULATIVE

3 WAFER LOTS

COUNT = 573

FREQ. DIST

Figure 56. AD9632 Input Offset Voltage Distribution

AD9631/AD9632

REV. A

≠13≠

THEORY OF OPERATION

General

The AD9631 and AD9632 are wide bandwidth, voltage feed-

back amplifiers. Since their open-loop frequency response fol-

lows the conventional 6 dB/octave roll-off, their gain bandwidth

product is basically constant. Increasing their closed-loop gain

results in a corresponding decrease in small signal bandwidth.

This can be observed by noting the bandwidth specification

between the AD9631 (gain of 1) and AD9632 (gain of 2). The

AD9631/AD9632 typically maintain 65 degrees of phase mar-

gin. This high margin minimizes the effects of signal and noise

peaking.

Feedback Resistor Choice

The value of the feedback resistor is critical for optimum perfor-

mance on the AD9631 (gain +1) and less critical as the gain in-

creases. Therefore, this section is specifically targeted at the

AD9631.

At minimum stable gain (+1), the AD9631 provides optimum

dynamic performance with R

F

= 140

. This resistor acts only

as a parasitic suppressor against damped RF oscillations that

can occur due to lead (input, feedback) inductance and parasitic

capacitance. This value of R

F

provides the best combination of

wide bandwidth, low parasitic peaking, and fast settling time.

In fact, for the same reasons, a 100≠130

resistor should be

placed in series with the positive input for other AD9631

noninverting and all AD9631 inverting configurations. The cor-

rect connection is shown in Figures 57 and 58.

+V

S

≠V

S

V

IN

100≠130

0.1

µ

F

10

µ

F

6

7

2

4

3

0.1

µ

F

10

µ

F

R

F

R

G

R

IN

V

OUT

G = 1 +

R

F

R

G

AD9631/32

R

TERM

Figure 57. Noninverting Operation

+V

S

≠V

S

V

IN

100≠130

0.1

µ

F

10

µ

F

6

7

2

4

3

0.1

µ

F

10

µ

F

R

F

R

G

R

TERM

V

OUT

G = ≠

R

F

R

G

AD9631/32

R

IN

Figure 58. Inverting Operation

When the AD9631 is used in the transimpedance (I to V) mode,

such as in photodiode detection, the value of R

F

and diode ca-

pacitance (C

I

) are usually known. Generally, the value of R

F

se-

lected will be in the k

range, and a shunt capacitor (C

F

) across

R

F

will be required to maintain good amplifier stability. The

value of C

F

required to maintain optimal flatness (<1 dB Peak-

ing) and settling time can be estimated as:

C

F

(2

O

C

I

R

F

≠ 1)/

O

2

R

F

2

[

]

1/2

where

O

is equal to the unity gain bandwidth product of the

amplifier in rad/sec, and C

I

is the equivalent total input

capacitance at the inverting input. Typically

O

= 800

◊

10

6

rad/sec (see Open-Loop Frequency Response curve (Fig-

ure 17).

As an example, choosing R

F

= 10 k

and C

I

= 5 pF, requires

C

F

to be 1.1 pF (Note: C

I

includes both source and parasitic

circuit capacitance). The bandwidth of the amplifier can be es-

timated using the C

F

calculated as:

f

3 dB

1.6

2

R

F

C

F

R

F

V

OUT

AD9631

C

F

C

I

I

I

Figure 59. Transimpedance Configuration

AD9631/AD9632

REV. A

≠14≠

For general voltage gain applications, the amplifier bandwidth

can be closely estimated as:

f

3 dB

O

2

1

+

R

F

R

G

This estimation loses accuracy for gains of +2/≠1 or lower due

to the amplifier's damping factor. For these "low gain" cases,

the bandwidth will actually extend beyond the calculated value

(see Closed-Loop BW plots, Figures 15 and 27).

As a rule of thumb, capacitor C

F

will not be required if:

(R

F

R

G

)

◊

C

I

NG

4

O

where NG is the Noise Gain (1 + R

F

/R

G

) of the circuit. For

most voltage gain applications, this should be the case.

Pulse Response

Unlike a traditional voltage feedback amplifier, where the slew

speed is dictated by its front end dc quiescent current and gain

bandwidth product, the AD9631 and AD9632 provide "on de-

mand" current that increases proportionally to the input "step"

signal amplitude. This results in slew rates (1300 V/

µ

s) compa-

rable to wideband current feedback designs. This, combined

with relatively low input noise current (2.0 pA/

Hz

), gives the

AD9631 and AD9632 the best attributes of both voltage and

current feedback amplifiers.

Large Signal Performance

The outstanding large signal operation of the AD9631 and

AD9632 is due to a unique, proprietary design architecture.

In order to maintain this level of performance, the maximum

550 V-MHz product must be observed, (e.g., @ 100 MHz,

V

O

5.5 V p-p).

Power Supply Bypassing

Adequate power supply bypassing can be critical when optimiz-

ing the performance of a high frequency circuit. Inductance in

the power supply leads can form resonant circuits that produce

peaking in the amplifier's response. In addition, if large current

transients must be delivered to the load, then bypass capacitors

(typically greater than 1

µ

F) will be required to provide the best

settling time and lowest distortion. A parallel combination of at

least 4.7

µ

F, and between 0.1

µ

F and 0.01

µ

F, is recommended.

Some brands of electrolytic capacitors will require a small series

damping resistor

4.7

for optimum results.

Driving Capacitive Loads

The AD9631 and AD9632 were designed primarily to drive

nonreactive loads. If driving loads with a capacitive component

is desired, the best frequency response is obtained by the addi-

tion of a small series resistance as shown in Figure 60. The ac-

companying graph shows the optimum value for R

SERIES

vs.

capacitive load. It is worth noting that the frequency response of

the circuit when driving large capacitive loads will be dominated

by the passive roll-off of R

SERIES

and C

L

.

R

F

R

SERIES

R

L

1k

C

L

R

IN

AD9631/32

R

IN

Figure 60. Driving Capacitive Loads

40

0

25

30

10

5

20

15

20

10

R

SERIES

≠

C

L

≠ pF

Figure 61. Recommended R

SERIES

vs. Capacitive Load

AD9631/AD9632

REV. A

≠15≠

APPLICATIONS

The AD9631 and AD9632 are voltage feedback amplifiers well

suited for such applications as photodetectors, active filters, and

log amplifiers. The devices' wide bandwidth (320 MHz), phase

margin (65

∞

), low noise current (2.0 pA/

Hz

), and slew rate

(1300 V/

µ

s) give higher performance capabilities to these appli-

cations over previous voltage feedback designs.

With a settling time of 16 ns to 0.01% and 11 ns to 0.1%, the

devices are an excellent choice for DAC I/V conversion. The

same characteristics along with low harmonic distortion make

them a good choice for ADC buffering/amplification. With su-

perb linearity at relatively high signal frequencies, the AD9631

and AD9632 are ideal drivers for ADCs up to 12 bits.

Operation as a Video Line Driver

The AD9631 and AD9632 have been designed to offer out-

standing performance as video line drivers. The important

specifications of differential gain (0.02%) and differential phase

(0.02

∞

) meet the most exacting HDTV demands for driving

video loads.

75

CABLE

274

274

75

CABLE

75

75

V

OUT

+V

S

≠V

S

75

V

IN

0.1

µ

F

10

µ

F

AD9631/

AD9632

3

2

7

0.1

µ

F

10

µ

F

4

6

Figure 62. Video Line Driver

Active Filters

The wide bandwidth and low distortion of the AD9631 and

AD9632 are ideal for the realization of higher bandwidth active

filters. These characteristics, while being more common in many

current feedback op amps, are offered in the AD9631 and AD9632

in a voltage feedback configuration. Many active filter configu-

rations are not realizable with current feedback amplifiers.

A multiple feedback active filter requires a voltage feedback

amplifier and is more demanding of op amp performance than

other active filter configurations such as the Sallen-Key. In

general, the amplifier should have a bandwidth that is at least

ten times the bandwidth of the filter if problems due to phase

shift of the amplifier are to be avoided.

Figure 63 is an example of a 20 MHz low pass multiple feed-

back active filter using an AD9632.

1

5

V

IN

R4

154

C1

50pF

C2

100pF

R1

154

AD9632

R3

78.7

0.1

µ

F

+5V

≠5V

0.1

µ

F

7

3

2

4

100

6

V

OUT

10

µ

F

10

µ

F

Figure 63. Active Filter Circuit

Choose:

F

O

= Cutoff Frequency = 20 MHz

= Damping Ratio = 1/Q = 2

H = Absolute Value of Circuit Gain =

≠R4

R1 = 1

Then:

k

=

2

F

O

C1

C2

=

4 C1(H

+

1)

2

R1

=

2 HK

R3

=

2 K (H

+

1)

R4

=

H(R1)

AD9631/AD9632

REV. A

≠16≠

A/D Converter Driver

As A/D converters move toward higher speeds with higher reso-

lutions, there becomes a need for high performance drivers that

will not degrade the analog signal to the converter. It is desir-

able from a system's standpoint that the A/D be the element in

the signal chain that ultimately limits overall distortion. This

places new demands on the amplifiers used to drive fast, high

resolution A/Ds.

With high bandwidth, low distortion and fast settling time the

AD9631 and AD9632 make high performance A/D drivers for

advanced converters. Figure 64 is an example of an AD9631

used as an input driver for an AD872. A 12-bit, 10 Msps A/D

converter.

MSB

BIT2

BIT3

BIT4

BIT5

BIT6

BIT7

BIT8

BIT9

BIT10

BIT11

BIT12

AV

DD

AGND

V

INA

REF GND

REF IN

REF OUT

AV

SS

AV

SS

AGND

OTR

CLK

DRGND

DRV

DD

DGND

DV

DD

19

18

17

16

15

14

13

12

11

10

9

8

24

25

3

26

28

27

1

20

21

23

22

6

7

4

5

V

INB

0.1

µ

F

≠5V ANALOG

AD872

1

7

6

4

3

2

5

1

µ

F

+5V ANALOG

AD9631

ANALOG IN

0.1

µ

F

0.1

µ

F

0.1

µ

F

DIGITAL OUTPUT

0.1

µ

F

0.1

µ

F

10

49.9

CLOCK INPUT

0.1

µ

F

0.1

µ

F

140

+5V ANALOG

+5V DIGITAL

+5V DIGITAL

130

≠5V

ANALOG

2

10

µ

F

10

µ

F

Figure 64. AD9631 Used as Driver for an AD872, a 12-Bit, 10 Msps A/D Converter

AD9631/AD9632

REV. A

≠17≠

R

F

R

O

IN

+V

S

≠V

S

R

S

R

T

R

G

OUT

C1

1000pF

C3

0.1

µ

F

C5

10

µ

F

C2

1000pF

C4

0.1

µ

F

C6

10

µ

F

+V

S

≠V

S

OPTIONAL

R

F

R

O

IN

+V

S

≠V

S

R

T

R

G

OUT

R

S

Inverting Configuration

Noninverting Configuration

Supply Bypassing

Figure 65. Inverting and Noninverting Configurations for

Evaluation Boards

Table I.

AD9631A

AD9632A

Gain

Gain

Component

≠1

+1

+2

+10

+100

≠1

+2

+10

+100

R

F

274

140

274

2 k

2 k

274

274

2 k

2 k

R

G

274

274

221

20.5

274

274

221

20.5

R

O

(Nominal)

49.9

49.9

49.9

49.9

49.9

100

100

49.9

49.9

R

S

100

130

100

100

100

100

100

100

100

R

T

(Nominal)

61.9

49.9

49.9

49.9

49.9

61.9

49.9

49.9

49.9

Small Signal

BW (MHz)

90

320

90

10

1.3

250

250

20

3

Layout Considerations

The specified high speed performance of the AD9631 and

AD9632 requires careful attention to board layout and compo-

nent selection. Proper RF design techniques and low pass para-

sitic component selection are mandatory.

The PCB should have a ground plane covering all unused por-

tions of the component side of the board to provide a low im-

pedance path. The ground plane should be removed from the

area near the input pins to reduce stray capacitance.

Chip capacitors should be used for the supply bypassing (see

Figure 64). One end should be connected to the ground plane

and the other within 1/8 inch of each power pin. An additional

large (0.47

µ

F≠10

µ

F) tantalum electrolytic capacitor should be

connected in parallel, though not necessarily so close, to supply

current for fast, large signal changes at the output.

The feedback resistor should be located close to the inverting

input pin in order to keep the stray capacitance at this node to a

minimum. Capacitance variations of less than 1 pF at the in-

verting input will significantly affect high speed performance.

Stripline design techniques should be used for long signal traces

(greater than about 1 inch). These should be designed with a

characteristic impedance of 50

or 75

and be properly termi-

nated at each end.

Evaluation Board

An evaluation board for both the AD9631 and AD9632 is avail-

able that has been carefully laid out and tested to demonstrate

that the specified high speed performance of the device can be

realized. For ordering information, please refer to the Ordering

Guide.

The layout of the evaluation board can be used as shown or

serve as a guide for a board layout.

AD9631/AD9632

REV. A

≠18≠

Figure 66. Evaluation Board Silkscreen (Top)

DIP (N)

INVERTER

SOIC (R)

INVERTER

DIP (N)

INVERTER

SOIC (R)

INVERTER

DIP (N)

NONINVERTER

SOIC (R)

NONINVERTER

DIP (N)

NONINVERTER

SOIC (R)

NONINVERTER

Figure 67. Board Layout (Solder Side)

AD9631/AD9632

REV. A

≠19≠

Figure 68. Board Layout (Component Side)

DIP (N)

INVERTER

SOIC (R)

INVERTER

DIP (N)

NONINVERTER

SOIC (R)

NONINVERTER

AD9631/AD9632

REV. A

≠20≠

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

C1936a≠2.5≠11/94

PRINTED IN U.S.A.

8-Pin Plastic DIP

(N Package)

PIN 1

0.280 (7.11)

0.240 (6.10)

4

5

8

1

0.060 (1.52)

0.015 (0.38)

0.130

(3.30)

MIN

0.210

(5.33)

MAX

0.160 (4.06)

0.115 (2.93)

0.430 (10.92)

0.348 (8.84)

SEATING

PLANE

0.022 (0.558)

0.014 (0.356)

0.070 (1.77)

0.045 (1.15)

0.100

(2.54)

BSC

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

0.195 (4.95)

0.115 (2.93)

8-Pin Plastic SOIC

(R Package)

0.019 (0.48)

0.014 (0.36)

0.050

(1.27)

BSC

0.102 (2.59)

0.094 (2.39)

0.197 (5.01)

0.189 (4.80)

0.010 (0.25)

0.004 (0.10)

0.098 (0.2482)

0.075 (0.1905)

0.190 (4.82)

0.170 (4.32)

0.030 (0.76)

0.018 (0.46)

10

∞

0

∞

0.090

(2.29)

8

∞

0

∞

0.020 (0.051) x 45

∞

CHAMF

1

8

5

4

PIN 1

0.157 (3.99)

0.150 (3.81)

0.244 (6.20)

0.228 (5.79)

0.150 (3.81)

8-Pin Cerdip

(Q Package)

0.320 (8.13)

0.290 (7.37)

0.015 (0.38)

0.008 (0.20)

15

∞

0

∞

0.005 (0.13) MIN

0.055 (1.4) MAX

1

PIN 1

4

5

8

0.310 (7.87)

0.220 (5.59)

0.405 (10.29) MAX

0.200

(5.08)

MAX

0.060 (1.52)

0.015 (0.38)

0.150

(3.81)

MIN

0.200 (5.08)

0.125 (3.18)

SEATING

PLANE

0.023 (0.58)

0.014 (0.36)

0.070 (1.78)

0.030 (0.76)

0.100

(2.54)

BSC