Alliance Semiconductor

2575 Augustine Drive . Santa Clara, CA 95054 . Tel: 408.855.4900 . Fax: 408.855.4999 . www.alsc.com

Notice: The information in this document is subject to change without notice

October 2003

rev 1.0

3/3.3/4.0 V µP Supervisor Circuits

ASM706 P/ R/ S/ T/ J

ASM708 R/ S/ T/ J

General Description

The ASM706P/R/S/T/J and ASM708R/S/T/J are cost effective

CMOS supervisor circuits that monitor power-supply and

battery voltage level, and

µP/µC operation.

The family offers several functional options. Each device

generates a reset signal during power-up, power-down and

during brownout conditions. A reset is generated when the

supply drops below 2.63V (ASM706P/R, ASM708R), 2.93V

(ASM706S, ASM708S), 3.08V (ASM706T, ASM708T) or 4.00

(ASM706J, ASM708J). In addition, the ASM706P/R/S/T/J

feature a 1.6 second watchdog timer. The watchdog timer

output will trigger a reset if connected to MR. Floating the WDI

input pin disables the watchdog timer.

The ASM708R/S/T/J have both active-HIGH and active-LOW

reset outputs but no watchdog function. The ASM706P has the

same pin-out and functions as the ASM706R but has an active-

HIGH reset output.

A versatile power-fail circuit, useful in checking battery levels

and non-5V supplies, has a 1.25V threshold. All devices have a

manual reset input. All devices are available in 8-pin DIP, SO

and the compact MicroSO packages. The MicroSO package

requires 50% less PC board area than the conventional SO

package.

Features

∑

Precision power supply minotor

∑2.63V threshold (ASM706P/R, ASM708R)

∑2.93V threshold (ASM706S, ASM708S)

∑3.08V threshold (ASM706T, ASM708T)

∑New 4.00V threshold (ASM706J , ASM708J)

∑

Debounced manual reset input

∑

Auxiliary voltage monitor comparator

∑1.25V threshold

∑Battery monitor / auxiliary supply monitor

∑

Watchdog timer (ASM706P/R/S/T/J)

∑Watchdog can be disabled by floating WDI

∑

200ms reset time delay

∑

Three reset signal options

∑Active HIGH: ASM706P

∑Active LOW: ASM706R/S/T/J

∑Active HIGH and LOW outputs: ASM708R/S/T/J

∑

DIP, SO and MicroSO packages

∑

Guaranteed RESET assertion to V

CC

= 1.1V

Applications

∑

Computers and embedded controllers

∑

CTI applications

∑

Automotive systems

∑

Portable/Battery-operated systems

∑

Intelligent instruments

∑

Wireless communication systems

∑

PDAs and hand-held equipment

∑

Safety systems

Typical Operating Circuit

+3.3V Regulator

V

CC

PFI

MR

(RESET)

WDI

WDO

PFO

V

CC

(RESET)

I/O LINE

NMI

INTERRUPT

Unregulated DC

R

1

R

2

µP

ASM706 R/S/T

ASM708 R/S/T

(ASM706 P)

RESET

RESET

ASM706 P/ R/ S/ T/ J

2 of 16

Notice: The information in this document is subject to change without notice

3/3.3/4.0 V µP Supervisor Circuits

ASM708 R/ S/ T/ J

October 2003

rev 1.0

Block Diagrams

Pin Configuration

RESET

RESET

MR

V

CC

PFI

PFO

GND

Generator

+

-

+

-

V

CC

20k

ASM708R/S/T/J

2.63V (ASM708R)

2.93V (ASM708S)

3.08V (ASM708T)

4.00V (ASM708J)

1.25V

+

RESET

Transition

Watchdog

Timebase

RESET

WDI

WDO

RESET

(RESET) ASM706P

MR

V

CC

PFI

PFO

GND

Detector

Timer

Generator

+

-

+

-

V

CC

20k

ASM706P/R/S/T/J

2.63V (ASM706P/R)

2.93V (ASM706S)

3.08V (ASM706T)

4.00V (ASM706J)

1.25V

+

MR

V

CC

GND

PFI

RESET

RESET

NC

PFO

1

2

3

4

5

6

7

8

MR

V

CC

GND

PFI

RESET

PFO

1

2

3

4

5

6

7

8

MR

V

CC

GND

PFI

RESET

NC

PFO

1

2

3

4

5

6

7

8

MR

V

CC

GND

PFI

RESET

PFO

1

2

3

4

5

6

7

8

WDI

WDO

WDO

WDI

WDO

WDI

MR

V

CC

GND

PFI

RESET

PFO

1

2

3

4

5

6

7

8

RESET

(RESET)

(ASM706P)

DIP/SO

MicroSO

ASM708R/S/

T

/J

ASM

706

P

ASM706R/S/T

/J

A

S

M

706P

ASM706R/S/

T

/J

ASM708R/

S

/T/

J

ASM706 P/ R/ S/ T/ J

3 of 16

Notice: The information in this document is subject to change without notice

3/3.3/4.0 V µP Supervisor Circuits

ASM708 R/ S/ T/ J

October 2003

rev 1.0

Pin Description

Pin Number

Name

Function

ASM706P

ASM706R/S/T/J

ASM708R/S/T/J

DIP/

SO

MicroSO

DIP/

SO

MicroSO

DIP/

SO

MicroSO

1

3

1

3

1

3

MR

Manual reset input. The active LOW input triggers

a reset pulse. It is pulled HIGH by a 20k

pull-up

resistor. It is compatible with TTL/CMOS signals

when V

CC

= 5V. It can be shorted to ground

through a mechanical switch. Leave folating or

connect to V

CC

if the function is not used.

2

4

2

4

2

4

V

CC

Monitored power supply input.

3

5

3

5

3

5

GND

Ground.

4

6

4

6

4

6

PFI

Power-fail input voltage monitor. With PFI less

than 1.25V, PFO goes LOW. Connect PFI to

Ground when not in use.

5

7

5

7

5

7

PFO

Power-fail output. The output is active LOW and

sinks current when PFI is less than 1.25V. If not

used, leave the pin unconnected.

6

8

6

8

-

-

WDI

Watchdog input. WDI controls the internal watch-

dog timer. A HIGH or LOW signal for 1.6sec at

WDI allows the internal timer to run-out, setting

WDO low. A rising or falling edge must occur at

WDI within 1.6 seconds or WDO goes LOW. The

watchdog function is disabled by floating WDI. The

internal watchdog timer clears when: RESET is

asserted; WDI is three-stated ; or WDI sees a ris-

ing or falling edge.

-

-

-

-

6

8

NC

Not Connected

-

-

7

1

7

1

RESET

Active LOW reset output. Pulses LOW for 200ms

when triggered, and stays LOW whenever V

CC

is

below the reset threshold. RESET remains LOW

for 200ms after V

CC

rises above the reset thresh-

old or MR goes from HIGH to LOW. A watchdog

timeout will not trigger RESET unless WDO is con-

nected to MR.

ASM706 P/ R/ S/ T/ J

4 of 16

Notice: The information in this document is subject to change without notice

3/3.3/4.0 V µP Supervisor Circuits

ASM708 R/ S/ T/ J

October 2003

rev 1.0

8

2

8

2

-

-

WDO

Watchdog output. WDO goes LOW when the 1.6

second interval watchdog timer times-out and

does not go HIGH until a transition occurs at WDI.

In addition, when V

CC

falls below the reset thresh-

old, WDO goes LOW. Unlike RESET, WDO does

not have a minimum pulse width and as soon as

V

CC

exceeds the reset threshold, WDO becomes

HIGH with no delay.

7

1

-

-

8

2

RESET

Active HIGH reset output. The inverse of RESET.

Pin Number

Name

Function

ASM706P

ASM706R/S/T/J

ASM708R/S/T/J

DIP/

SO

MicroSO

DIP/

SO

MicroSO

DIP/

SO

MicroSO

5 of 16

Notice: The information in this document is subject to change without notice

3/3.3/4.0 V µP Supervisor Circuits

ASM706 P/ R/ S/ T/ J

ASM708 R/ S/ T/ J

October 2003

rev 1.0

Detailed Descriptions

A proper reset input enables a microprocessor/

microcontroller to start in a known state. ASM706 P/ R/ S/ T/

J and ASM708 R/ S/ T/ J assert reset to prevent code

execution errors during power-up, power-down and brown-

out conditions.

RESET/RESET Operation

The RESET/RESET signals are designed to start or return a

µP/µC to a known state.

With V

CC

above 1.2V, RESET and RESET are guaranteed to

be asserted. During a power-up sequence, the reset outputs

remain asserted until the supply rises above the threshold

level. The resets are deasserted approximately 200ms after

crossing the threshold.

In a brownout situation where V

CC

falls below the threshold

level, the reset outputs are asserted. If a brownout occurs

during an already initiated reset period, the reset period will

extend for an additional reset period of 200ms.

The ASM708 devices have dual reset outputs, one active

LOW and one active HIGH. The ASM706P has a single

active HIGH reset and the ASM706/R/S/T/J devices have an

active LOW reset output.

Manual Reset (MR)

The active-LOW manual reset input is pulled high by an

internal 20k

pull-up resistor and can be driven low by

CMOS/TTL logic or a mechanical switch to ground. An

external debounce circuit is

unnecessary since the 140ms minimum reset time will

debounce mechanical pushbutton switches. The minimum

MR input pulse width is 0.5

µs with a 3V V

CC

input and 0.15

µs

with a 5V V

CC

input. If not used, tie MR to V

CC

or leave

floating.

By connecting the watchdog output (WDO) and MR, a

watchdog timeout forces a RESET to be generated.

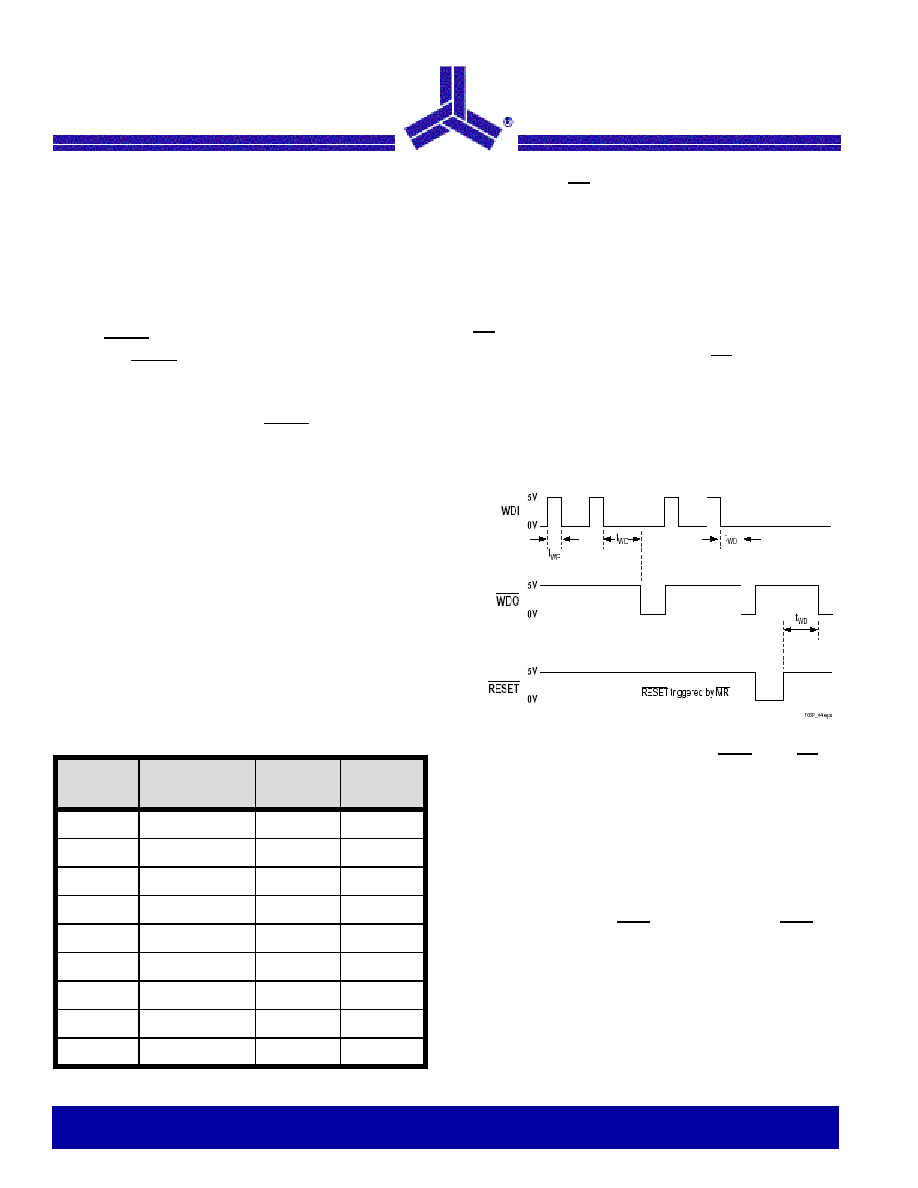

Watchdog Timer

A watchdog timer available on the ASM706P/R/S/T/J

monitors

µP/µC activity. An output line on the processor is

used to toggle the WDI line. If the line is not toggled within 1.6

seconds on the Watchdog Input (WDI), the internal timer puts

the Watchdog Output (WDO) into a LOW state. WDO will

remain LOW until a toggle is detected at WDI.

The watchdog function is disabled, meaning it is cleared and

not counting, if WDI is floated or connected to a three-stated

circuit. The watchdog timer is also disabled if RESET is

asserted. When RESET becomes inactive and the WDI input

sees a high or low transition as short as 100ns (V

CC

= 2.7V)/

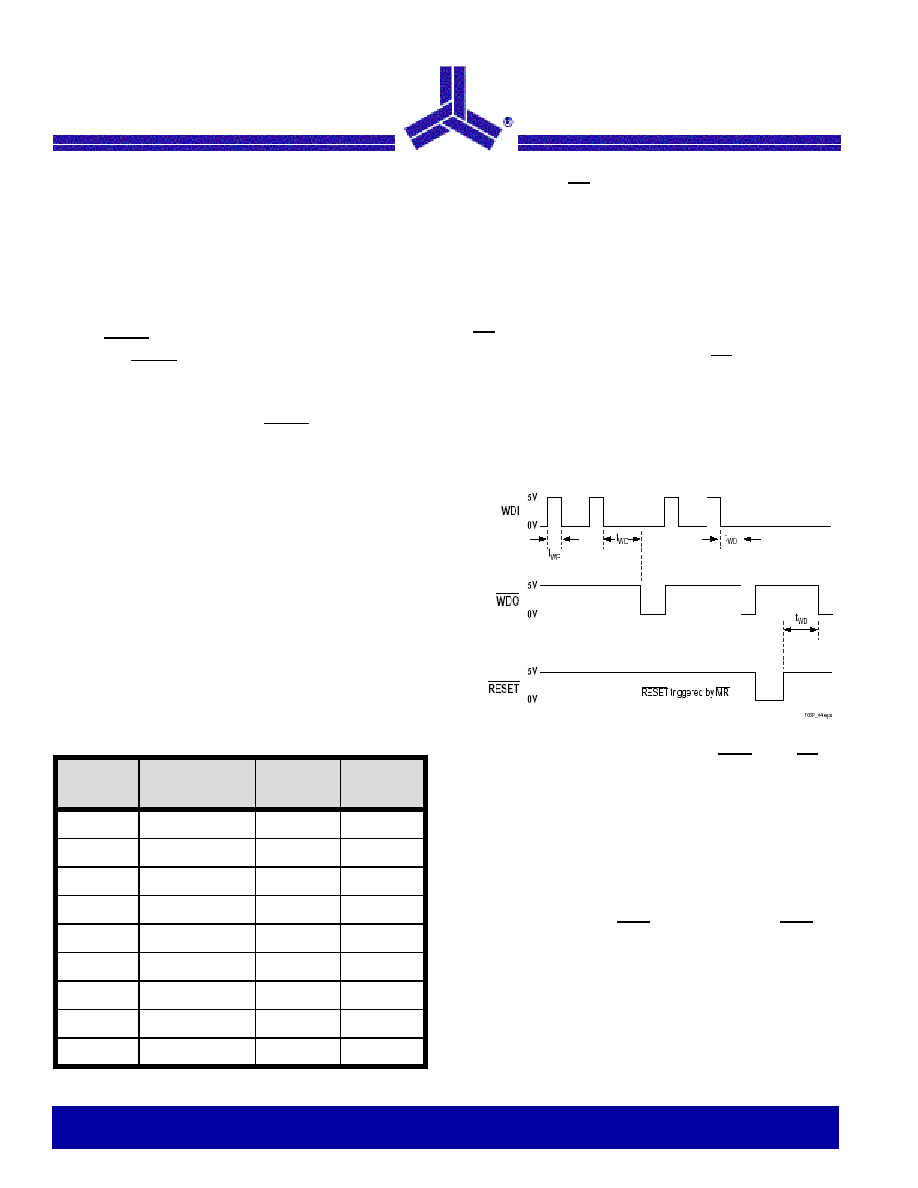

Alliance

Part #

RESET

Polarity

Threshold

Watchdog

Timer

ASM706P

HIGH

2.63V

YES

ASM706R

LOW

2.63V

YES

ASM706S

LOW

2.93V

YES

ASM706T

LOW

3.08V

YES

ASM706J

LOW

4.00V

YES

ASM708R

HIGH & LOW

2.63V

NO

ASM708S

HIGH & LOW

2.93V

NO

ASM708T

HIGH & LOW

3.08V

NO

ASM708J

HIGH & LOW

4.00V

NO

Figure 1: WDI Three-state operation