Æ

Altera Corporation

1

EP312 & EP324

Classic EPLDs

April 1995, ver. 1

Data Sheet

A-DS-312/324.01

Features

s

High-performance EPLDs with 12 macrocells (EP312) or 24

macrocells (EP324)

≠

Combinatorial speeds as fast as 25 ns

≠

Counter frequencies of up to 33.3 MHz

≠

Pipelined data rates of up to 66 MHz

s

Multiple 20-pin PAL and GAL replacement and integration

s

Device erasure and reprogramming with advanced, nonvolatile

EPROM configuration elements

s

Programmable registers providing D, T, JK, and SR flipflops with

individual Clear and Clock controls

s

Dual feedback on all macrocells for implementing buried registers

with bidirectional I/O

s

Programmable-

AND

/allocatable-

OR

structure allowing up to 16

product terms per macrocell

s

Two product terms on all macrocell control signals

s

Programmable inputs (8 in EP312, 10 in EP324) configurable as

latches, registers, or flow-through input

s

Available in windowed ceramic and one-time-programmable (OTP)

plastic packages with 24 to 44 pins:

≠

24-pin ceramic and plastic dual in-line package (CerDIP and

PDIP)

≠

28-pin plastic J-lead chip carrier (PLCC)

≠

40-pin CerDIP and PDIP

≠

44-pin PLCC

s

One global Clock pin; one global Input Latch Enable/Input

Clock/Input (

ILE

/

ICLK

/

INPUT

) pin

s

Programmable "standby" option for low-power operation

s

Programmable Security Bit for total protection of proprietary designs

s

100

%

generically testable to provide 100

%

programming yield

s

Software design support with the Altera PLDshell Plus software and

a wide range of third-party tools; programming support through

third-party vendors

General

Description

The CMOS EPROM EP312 and EP324 devices have a versatile macrocell

structure and I/O architecture, which allow them to implement high-

performance logic functions effectively. The EP312 and EP324 input and

macrocell features are a superset of features offered by PAL/GAL

devices. Therefore, EP312 and EP324 devices can be used as an alternative

to multiple PAL/GAL devices, SSI and MSI logic devices, or low-end gate

arrays.

2

Altera Corporation

EP312 & EP324 Classic EPLDs

EP312 and EP324 devices operate in high-performance systems with

low power consumption. The programmable standby function

provides "zero" power consumption for applications where

performance can be traded for power savings.

Functional

Description

The EP312 and EP324 architecture is based on a sum-of-products

programmable-

AND

/allocatable-

OR

structure. EP312 and EP324

devices can implement combinatorial and sequential logic functions,

as well as combinatorial-register and register-combinatorial-register

logic forms, to easily accommodate state machine designs.

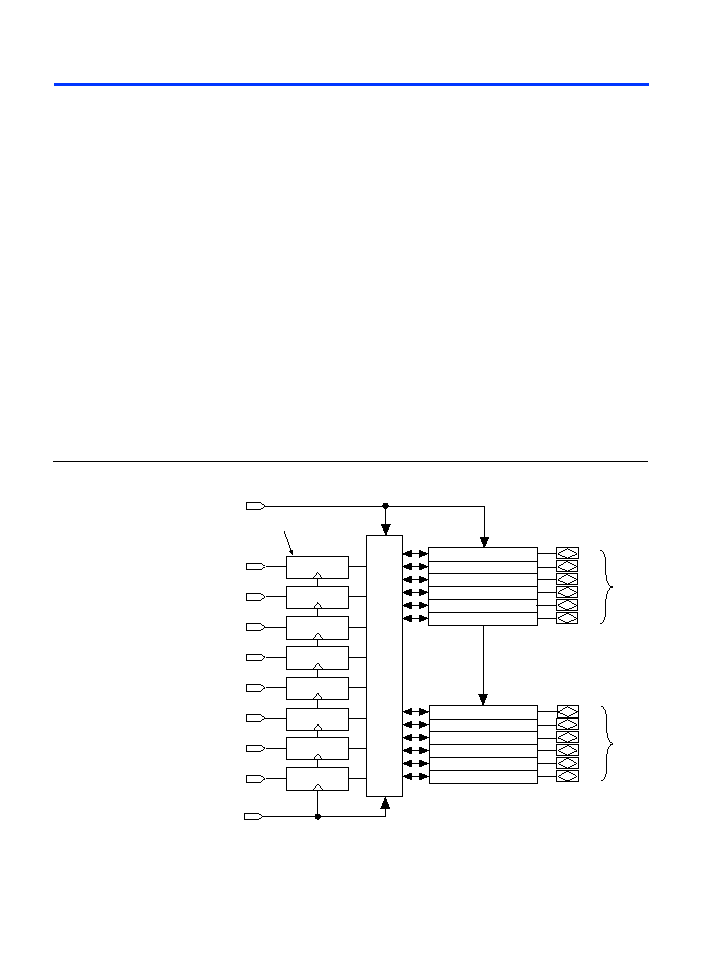

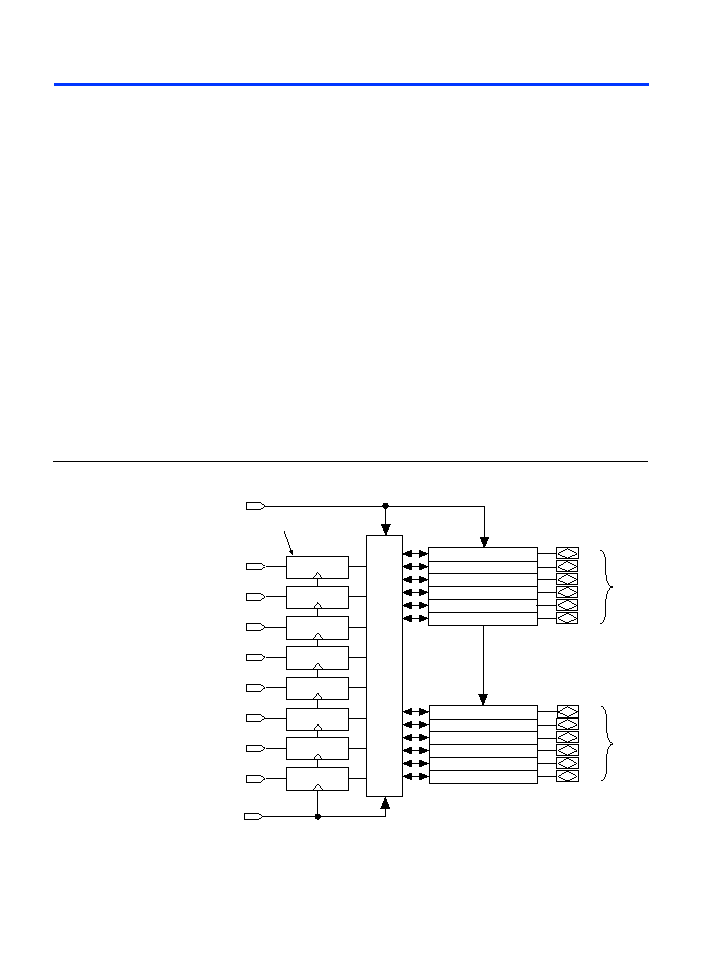

Figure 1

and

Figure 2

show block diagrams of the EP312 and EP324

architectures. The EP312 device contains 12 I/O macrocells and 8

programmable input structures; the EP324 device contains 24 I/O

macrocells and 10 programmable input structures. EP312 and EP324

macrocells are divided into 2 rings for product-term allocation. Both

devices have 2 additional inputs that can be programmed either as

combinatorial inputs or Clock inputs. Each input structure can be

individually configured as a latch, register, or flow-through input.

Input latches and registers can be clocked synchronously or

asynchronously.

Figure 1. EP312 Block Diagram

Input/Register/Latch

Ring 1

1

2

3

4

5

6

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Input Latch

Enable/Input

Clock/Input 2

Global Clock

Clock/Input 1

7

8

9

10

11

12

Macrocell 7

Macrocell 8

Macrocell 9

Macrocell 10

Macrocell 11

Macrocell 12

Global Clock

Global

Bus

Ring 2

Input 1

Input 2

Input 3

Input 4

Input 5

Input 6

Input 7

Input 8

Altera Corporation

3

EP312 & EP324 Classic EPLDs

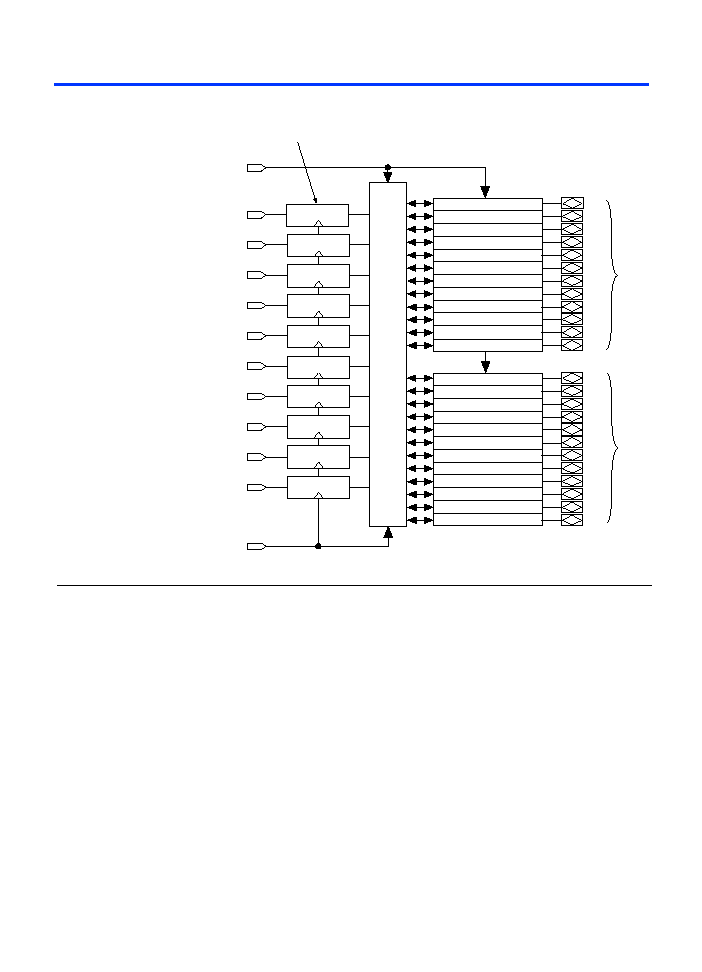

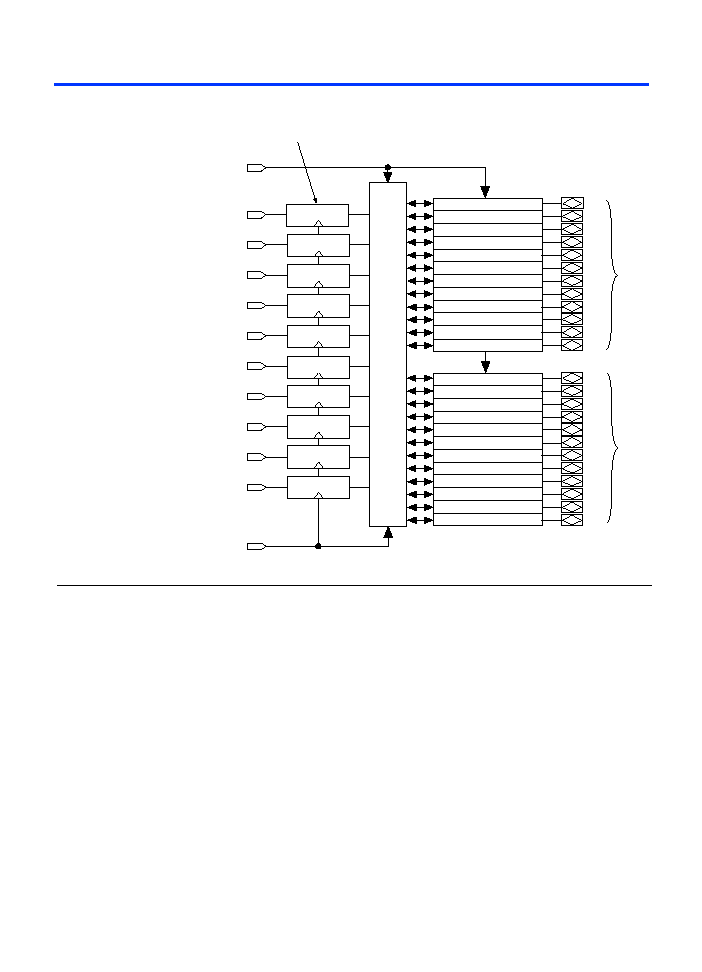

Figure 2. EP324 Block Diagram

The EP312 and EP324 architectures include the following features:

s

Macrocells

s

Product-term allocation

s

Programmable inputs

s

Power-on characteristics

Macrocells

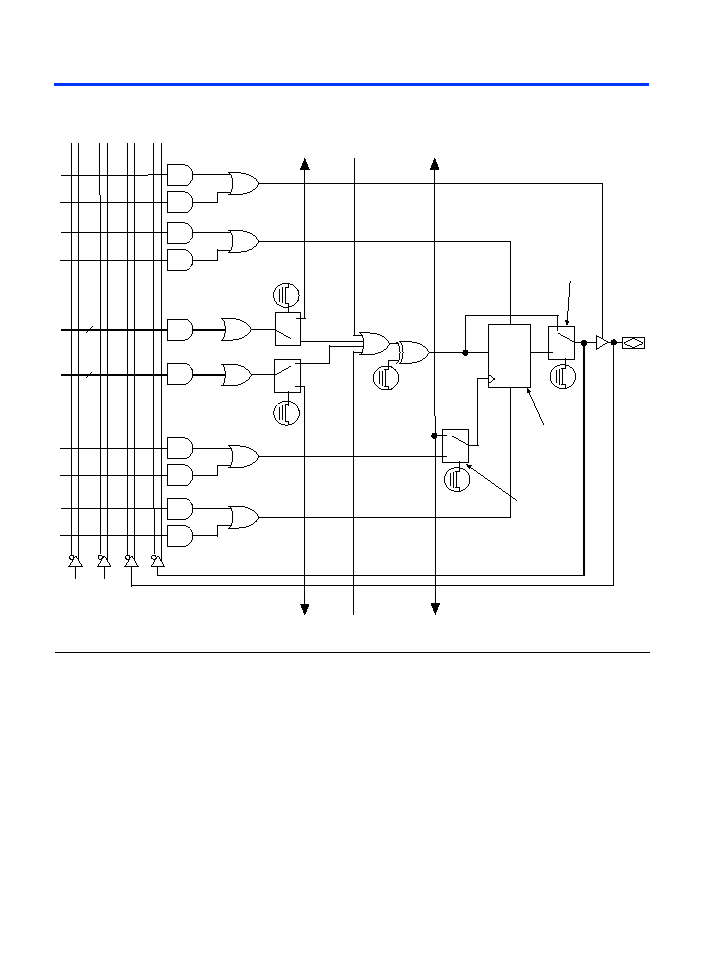

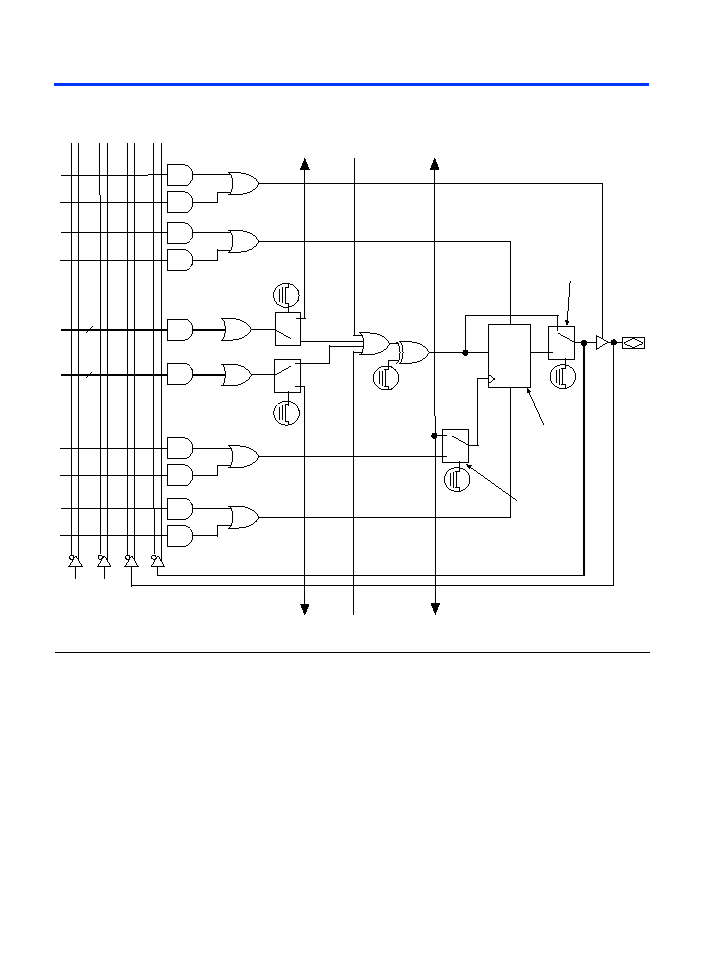

Each EP312 and EP324 macrocell contains 16 product terms (see

Figure 3

).

Half of the product terms are available to support logic functions; half are

dedicated to the macrocell control signals. The inputs to the

AND

array

originate from the true and complement signals of the programmable

input structure, the dedicated inputs, and the 2 feedback paths from each

I/O macrocell to the global bus.

Global

Bus

Input/Register/Latch

13

14

15

16

17

18

19

20

21

22

23

24

Macrocell 13

Macrocell 14

Macrocell 15

Macrocell 16

Macrocell 17

Macrocell 18

Macrocell 19

Macrocell 20

Macrocell 21

Macrocell 22

Macrocell 23

Macrocell 24

Global Clock

Clock/Input 1

Input Latch

Enable/Input

Clock/Input 2

Global Clock

Ring 2

1

2

3

4

5

6

7

8

9

10

11

12

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Macrocell 9

Macrocell 10

Macrocell 11

Macrocell 12

Ring 1

Input 1

Input 2

Input 3

Input 4

Input 5

Input 6

Input 7

Input 8

Input 9

Input 10

4

Altera Corporation

EP312 & EP324 Classic EPLDs

Figure 3. EP312 & EP324 Macrocell

The eight product terms available for implementing logic functions are

divided into two equal groups, and can be used in other macrocells. Each

macrocell provides a dual feedback to the logic array.

The eight product terms for control functions support the following four

control signals, with two product terms each: Output Enable (

OE

), Preset,

Clear, and asynchronous Clock. When the global Clock (

CLK

) signal

synchronously clocks a macrocell register, it cannot function as an input

to the logic array. However, the global Clock can simultaneously function

as an input to the logic array and as an asynchronous, non-global Clock.

Logic Array

to

Previous

Macrocell

from

Previous

Macrocell

Allocation

Control

Clock

Multiplexer

to Next

Macrocell

from Next

Macrocell

Programmable

Register

Output

Multiplexer

Lower Half

Product Terms 1 to 4

Upper Half

Product Terms 1 to 4

PRN

CLR

ILE/ICLK

Global

Clock

4

4

Output Enable

D/T

Q

Invert

Contro

l

Altera Corporation

5

EP312 & EP324 Classic EPLDs

To implement registered functions, each macrocell register can be

individually programmed for D, T, JK, or SR operation. If necessary, the

register can be bypassed for combinatorial operation. The

XOR

gate can

implement active-high or active-low logic, or use DeMorgan's inversion

to reduce the number of product terms required to implement a function.

Registers are cleared automatically during power-up.

The macrocell output can be fed back to the logic array via two paths. Pin

feedback that is connected after the output buffer can be used to

implement bidirectional I/O; if internal feedback is used for a buried

register or logic function, the pin feedback can be used as an input.

Product-Term Allocation

In EP312 and EP324 devices, product-term resources can be taken from

one macrocell and used in another. For product-term allocation,

macrocells in both the EP312 and EP324 are divided into 2 rings. The

EP312 has 6 macrocells per ring; the EP324 has 12 macrocells per ring.

Product terms from one macrocell can be allocated to adjacent macrocells

in the same ring. Product terms are allocated in groups of 4, and a

macrocell can borrow up to 8 product terms (4 from each adjacent

macrocell).

Table 1

and

Table 2

show the product-term allocation rings for the EP312

and EP324 devices, respectively. The Altera PLDshell Plus design

software automatically allocates product terms.