| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ARM1022E | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- ARM1022Eí

- Change history

- Contents

- List of Tables

- List of Figures

- Preface

- Introduction

- Integer Core

- System Control Coprocessor

- 3.1 About the system control coprocessor

- 3.2 Register descriptions

- 3.2.1 CP15 R0, device ID and cache type registers

- 3.2.2 CP15 R1, control register 1

- 3.2.3 CP15 R2, translation table base register

- 3.2.4 CP15 R3, domain access control register

- 3.2.5 CP15 R4

- 3.2.6 CP15 R5, fault status register

- 3.2.7 CP15 R6, fault address register

- 3.2.8 CP15 R7, index and VA cache operations registers

- 3.2.9 CP15 R8, TLB operations register

- 3.2.10 CP15 R9, cache lockdown register

- 3.2.11 CP15 R10, TLB lockdown register

- 3.2.12 CP15 R11

- 3.2.13 CP15 R12

- 3.2.14 CP15 R13, process ID and context ID registers

- 3.2.15 CP15 R14

- 3.2.16 CP15 R15

- Memory Management Units

- Caches and Write Buffer

- Prefetch Unit

- Bus Interface

- Coprocessor Interface

- JTAG Interface

- Debug

- Instruction Cycle Summary and Interlocks

- Design for Test

- Power Manager

- Clock Generator

- Signal Descriptions

- Glossary

- Index

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

ARM1022ETM

Technical Reference Manual

ii

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

ARM1022ETM

Technical Reference Manual

Copyright © 2001 ARM Limited. All rights reserved.

Release Information

Proprietary Notice

Words and logos marked with

Æ

or

TM

are registered trademarks or trademarks owned by ARM Limited, except

as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the

trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document

may be adapted or reproduced in any material form except with the prior written permission of the copyright

holder.

The product described in this document is subject to continuous developments and improvements. All

particulars of the product and its use contained in this document are given by ARM in good faith. However,

all warranties implied or expressed, including but not limited to implied warranties of merchantability, or

fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable

for any loss or damage arising from the use of any information in this document, or any error or omission in

such information, or any incorrect use of the product.

Confidentiality Status

This document is Open Access. This document has no restriction on distribution.

Product Status

The information in this document is Final (information on a developed product).

Web Address

http://www.arm.com

Change history

Date

Issue

Change

30 Nov, 2001

A

First release

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

iii

Contents

ARM1022E Technical Reference Manual

Preface

About this document .................................................................................. xviii

Feedback .................................................................................................... xxii

Chapter 1

Introduction

1.1

About the processor .................................................................................... 1-2

1.2

Programmer's model ................................................................................... 1-4

1.3

Components of the processor ..................................................................... 1-5

1.4

Instruction set summary ............................................................................ 1-10

Chapter 2

Integer Core

2.1

About the integer core ................................................................................. 2-2

2.2

Pipeline ....................................................................................................... 2-4

2.3

Prefetch unit ................................................................................................ 2-5

2.4

Typical operations ....................................................................................... 2-6

2.5

Load/store unit ............................................................................................ 2-9

2.6

Instruction progression .............................................................................. 2-10

Chapter 3

System Control Coprocessor

3.1

About the system control coprocessor ........................................................ 3-2

3.2

Register descriptions .................................................................................. 3-6

Contents

iv

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Chapter 4

Memory Management Units

4.1

About the MMUs ......................................................................................... 4-2

4.2

MMU software-accessible registers ............................................................ 4-3

4.3

Address translation ..................................................................................... 4-5

4.4

MMU memory access control ................................................................... 4-21

4.5

MMU cachable and bufferable information ............................................... 4-23

4.6

MMU and write buffer ............................................................................... 4-24

4.7

MMU aborts .............................................................................................. 4-25

4.8

MMU fault checking sequence ................................................................. 4-26

4.9

CPU aborts on MMU faults ....................................................................... 4-29

4.10

Fault priority .............................................................................................. 4-30

4.11

External aborts ......................................................................................... 4-31

4.12

Interaction of the MMU, caches, and write buffer ..................................... 4-33

4.13

Soft page table support ............................................................................ 4-34

Chapter 5

Caches and Write Buffer

5.1

About the caches and write buffer .............................................................. 5-2

5.2

ICache ........................................................................................................ 5-3

5.3

DCache and write buffer ............................................................................. 5-7

5.4

Cache coherence ..................................................................................... 5-16

5.5

Portability issues ....................................................................................... 5-18

Chapter 6

Prefetch Unit

6.1

About the prefetch unit ............................................................................... 6-2

6.2

Branch prediction activity ............................................................................ 6-3

6.3

Branch instruction cycle summary .............................................................. 6-6

6.4

Instruction memory barriers ........................................................................ 6-8

Chapter 7

Bus Interface

7.1

Bus features ............................................................................................... 7-2

7.2

AMBA AHB signals ..................................................................................... 7-3

7.3

Arbiter signals ............................................................................................. 7-6

7.4

AHB control signals .................................................................................... 7-7

7.5

Timing ......................................................................................................... 7-9

7.6

Bus interface ............................................................................................. 7-10

Chapter 8

Coprocessor Interface

8.1

About the coprocessor interface ................................................................. 8-2

8.2

Coprocessor interface signals .................................................................... 8-3

8.3

Design considerations ................................................................................ 8-5

8.4

Parallel execution ....................................................................................... 8-7

8.5

Rules for the interface ................................................................................ 8-8

8.6

Pipeline signal assertion ............................................................................. 8-9

8.7

Instruction issue ........................................................................................ 8-10

8.8

Hold signals .............................................................................................. 8-18

8.9

Instruction cancelation .............................................................................. 8-37

Contents

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

v

8.10

Bounced instructions ................................................................................. 8-44

8.11

Data buses ................................................................................................ 8-49

Chapter 9

JTAG Interface

9.1

JTAG interface and halt mode .................................................................... 9-2

9.2

JTAG instructions ........................................................................................ 9-4

9.3

Scan chain descriptions .............................................................................. 9-8

Chapter 10

Debug

10.1

About the debug unit ................................................................................. 10-2

10.2

Register descriptions ................................................................................ 10-5

10.3

Software lockout function ........................................................................ 10-15

10.4

Halt mode ................................................................................................ 10-16

10.5

Monitor mode .......................................................................................... 10-19

10.6

Values in the link register after aborts ..................................................... 10-20

10.7

Comms channel ...................................................................................... 10-21

Chapter 11

Instruction Cycle Summary and Interlocks

11.1

Cycle timing considerations ...................................................................... 11-2

11.2

Instruction cycle counts ............................................................................. 11-3

11.3

Interlocks ................................................................................................. 11-23

Chapter 12

Design for Test

12.1

Test modes and ports ............................................................................... 12-2

12.2

Scan chain configuration ........................................................................... 12-6

12.3

Clocks and clock gating ............................................................................ 12-8

12.4

Wrapper cells .......................................................................................... 12-11

12.5

Reset ....................................................................................................... 12-17

12.6

Memories ................................................................................................ 12-18

12.7

Memory BIST waveforms ........................................................................ 12-27

12.8

Cache upload/download, manufacturing test .......................................... 12-33

12.9

Test signal value tables .......................................................................... 12-39

Chapter 13

Power Manager

13.1

About the power manager ......................................................................... 13-2

13.2

ARM10 processor power modes ............................................................... 13-3

13.3

System control coprocessor ...................................................................... 13-8

13.4

Programming examples .......................................................................... 13-13

13.5

Power manager interface ........................................................................ 13-15

13.6

Timing ..................................................................................................... 13-16

13.7

Software example code sequences ........................................................ 13-20

Chapter 14

Clock Generator

14.1

Features .................................................................................................... 14-2

14.2

About the clock generator ......................................................................... 14-3

14.3

Interface description .................................................................................. 14-6

Contents

vi

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

14.4

Output clock behavior ............................................................................... 14-9

14.5

PLL configuration register ....................................................................... 14-11

Appendix A

Signal Descriptions

A.1

Global control signals ................................................................................. A-2

A.2

AHB signals in normal mode ...................................................................... A-3

A.3

PLL signals ................................................................................................. A-6

A.4

JTAG and TAP controller signals .............................................................. A-7

A.5

Debug signals ............................................................................................. A-8

A.6

Coprocessor signals ................................................................................... A-9

A.7

Design for test signals .............................................................................. A-11

A.8

ETM signals .............................................................................................. A-13

Glossary

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

vii

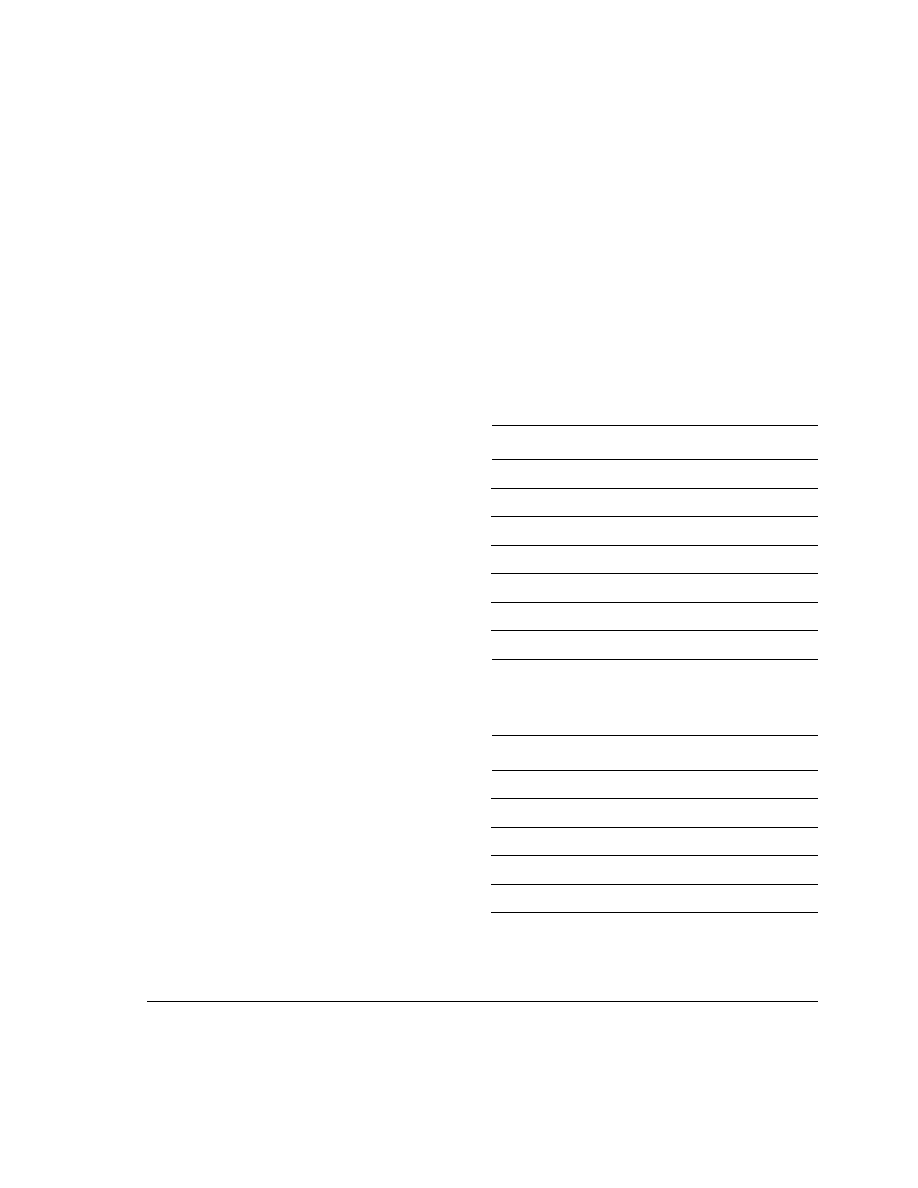

List of Tables

ARM1022E Technical Reference Manual

Change history .............................................................................................................. ii

Register notation conventions .................................................................................... xxi

Table 1-1

Key to instruction set table notation ........................................................................ 1-10

Table 1-2

ARM instruction summary ....................................................................................... 1-11

Table 1-3

Addressing mode 2 ................................................................................................. 1-14

Table 1-4

Addressing mode 2, privileged ................................................................................ 1-15

Table 1-5

Addressing mode 3 ................................................................................................. 1-16

Table 1-6

Addressing mode 4, load ........................................................................................ 1-17

Table 1-7

Addressing mode 4, store ....................................................................................... 1-17

Table 1-8

Addressing mode 5 ................................................................................................. 1-17

Table 1-9

Oprnd2 examples .................................................................................................... 1-18

Table 1-10

Suffixes to set fields ................................................................................................ 1-18

Table 1-11

Condition fields ........................................................................................................ 1-19

Table 1-12

Thumb instruction summary .................................................................................... 1-20

Table 3-1

CP15 register summary ............................................................................................ 3-4

Table 3-2

Address types ........................................................................................................... 3-5

Table 3-3

Device ID and cache type register instructions ......................................................... 3-7

Table 3-4

Encoding of the device ID register ............................................................................ 3-7

Table 3-5

Encoding of the cache type register .......................................................................... 3-8

Table 3-6

Control register 1 instructions ................................................................................... 3-9

Table 3-7

Encoding of control register 1 ................................................................................. 3-10

Table 3-8

Translation table base register instructions ............................................................. 3-12

Table 3-9

Domain access control register instructions ............................................................ 3-13

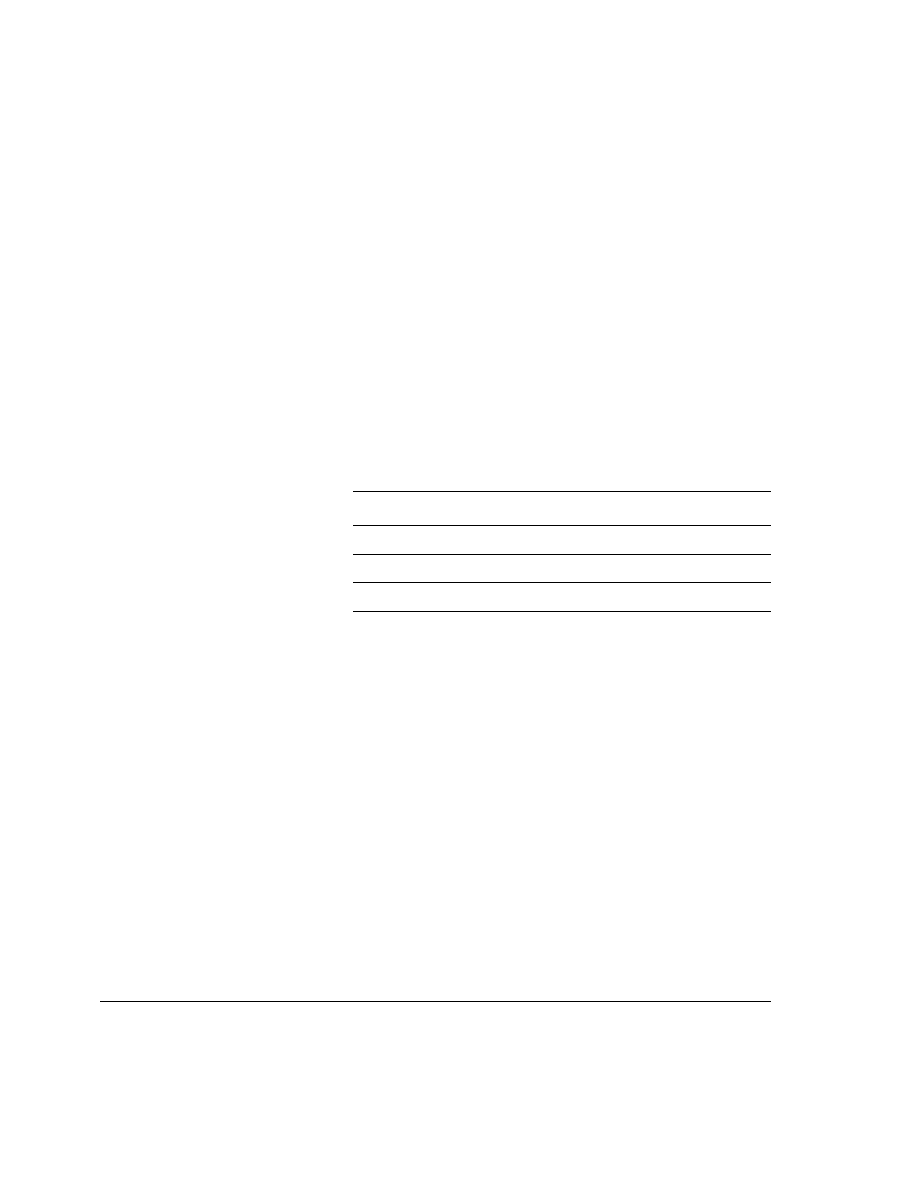

List of Tables

viii

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Table 3-10

Encoding of the domain access control register ..................................................... 3-13

Table 3-11

Fault status register instructions ............................................................................. 3-14

Table 3-12

Encoding of the fault status register ....................................................................... 3-14

Table 3-13

Priority of fault types ............................................................................................... 3-15

Table 3-14

Fault address register instructions .......................................................................... 3-16

Table 3-15

Cache operations register instructions ................................................................... 3-17

Table 3-16

Cache operation descriptions ................................................................................. 3-18

Table 3-17

Encoding of the index cache operations register .................................................... 3-19

Table 3-18

Encoding of the VA cache operations register ........................................................ 3-20

Table 3-19

TLB operations register instructions ....................................................................... 3-21

Table 3-20

Cache lockdown register instructions ..................................................................... 3-22

Table 3-21

TLB lockdown register instructions ......................................................................... 3-23

Table 3-22

Process ID and context ID register instructions ...................................................... 3-25

Table 3-23

PLL configuration register instructions .................................................................... 3-28

Table 3-24

Encoding of the PLL configuration register ............................................................. 3-28

Table 3-25

Power manager status instructions ......................................................................... 3-29

Table 3-26

Encoding of the power manager status register ..................................................... 3-29

Table 3-27

Encoding of the power manager receive data register ........................................... 3-30

Table 3-28

Encoding of the power manager transmit data register .......................................... 3-31

Table 3-29

Control register 2 instructions ................................................................................. 3-33

Table 3-30

Encoding of control register 2 ................................................................................. 3-33

Table 4-1

CP15 register MMU functions ................................................................................... 4-3

Table 4-2

Access types from level 1 descriptor ........................................................................ 4-9

Table 4-3

Access types from level 2 descriptor ...................................................................... 4-12

Table 4-4

Access types from level 2 descriptor ...................................................................... 4-17

Table 4-5

Domain access encoding ........................................................................................ 4-21

Table 4-6

S and R bit encoding .............................................................................................. 4-22

Table 4-7

C and B bit access control ...................................................................................... 4-23

Table 4-8

Priority encoding of MMU faults .............................................................................. 4-30

Table 4-9

First-access-only external abort .............................................................................. 4-31

Table 4-10

First-access and page-boundary external aborts ................................................... 4-31

Table 4-11

First-access and last-access external aborts .......................................................... 4-32

Table 4-12

Encoding of instruction TLB bit fields ...................................................................... 4-35

Table 4-13

Protected RAM bit field values ................................................................................ 4-36

Table 4-14

TLB physical address bit fields and meanings ........................................................ 4-37

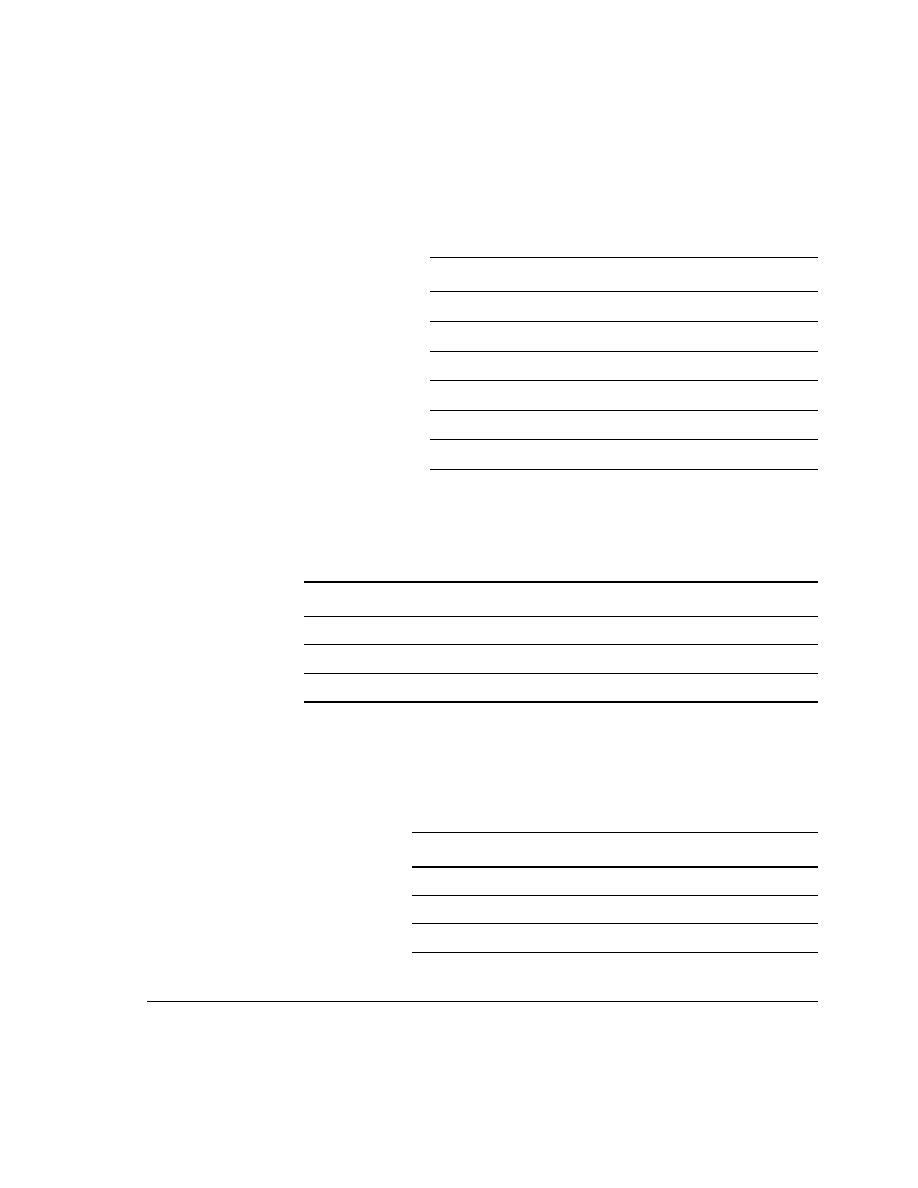

Table 5-1

Selection of cachable instructions ............................................................................ 5-5

Table 5-2

Selection of cachable and bufferable data .............................................................. 5-10

Table 6-1

Penalty for an erroneously predicted branch ............................................................ 6-4

Table 6-2

ARM and Thumb branch instruction cycle counts .................................................... 6-6

Table 7-1

AMBA AHB signals ................................................................................................... 7-3

Table 7-2

Arbiter signals ........................................................................................................... 7-6

Table 7-3

Transfer sizes ........................................................................................................... 7-7

Table 7-4

BURST lengths ......................................................................................................... 7-8

Table 7-5

Transfer attributes ..................................................................................................... 7-8

Table 7-6

Blocking and nonblocking request types ................................................................ 7-10

Table 7-7

Typical bus interface request sizes ......................................................................... 7-11

Table 7-8

Cachable and bufferable bits in buffered writes ...................................................... 7-14

List of Tables

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

ix

Table 8-1

Pipeline stages and active signals ............................................................................ 8-9

Table 8-2

CPINSTR interactions with other signals ................................................................ 8-11

Table 8-3

CPINSTRV interactions with other signals .............................................................. 8-12

Table 8-4

CPVALIDD interactions with other signals .............................................................. 8-14

Table 8-5

CPLSLEN interactions with other signals ................................................................ 8-16

Table 8-6

CPLSSWP interactions with other signals .............................................................. 8-17

Table 8-7

CPLSDBL interactions with other signals ................................................................ 8-17

Table 8-8

Hold signals summary ............................................................................................. 8-19

Table 8-9

ASTOPCPD interactions with other signals ............................................................ 8-20

Table 8-10

ASTOPCPE interactions with other signals ............................................................ 8-22

Table 8-11

LSHOLDCPE interactions with other signals .......................................................... 8-24

Table 8-12

LSHOLDCPM interactions with other signals .......................................................... 8-26

Table 8-13

CPBUSYE interactions with other signals ............................................................... 8-28

Table 8-14

CPLSBUSY interactions with other signals ............................................................. 8-36

Table 8-15

ACANCELCP interactions with other signals .......................................................... 8-37

Table 8-16

AFLUSHCP interactions with other signals ............................................................. 8-41

Table 8-17

CPBOUNCEE interactions with other signals ......................................................... 8-45

Table 8-18

STCMRCDATA interactions with signals ................................................................ 8-49

Table 8-19

LDCMRCDATA interactions with signals ................................................................ 8-50

Table 9-1

Defined public JTAG instructions .............................................................................. 9-4

Table 9-2

Method of debug entry bit values ............................................................................ 9-11

Table 9-3

DSCR bits from the core ......................................................................................... 9-14

Table 10-1

CP14 registers and scan chain numbers ................................................................ 10-3

Table 10-2

Debug ID register instructions ................................................................................. 10-5

Table 10-3

Encoding of the debug ID register ........................................................................... 10-6

Table 10-4

Debug status and control register instructions ........................................................ 10-6

Table 10-5

Encoding of debug status and control register ........................................................ 10-7

Table 10-6

Data transfer register instructions ........................................................................... 10-8

Table 10-7

Breakpoint address register instructions ................................................................. 10-9

Table 10-8

Breakpoint control register instructions ................................................................. 10-10

Table 10-9

Encoding of breakpoint control registers ............................................................... 10-11

Table 10-10

Watchpoint address register instructions .............................................................. 10-12

Table 10-11

Watchpoint control register instructions ................................................................ 10-13

Table 10-12

Encoding of watchpoint control registers .............................................................. 10-13

Table 10-13

Values in the link register after exceptions ............................................................ 10-20

Table 10-14

Value in the link register after a watchpoint .......................................................... 10-20

Table 11-1

Subcategories of data processing instructions ........................................................ 11-5

Table 11-2

Cycle counts of data processing instructions .......................................................... 11-5

Table 11-3

Cycle counts of multiply instructions ....................................................................... 11-7

Table 11-4

Cycle counts of branch instructions ........................................................................ 11-8

Table 11-5

Cycle counts of MRS and MSR instructions ........................................................... 11-9

Table 11-6

Cycle counts of load instructions ........................................................................... 11-10

Table 11-7

Cycle counts of store instructions ......................................................................... 11-12

Table 11-8

Cycle counts of load multiple and store multiple instructions ................................ 11-14

Table 11-9

Cycle counts of preload instructions ..................................................................... 11-15

Table 11-10

Cycle counts of coprocessor instructions .............................................................. 11-16

Table 11-11

Cycle counts of swap instructions ......................................................................... 11-17

List of Tables

x

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Table 11-12

Cycle counts of Thumb data processing instructions ........................................... 11-17

Table 11-13

Cycle count of the Thumb multiply instruction ...................................................... 11-19

Table 11-14

Cycle counts of Thumb branch instructions .......................................................... 11-20

Table 11-15

Cycle counts of Thumb store instruction ............................................................... 11-21

Table 11-16

Cycle counts of Thumb load instructions .............................................................. 11-21

Table 11-17

Cycle counts of Thumb load/store multiple instructions ........................................ 11-22

Table 12-1

ATPG mode selection ............................................................................................. 12-2

Table 12-2

Test port signals ..................................................................................................... 12-3

Table 12-3

Cache upload signal constraints ............................................................................. 12-4

Table 12-4

Test port wrapper signals ....................................................................................... 12-4

Table 12-5

Scan chain configurations ....................................................................................... 12-6

Table 12-6

Wrapper scan chain configurations ........................................................................ 12-6

Table 12-7

Scan chain clocks ................................................................................................... 12-8

Table 12-8

Test pin configuration for upload, download, and BIST ........................................ 12-18

Table 12-9

Encoding of BIST instruction fields ....................................................................... 12-20

Table 12-10

Encoding of BIST engine control field ................................................................... 12-20

Table 12-11

Encoding of BIST block under test field ................................................................ 12-21

Table 12-12

Encoding of BIST data word field ......................................................................... 12-21

Table 12-13

Encoding of BIST pattern field .............................................................................. 12-21

Table 12-14

BIST pattern terms and definitions ....................................................................... 12-22

Table 12-15

A1020SCANOUT[15:0] mapping .......................................................................... 12-24

Table 12-16

Failure address formulas ...................................................................................... 12-25

Table 12-17

Instruction fields for reset followed by BIST test ................................................... 12-28

Table 12-18

Instruction fields for test completion followed by new test .................................... 12-30

Table 12-19

Instruction fields for cache download .................................................................... 12-36

Table 12-20

Test signals for ATPG testing ............................................................................... 12-39

Table 12-21

Test signals in functional mode ............................................................................ 12-40

Table 12-22

Test signals during BIST testing ........................................................................... 12-40

Table 12-23

Test signals in cache upload mode ...................................................................... 12-41

Table 12-24

Test signals in external test wrapper mode with one wrapper chain .................... 12-43

Table 12-25

Test signals in external test wrapper mode with three wrapper chains ................ 12-44

Table 13-1

ARM10 processor power modes ............................................................................ 13-3

Table 13-2

Power mode VDD states ........................................................................................ 13-5

Table 13-3

Reentering RUN mode ........................................................................................... 13-6

Table 13-4

PMSR bit fields ....................................................................................................... 13-8

Table 13-5

PMRDR bit fields .................................................................................................... 13-9

Table 13-6

PMTDR bit fields ................................................................................................... 13-10

Table 13-7

Power manager/processor interface signals ......................................................... 13-15

Table 14-1

GCLK/HCLK frequencies with XTAL1 = 20MHz ..................................................... 14-4

Table 14-2

Test mode programming ......................................................................................... 14-6

Table 14-3

GCLK and HCLK behavior .................................................................................... 14-10

Table A-1

Global control signals ............................................................................................... A-2

Table A-2

AHB signals .............................................................................................................. A-3

Table A-3

Arbiter signals ........................................................................................................... A-5

Table A-4

PLL signals ............................................................................................................... A-6

Table A-5

TAP controller signals ............................................................................................... A-7

Table A-6

JTAG signals ............................................................................................................ A-7

List of Tables

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

xi

Table A-7

Debug signals ........................................................................................................... A-8

Table A-8

Coprocessor signals .................................................................................................. A-9

Table A-9

Design for test signals ............................................................................................. A-11

Table A-10

ETM10 signals ........................................................................................................ A-13

List of Tables

xii

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

xiii

List of Figures

ARM1022E Technical Reference Manual

Key to timing diagram conventions ............................................................................. xx

Figure 1-1

ARM1022E processor block diagram ........................................................................ 1-6

Figure 2-1

Integer core components .......................................................................................... 2-3

Figure 2-2

Pipeline stages of a typical operation ........................................................................ 2-6

Figure 2-3

Pipeline stages of a typical ALU operation ................................................................ 2-7

Figure 2-4

Pipeline stages of a typical multiply operation .......................................................... 2-8

Figure 2-5

Pipeline stages of a load or store operation ............................................................ 2-10

Figure 2-6

Pipeline stages of a load multiple or store multiple operation ................................. 2-11

Figure 2-7

Pipeline stages of an LDR operation that misses ................................................... 2-12

Figure 3-1

CP15 MCR instruction format ................................................................................... 3-3

Figure 3-2

CP15 MRC instruction format ................................................................................... 3-3

Figure 3-3

Device ID register ...................................................................................................... 3-7

Figure 3-4

Cache type register ................................................................................................... 3-8

Figure 3-5

Control register 1 ..................................................................................................... 3-10

Figure 3-6

Translation table base register ................................................................................ 3-12

Figure 3-7

Domain access control register ............................................................................... 3-13

Figure 3-8

Fault status register ................................................................................................. 3-14

Figure 3-9

Fault address register ............................................................................................. 3-16

Figure 3-10

Index cache operations register .............................................................................. 3-18

Figure 3-11

VA cache operations register .................................................................................. 3-20

Figure 3-12

TLB operations register ........................................................................................... 3-21

Figure 3-13

Cache lockdown register ......................................................................................... 3-22

Figure 3-14

TLB lockdown register ............................................................................................. 3-24

List of Figures

xiv

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Figure 3-15

Process ID register ................................................................................................. 3-25

Figure 3-16

Context ID register .................................................................................................. 3-25

Figure 3-17

Address mapping using CP15 R13 ......................................................................... 3-26

Figure 3-18

PLL configuration register ....................................................................................... 3-28

Figure 3-19

Power manager status register ............................................................................... 3-29

Figure 3-20

Power manager receive data register ..................................................................... 3-30

Figure 3-21

Power manager transmit data register .................................................................... 3-31

Figure 3-22

Control register 2 .................................................................................................... 3-33

Figure 4-1

Translating pages and section addresses ................................................................ 4-7

Figure 4-2

Translating a level 1 descriptor address ................................................................... 4-8

Figure 4-3

Level 1 descriptor formats ........................................................................................ 4-9

Figure 4-4

Translating a section address ................................................................................. 4-10

Figure 4-5

Level 2 descriptor formats ...................................................................................... 4-11

Figure 4-6

Translating a coarse page table address ................................................................ 4-12

Figure 4-7

Translating a large page or subpage address from a coarse page table ............... 4-14

Figure 4-8

Translating a small page or subpage address from a coarse page table ............... 4-15

Figure 4-9

Translating a fine page table address ..................................................................... 4-16

Figure 4-10

Translating a large page or subpage address from a fine page table .................... 4-18

Figure 4-11

Translating a small page or subpage address from a fine page table .................... 4-19

Figure 4-12

Translating a tiny page address .............................................................................. 4-20

Figure 4-13

Fault checking flowchart ......................................................................................... 4-27

Figure 4-14

Instruction TLB bit fields ......................................................................................... 4-34

Figure 4-15

Protected RAM bit fields ......................................................................................... 4-35

Figure 4-16

Physical address RAM bit fields ............................................................................. 4-36

Figure 7-1

Arbiter-bus interface connections ............................................................................. 7-6

Figure 7-2

Bus interface block diagram ................................................................................... 7-12

Figure 7-3

Write buffer and castout buffer ............................................................................... 7-13

Figure 8-1

ARM10 and CP pipeline stages ................................................................................ 8-2

Figure 8-2

Instruction issue example ....................................................................................... 8-15

Figure 8-3

ASTOPCPD example ............................................................................................. 8-21

Figure 8-4

ASTOPCPE example .............................................................................................. 8-23

Figure 8-5

LSHOLDCPE example ........................................................................................... 8-25

Figure 8-6

LSHOLDCPM example ........................................................................................... 8-27

Figure 8-7

CPBUSYE example ................................................................................................ 8-29

Figure 8-8

CPBUSYE ignored due to ASTOPCPD assertion .................................................. 8-30

Figure 8-9

CPBUSYE asserted before ASTOPCPD ................................................................ 8-30

Figure 8-10

ASTOPCPD with CPBUSYE .................................................................................. 8-31

Figure 8-11

CPBUSYE ignored due to ASTOPCPE assertion .................................................. 8-32

Figure 8-12

CPBUSYE asserted before ASTOPCPE ................................................................ 8-32

Figure 8-13

I2 held up by ASTOPCPE and CPBUSYE ............................................................. 8-33

Figure 8-14

I1 held up by ASTOPCPE and I2 held up by CPBUSYE ........................................ 8-34

Figure 8-15

I1 held up by CPBUSYE and I2 held up by ASTOPCPD ........................................ 8-35

Figure 8-16

ACANCELCP example ........................................................................................... 8-38

Figure 8-17

ACANCELCP with ASTOPCPE example ............................................................... 8-39

Figure 8-18

ACANCELCP with CPBUSYE example .................................................................. 8-40

Figure 8-19

AFLUSHCP example .............................................................................................. 8-43

Figure 8-20

CPBOUNCEE example .......................................................................................... 8-46

List of Figures

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

xv

Figure 8-21

CPBOUNCEE with ASTOPCPE example ............................................................... 8-47

Figure 8-22

CPBOUNCEE with CPBUSYE example ................................................................. 8-48

Figure 9-1

JTAG TAP state machine diagram ............................................................................ 9-2

Figure 9-2

TAP ID register .......................................................................................................... 9-9

Figure 9-3

Scan chain 2 ........................................................................................................... 9-15

Figure 10-1

Debug ID register .................................................................................................... 10-5

Figure 10-2

Debug status and control register ........................................................................... 10-6

Figure 10-3

Data transfer register .............................................................................................. 10-9

Figure 10-4

Breakpoint address registers ................................................................................ 10-10

Figure 10-5

Breakpoint control registers .................................................................................. 10-11

Figure 10-6

Watchpoint address registers ................................................................................ 10-12

Figure 10-7

Watchpoint control registers .................................................................................. 10-13

Figure 10-8

Comms channel output ......................................................................................... 10-22

Figure 11-1

Pipeline forwarding paths ...................................................................................... 11-24

Figure 12-1

Production scan mode clocking .............................................................................. 12-9

Figure 12-2

Clocking in serial core test mode .......................................................................... 12-10

Figure 12-3

Dedicated input and output wrapper cells ............................................................. 12-12

Figure 12-4

Reset dedicated wrapper cell ................................................................................ 12-13

Figure 12-5

HRESET and SFRESET wrapper cell ................................................................... 12-14

Figure 12-6

Shared wrapper cells ............................................................................................ 12-15

Figure 12-7

HCLK domain wrapper chain isolation .................................................................. 12-16

Figure 12-8

Reset followed by BIST test .................................................................................. 12-27

Figure 12-9

Test completion followed by a new test ................................................................ 12-29

Figure 12-10

Setting a real time failure flag ................................................................................ 12-31

Figure 12-11

Completion of pattern fail test ............................................................................... 12-32

Figure 12-12

Cache upload test execution ................................................................................. 12-35

Figure 12-13

Execution of cache download start ....................................................................... 12-37

Figure 12-14

Execution of binary test download ........................................................................ 12-38

Figure 13-1

Power manager state diagram ................................................................................ 13-4

Figure 13-2

Power manager status register ............................................................................... 13-8

Figure 13-3

Power manager receive data register ..................................................................... 13-9

Figure 13-4

Power manager transmit data register .................................................................. 13-10

Figure 13-5

CPU transmit request timing ................................................................................. 13-16

Figure 13-6

CPU transmit request timing with emulation bit set ............................................... 13-17

Figure 13-7

CPU previous state request timing ........................................................................ 13-17

Figure 13-8

CPU previous state request timing with emulation bit set ..................................... 13-18

Figure 13-9

Hard reset timing ................................................................................................... 13-18

Figure 13-10

Soft reset from power-down timing ....................................................................... 13-19

Figure 14-1

Clock generator block diagram ............................................................................... 14-3

Figure 14-2

PLL configuration register ..................................................................................... 14-11

List of Figures

xvi

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

xvii

Preface

This preface is an introduction to this document and other related documents. It contains

the following sections:

∑

About this document on page xviii

∑

Feedback on page xxii.

Preface

xviii

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

About this document

This is the technical reference manual for the ARM1022E processor.

Intended audience

This document is written to help designers develop systems around the ARM1022E

processor.

Using this document

This document is organized into the following chapters:

Chapter 1 Introduction

Read this chapter to learn about the components of the ARM10 processor

and about the ARM and Thumb instruction sets.

Chapter 2 Integer Core

Read this chapter to learn how the integer core pipeline achieves a

throughput approaching one instruction per cycle.

Chapter 3 System Control Coprocessor

Read this chapter to learn how to use CP15, the system control

coprocessor.

Chapter 4 Memory Management Units

Read this chapter to learn how to use the address translation process of

the memory management units.

Chapter 5 Caches and Write Buffer

Read this chapter to learn how to use CP15 to control operation of the

instruction and data caches, the write buffer, and the hit-under-miss

buffer.

Chapter 6 Prefetch Unit

Read this chapter to learn how the ARM10 processor prefetches and

buffers instructions, and how to implement an instruction memory barrier

to flush the prefetch buffer.

Chapter 7 Bus Interface

Read this chapter to learn how to use the bus interface to AMBATM.

Preface

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

xix

Chapter 8 Coprocessor Interface

Read this chapter to learn how to integrate one or more coprocessors with

the ARM10 processor.

Chapter 9 JTAG Interface

Read this chapter to learn how to use the built-in JTAG debug hardware.

Chapter 10 Debug

Read this chapter to learn how to use coprocessor 14 to debug application

software, operating systems, and hardware systems.

Chapter 11 Instruction Cycle Summary and Interlocks

Read this chapter to learn about the cycle counts of ARM and Thumb

instructions and how pipeline interlocks resolve data dependencies.

Chapter 12 Design for Test

Read this chapter to learn how to use the built-in scan chains, wrapper

cells, and memory BIST to test the ARM10 processor.

Chapter 13 Power Manager

Read this chapter to learn how to use the power manager to control

system power modes.

Chapter 14 Clock Generator

Read this chapter to learn how to synthesize the two programmable

system clocks.

Appendix A Signal Descriptions

Refer to this appendix for a summary of ARM10 signal descriptions.

Typographical conventions

The following typographical conventions are used in this book:

italic

Introduces special terminology. Also denotes cross-references.

bold

Denotes signal names. Also used for terms in descriptive lists,

where appropriate.

monospace

Denotes text that can be entered at the keyboard, such as

commands, file and program names, and source code.

Preface

xx

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

monospace

Denotes a permitted abbreviation for a command or option. The

underlined text can be entered instead of the full command or

option name.

monospace

italic

Denotes arguments to commands and functions where the

argument is to be replaced by a specific value.

monospace

bold

Denotes language keywords when used outside example code.

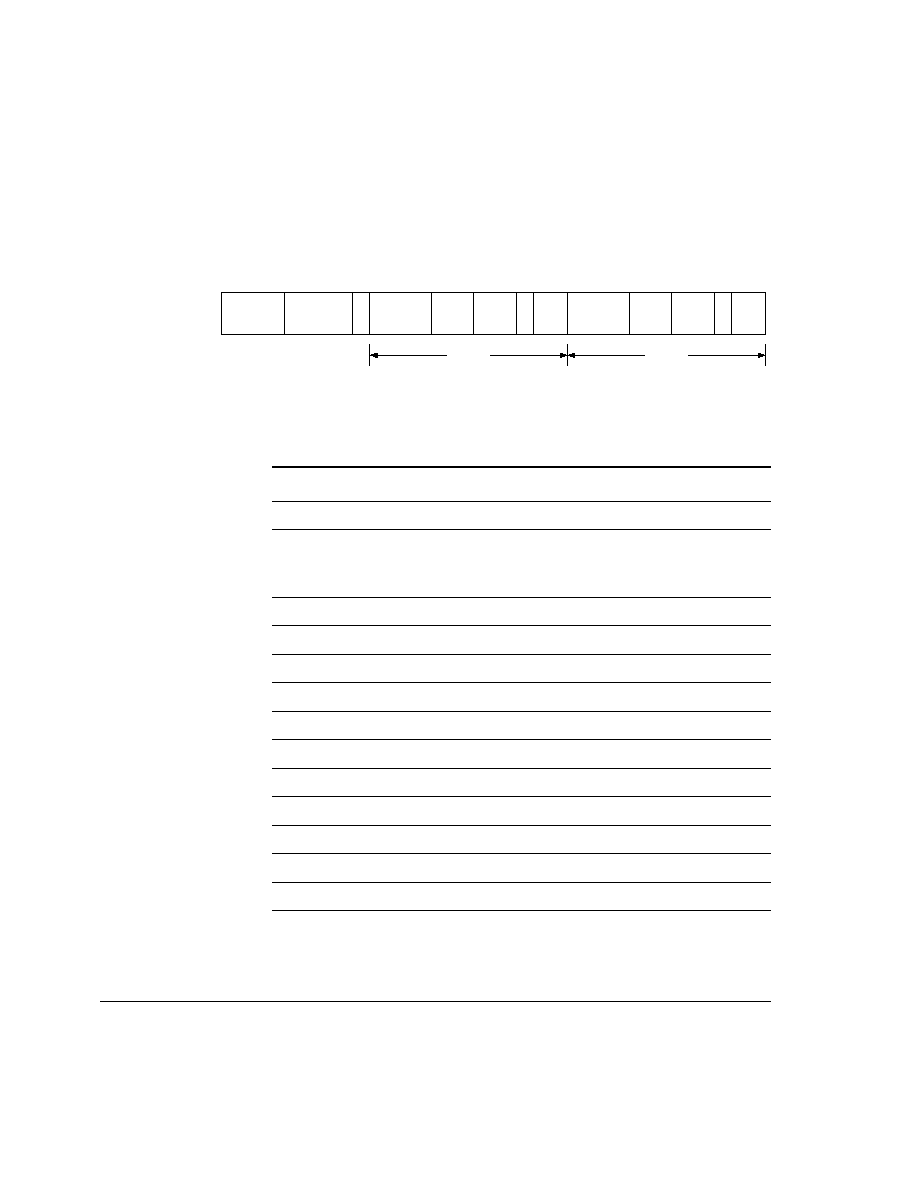

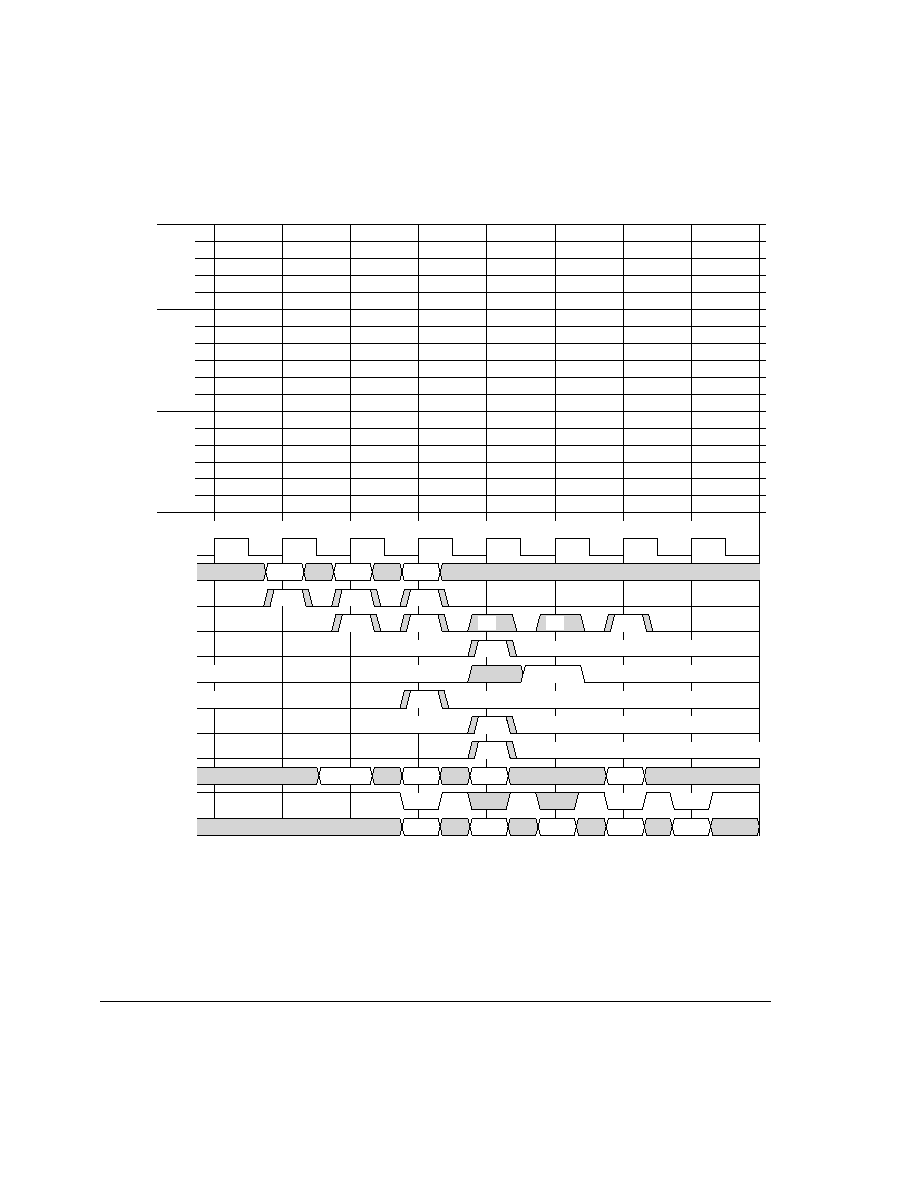

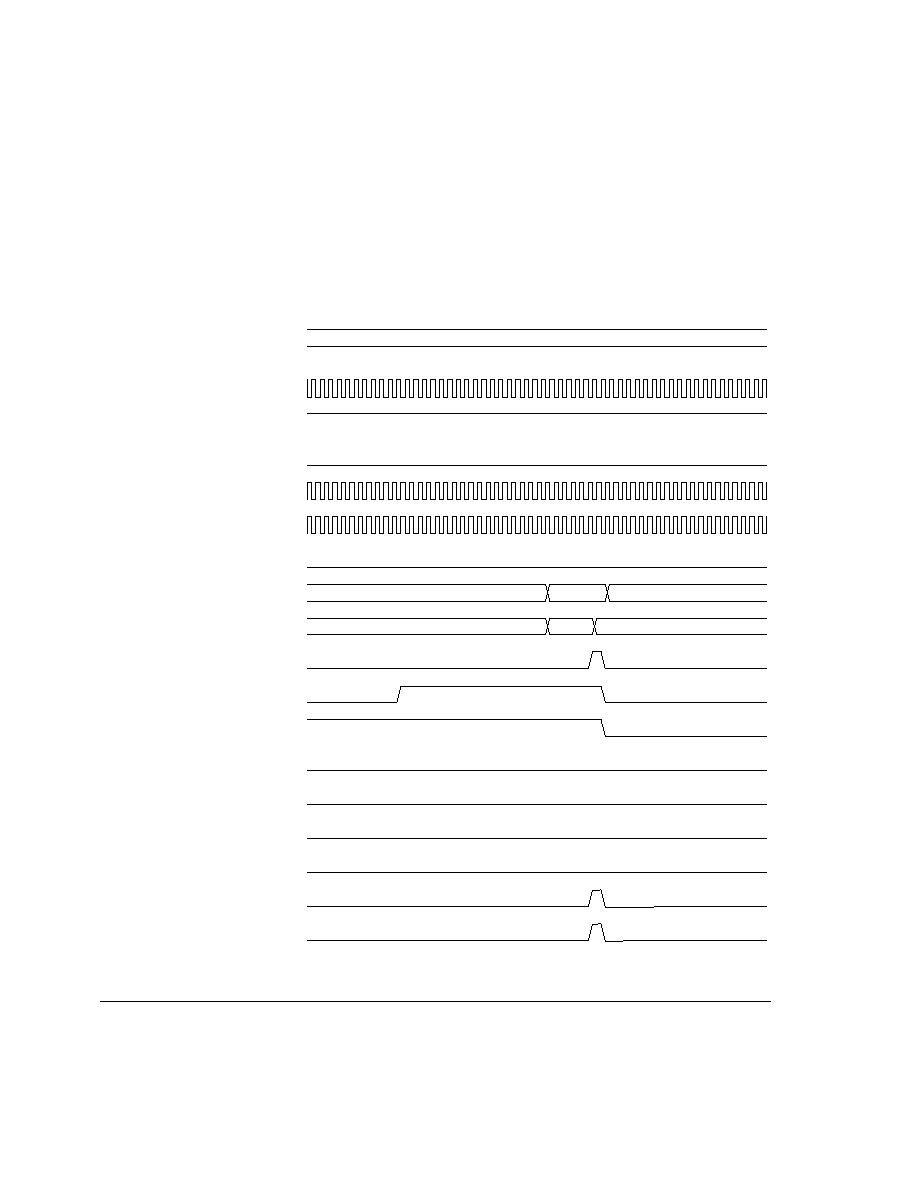

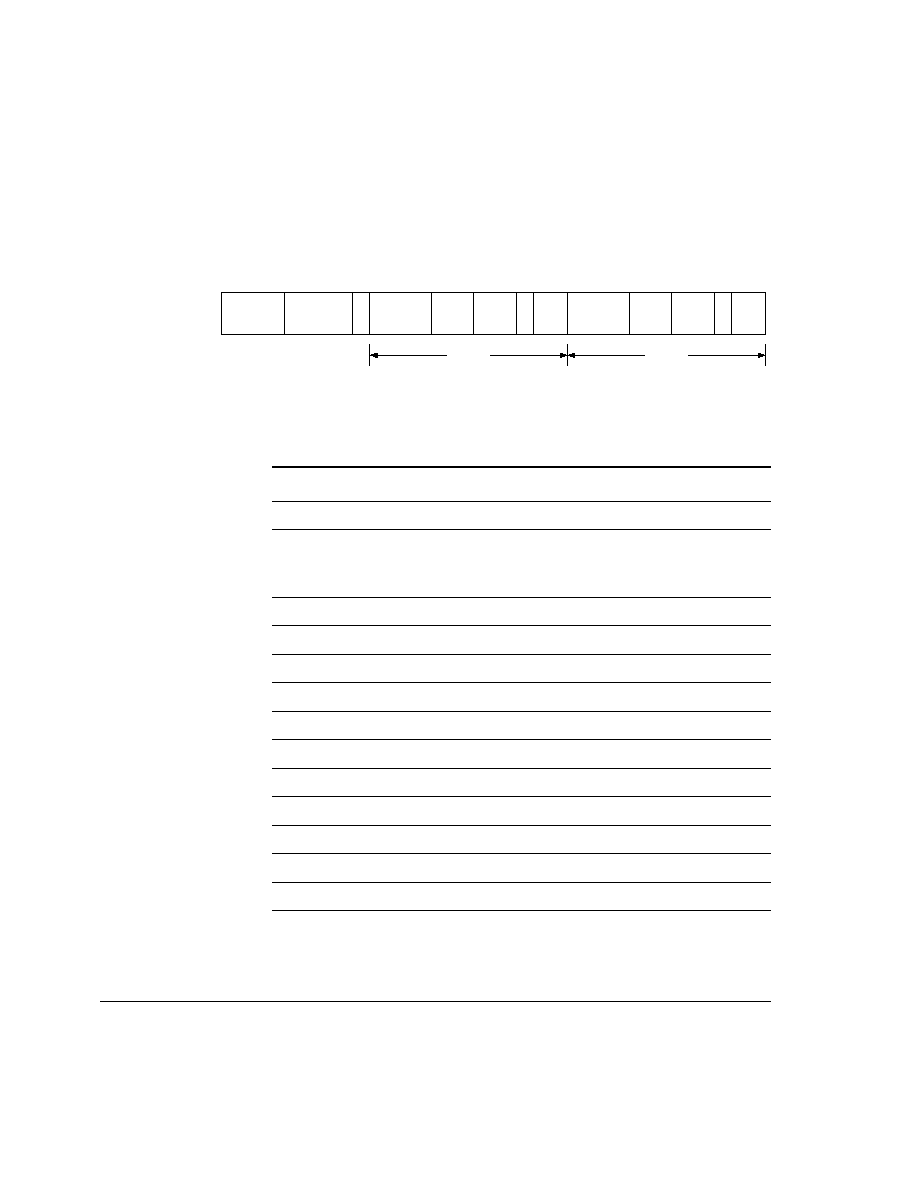

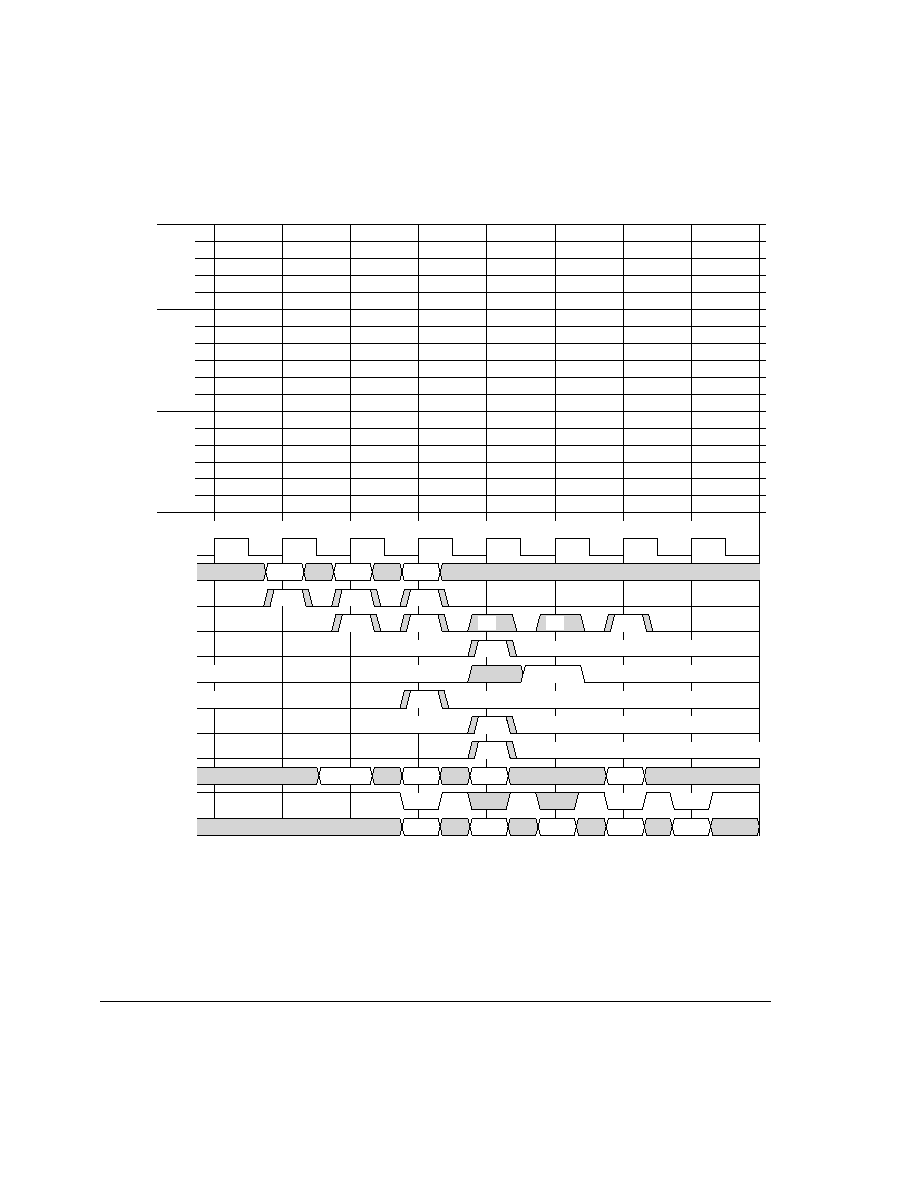

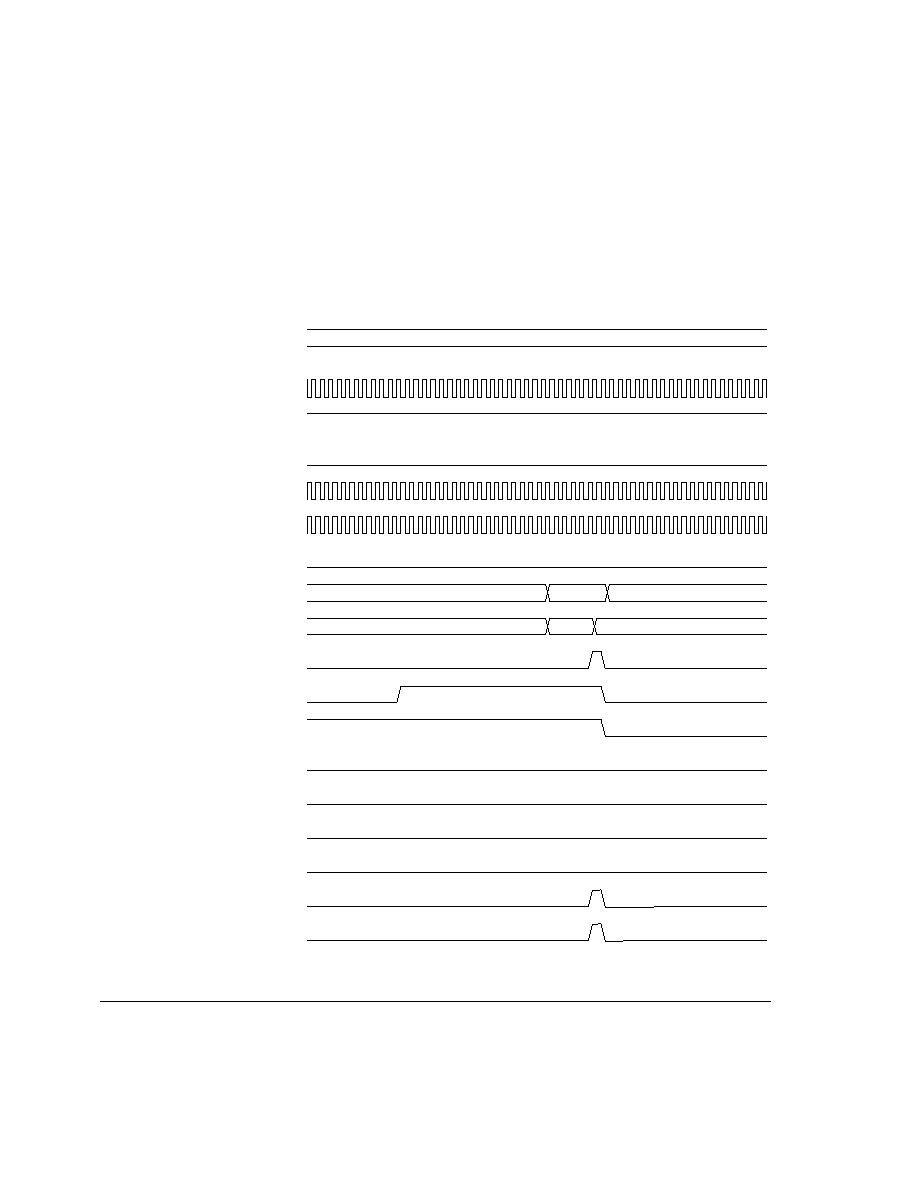

Timing diagram conventions

The figure explains the symbols used in timing diagrams. Any variations are clearly

labeled when they occur. Therefore, you must attach no additional meaning unless

specifically stated.

Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value

within the shaded area at that time. The actual level is unimportant and does not affect

normal operation.

Clock

Bus stable

HIGH to LOW

Transient

Bus to high impedance

Bus change

HIGH/LOW to HIGH

High impedance to stable bus

Preface

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

xxi

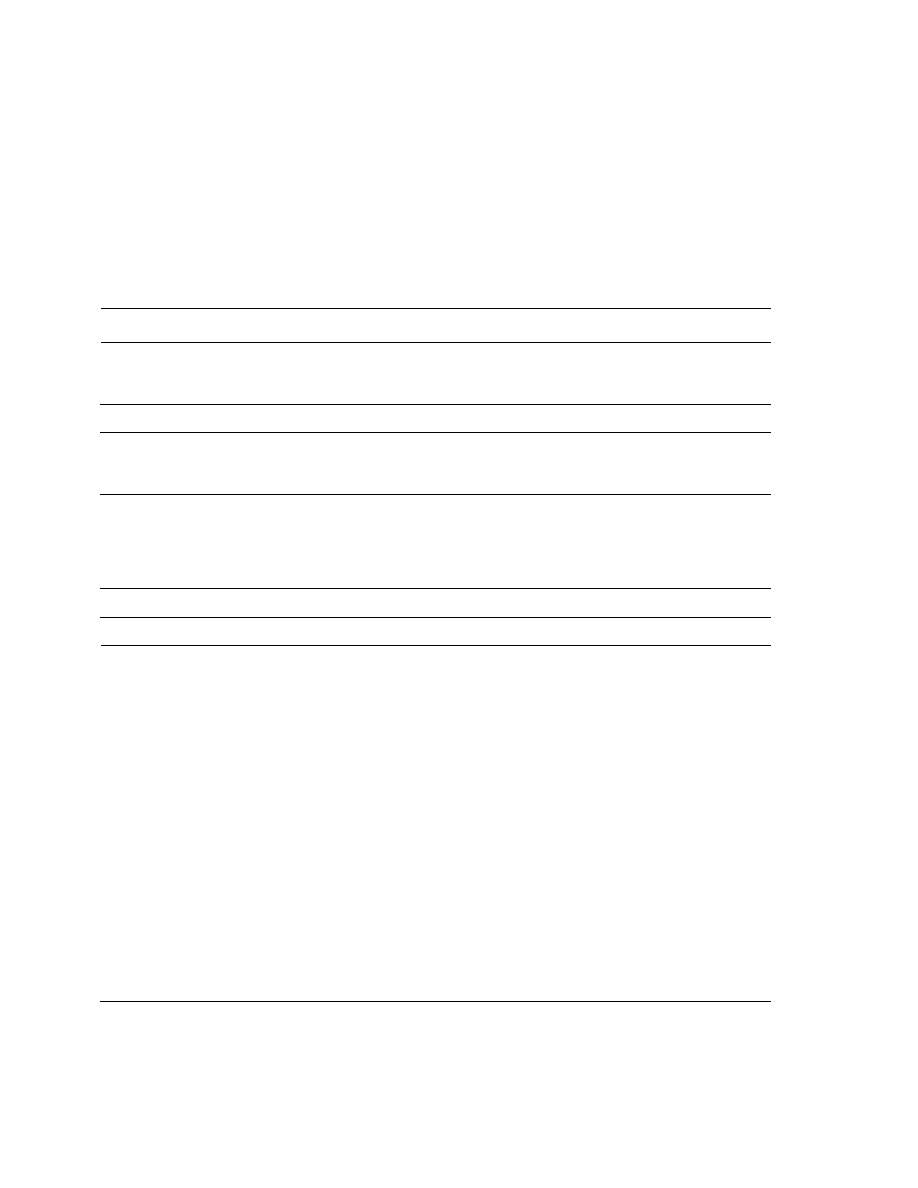

Register Notation Conventions

The table shows the terms and abbreviations used in register descriptions. In all cases,

reading or writing any fields, including those specified as

UNPREDICTABLE

,

SHOULD BE ONE

,

or

SHOULD BE ZERO

, does not cause any physical damage to the chip.

Further reading

This section lists publications by ARM Limited and by third parties.

ARM periodically provides updates and corrections to its documentation. See

http://www.arm.com

for current errata sheets and addenda.

See also the ARM Frequently Asked Questions list at:

http://www.arm.com/DevSupp/Sales+Support/faq.html

ARM publications

This document contains information that is specific to the ARM1022E processor. Refer

to the following documents for other relevant information:

∑

ARM Architecture Reference Manual (ARM DUI 0100)

∑

ARM AMBA Specification (Rev 2.0) (ARM IHI 0001)

∑

ARM10220E Test Chip Implementation Guide (ARM DXI 0141)

∑

ARM VFP10 (Rev 1) Technical Reference Manual (ARM DDI 0106)

∑

ARM ETM10 (Rev 0) Technical Reference Manual (ARM DDI 0206).

Other publications

This section lists relevant documents published by third parties:

∑

IEEE Standard, Test Access Port and Boundary-Scan Architecture specification

1149.1-1990 (JTAG).

Register notation conventions

Term

Description

UNPREDICTABLE (UNP)

Data read from this field can have any value. Writing to this field causes unpredictable behavior or

an unpredictable change in device configuration.

UNDEFINED (UND)

An instruction that accesses this field in the manner indicated takes the undefined instruction trap.

SHOULD BE ZERO (SBZ)

When writing to this field, write only zeros. Writing ones has

UNPREDICTABLE

results.

SHOULD BE ONE (SBO)

When writing to this field, write only ones. Writing zeros has

UNPREDICTABLE

results.

Preface

xxii

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Feedback

ARM Limited welcomes feedback both on the ARM1022E processor, and on the

documentation.

Feedback on the ARM1022E processor

If you have any comments or suggestions about this product, please contact your

supplier giving:

∑

the product name

∑

a concise explanation of your comments.

Feedback on this document

If you have any comments on this document, please send email to

errata@arm.com

giving:

∑

the document title

∑

the document number

∑

the page number(s) to which your comments refer

∑

a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

1-1

Chapter 1

Introduction

This chapter describes the components and features of the ARM1022E processor. It

contains the following sections:

∑

About the processor on page 1-2

∑

Programmer's model on page 1-4

∑

Components of the processor on page 1-5

∑

Instruction set summary on page 1-10.

Introduction

1-2

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

1.1

About the processor

The ARM1022E processor incorporates the ARM10ETM integer core, which

implements the ARMv5TE architecture. It is a high-performance, low-power, cached

processor that provides full virtual memory capabilities. It is designed to run high-end

embedded applications and sophisticated operating systems such as JavaOS, Linux,

Microsoft WindowsCE, NetBSD, and EPOC-32 from Symbian. It supports the ARM

and Thumb instruction sets, and includes EmbeddedICE-RTTM logic and JTAG

software debug features.

The ARM1022E processor consists of:

∑

the ARM10E integer core:

- load/store unit

- prefetch unit

- integer unit

- EmbeddedICE-RT logic for JTAG-based debug

∑

external coprocessor interface and coprocessors CP14 and CP15

∑

Memory Management Unit (MMU)

∑

instruction and data caches

∑

write-back Physical Address (PA) TAG RAM

∑

write buffer and Hit-Under-Miss (HUM) buffer

∑

Advanced Micro Bus Architecture (AMBA) High-performance Bus (AHB) bus

interface

∑

Embedded Trace Macrocell (ETM) interface.

Features of the ARM1022E processor include:

∑

a six-stage pipeline

∑

branch prediction that supports branch folding (zero cycle branches)

∑

32KB level 1 cache (16KB instruction, 16KB data)

∑

full 64-bit interfaces between the integer core and caches, write buffer, and bus

interface units on both instruction and data sides, and coprocessors

∑

multilayer AHB support through independent 64-bit AHB interfaces for

instruction and data sides

Introduction

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

1-3

∑

parallel execution of data processing instructions under load and store multiple

instructions

∑

a HUM buffer that supports execution of load hits underneath an outstanding load

miss

∑

nonblocking caches that support execution of data processing instructions under

load misses

∑

additional register read and write ports to support reading of up to four registers

and writing of three registers in one cycle

∑

improved power management support

∑

enhanced debug support.

Introduction

1-4

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

1.2

Programmer's model

The ARM10E programmer's model, including a detailed instruction set specification,

is described in the ARM Architecture Reference Manual. The programmer's model of

the ARM1022E processor is the same as the programmer's model of the ARM10E core,

but extended in the following ways:

∑

The system control coprocessor (CP15) is integrated into the ARM10 processor

and provides additional registers for configuring and controlling caches, MMU,

protection system, power-down, and clocking mode.

∑

The MMU page tables define the virtual-to-physical address mapping, page and

section access permissions, cache, and write buffer configuration. These are

created by the operating system software and accessed automatically by the

MMU hardware whenever an instruction read or data access causes a TLB miss.

Introduction

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

1-5

1.3

Components of the processor

This section introduces the main blocks of the ARM1022E processor and gives

references to detailed descriptions of those blocks:

∑

Integer core on page 1-7

∑

Memory Management Unit on page 1-7

∑

Instruction and data caches on page 1-7

∑

Cache power-down capabilities on page 1-8

∑

Branch prediction and prefetch unit on page 1-8

∑

AMBA interface on page 1-8

∑

Coprocessor interface on page 1-8

∑

Debug on page 1-8

∑

Instruction cycle summary and interlocks on page 1-8

∑

Design-for-test features on page 1-8

∑

Power management on page 1-9

∑

Clocking and PLL on page 1-9.

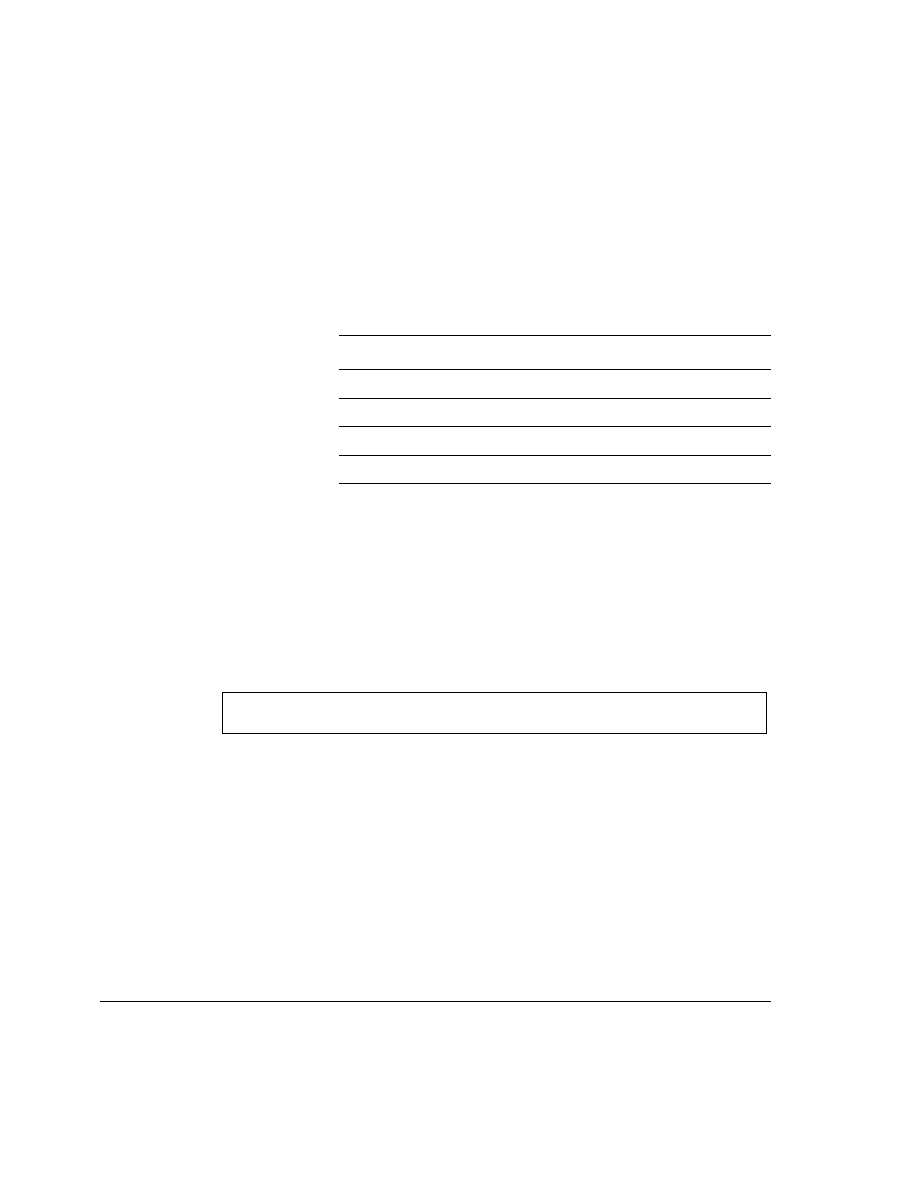

Figure 1-1 on page 1-6 shows the main blocks of the ARM1022E processor.

Introduction

1-6

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Figure 1-1 ARM1022E processor block diagram

DA[31:0]

PA[7:0]

IA[7:0]

Data-side

AHB

Instruction-side

AHB

DRD[63:0]

DWD[63:0]

DA[31:0]

External

coprocessors

ETM

interface

IPA[31:0]

IWD[63:0]

IA[31:0]

IA[31:0]

IRD[63:0]

DPA[31:0]

Write buffer

and fill buffer

ARM10E integer core

with EmbeddedICE-RT

logic

CP14

CP15

Load/Store

unit

Instruction

transfer

register

Prefetch unit

JTAG TAP

controller

Data cache

Data MMU

Instruction

cache

Instruction

MMU

AMBA bus

interface

Instruction

bus interface

unit

Data

bus interface

unit

Introduction

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

1-7

1.3.1

Integer core

This ARM1022E processor is built around the ARM10E integer core in an ARMv5TE

implementation that runs the 32-bit ARM and 16-bit compressed Thumb instruction

sets. You can balance high performance against code size and extract maximum

performance from 8-bit, 16-bit, and 32-bit memory. The processor includes

EmbeddedICE-RT logic for JTAG software debugging, and is supported by the

Multi-ICE JTAG debug interface.

Refer to Chapter 2 Integer Core for details of the pipeline stages and instruction

progression.

Refer to Chapter 3 System Control Coprocessor for system coprocessor programming

information.

1.3.2

Memory Management Unit

The MMU has separate instruction and data Translation Lookaside Buffers (TLBs). It

is backward-compatible with the ARM v4 architecture MMU of StrongARM and

ARM920T. The MMU includes a 1KB tiny page mapping size to enable a smaller RAM

and ROM footprint for embedded systems and operating systems such as

WindowsCETM that have many small mapped objects. The ARM1022E processor

implements the Fast Context Switching Extension (FCSE) and high vectors extension

that are required to run Microsoft WindowsCE. Refer to Chapter 4 Memory

Management Units for more information.

1.3.3

Instruction and data caches

This ARM1022E processor has a 16KB Instruction Cache (ICache) and a 16KB Data

Cache (DCache). The data cache provides Write-Through (WT) or Write-Back (WB)

operation, selected under software control on a per-region basis. The large caches

enable you to obtain high performance from commodity memory systems by

significantly reducing:

∑

the read bandwidth required of main memory

∑

the write bandwidth required of main memory (when write-back caching is used)

∑

overall system power consumption by reducing accesses to off-chip memory.

The processor provides a write buffer that holds up to eight 64-bit values, each at an

independent address.

Refer to Chapter 5 Caches and Write Buffer for more information.

Introduction

1-8

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

1.3.4

Cache power-down capabilities

The power manager provides a software-controlled hardware mechanism to maintain

power to the CAM and RAM state element arrays in the caches when the remainder of

the device is powered down. Refer to Chapter 5 Caches and Write Buffer for more

information.

1.3.5

Branch prediction and prefetch unit

The prefetch unit is part of the integer core. It fetches instructions from the ICache or

from external memory and issues them to the integer core. To increase performance, it

also predicts the outcome of branches in the instruction stream. Refer to Chapter 6

Prefetch Unit for more information.

1.3.6

AMBA interface

The bus interface unit provides a multimaster AHB interface to memory and

peripherals. The AHB is an on-chip bus with two unidirectional 64-bit data buses and

one 32-bit address bus. Refer to Chapter 7 Bus Interface for more information.

1.3.7

Coprocessor interface

Chapter 8 Coprocessor Interface describes the interface for on-chip coprocessors such

as floating-point units or application-specific hardware acceleration units.

1.3.8

Debug

The debug coprocessor, CP14, implements a full range of debug features described in

Chapter 9 JTAG Interface and Chapter 10 Debug.

1.3.9

Instruction cycle summary and interlocks

Chapter 11 Instruction Cycle Summary and Interlocks describes instruction cycle times

and gives examples of interlock timing.

1.3.10

Design-for-test features

The ARM1022E processor is designed to be embedded into large System-on-Chip

(SoC) designs. The EmbeddedICE-RT logic debug facilities, AMBA on-chip system

bus, and test methodology are all designed for efficient use of the processor when

integrated into a larger IC. Refer to Chapter 12 Design for Test for details of testing.

Introduction

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

1-9

1.3.11

Power management

Power management features are described in Chapter 13 Power Manager.

1.3.12

Clocking and PLL

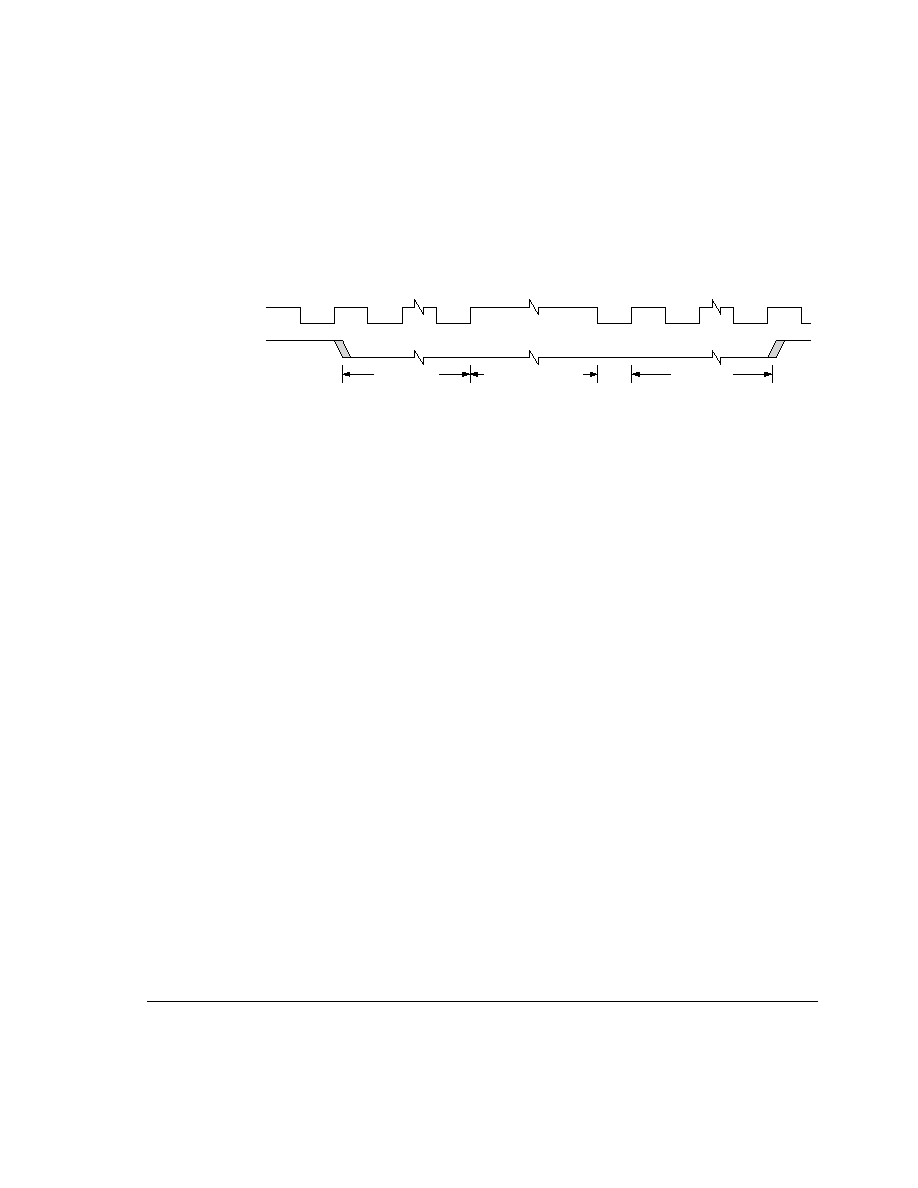

The ARM10 processor has two clock inputs:

∑

GCLK

∑

HCLK.

The design is fully static. When both these clocks are stopped, the internal state of the

processor is preserved indefinitely. GCLK drives the internal logic in the processor.

HCLK drives the bus interface. Most input and output timings are specified with

respect to HCLK.

Refer to Chapter 14 Clock Generator and Chapter 7 Bus Interface for details.

Note

Typically, GCLK frequency is higher than that of HCLK. The two clocks must have a

fixed phase relationship. HCLK is usually derived by dividing down the source of

GCLK.

1.3.13

ETM interface logic

An optional external ETM can be connected to the ARM1022E processor to provide

real-time tracing of instructions and data in an embedded system. The processor

includes the logic and interface to enable you to trace program execution and data

transfers using the ETM10. Further details are in Embedded Trace Macrocell

Specification. See Table A-10 on page A-13 for descriptions of ETM-related signals.

Introduction

1-10

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

1.4

Instruction set summary

This section provides a summary of the ARM and Thumb instruction sets:

∑

ARM instruction summary on page 1-11

∑

Thumb instruction summary on page 1-20.

The ARM1022E processor is an implementation of the ARM architecture version 5TE.

For a complete description of both instruction sets, refer to the ARM Architecture

Reference Manual.

Table 1-1 is a key to the notation used in the instruction set tables.

Table 1-1 Key to instruction set table notation

Notation

Description

{cond}

Table 1-11 on page 1-19 defines the condition notation.

<Oprnd2>

Table 1-9 on page 1-18 gives examples of Oprnd2.

{field}

Table 1-10 on page 1-18 defines the field notation.

S

Sets condition codes (optional).

B

Byte operation (optional).

H

Halfword operation (optional).

T

Forces address translation. Cannot be used with preindexed addresses.

<a_mode2>

Table 1-3 on page 1-14 describes addressing mode 2.

<a_mode2P>

Table 1-4 on page 1-15 describes addressing mode 2 (privileged).

<a_mode3>

Table 1-5 on page 1-16 describes addressing mode 3.

<a_mode4L>

Table 1-6 on page 1-17 describes addressing mode 4 (load).

<a_mode4S>

Table 1-7 on page 1-17 describes addressing mode 4 (store).

<a_mode5>

Table 1-8 on page 1-17 describes addressing mode 5.

#32bit_Imm

A 32-bit constant, formed by right-rotating an 8-bit value by an even number

of bits.

<reglist>

A comma-separated list of registers, enclosed in braces ( { and } ).

Introduction

ARM DDI 0237A

Copyright © 2001 ARM Limited. All rights reserved.

1-11

1.4.1

ARM instruction summary

Table 1-2 summarizes the ARM instructions. Asterisks in the Operation column denote

ARMv5TE instructions.

Table 1-2 ARM instruction summary

Operation

Assembler

Move

Move

MOV{cond}{S} Rd, <Oprnd2>

Move NOT

MVN{cond}{S} Rd, <Oprnd2>

Move SPSR to register

MRS{cond} Rd, SPSR

Move CPSR to register

MRS{cond} Rd, CPSR

Move register to SPSR

MSR{cond} SPSR_{field}, Rm

Move register to CPSR

MSR{cond} CPSR_{field}, Rm

Move immediate to SPSR flags

MSR{cond} SPSR_f, #32bit_Imm

Move immediate to CPSR flags

MSR{cond} CPSR_f, #32bit_Imm

Arithmetic

Add

ADD{cond}{S} Rd, Rn, <Oprnd2>

Add with carry

ADC{cond}{S} Rd, Rn, <Oprnd2>

*

Saturating add

QADD{cond} Rd, Rm, Rn

*

Saturating add

QDADD{cond} Rd, Rm, Rn

Subtract

SUB{cond}{S} Rd, Rn, <Oprnd2>

*

Saturating subtract

QSUB{cond} Rd, Rm, Rn

*

Saturating subtract

QDSUB{cond} Rd, Rm, Rn

Subtract with carry

SBC{cond}{S} Rd, Rn, <Oprnd2>

Subtract reverse subtract

RSB{cond}{S} Rd, Rn, <Oprnd2>

Subtract reverse subtract with carry

RSC{cond}{S} Rd, Rn, <Oprnd2>

Multiply

MUL{cond}{S} Rd, Rm, Rs

Multiply accumulate

MLA{cond}{S} Rd, Rm, Rs, Rn

Multiply unsigned long

UMULL{cond}{S} RdLo, RdHi, Rm, Rs

Multiply unsigned accumulate long

UMLAL{cond}{S} RdLo, RdHi, Rm, Rs

Introduction

1-12

Copyright © 2001 ARM Limited. All rights reserved.

ARM DDI 0237A

Multiply signed long

SMULL{cond}{S} RdLo, RdHi, Rm, Rs

*

Multiply signed, 16-bit operands

SMUL<x><y>{cond}Rd, Rm, Rs, Rn

Multiply signed, Word and 16-bit operand

SMULW<y>{cond}Rd, Rm, Rs, Rn

*

Multiply signed accumulate, 16-bit operands

SMLA<x><y>{cond} Rd, Rs, Rm, Rn

Multiply signed accumulate long

SMLAL{cond}{S} RdLo, RdHi, Rm, Rs

*

Multiply signed accumulate long, 16-bit operands

SMLAL<x><y>{cond}{S} RdLo, RdHi, Rm, Rs

*

Multiply signed accumulate, Word and 16-bit operand

SMLAW<y>{cond} Rd, Rs, Rm, Rn

Compare

CMP{cond} Rd, <Oprnd2>

Compare negative

CMN{cond} Rd, <Oprnd2>

Logical

Test

TST{cond} Rn, <Oprnd2>

Test equivalence

TEQ{cond} Rn, <Oprnd2>

AND

AND{cond}{S} Rd, Rn, <Oprnd2>

EOR

EOR{cond}{S} Rd, Rn, <Oprnd2>

ORR

ORR{cond}{S} Rd, Rn, <Oprnd2>

Bit clear

BIC{cond}{S} Rd, Rn, <Oprnd2>

Branch

Branch

B{cond} label

Branch with link

BL{cond} label

Branch and exchange instruction set

BX{cond} Rn

Load

Word

LDR{cond} Rd, <a_mode2>

Word with user-mode privilege