| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 24C1024 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

Features

∑

Low-voltage Operation

≠ 2.7 (V

CC

= 2.7V to 5.5V)

∑

Internally Organized 131,072 x 8

∑

2-wire Serial Interface

∑

Schmitt Triggers, Filtered Inputs for Noise Suppression

∑

Bi-directional Data Transfer Protocol

∑

400 kHz (2.7V) and 1 MHz (5V) Clock Rate

∑

Write Protect Pin for Hardware and Software Data Protection

∑

256-byte Page Write Mode (Partial Page Writes Allowed)

∑

Random and Sequential Read Modes

∑

Self-timed Write Cycle (5 ms Typical)

∑

High Reliability

≠ Endurance: 100,000 Write Cycles/Page

≠ Data Retention: 40 Years

∑

8-lead PDIP, 8-lead EIAJ SOIC, 8-lead LAP and 8-ball dBGA

TM

Packages

Description

The AT24C1024 provides 1,048,576 bits of serial electrically erasable and program-

mable read only memory (EEPROM) organized as 131,072 words of 8 bits each. The

device's cascadable feature allows up to 2 devices to share a common 2-wire bus. The

device is optimized for use in many industrial and commercial applications where low-

power and low-voltage operation are essential. The devices are available in space-

saving 8-lead PDIP, 8-lead EIAJ SOIC, 8-lead Leadless Array (LAP) and 8-ball dBGA

packages. In addition, the entire family is available in 2.7V (2.7V to 5.5V) versions.

2-wire Serial

EEPROM

1M (131,072 x 8)

AT24C1024

Rev. 1471H≠SEEPR≠03/03

Pin Configurations

Pin Name

Function

A1

Address Input

SDA

Serial Data

SCL

Serial Clock Input

WP

Write Protect

NC

No Connect

8-lead PDIP

1

2

3

4

8

7

6

5

NC

A1

NC

GND

VCC

WP

SCL

SDA

8-lead Leadless Array

Bottom View

1

2

3

4

8

7

6

5

VCC

WP

SCL

SDA

NC

A1

NC

GND

8-lead SOIC

1

2

3

4

8

7

6

5

NC

A1

NC

GND

VCC

WP

SCL

SDA

8-ball dBGA

Bottom View

VCC

WP

SCL

SDA

NC

A1

NC

GND

1

2

3

4

8

7

6

5

2

AT24C1024

1471H≠SEEPR≠03/03

Block Diagram

Absolute Maximum Ratings*

Operating Temperature.................................. -55

∞C to +125∞C

*NOTICE:

Stresses beyond those listed under "Absolute

Maximum Ratings" may cause permanent dam-

age to the device. This is a stress rating only and

functional operation of the device at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions for extended periods may affect device

reliability.

Storage Temperature ..................................... -65

∞C to +150∞C

Voltage on Any Pin

with Respect to Ground .....................................-1.0V to +7.0V

Maximum Operating Voltage .......................................... 6.25V

DC Output Current........................................................ 5.0 mA

3

AT24C1024

1471H≠SEEPR≠03/03

Pin Description

SERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each

EEPROM device and negative edge clock data out of each device.

SERIAL DATA (SDA): The SDA pin is bi-directional for serial data transfer. This pin is open-

drain driven and may be wire-ORed with any number of other open-drain or open-collector

devices.

DEVICE/PAGE ADDRESSES (A1): The A1 pin is a device address input that can be hard-

wired or left not connected for hardware compatibility with AT24C128/256/512. When the A1

pin is hardwired, as many as two 1024K devices may be addressed on a single bus system

(device addressing is discussed in detail under the Device Addressing section). When the pin

is not hardwired, the default A1 is zero.

WRITE PROTECT (WP): The hardware Write Protect pin is useful for protecting the entire

contents of the memory from inadvertent write operations. The write-protect input, when tied to

GND, allows normal write operations. When WP is tied high to V

CC

, all write operations to the

memory are inhibited. If left unconnected, WP is internally pulled down to GND. Switching WP

to V

CC

prior to a write operation creates a software write-protect function.

Memory

Organization

AT24C1024, 1024K SERIAL EEPROM: The 1024K is internally organized as 512 pages of

256 bytes each. Random word addressing requires a 17-bit data word address.

4

AT24C1024

1471H≠SEEPR≠03/03

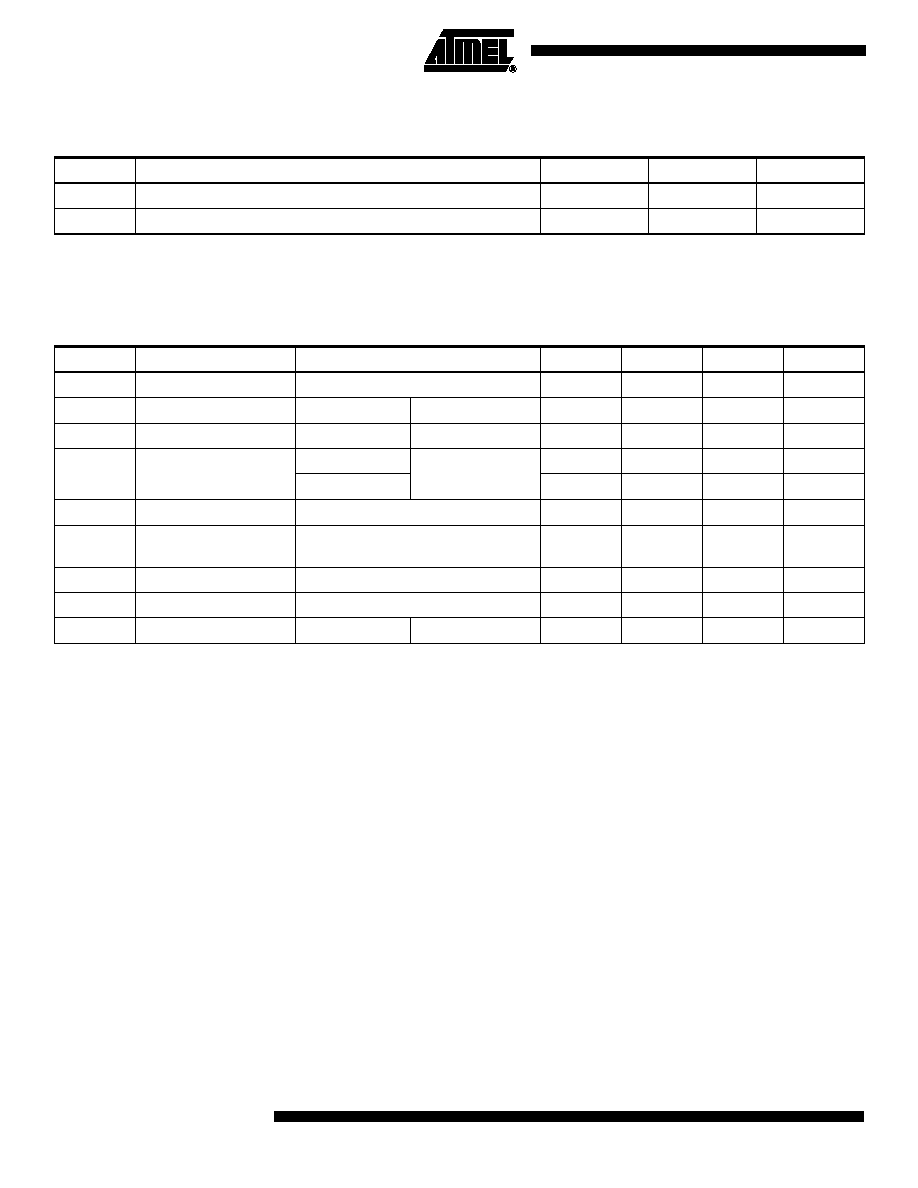

Pin Capacitance

(1)

Note:

1. This parameter is characterized and is not 100% tested.

DC Characteristics

Note:

1. V

IL

min and V

IH

max are reference only and are not tested.

Applicable over recommended operating range from T

A

= 25

∞C, f = 1.0 MHz, V

CC

= +2.7V.

Symbol

Test Condition

Max

Units

Conditions

C

I/O

Input/Output Capacitance (SDA)

8

pF

V

I/O

= 0V

C

IN

Input Capacitance (A

1

, SCL)

6

pF

V

IN

= 0V

Applicable over recommended operating range from: T

AI

= -40

∞C to +85∞C, V

CC

= +2.7V to +5.5V, T

AC

= 0

∞C to +70∞C,

V

CC

= +2.7V to +5.5V (unless otherwise noted).

Symbol

Parameter

Test Condition

Min

Typ

Max

Units

V

CC

Supply Voltage

2.7

5.5

V

I

CC

Supply Current

V

CC

= 5.0V

READ at 400 kHz

2.0

mA

I

CC

Supply Current

V

CC

= 5.0V

WRITE at 400 kHz

5.0

mA

I

SB

Standby Current

V

CC

= 2.7V

V

IN

= V

CC

or V

SS

3.0

µA

V

CC

= 5.5V

6.0

µA

I

LI

Input Leakage Current

V

IN

= V

CC

or

V

SS

0.10

3.0

µA

I

LO

Output Leakage

Current

V

OUT

= V

CC

or

V

SS

0.05

3.0

µA

V

IL

Input Low Level

(1)

-0.6

V

CC

x 0.3

V

V

IH

Input High Level

(1)

V

CC

x 0.7

V

CC

+ 0.5

V

V

OL

Output Low Level

V

CC

= 3.0V

I

OL

= 2.1 mA

0.4

V

5

AT24C1024

1471H≠SEEPR≠03/03

AC Characteristics

Notes:

1. This parameter is characterized and is not 100% tested.

2. AC measurement conditions:

R

L

(connects to V

CC

): 1.3 k

(2.7V, 5V)

Input pulse voltages: 0.3 V

CC

to 0.7 V

CC

Input rise and fall times:

50 ns

Input and output timing reference voltages: 0.5 V

CC

Applicable over recommended operating range from T

A

= -40

∞C to +85∞C, V

CC

= +2.7V to +5.5V, C

L

= 100 pF (unless

otherwise noted). Test conditions are listed in Note 2.

Symbol

Parameter

Test Conditions

Min

Max

Units

f

SCL

Clock Frequency, SCL

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

1000

400

kHz

t

LOW

Clock Pulse Width Low

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.4

1.3

µs

t

HIGH

Clock Pulse Width High

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.4

0.6

µs

t

AA

Clock Low to Data Out Valid

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.05

0.05

0.55

0.9

µs

t

BUF

Time the bus must be free before a new

transmission can start

(1)

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.5

1.3

µs

t

HD.STA

Start Hold Time

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.25

0.6

µs

t

SU.STA

Start Setup Time

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.25

0.6

µs

t

HD.DAT

Data In Hold Time

0

µs

t

SU.DAT

Data In Setup Time

100

ns

t

R

Inputs Rise Time

(1)

0.3

µs

t

F

Inputs Fall Time

(1)

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

100

300

ns

t

SU.STO

Stop Setup Time

4.5V

V

CC

5.5V

2.7V

V

CC

5.5V

0.25

0.6

µs

t

DH

Data Out Hold Time

50

ns

t

WR

Write Cycle Time

10

ms

Endurance

(1)

5.0V, 25

∞C, Page Mode

100K

Write Cycles