1

Features

∑

Serial Peripheral Interface (SPI) Compatible

∑

Supports SPI Modes 0 (0,0) and 3 (1,1)

∑

10 MHz Clock Rate

∑

128-Byte Page Mode Only for Write Operations

∑

Low-Voltage and Standard-Voltage Operation

≠ 5.0 (V

CC

= 4.5V to 5.5V)

≠ 2.7 (V

CC

= 2.7V to 5.5V)

≠ 1.8 (V

CC

= 1.8V to 3.6V)

∑

Block Write Protection

≠ Protect 1/4, 1/2, or Entire Array

∑

Write Protect (WP) Pin and Write Disable Instructions for

Both Hardware and Software Data Protection

∑

High Reliability

≠ Endurance: 100K Write Cycles

≠ Data Retention: > 40 Years

≠ ESD Protection: > 3000V

∑

8-Pin PDIP, 8-Pin EIAJ SOIC, and 8-Pin Leadless Array Package

Description

The AT25HP256/512 provides 262,144/524,288 bits of serial electrically erasable pro-

grammable read only memory (EEPROM) organized as 32,768/65,536 words of 8-bits

each. The device is optimized for use in many industrial and commercial applications

where high-speed, low-power, and low-voltage operation are essential. The

AT25HP256/512 is available in a space saving 8-pin PDIP (AT25HP256/512), 8-pin

EIAJ SOIC (AT25HP256), and 8-pin Leadless Array (AT25HP256/512) packages. In

Rev. 1113B≠07/98

SPI Serial

EEPROMs

256K (32,768 x 8)

512K (65,536 x 8)

AT25HP256

AT25HP512

Preliminary

Pin Configurations

Pin Name

Function

CS

Chip Select

SCK

Serial Data Clock

SI

Serial Data Input

SO

Serial Data Output

GND

Ground

VCC

Power Supply

WP

Write Protect

HOLD

Suspends Serial Input

(continued)

8-Pin SOIC

C S

S C K

S O

W P

H O L D

G N D

V C C

1

2

3

4

8

7

6

5

S I

8-Pin PDIP

C S

S C K

S O

W P

H O L D

G N D

V C C

1

2

3

4

8

7

6

5

S I

8-Pin Leadless Array

Bottom View

1

2

3

4

8

7

6

5

VCC

HOLD

SCK

SI

CS

SO

WP

GND

AT25HP256/512

2

addition, the entire family is available in 5.0V (4.5V to

5.5V), 2.7V (2.7V to 5.5V), and 1.8V (1.8V to 3.6V) ver-

sions.

The AT25HP256/512 is enabled through the Chip Select

pin (CS) and accessed via a 3-wire interface consisting of

Serial Data Input (SI), Serial Data Output (SO), and Serial

Clock (SCK). All programming cycles are completely self-

timed, and no separate ERASE cycle is required before

WRITE.

BLOCK WRITE protection is enabled by programming the

status register with top º, top Ω or entire array of write pro-

tection. Separate program enable and program disable

instructions are provided for additional data protection.

Hardware data protection is provided via the WP pin to pro-

tect against inadvertent write attempts to the status regis-

ter. The HOLD pin may be used to suspend any serial

communication without resetting the serial sequence.

*NOTICE:

Stresses beyond those listed under "Absolute Maxi-

mum Ratings" may cause permanent damage to the

device. This is a stress rating only and functional

operation of the device at these or any other condi-

tions beyond those indicated in the operational sec-

tions of this specification is not implied. Exposure to

absolute maximum rating conditions for extended

periods may affect device reliability.

Block Diagram

Absolute Maximum Ratings*

Operating Temperature .................................. -55

∞

C to +125

∞

C

Storage Temperature ..................................... -65

∞

C to +150

∞

C

Voltage on Any Pin

with Respect to Ground .................................... -1.0V to +7.0V

Maximum Operating Voltage ........................................... 6.25V

DC Output Current ........................................................ 5.0 mA

32,768/65,536 x 8

AT25HP256/512

3

Note:

1. This parameter is characterized and is not 100% tested.

Note:

1. V

IL

and V

IH

max are reference only and are not tested.

Pin Capacitance

(1)

Applicable over recommended operating range from T

A

= 25

∞

C, f = 1.0 MHz, V

CC

= +5.0V (unless otherwise noted).

Test Conditions

Max

Units

Conditions

C

OUT

Output Capacitance (SO)

8

pF

V

OUT

= 0V

C

IN

Input Capacitance (CS, SCK, SI, WP, HOLD)

6

pF

V

IN

= 0V

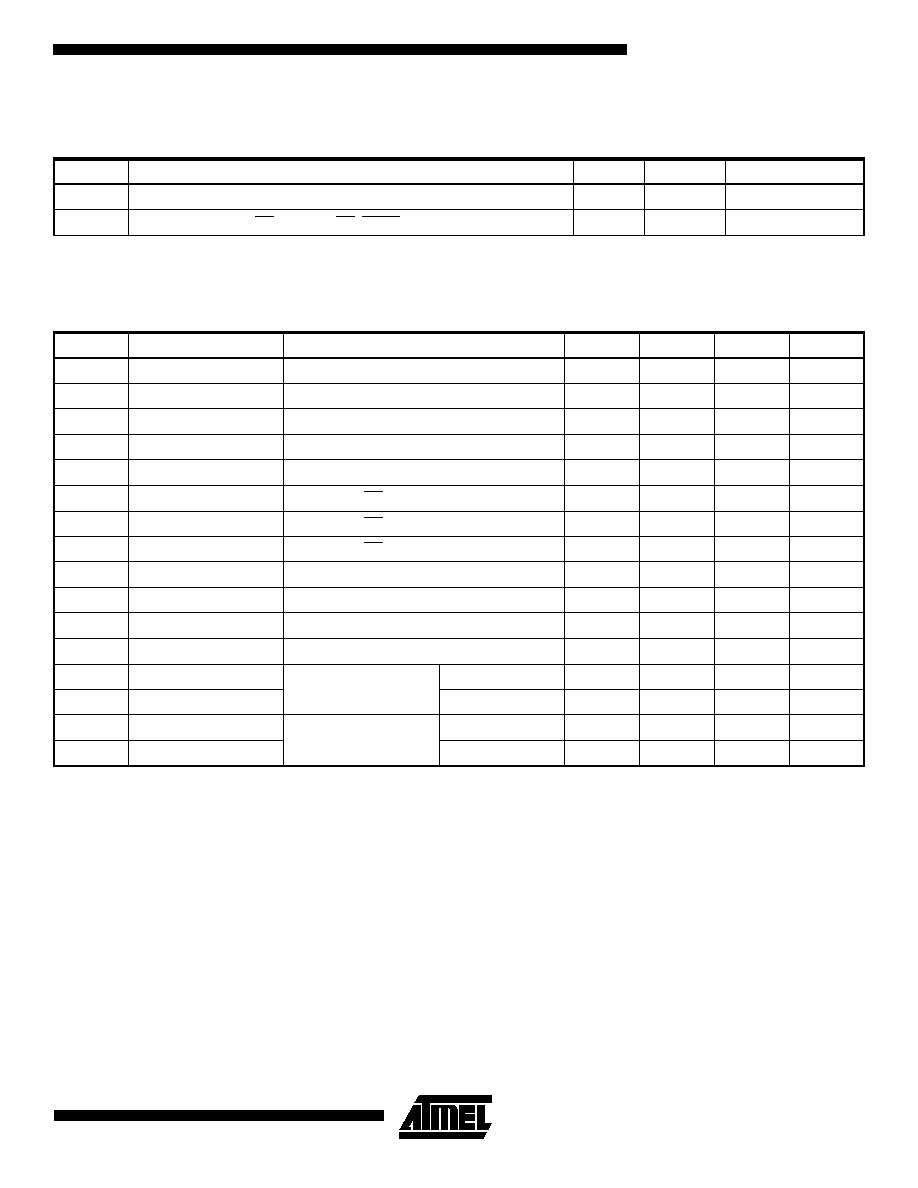

DC Characteristics

Applicable over recommended operating range from: T

AI

= -40

∞

C to +85

∞

C, V

CC

= +1.8V to +5.5V,

T

AC

= 0

∞

C to +70

∞

C, V

CC

= +1.8V to +5.5V (unless otherwise noted).

Symbol

Parameter

Test Condition

Min

Typ

Max

Units

V

CC1

Supply Voltage

1.8

3.6

V

V

CC2

Supply Voltage

2.7

5.5

V

V

CC3

Supply Voltage

4.5

5.5

V

I

CC1

Supply Current

V

CC

= 5.0V at 5 MHz, SO = Open Read

6.0

10.0

mA

I

CC2

Supply Current

V

CC

= 5.0V at 5 MHz, SO = Open Write

4.0

7.0

mA

I

SB1

Standby Current

V

CC

= 1.8V, CS = V

CC

0.1

2.0

µ

A

I

SB2

Standby Current

V

CC

= 2.7V, CS = V

CC

0.2

2.0

µ

A

I

SB3

Standby Current

V

CC

= 5.0V, CS = V

CC

2.0

5.0

µ

A

I

IL

Input Leakage

V

IN

= 0V to V

CC

-3.0

3.0

µ

A

I

OL

Output Leakage

V

IN

= 0V to V

CC

, T

AC

= 0

∞

C to 70

∞

C

-3.0

3.0

µ

A

V

IL

(1)

Input Low Voltage

-0.6

V

CC

x 0.3

V

V

IH

(1)

Input High Voltage

V

CC

x 0.7

V

CC

+ 0.5

V

V

OL1

Output Low Voltage

4.5V

V

CC

5.5V

I

OL

= 3.0 mA

0.4

V

V

OH1

Output High Voltage

I

OH

= -1.6 mA

V

CC

- 0.8

V

V

OL2

Output Low Voltage

1.8V

V

CC

3.6V

I

OL

= 0.15 mA

0.2

V

V

OH2

Output High Voltage

I

OH

= -100

µ

A

V

CC

- 0.2

V

AT25HP256/512

4

AC Characteristics

Applicable over recommended operating range from T

A

= -40

∞

C to +85

∞

C, V

CC

= As Specified,

C

L

= 1 TTL Gate and 30 pF (unless otherwise noted).

Symbol

Parameter

Voltage

Min

Max

Units

f

SCK

SCK Clock Frequency

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

10

5

TBD

MHz

t

RI

Input Rise Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

2

2

TBD

µ

s

t

FI

Input Fall Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

2

2

TBD

µ

s

t

WH

SCK High Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

40

80

TBD

ns

t

WL

SCK Low Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

40

80

TBD

ns

t

CS

CS High Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

50

100

TBD

ns

t

CSS

CS Setup Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

50

100

TBD

ns

t

CSH

CS Hold Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

50

100

TBD

ns

t

SU

Data In Setup Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

12

20

TBD

ns

t

H

Data In Hold Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

10

20

TBD

ns

t

HD

Hold Setup Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

25

50

TBD

ns

t

CD

Hold Hold Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

25

50

TBD

ns

t

V

Output Valid

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

40

80

TBD

ns

t

HO

Output Hold Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

ns

AT25HP256/512

5

Note:

1. This parameter is characterized and is not 100% tested.

t

LZ

Hold to Output Low Z

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

100

200

TBD

ns

t

HZ

Hold to Output High Z

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

100

200

TBD

ns

t

DIS

Output Disable Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

100

100

TBD

ns

t

WC

Write Cycle Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

5

10

TBD

ms

Endurance

(1)

5.0V, 25

∞

C, Page Mode

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

100K

Write

Cycles

AC Characteristics (Continued)

Applicable over recommended operating range from T

A

= -40

∞

C to +85

∞

C, V

CC

= As Specified,

C

L

= 1 TTL Gate and 30 pF (unless otherwise noted).

Symbol

Parameter

Voltage

Min

Max

Units