1

Features

∑

Fast Read Access Time ≠ 120 ns

∑

Fast Byte Write ≠ 200

µs or 1 ms

∑

Self-timed Byte Write Cycle

≠ Internal Address and Data Latches

≠ Internal Control Timer

≠ Automatic Clear Before Write

∑

Direct Microprocessor Control

≠ READY/BUSY Open Drain Output

≠ DATA Polling

∑

Low Power

≠ 30 mA Active Current

≠ 100

µA CMOS Standby Current

∑

High Reliability

≠ Endurance: 10

4

or 10

5

Cycles

≠ Data Retention: 10 Years

∑

5V

± 10% Supply

∑

CMOS and TTL Compatible Inputs and Outputs

∑

JEDEC Approved Byte-wide Pinout

∑

Commercial and Industrial Temperature Ranges

Description

The AT28C64 is a low-power, high-performance 8,192 words by 8-bit nonvolatile elec-

trically erasable and programmable read only memory with popular, easy-to-use fea-

tures. The device is manufactured with Atmel's reliable nonvolatile technology.

64K (8K x 8)

Parallel

EEPROMs

AT28C64

AT28C64X

Rev. 0001H≠12/99

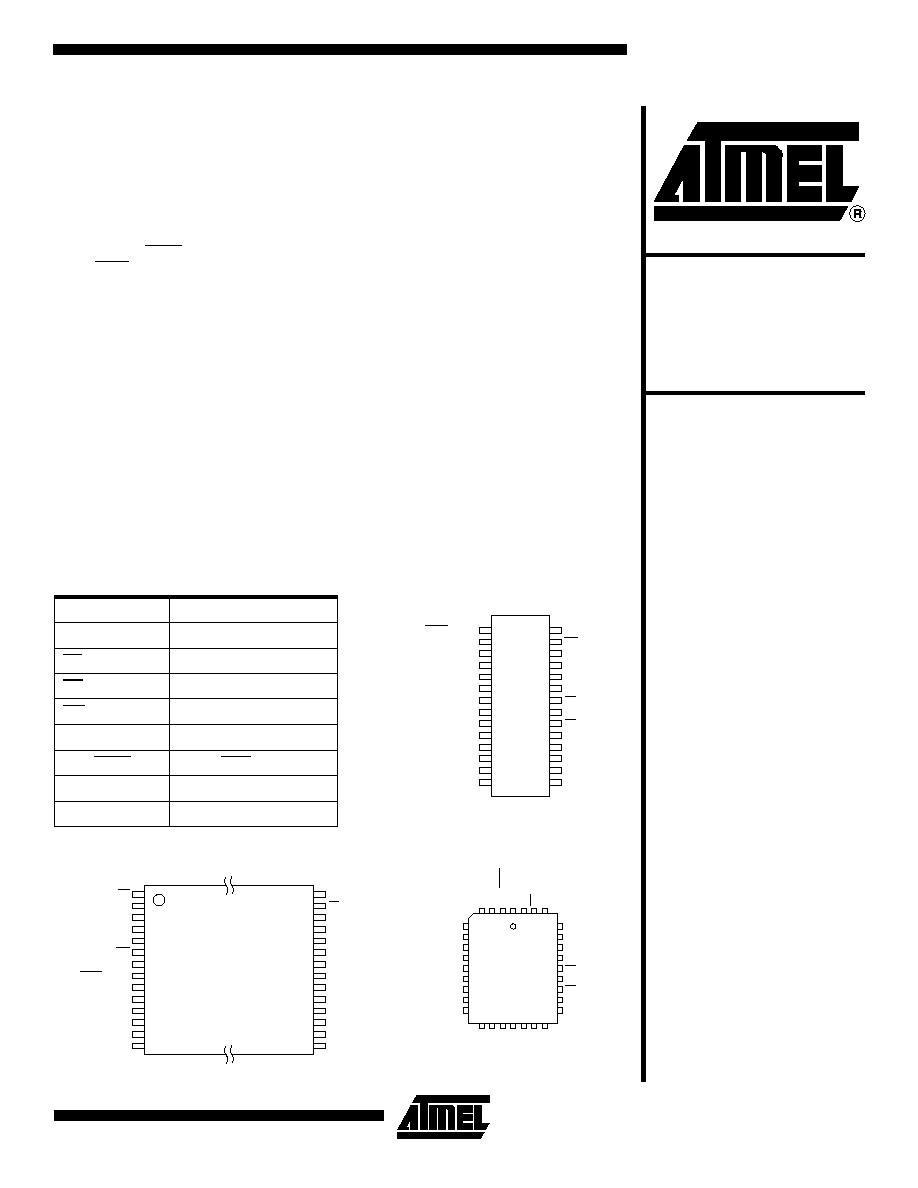

Pin Configurations

Pin Name

Function

A0 - A12

Addresses

CE

Chip Enable

OE

Output Enable

WE

Write Enable

I/O0 - I/O7

Data Inputs/Outputs

RDY/BUSY

Ready/Busy Output

NC

No Connect

DC

Don't Connect

TSOP

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

OE

A11

A9

A8

NC

WE

VCC

RDY/BUSY (or NC)

A12

A7

A6

A5

A4

A3

A10

CE

I/O7

I/O6

I/O5

I/O4

I/O3

GND

I/O2

I/O1

I/O0

A0

A1

A2

LCC, PLCC

Top View

Note: PLCC package pins 1 and 17 are

DON'T CONNECT.

5

6

7

8

9

10

11

12

13

29

28

27

26

25

24

23

22

21

A6

A5

A4

A3

A2

A1

A0

NC

I/O0

A8

A9

A11

NC

OE

A10

CE

I/O7

I/O6

4

3

2

1

32

31

30

14

15

16

17

18

19

20

I/O1

I/O2

VSS

DC

I/O3

I/O4

I/O5

A7

A12

RDY/BUSY (or NC)

DC

VCC

WE

NC

(continued)

PDIP, SOIC

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RDY/BUSY (or NC)

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O0

I/O1

I/O2

GND

VCC

WE

NC

A8

A9

A11

OE

A10

CE

I/O7

I/O6

I/O5

I/O4

I/O3

AT28C64(X)

2

The AT28C64 is accessed like a Static RAM for the read or

write cycles without the need for external components. Dur-

ing a byte write, the address and data are latched inter-

nally, freeing the microprocessor address and data bus for

other operations. Following the initiation of a write cycle,

the device will go to a busy state and automatically clear

and write the latched data using an internal control timer.

The device includes two methods for detecting the end of a

write cycle, level detection of RDY/BUSY (unless pin 1 is

N.C.) and DATA Polling of I/O

7

. Once the end of a write

cycle has been detected, a new access for a read or write

can begin.

The CMOS technology offers fast access times of 120 ns at

low power dissipation. When the chip is deselected the

standby current is less than 100

µA.

Atmel's AT28C64 has additional features to ensure high

quality and manufacturability. The device utilizes error cor-

rection internally for extended endurance and for improved

data retention characteristics. An extra 32 bytes of

EEPROM are available for device identification or tracking.

Block Diagram

Absolute Maximum Ratings*

Temperature under Bias ................................ -55∞C to +125∞C

*NOTICE:

Stresses beyond those listed under "Absolute

Maximum Ratings" may cause permanent dam-

age to the device. This is a stress rating only and

functional operation of the device at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions for extended periods may affect

device reliability

Storage Temperature ..................................... -65∞C to +150∞C

All Input Voltages (including NC Pins)

with Respect to Ground ...................................-0.6V to +6.25V

All Output Voltages

with Respect to Ground .............................-0.6V to V

CC

+ 0.6V

Voltage on OE and A9

with Respect to Ground ...................................-0.6V to +13.5V

AT28C64(X)

3

Device Operation

READ: The AT28C64 is accessed like a Static RAM.

When CE and OE are low and WE is high, the data stored

at the memory location determined by the address pins is

asserted on the outputs. The outputs are put in a high

impedance state whenever CE or OE is high. This dual line

control gives designers increased flexibility in preventing

bus contention.

BYTE WRITE: Writing data into the AT28C64 is similar to

writing into a Static RAM. A low pulse on the WE or CE

input with OE high and CE or WE low (respectively) ini-

tiates a byte write. The address location is latched on the

falling edge of WE (or CE); the new data is latched on the

rising edge. Internally, the device performs a self-clear

before write. Once a byte write has been started, it will

automatically time itself to completion. Once a program-

ming operation has been initiated and for the duration of

t

WC

, a read operation will effectively be a polling operation.

FAST BYTE WRITE: The AT28C64E offers a byte write

time of 200

µs maximum. This feature allows the entire

device to be rewritten in 1.6 seconds.

READY/BUSY: Pin 1 is an open drain RDY/BUSY output

that can be used to detect the end of a write cycle.

RDY/BUSY is actively pulled low during the write cycle and

is released at the completion of the write. The open drain

connection allows for OR-tying of several devices to the

same RDY/BUSY line. The RDY/BUSY pin is not con-

nected for the AT28C64X.

DATA POLLING: The AT28C64 provides DATA Polling to

signal the completion of a write cycle. During a write cycle,

an attempted read of the data being written results in the

complement of that data for I/O

7

(the other outputs are

indeterminate). When the write cycle is finished, true data

appears on all outputs.

WRITE PROTECTION: Inadvertent writes to the device

are protected against in the following ways: (a) V

CC

sense ≠

if V

CC

is below 3.8V (typical) the write function is inhibited;

(b) V

CC

power on delay ≠ once V

CC

has reached 3.8V the

device will automatically time out 5 ms (typical) before

allowing a byte write; and (c) write inhibit ≠ holding any one

of OE low, CE high or WE high inhibits byte write cycles.

CHIP CLEAR: The contents of the entire memory of the

AT28C64 may be set to the high state by the CHIP CLEAR

operation. By setting CE low and OE to 12 volts, the chip is

cleared when a 10 msec low pulse is applied to WE.

D E V I C E I D E N T I F I C A T I O N : A n e x t r a 3 2 b y t e s o f

EEPROM memory are available to the user for device iden-

tification. By raising A9 to 12

± 0.5V and using address

locations 1FE0H to 1FFFH the additional bytes may be

written to or read from in the same manner as the regular

memory array.

AT28C64(X)

4

Notes:

1. X can be V

IL

or V

IH

.

2. Refer to AC programming waveforms.

3. V

H

= 12.0V

±

0.5V.

DC and AC Operating Range

AT28C64-12

AT28C64-15

AT28C64-20

AT28C64-25

Operating

Temperature (Case)

Com.

0∞C - 70∞C

0∞C - 70∞C

0∞C - 70∞C

0∞C - 70∞C

Ind.

-40∞C - 85∞C

-40∞C - 85∞C

-40∞C - 85∞C

-40∞C - 85∞C

V

CC

Power Supply

5V

± 10%

5V

± 10%

5V

± 10%

5V

± 10%

Operating Modes

Mode

CE

OE

WE

I/O

Read

V

IL

V

IL

V

IH

D

OUT

Write

(2)

V

IL

V

IH

V

IL

D

IN

Standby/Write Inhibit

V

IH

X

(1)

X

High Z

Write Inhibit

X

X

V

IH

Write Inhibit

X

V

IL

X

Output Disable

X

V

IH

X

High Z

Chip Erase

V

IL

V

H

(3)

V

IL

High Z

DC Characteristics

Symbol

Parameter

Condition

Min

Max

Units

I

LI

Input Load Current

V

IN

= 0V to V

CC

+ 1V

10

µA

I

LO

Output Leakage Current

V

I/O

= 0V to V

CC

10

µA

I

SB1

V

CC

Standby Current CMOS

CE = V

CC

- 0.3V to V

CC

+ 1.0V

100

µA

I

SB2

V

CC

Standby Current TTL

CE = 2.0V to V

CC

+ 1.0V

Com.

2

mA

Ind.

3

mA

I

CC

V

CC

Active Current AC

f = 5 MHz; I

OUT

= 0 mA

CE = V

IL

Com.

30

mA

Ind.

45

mA

V

IL

Input Low Voltage

0.8

V

V

IH

Input High Voltage

2.0

V

V

OL

Output Low Voltage

I

OL

= 2.1 mA

= 4.0 mA for RDY/BUSY

0.45

V

V

OH

Output High Voltage

I

OH

= -400

µA

2.4

V

AT28C64(X)

5

AC Read Waveforms

(1)(2)(3)(4)

Notes:

1. CE may be delayed up to t

ACC

- t

CE

after the address transition without impact on t

ACC

.

2. OE may be delayed up to t

CE

- t

OE

after the falling edge of CE without impact on t

CE

or by t

ACC

- t

OE

after an address change

without impact on t

ACC

.

3. t

DF

is specified from OE or CE whichever occurs first (C

L

= 5 pF).

4. This parameter is characterized and is not 100% tested.

Input Test Waveforms and

Measurement Level

Output Test Load

Note:

1. This parameter is characterized and is not 100% tested.

AC Read Characteristics

Symbol

Parameter

AT28C64-12

AT28C64-15

AT28C64-20

AT28C64-25

Units

Min

Max

Min

Max

Min

Max

Min

Max

t

ACC

Address to Output Delay

120

150

200

250

ns

t

CE

(1)

CE to Output Delay

120

150

200

250

ns

t

OE

(2)

OE to Output Delay

10

60

10

70

10

80

10

100

ns

t

DF

(3)(4)

CE or OE High to Output Float

0

45

0

50

0

55

0

60

ns

t

OH

Output Hold from OE, CE or

Address, whichever occurred first

0

0

0

0

ns

t

R

, t

F

< 20 ns

Pin Capacitance

f = 1 MHz, T = 25∞C

(1)

Symbol

Typ

Max

Units

Conditions

C

IN

4

6

pF

V

IN

= 0V

C

OUT

8

12

pF

V

OUT

= 0V