Document Outline

- FEATURES

- APPLICATIONS

- EVALUATION TOOLS

- PACKAGE/ORDERING INFORMATION(1)

- ABSOLUTE MAXIMUM RATINGS(1)

- PIN CONFIGURATION

- PIN DESCRIPTION

- TYPICAL CHARACTERISTICS

- FUNCTIONAL DESCRIPTION

- SENSOR ERROR ADJUSTMENT RANGE

- GAIN SCALING

- OFFSET ADJUSTMENT

- VOLTAGE REFERENCE

- SENSOR EXCITATION AND LINEARIZATION

- ADC FOR TEMPERATURE SENSING

- EXTERNAL EEPROM AND TEMPERATURE COEFFICIENTS

- FAULT MONITOR

- OVER-SCALE AND UNDER-SCALE LIMITS

- POWER-UP AND NORMAL OPERATION

- DIGITAL INTERFACE

- DETAILED BLOCK DIAGRAM

FEATURES

D

COMPLETE BRIDGE SENSOR CONDITIONER

D

VOLTAGE OUTPUT: Ratiometric or Absolute

D

DIGITAL CAL: No Potentiometers/Sensor Trims

D

SENSOR ERROR COMPENSATION

- Span, Offset, and Temperature Drifts

D

LOW ERROR, TIME-STABLE

D

SENSOR LINEARIZATION CIRCUITRY

D

TEMPERATURE SENSE: Internal or External

D

CALIBRATION LOOKUP TABLE LOGIC

- Uses External EEPROM (SOT23-5)

D

OVER/UNDER-SCALE LIMITING

D

SENSOR FAULT DETECTION

D

+2.7V TO +5.5V OPERATION

D

-40

∞

C to +125

∞

C OPERATION

D

SMALL TSSOP-16 PACKAGE

APPLICATIONS

D

BRIDGE SENSORS

D

REMOTE 4-20mA TRANSMITTERS

D

STRAIN, LOAD, AND WEIGH SCALES

D

AUTOMOTIVE SENSORS

EVALUATION TOOLS

D

HARDWARE DESIGNER'S KIT (PGA309EVM)

- Temperature Eval of PGA309 + Sensor

- Full Programming of PGA309

- Sensor Compensation Analysis Tool

DESCRIPTION

The PGA309 is a programmable analog signal conditioner

designed for bridge sensors. The analog signal path am-

plifies the sensor signal and provides digital calibration for

zero, span, zero drift, span drift, and sensor linearization

errors with applied stress (pressure, strain, etc.). The cal-

ibration is done via a One-Wire digital serial interface or

through a Two-Wire industry-standard connection. The

calibration parameters are stored in external nonvolatile

memory (typically SOT23-5) to eliminate manual trimming

and achieve long-term stability.

The all-analog signal path contains a 2x2 input multiplex-

er (mux), auto-zero programmable-gain instrumentation

amplifier, linearization circuit, voltage reference, internal

oscillator, control logic, and an output amplifier. Program-

mable level shifting compensates for sensor DC offsets.

The core of the PGA309 is the precision, low-drift, no 1/f

noise Front-End PGA (Programmable Gain Amplifier).

The overall gain of the Front-End PGA + Output Amplifier

can be adjusted from 2.7V/V to 1152V/V. The polarity of

the inputs can be switched through the input mux to ac-

commodate sensors with unknown polarity output. The

Fault Monitor circuit detects and signals sensor burnout,

overload, and system fault conditions.

For detailed application information, see the PGA309

User's Guide (SBOU024), available for download at

www.ti.com.

All trademarks are the property of their respective owners.

PGA309

SBOS292A - DECEMBER 2003 - REVISED AUGUST 2004

Voltage Output

PROGRAMMABLE SENSOR CONDITIONER

PRODUCTION DATA information is current as of publication date. Products

conform to specifications per the terms of Texas Instruments standard warranty.

Production processing does not necessarily include testing of all parameters.

www.ti.com

Copyright

2003-2004, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

semiconductor products and disclaimers thereto appears at the end of this data sheet.

Analog Sensor Linearization

Digital

Temperature

Compensation

Analog Signal Conditioning

Linear

V

OUT

PGA309

Digital Cal

V

EXC

V

S

0

50

psi

P

Ext Temp

Ext Temp

N onlinear

Bridge

Transducer

Linearization

Circuit

Auto-Zero

PGA

Fault

Monitor

Int Temp

Control Register

Interface Circuitry

EEPROM

(SOT23-5)

Ref

T

+125

_

C

-

40

_

C

Over/Under

Scale Limiter

Lin DAC

Temp

ADC

PGA309

SBOS292A - DECEMBER 2003 - REVISED AUGUST 2004

www.ti.com

2

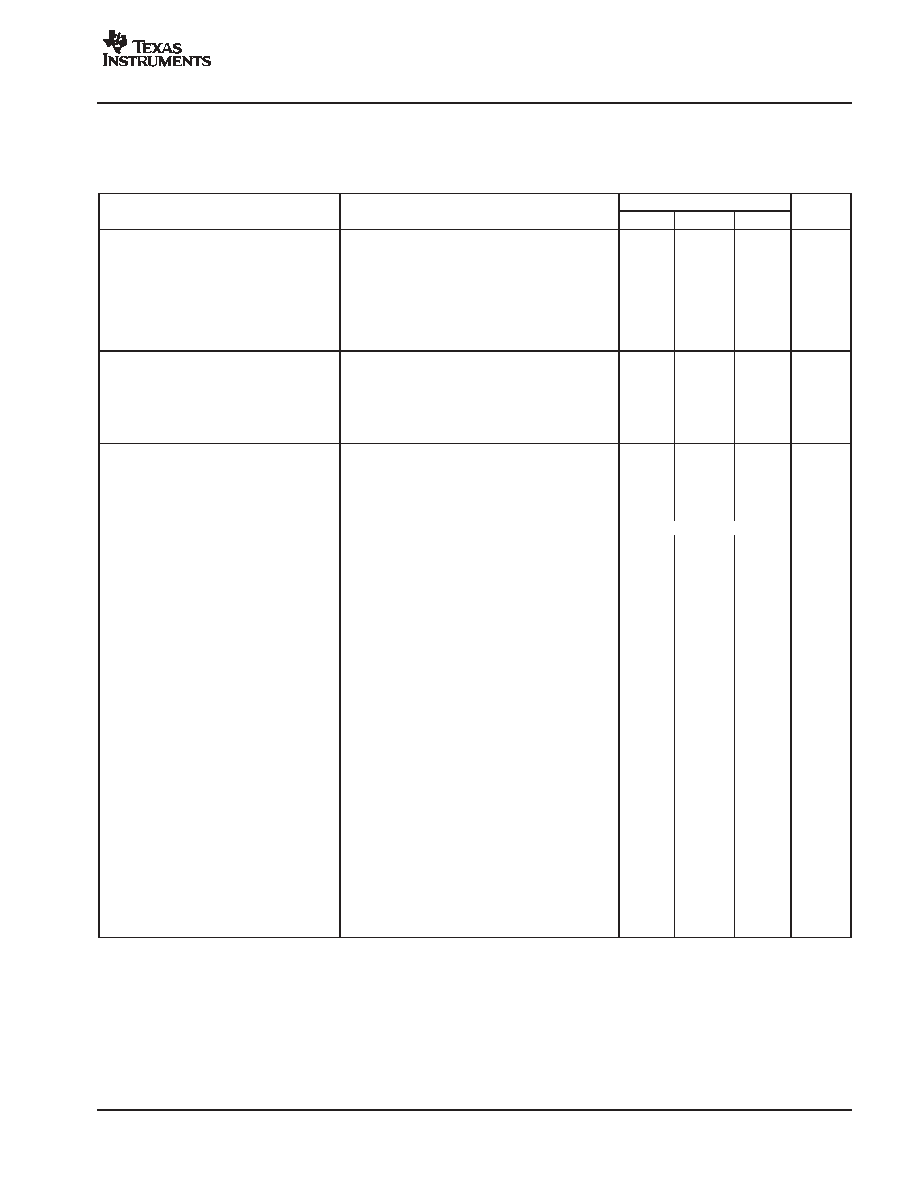

PACKAGE/ORDERING INFORMATION

(1)

PRODUCT

PACKAGE-LEAD

PACKAGE

DRAWING

SPECIFIED

TEMPERATURE

RANGE

PACKAGE

MARKING

ORDERING

NUMBER

TRANSPORT MEDIA,

QUANTITY

PGA309

TSSOP-16

PW

-40

∞

C to +125

∞

C

PGA309

PGA309AIPWR

Tape and Reel, 2500

PGA309

TSSOP-16

PW

-40

∞

C to +125

∞

C

PGA309

PGA309AIPWT

Tape and Reel, 250

(1) For the most current package and ordering information, refer to our web site at www.ti.com.

ABSOLUTE MAXIMUM RATINGS

(1)

Over operating free-air temperature range unless otherwise noted.

Supply Voltage, VSD, VSD

+7.0V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Voltage, VIN1, VIN2(2)

-0.3V to VSA +0.3V

. . . . . . . . . . . . . . . . . . . . .

Input Current, VFB, VOUT

±

150mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Current

±

10mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Current Limit

50mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage Temperature Range

-60

∞

C to +150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . .

Operating Temperature Range

-55

∞

C to +150

∞

C

. . . . . . . . . . . . . . . . . . . . . .

Junction Temperature

+150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead Temperature (soldering, 10s)

+300

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . .

ESD Protection (Human Body Model)

4kV

. . . . . . . . . . . . . . . . . . . . . . . . . . .

(1) Stresses above these ratings may cause permanent damage.

Exposure to absolute maximum conditions for extended periods

may degrade device reliability. These are stress ratings only, and

functional operation of the device at these or any other conditions

beyond those specified is not implied.

(2) Input terminals are diode-clamped to the power-supply rails.

Input signals that can swing more than 0.5V beyond the supply

rails should be current limited to 10mA or less.

This integrated circuit can be damaged by ESD. Texas

Instruments recommends that all integrated circuits be

handled with appropriate precautions. Failure to observe

proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to

complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could

cause the device not to meet its published specifications.

PGA309

SBOS292A - DECEMBER 2003 - REVISED AUGUST 2004

www.ti.com

3

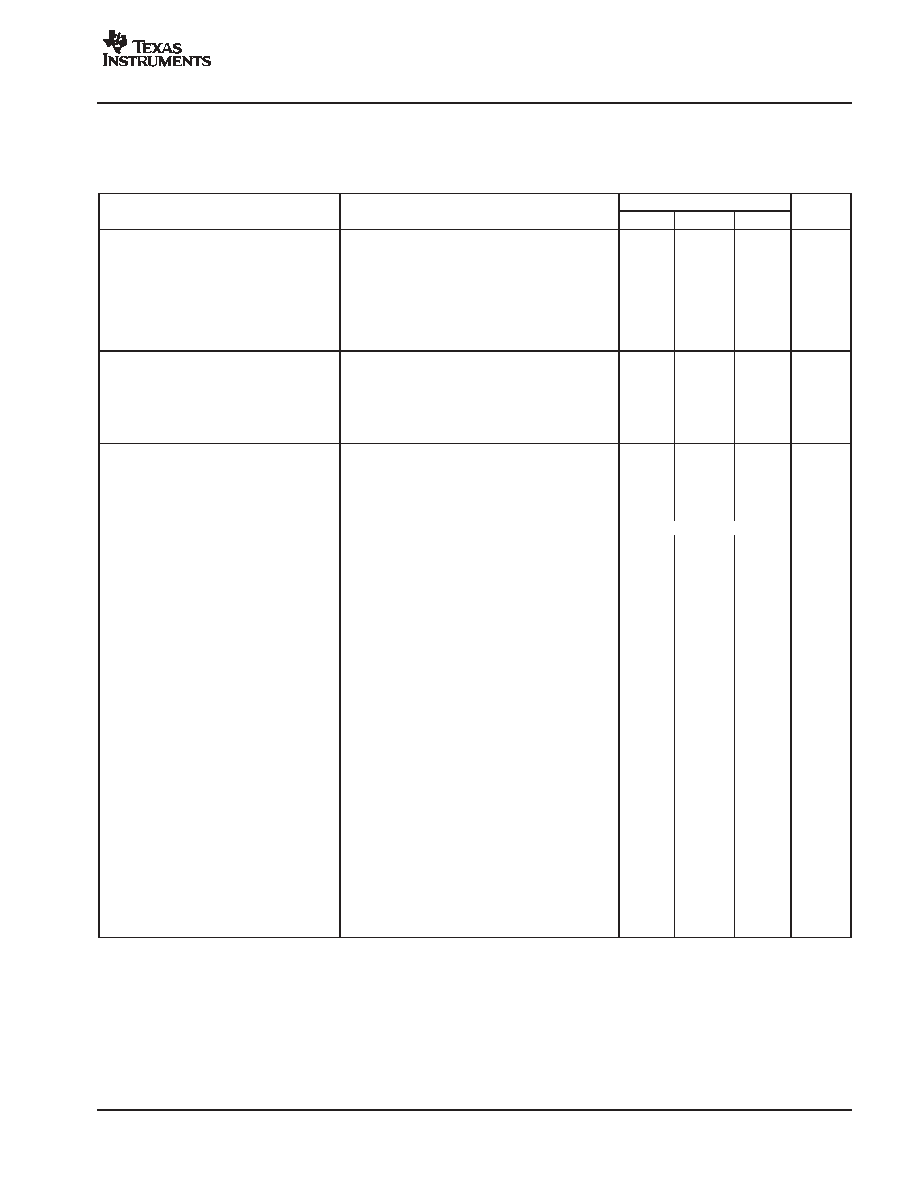

ELECTRICAL CHARACTERISTICS

BOLDFACE limits apply over the specified temperature range: T

A

= -40

∞

C to +125

∞

C

TA = +25

∞

C, VSA = VSD = +5V (VSA = VSUPPLY ANALOG, VSD = VSUPPLY DIGITAL; VSA must equal VSD), GNDD = GNDA = 0, and VREF = REFIN/REFOUT = +5V,

unless otherwise noted.

PGA309

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

FRONT-END PGA + OUTPUT AMPLIFIER

VOUT/VIN Differential Signal Gain Range(1)

Fine Gain Adjust = 1

Front-End PGA Gains: 4, 8, 16, 23.27, 32, 42.67, 64, 128

Output Amplifier Gains: 2, 2.4, 3, 3.6, 4.5, 6, 9

8 to 1152

V/V

VOUT Slew Rate

0.5

V/

µ

s

VOUT Settling Time (0.01%)

VOUT/VIN Differential Gain = 8, RL = 5k

|| 200pF

6

µ

s

VOUT Settling Time (0.01%)

VOUT/VIN Differential Gain = 191, RL = 5k

|| 200pF

4.1

µ

s

VOUT Nonlinearity

0.002

%FSR

External Sensor Output Sensitivity

VSA = VSD = VEXC = +5V

1 to 245

mV/V

FRONT-END PGA

Auto-Zero Internal Frequency

7

kHz

Offset Voltage (RTI)(2)

Coarse Offset Adjust Disabled

±

3

±

50

µ

V

vs Temperature

+

0.2

µ

V/

∞

C

vs Supply Voltage, VSA

±

2

µ

V/V

vs Common-Mode Voltage

GF = Front-End PGA Gain

1500/GF

6000/GF

µ

V/V

Linear Input Voltage Range(3)

0.2

VSA-1.5

V

Input Bias Current

0.1

1.5

nA

Input Impedance: Differential

30 || 6

G

|| pF

Input Impedance: Common-Mode

50 || 20

G

|| pF

Input Voltage Noise

0.1Hz to 10Hz, GF = 128

4

µ

VPP

PGA Gain

Gain Range Steps

4, 8, 16, 23.27, 32, 42.67, 64, 128

4 to 128

V/V

Initial Gain Error

GF = 4 to 42

0.2

±

1

%

GF = 64

0.25

±

1.2

%

GF = 128

0.3

±

1.6

%

vs Temperature

10

ppm/

∞

C

Output Voltage Range

0.05 to VSA - 0.1

V

Bandwidth

Gain = 4

400

kHz

Gain = 128

60

kHz

COARSE OFFSET ADJUST

(RTI OF FRONT-END PGA)

Range

±

(14)(VREF)(0.00085)

±

56

±

59.5

±

64

mV

vs Temperature

0.004

%/

∞

C

Resolution

±

14 steps, 4-Bit + Sign

4

mV

FINE OFFSET ADJUST (ZERO DAC)

(RTO of the Front-End PGA)(2)

Programming Range

0

VREF

V

Output Range

0.1

VSA-0.1

V

Resolution

65,536 steps, 16-Bit DAC

73

µ

V

Integral Nonlinearity

20

LSB

Differential Nonlinearity

0.5

LSB

Gain Error

0.1

%

Gain Error Drift

10

ppm/

∞

C

Offset

5

mV

Offset Drift

10

µ

V/

∞

C

OUTPUT FINE GAIN ADJUST (GAIN DAC)

Range

0.33 to 1

V/V

Resolution

65,536 steps, 16-Bit DAC

10

µ

V/V

Integral NonLinearity

20

LSB

Differential NonLinearity

0.5

LSB

PGA309

SBOS292A - DECEMBER 2003 - REVISED AUGUST 2004

www.ti.com

4

ELECTRICAL CHARACTERISTICS (continued)

BOLDFACE limits apply over the specified temperature range: T

A

= -40

∞

C to +125

∞

C

TA = +25

∞

C, VSA = VSD = +5V (VSA = VSUPPLY ANALOG, VSD = VSUPPLY DIGITAL; VSA must equal VSD), GNDD = GNDA = 0, and VREF = REFIN/REFOUT = +5V,

unless otherwise noted.

PGA309

PARAMETER

UNITS

MAX

TYP

MIN

CONDITIONS

OUTPUT AMPLIFIER

Offset Voltage (RTI of Output Amplifier)(2)

3

mV

vs Temperature

5

µ

V/

∞

C

vs Supply Voltage, VSA

30

µ

V/V

Common-Mode Input Range

0

VSA-1.5

V

Input Bias Current

100

pA

Amplifier Internal Gain

Gain Range Steps

2, 2.4, 3, 3.6, 4.5, 6, 9

2 to 9

V/V

Initial Gain Error

2, 2.4, 3.6

0.25

±

1

%

4.5

0.3

±

1.2

%

6

0.4

±

1.5

%

9

0.6

±

2.0

%

vs Temperature

2, 2.4, 3.6

5

ppm/

∞

C

4.5

5

ppm/

∞

C

6

15

ppm/

∞

C

9

30

ppm/

∞

C

Output Voltage Range(4)

RL = 10k

0.1

4.9

V

Open Loop Gain

115

dB

Gain-Bandwidth Product

2

MHz

Phase Margin

Gain = 2, CL = 200pF

45

Degrees

Output Resistance

AC Small-Signal, Open-Loop, f = 1MHz, IO = 0

675

OVER- AND UNDER-SCALE LIMITS

(VREF = 4.096)

Over-Scale Thresholds

Ratio of VREF, Register 5--Bits D5, D4, D3 = `000'

0.9708

Ratio of VREF, Register 5--Bits D5, D4, D3 = `001'

0.9610

Ratio of VREF, Register 5--Bits D5, D4, D3 = `010'

0.9394

Ratio of VREF, Register 5--Bits D5, D4, D3 = `011'

0.9160

Ratio of VREF, Register 5--Bits D5, D4, D3 = `100'

0.9102

Ratio of VREF, Register 5--Bits D5, D4, D3 = `101'

0.7324

Ratio of VREF, Register 5--Bits D5, D4, D3 = `110'

0.5528

Over-Scale Comparator Offset

+6

+60

+114

mV

Over-Scale Comparator Offset Drift

+0.37

mV/

∞

C

Under-Scale Thresholds

Ratio of VREF, Register 5--Bits D2, D1, D0 = `111'

0.0605

Ratio of VREF, Register 5--Bits D2, D1, D0 = `110'

0.0547

Ratio of VREF, Register 5--Bits D2, D1, D0 = `101'

0.0507

Ratio of VREF, Register 5--Bits D2, D1, D0 = `100'

0.0449

Ratio of VREF, Register 5--Bits D2, D1, D0 = `011'

0.0391

Ratio of VREF, Register 5--Bits D2, D1, D0 = `010'

0.0352

Ratio of VREF, Register 5--Bits D2, D1, D0 = `001'

0.0293

Ratio of VREF, Register 5--Bits D2, D1, D0 = `000'

0.0254

Under-Scale Comparator Offset

-7

-50

+93

mV

Under-Scale Comparator Offset Drift

-0.15

mV/

∞

C

FAULT MONITOR CIRCUIT

INP_HI, INN_HI Comparator Threshold

See Note 5

VSA-1.2 or VEXC-0.1

V

INP_LO, INN_LO Comparator Threshold

40

100

mV

A1SAT_HI, A2SAT_HI Comparator Threshold

VSA-0.12

V

A1SAT_LO, A2SAT_LO Comparator Threshold

VSA-0.12

V

A3_VCM Comparator Threshold

VSA-1.2

V

Comparator Hysteresis

20

mV

PGA309

SBOS292A - DECEMBER 2003 - REVISED AUGUST 2004

www.ti.com

5

ELECTRICAL CHARACTERISTICS (continued)

BOLDFACE limits apply over the specified temperature range: T

A

= -40

∞

C to +125

∞

C

TA = +25

∞

C, VSA = VSD = +5V (VSA = VSUPPLY ANALOG, VSD = VSUPPLY DIGITAL; VSA must equal VSD), GNDD = GNDA = 0, and VREF = REFIN/REFOUT = +5V,

unless otherwise noted.

PGA309

PARAMETER

UNITS

MAX

TYP

MIN

CONDITIONS

INTERNAL VOLTAGE REFERENCE

VREF1

Register 3, Bit D9 = 1

2.46

2.5

2.53

V

VREF1 Drift vs Temperature

+10

ppm/

∞

C

VREF2

Register 3, Bit D9 = 0

4.0

4.096

4.14

V

VREF2 Drift vs Temperature

+10

ppm/

∞

C

Input Current REFIN/REFOUT

Internal VREF Disabled

100

µ

A

Output Current REFIN/REFOUT

VSA > 2.7V for VREF = 2.5V

1

mA

VSA > 4.3V for VREF = 4.096V

1

mA

TEMPERATURE SENSE CIRCUITRY (ADC)

Internal Temperature Measurement

Register 6, Bit D9 = 1

Accuracy

±

2

∞

C

Resolution

12-Bit + Sign, Two's Complement Data Format

±

0.0625

∞

C

Temperature Measurement Range

-55

+150

∞

C

Conversion Rate

R1, R0 = `11', 12-Bit + Sign Resolution

24

ms

TEMPERATURE ADC

External Temperature Mode

Temp PGA + Temp ADC

Gain Range Steps

GPGA = 1, 2, 4, 8

1 to 8

V/V

Analog Input Voltage Range

GND-0.2

VSA+0.2

V

Temperature ADC Internal REF (2.048V)

Register 6, Bit D8 = 1

Full-Scale Input Voltage

(+Input) - (-Input)

±

2.048/GPGA

V

Differential Input Impedance

2.8/GPGA

M

Common-Mode Input Impedance

G

PGA

= 1

3.5

M

G

PGA

= 2

3.5

M

G

PGA

= 4

1.8

M

G

PGA

= 8

0.9

M

Resolution

R1, R0 = `00', ADC2X = `0', Conversion Time = 8ms

11

Bits + Sign

R1, R0 = `01', ADC2X = `0', Conversion Time = 32ms

13

Bits + Sign

R1, R0 = `10', ADC2X = `0', Conversion Time = 64ms

14

Bits + Sign

R1, R0 = `11', ADC2X = `0', Conversion Time = 128ms

15

Bits + Sign

Integral Nonlinearity

0.004

%

Offset Error

G

PGA

= 1

1.2

mV

G

PGA

= 2

0.7

mV

G

PGA

= 4

0.5

mV

G

PGA

= 8

0.4

mV

Offset Drift

G

PGA

= 1

1.2

µ

V/

∞

C

G

PGA

= 2

0.6

µ

V/

∞

C

G

PGA

= 4

0.3

µ

V/

∞

C

G

PGA

= 8

0.3

µ

V/

∞

C

Offset vs VSA

G

PGA

= 1

800

µ

V/V

G

PGA

= 2

400

µ

V/V

G

PGA

= 4

200

µ

V/V

G

PGA

= 8

150

µ

V/V

Gain Error

0.05

0.50

%

Gain Error Drift

5

50

ppm/

∞

C

Noise

All Gains

< 1

LSB

Gain vs VSA

80

ppm/V

Common-Mode Rejection

At DC and

G

PGA

= 8

105

dB

At DC and

G

PGA

= 1

100

dB