Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

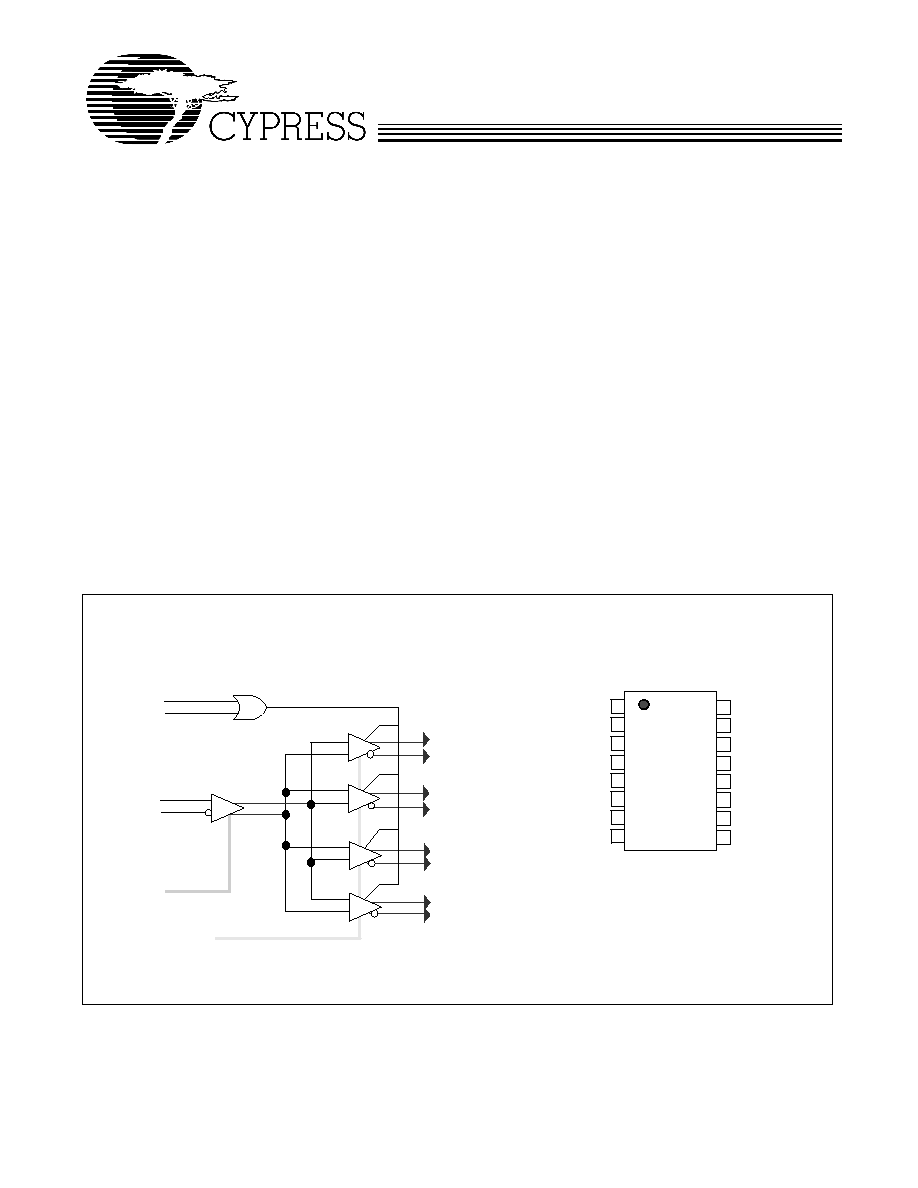

1:4 Clock Fanout Buffer

ComLinkTM Series

CY2DL814

Cypress Semiconductor Corporation

·

3901 North First Street

·

San Jose

·

CA 95134

·

408-943-2600

Document #: 38-07057 Rev. *A

Revised December 14, 2002

Features

· Low-voltage operation

· V

DD

= 3.3V

· 1:4 Fanout

· Single-input configurable for

-- LVDS, LVPECL, or LVTTL

-- Four differential pairs of LVDS outputs

· Drives 50- or 100-ohm load (selectable)

· Low input capacitance

· Low output skew

· Does not exceed Bellcore 802.3 standards

· Operation at

350 MHz 700 Mbps

· Low propagation delay Typical (tpd < 4 ns)

· Industrial versions available

· Packages available include TSSOP/SOIC

Description

The Cypress CY2 series of network circuits is produced using

advanced 0.35-micron CMOS technology, achieving the

industry's fastest logic.

The Cypress CY2DL814 fanout buffer features a single

LVDS-, LVPECL-, or LVTTL-compatible input and four LVDS

output pairs.

Designed for data-communication clock management applica-

tions, the fanout from a single input reduces loading on the

input clock.

The CY2DL814 is ideal for both level translations from single

ended to LVDS and/or for the distribution of LVDS-based clock

signals. The Cypress CY2DL814 has configurable input and

output functions. The input can be selectable for

LVPECL/LVTTL or LVDS signals while the output driver's

support standard and high drive LVDS. Drive either a 50-ohm

or 100-ohm line with a single part number/device.

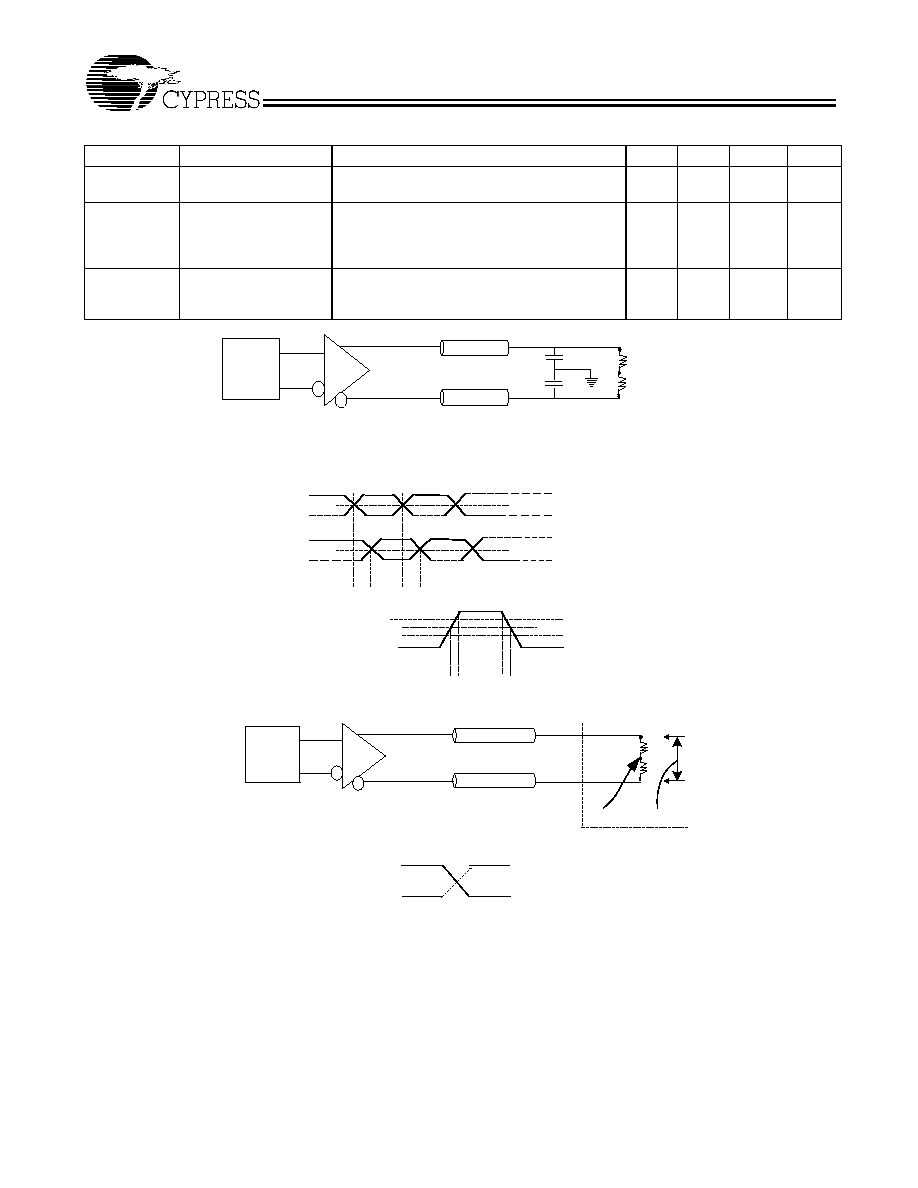

Block Diagram

Pin Configuration

OUTPUT

IN+

IN-

Q1A

Q1B

Q2A

Q2B

Q4A

Q4B

Q3A

Q3B

CNTRL

LVDS /

LVPECL /

LVTTL

CONFIG

EN1

EN2

LVDS

C

Y

2DL

814

16-pin TSSOP/SOIC

EN1

CONFIG

CNTRL

VDD

IN+

IN-

EN2

GND

Q1A

Q1B

Q2A

Q2B

Q3A

Q3B

Q4A

Q4B

1

2

3

4

5

6

7

8

10

9

11

12

13

14

15

16

ComLinkTM Series

CY2DL814

Document #: 38-07057 Rev. *A

Page 2 of 8

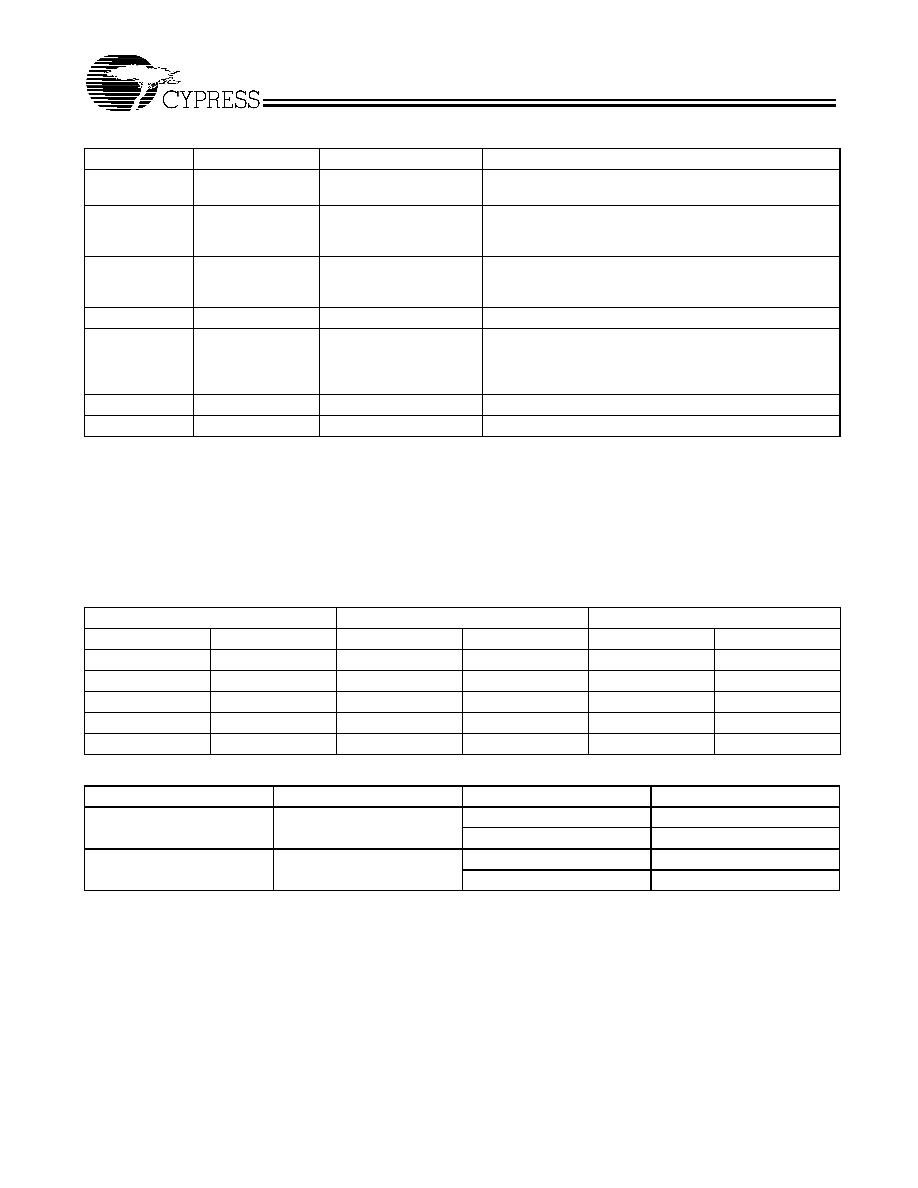

Maximum Ratings

[1][2]

Storage Temperature: ................................65

°

C to + 150

°

C

Ambient Temperature:................................... 40

°

C to +85

°

C

Supply Voltage to Ground Potential

(Inputs and V

CC

only)....................................... 0.3V to 4.6V

Supply Voltage to Ground Potential

(Outputs only) ........................................ 0.3V to V

DD

+ 0.3V

DC Input Voltage ................................... 0.3V to V

DD

+ 0.3V

DC Output Voltage................................. 0.3V to V

DD

+ 0.9V

Power Dissipation........................................................ 0.75W

Note:

1.

Stresses greater than those listed under absolute maximum ratings may cause permanent damage to the device. This is intended to be a stress rating only and

functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure

to absolute maximum rating conditions for extended periods may affect reliability.

2.

Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

Pin Description

Pin Number

Pin Name

Pin Standard Interface

Description

6,7

IN+, IN

Configurable

Differential input pair or single line.

LVPECL default. See config below.

3

CNTRL

LVTTL/LVCMOS

Converts into a High drive driver from a standard LVDS.

Standard drive (logic = 0)

B/High drive/Bus (logic = 1)

2

CONFIG

LVTTL/LVCMOS

Converts inputs (IN

+

/IN

), (EN, EN#) from the default

LVPECL/LVDS (logic = 0)

To LVTTL/LVCMOS (logic = 1)

1,8

EN1, EN2

LVTTL/LVCMOS

Enable/disable logic. See Table 1 below for details.

16,15,14,13

12,11,10,9

Q1A, Q1B, Q2A,

Q2B,

Q3A, Q3B, Q4A,

Q4B

LDVS

Differential outputs.

4

V

DD

POWER

Positive supply voltage

5

G

ND

POWER

Ground

Table 1. EN1 EN2 Function TableDifferential Input Mode

Enable Logic

Input

Outputs

EN1

EN2

IN+

IN

QnA

QnB

H

X

H

L

H

L

H

X

L

H

L

H

X

L

H

L

H

L

X

L

L

H

L

H

L

H

X

X

Z

Z

Table 2. Output Drive Control for Standard and Bus/B/High Drive B

CNTRL Pin 3 Binary Value

Drive STD

Impedance

Output Voltage Value

0

Standard

100 ohm

V0 = Voutput

50 ohm

V = 1/2 * V0

1

High Drive/Bus/B

100 ohm

V = 2 * V0

50 ohm

V = V0

ComLinkTM Series

CY2DL814

Document #: 38-07057 Rev. *A

Page 3 of 8

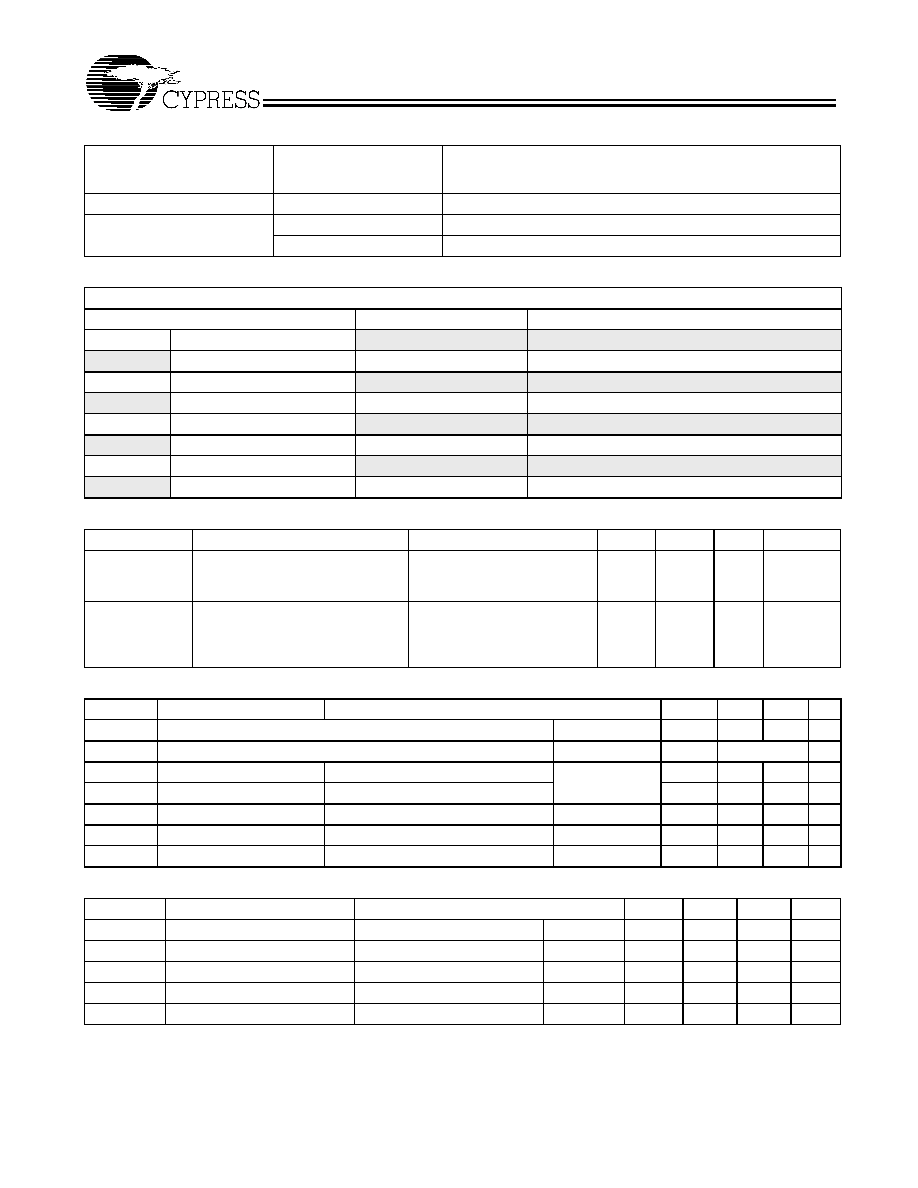

Table 3. Input Receiver Configuration for Differential or LVTTL/LVCMOS

CONFIG

Pin 2

Binary Value

Input Receiver Family

Input Receiver Type

1

LVTTL in LVCMOS

Single-ended, Non-inverting, Inverting, Void of Bias Resistors

0

LVDS

Low-voltage Differential Signaling

LVPECL

Low-voltage Pseudo (Positive) Emitter Coupled Logic

Table 4. Function Control of the TTL Input Logic Used to Accept or Invert the Input Signal

LVTTL/LVCMOS Input Logic

Input Condition

Input Logic

Output Logic Q Pins, Q1A or Q1

Ground

IN Pin 7

IN+ Pin 6

Input

True

V

CC

IN Pin 7

IN+ Pin 6

Input

Invert

Ground

IN+ Pin 6

IN Pin 7

Input

True

V

CC

IN+ Pin 6

IN Pin 7

Input

Invert

Table 5. Power Supply Characteristics

Parameter

Description

Test Conditions

Min.

Typ.

Max.

Unit

I

CCD

Dynamic Power Supply Current

V

DD

= Max.

Input toggling 50% Duty Cycle,

Outputs Open

1.5

2.0

mA/MHz

I

C

Total Power Supply Current

V

DD

= Max.

Input toggling 50% Duty Cycle,

Outputs Open

fL=100 MHz

90

100

mA

Table 6. D.C Electrical Characteristics: 3.3VLVDS Input

Parameter

Description

Conditions

Min.

Typ.

Max. Unit

V

ID

Magnitude of Differential Input Voltage

100

600

mV

V

IC

Common-mode of Differential Input Voltage IV

ID

I (min. and max.)

IVIDI/2

2.4(IVIDI/2)

V

V

IH

Input High Voltage

Guaranteed Logic High Level

Config/Cntrl Pins

2

V

V

IL

Input Low Voltage

Guaranteed Logic Low Level

0.8

V

I

IH

Input High Current

V

DD

= Max.

V

IN

= V

DD

±10

±20

µ

A

I

IL

Input Low Current

V

DD

= Max.

V

IN

= V

SS

±10

±20

µ

A

I

I

Input High Current

V

DD

= Max., V

IN

= V

DD

(max.)

±20

µ

A

Table 7. D.C Electrical Characteristics: 3.3VLVPECL Input

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

V

ID

Differential Input Voltage p-p

Guaranteed Logic High Level

400

2600

mV

V

CM

Common-mode Voltage

1.65

2.25

V

I

IH

Input High Current

V

DD

= Max.

V

IN

= V

DD

±10

±20

µ

A

I

IL

Input Low Current

V

DD

= Max.

V

IN

= V

SS

±10

±20

µ

A

I

I

Input High Current

V

DD

= Max., V

IN

= V

DD

(Max.)

±20

µ

A

ComLinkTM Series

CY2DL814

Document #: 38-07057 Rev. *A

Page 4 of 8

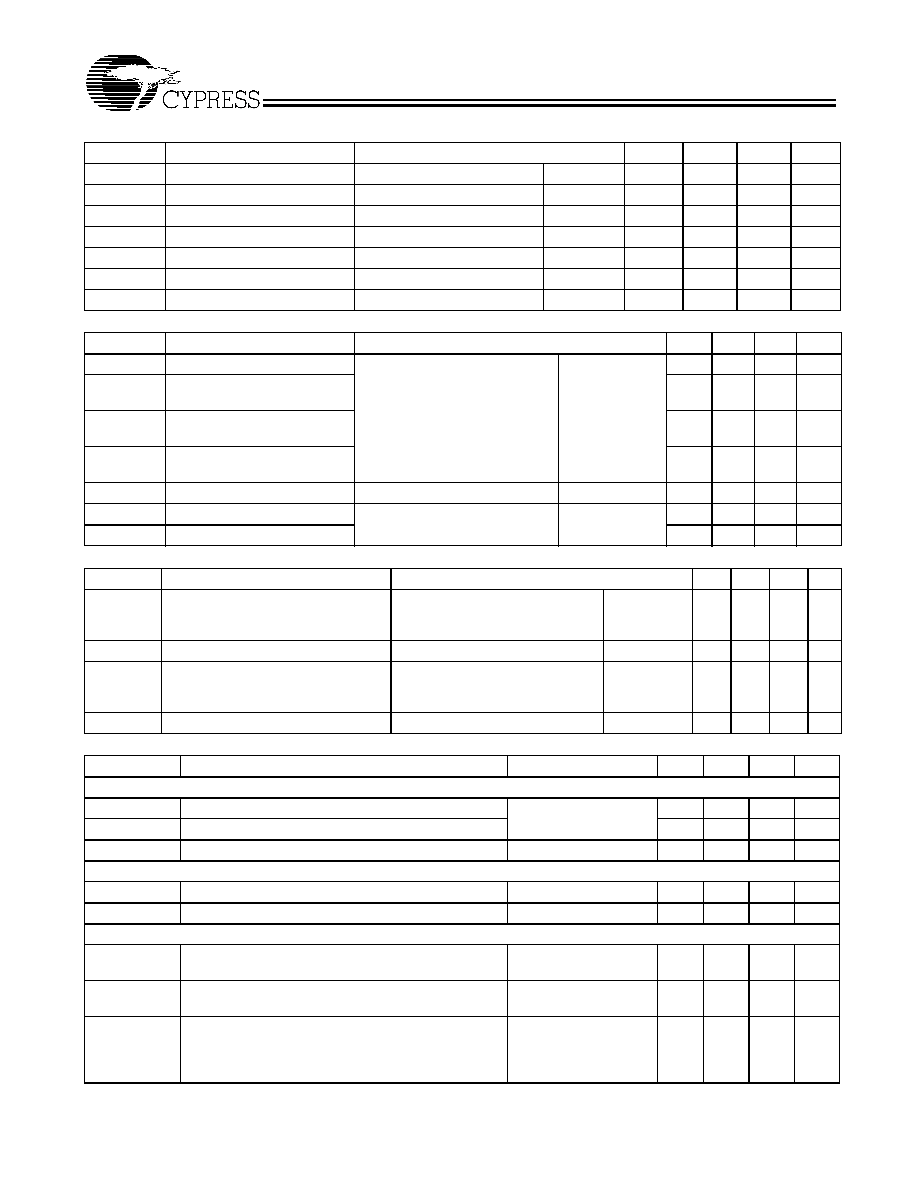

Table 8. D.C Electrical Characteristics: 3.3VLVTTL/LVCMOS Input

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

V

IH

Input High Voltage

Guaranteed Logic High Level

2

V

V

IL

Input Low Voltage

Guaranteed Logic Low Level

0.8

V

I

IH

Input High Current

V

DD

= Max.

V

IN

= 2.7V

1

µ

A

I

IL

Input Low Current

V

DD

= Max.

V

IN

= 0.5V

1

µ

A

I

I

Input High Current

V

DD

= Max.,

V

IN

=

V

DD

(Max.)

20

µ

A

V

IK

Clamp Diode Voltage

V

DD

= Min.,

I

IN = 18 mA

0.7

1.2

V

V

H

Input Hysteresis

80

mV

Table 9. D.C Electrical Characteristics: 3.3VLVDS OUTPUT

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

I V

OD

I

Differential output voltage p-p

V

DD

= 3.3V, V

IN

= V

IH

, or V

IL

RL = 100 ohm

0.25

0.45

V

VOC(SS)

Steady-state common-mode

output voltage

226

mV

Delta

VOC(SS)

Change in VOC(SS) between

logic states

50

3

50

mV

VOC(PP)

Peak to peak common mode

output voltage

150

mV

I

OS

Output short circuit

QA = 0V or QB = 0V

20

mA

Voh

Output voltage high

RL = 100 ohm

1475

mV

Vol

Output voltage low

925

mV

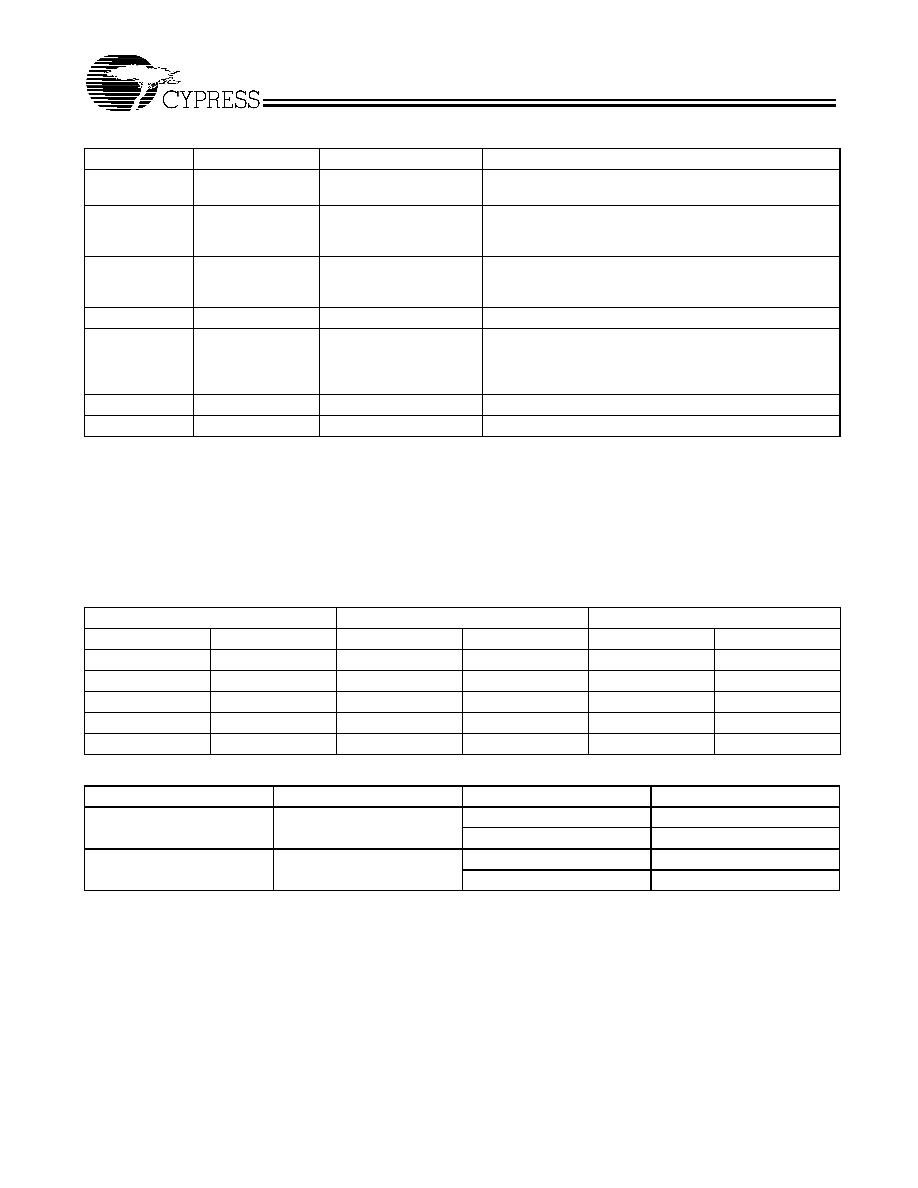

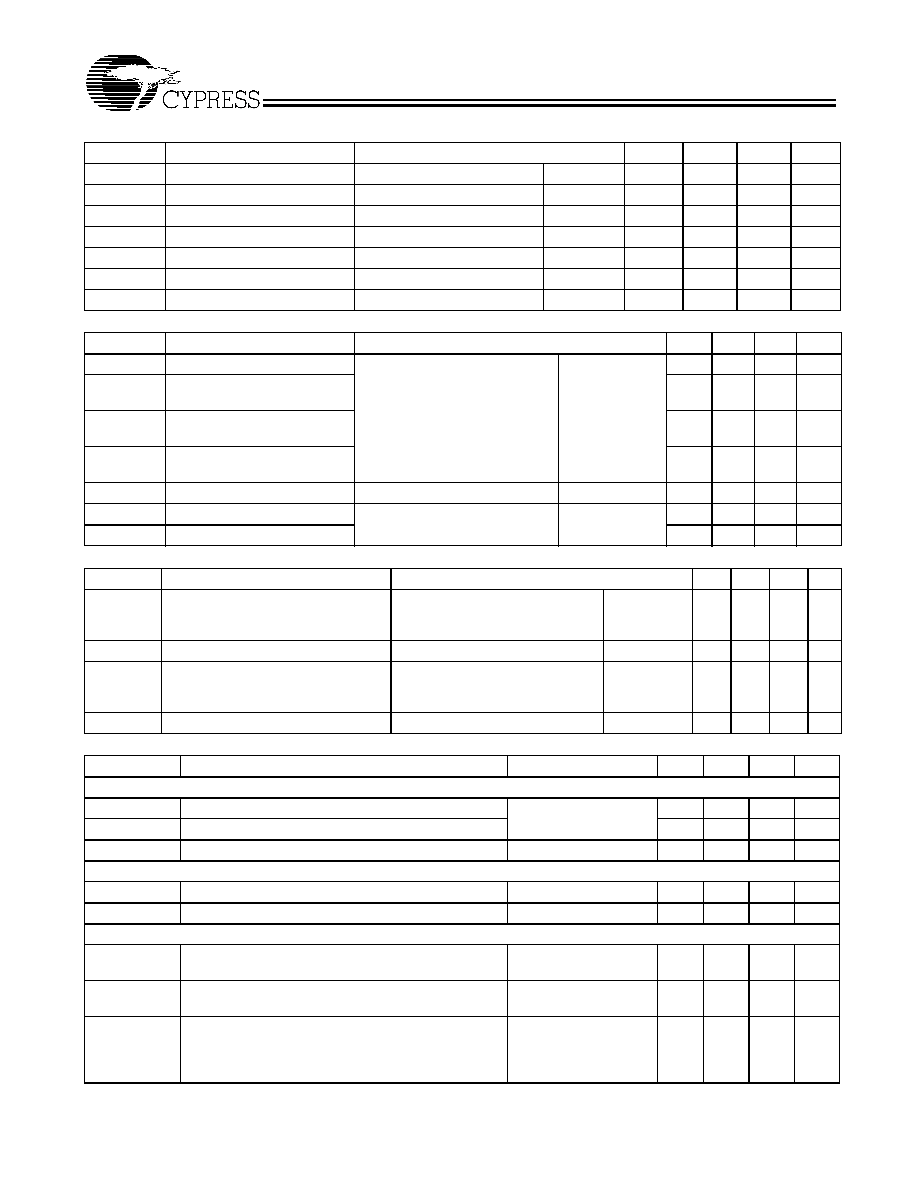

Table 10. AC Parameters

Parameter

Description

Conditions

Min. Typ. Max. Unit

Rise Time

Pin control (pin 3) logic is "FALSE"

defaulting to 100 ohm output drivers.

Differential 20% to 80%

CL10 pF

RL and CL to G

ND

3 CL = C

intrinsic

and C

external

RL = 100 ohm

1.4

ns

Fall Time

1.4

ns

Rise Time

Pin control (pin 3) logic is "True"

defaulting to 50 ohm output drivers.

Differential 20% to 80%

CL10 pF

RL and CL to G

ND

3 CL = C

intrinsic

and C

external

RL = 50 ohm

Output boost

350

600

ps

Fall Time

350

600

ps

Table 11. AC Switching Characteristics @ 3.3 V (V

DD

= 3.3V ±5%, Temperature = 40°C to +85°C)

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

IN [+,-] to Q[A,B] Data and Clock Speed

t

PLH

Propagation Delay Low to High

V

OD

= 100 mV

3

4

5

ns

t

PHL

Propagation Delay High to Low

3

4

5

ns

T

pd

Propagation Delay

3

4

5

ns

IN [1,2] to Q[A,B] Control Speed

T

Pe

Enable (EN) to functional operation

6

ns

T

pd

Functional operation to Disable

5

ns

Q[A,B] Output Skews

t

SK(0)

Output Skew: Skew between outputs of the same

package (in phase)

0.2

ns

t

SK(p)

Pulse Skew: Skew between opposite transitions of the

same output (t

PHL

t

PLH

)

0.2

ns

t

SK(t)

Package Skew: Skew between outputs of different

packages at the same power supply voltage, temper-

ature and package type. Same input signal level and

output load.

V

ID

= 100 mV

1

ns

ComLinkTM Series

CY2DL814

Document #: 38-07057 Rev. *A

Page 5 of 8

Notes:

3.

All input pulses are supplied by a frequency generator with the following characteristics: t

R

and t

F

1 ns; pulse rerate = 50 Mpps; pulse width = 10 ± 0.2 ns.

4.

RL= 50 ohm ± 1% Zline = 50 ohm 6".

5.

CL includes instrumentation and fixture capacitance within 6 mm of the UT.

6.

TPA and B are used for prop delay and Rise/Fall measurements. TPC is used for VOC measurements only and is otherwise connected to V

DD- 2

.

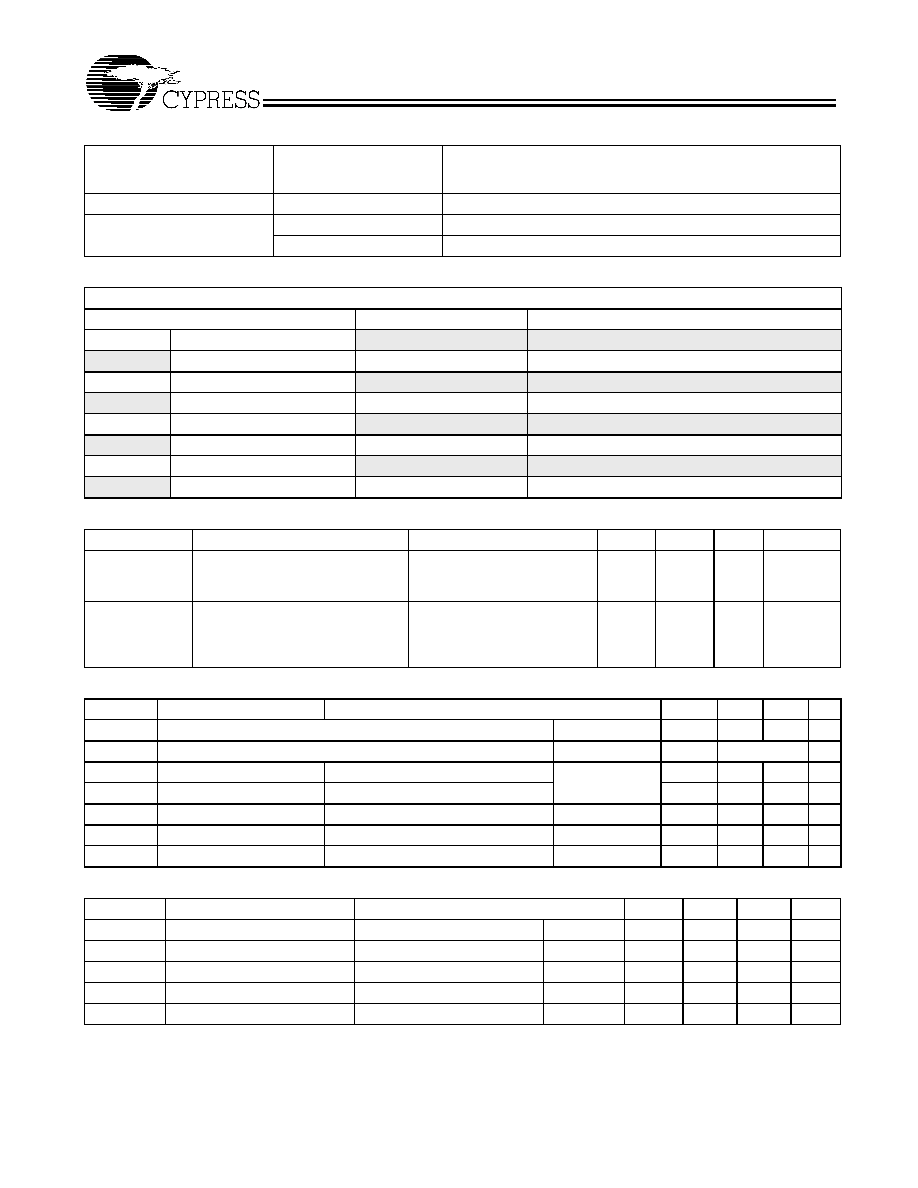

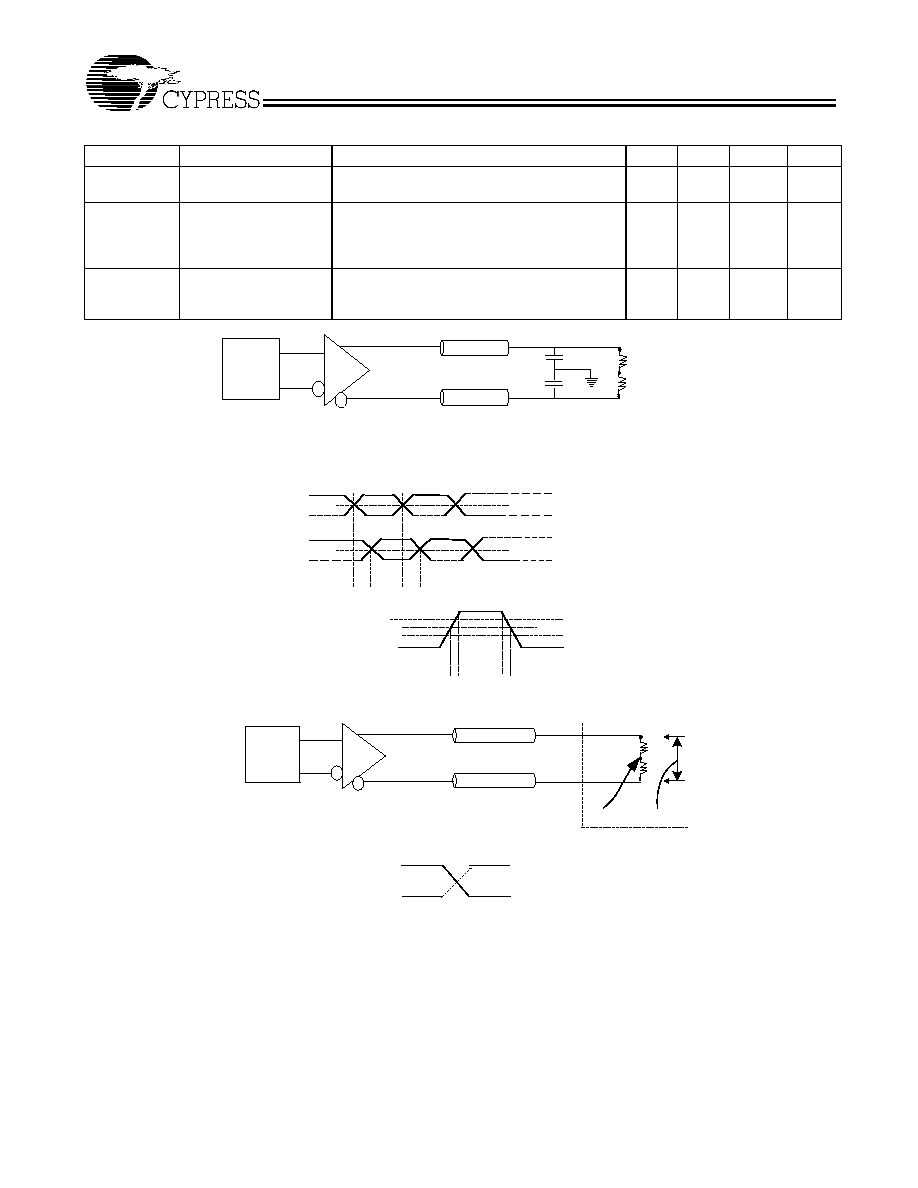

Table 12. High Frequency Parametrics

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

Fmax

Maximum frequency

V

DD

= 3.3V

50% duty cycle tW(5050)

Standard Load Circuit.

400

MHz

Fmax(20)

Maximum frequency

V

DD

= 3.3 V

20% duty cycle tW(5050)

LVPECL Input

V

IN

= V

IH

(Max.)/V

IL

(Min.)

V

OUT

= V

OH

(Min.)/V

OL

(Max.) (Limit)

200

MHz

TW

Minimum pulse

V

DD

= 3.3 V

LVPECL Input

V

IN

= V

IH

(Max.)/V

IL

(Min.) F= 100 MHz

V

OUT

= V

OH

(Min.)/V

OL

(Max.)(Limit)

1 ns

80%

20%

0V Differential

V0Y - V0Z

tR

tF

1.4 V

1.0 V

1.4 V

1.0 V

0V Differential

0V Differential

1.2 V CM

1.2 V CM

V1A

V1B

V0Y

V0Z

T

PLH

T

PHL

TPA

TPC

TPB

50

50

Standard Termination

Pulse

Generator

A

B

10pF

Figure 1. Differential Receiver to Driver Propagation Delay and Driver Transition Time

[3,4,5,6]

2.0V

1.6V

V

I(A)

V

I(B)

Next Device

VOD

VOC

TPA

TPC

TPB

50

50

Standard Termination

Pulse

Generator

A

B

Figure 2. Test Circuit and Voltage Definitions for the Driver Common-mode Output Voltage

[3,4,5,6]