9 Megabit CMOS SRAM

DPS256X36L

FEATURES:

∑

Configuration: 1Meg x 9, 512K x 18, 256K x 36

∑

Access Times: 20, 25, 30, 35, 45ns

∑

Fully Static Operation - No Clock or Refresh Required

∑

2-Volt Data Retention

∑

All inputs and Outputs are TTL-Compatible

∑

68 Pin FR-4 ZIP Module

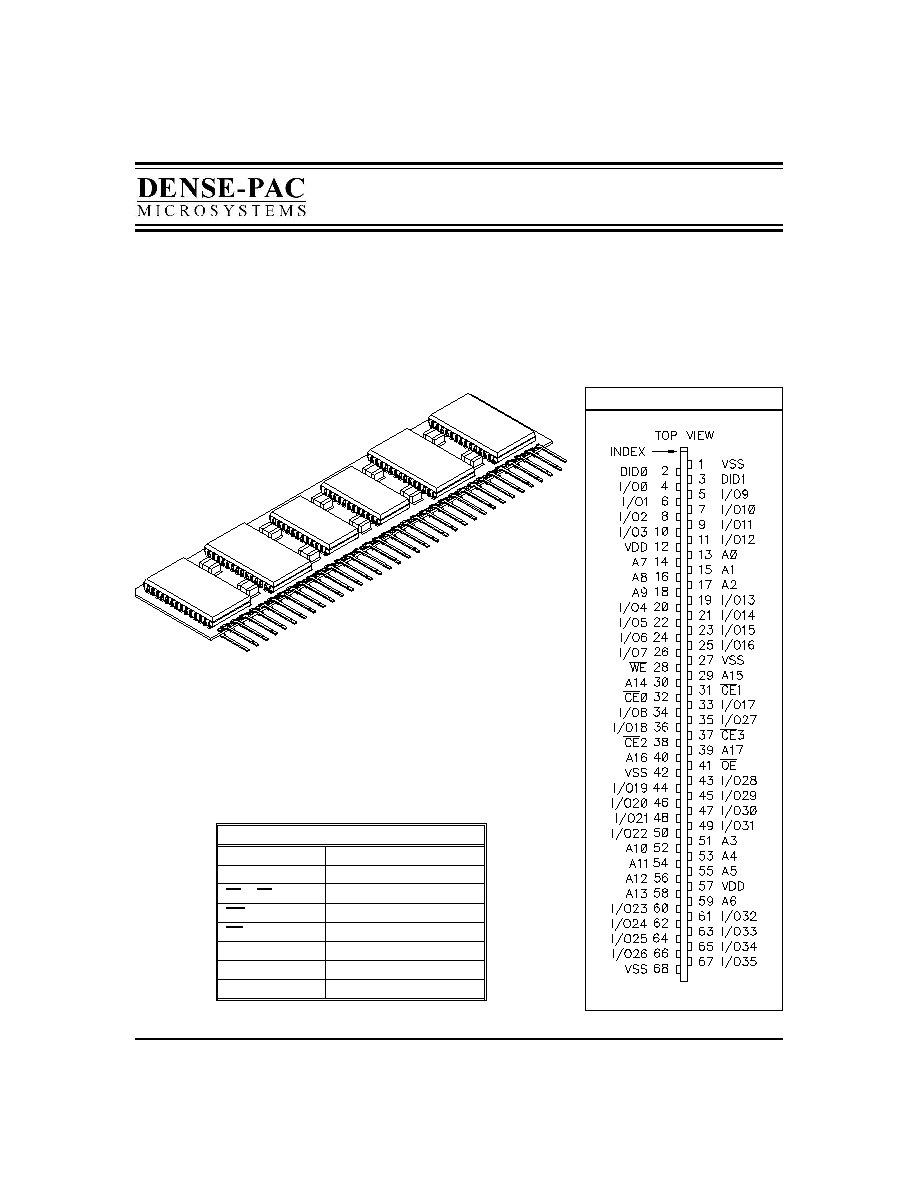

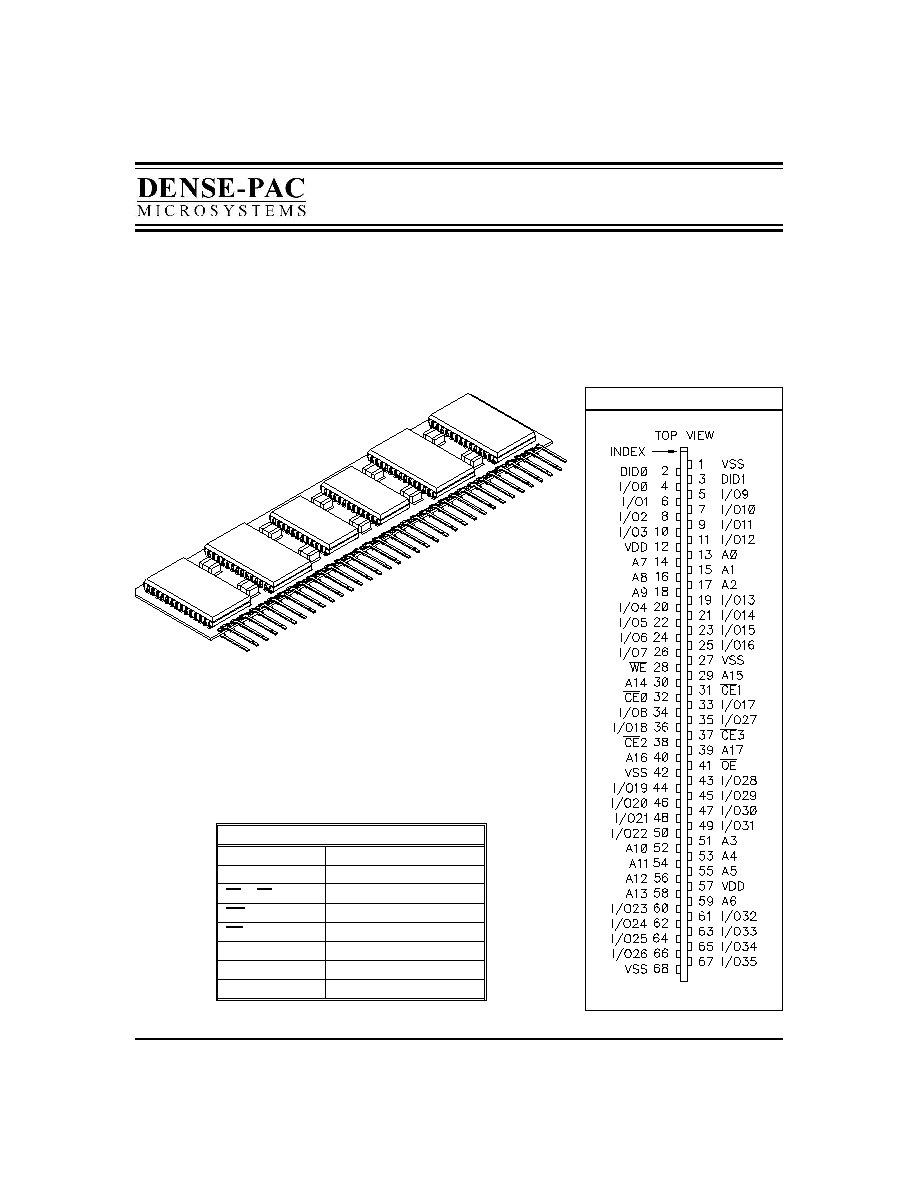

PIN-OUT DIAGRAM

DESCRIPTION:

The DPS256X36L is a 256K X 36 high-density,

low-power static RAM module comprised of eight

256K X 4 and four 256K x 1 monolithic SRAM's and

decoupling capacitors surface mounted on a FR-4

ZIP substrate.

The DPS256X36L operates from a single +5V

supply and all input and output pins are completely

TTL-compatible. The low standby power of the

DPS256X36L make it ideal for battery-backed

applications.

1Mx9/512Kx18/256Kx36, 20 - 45ns, ZIP

30A112-00

A

This document contains information on a product that is currently released

to production at Dense-Pac Microsystems, Inc. Dense-Pac reserves the

right to change products or specifications herein without prior notice.

PIN NAMES

A0 - A17

Address Inputs

I/O0 - I/O35

Data Input/Output

CE0 - CE3

Chip Enables

WE

Write Enable

OE

Output Enable

V

DD

Power (+5.0V)

V

SS

Ground

N.C.

No Connect

30A112-00

REV. A

1

DPS256X36L

Dense-Pac Microsystems, Inc.

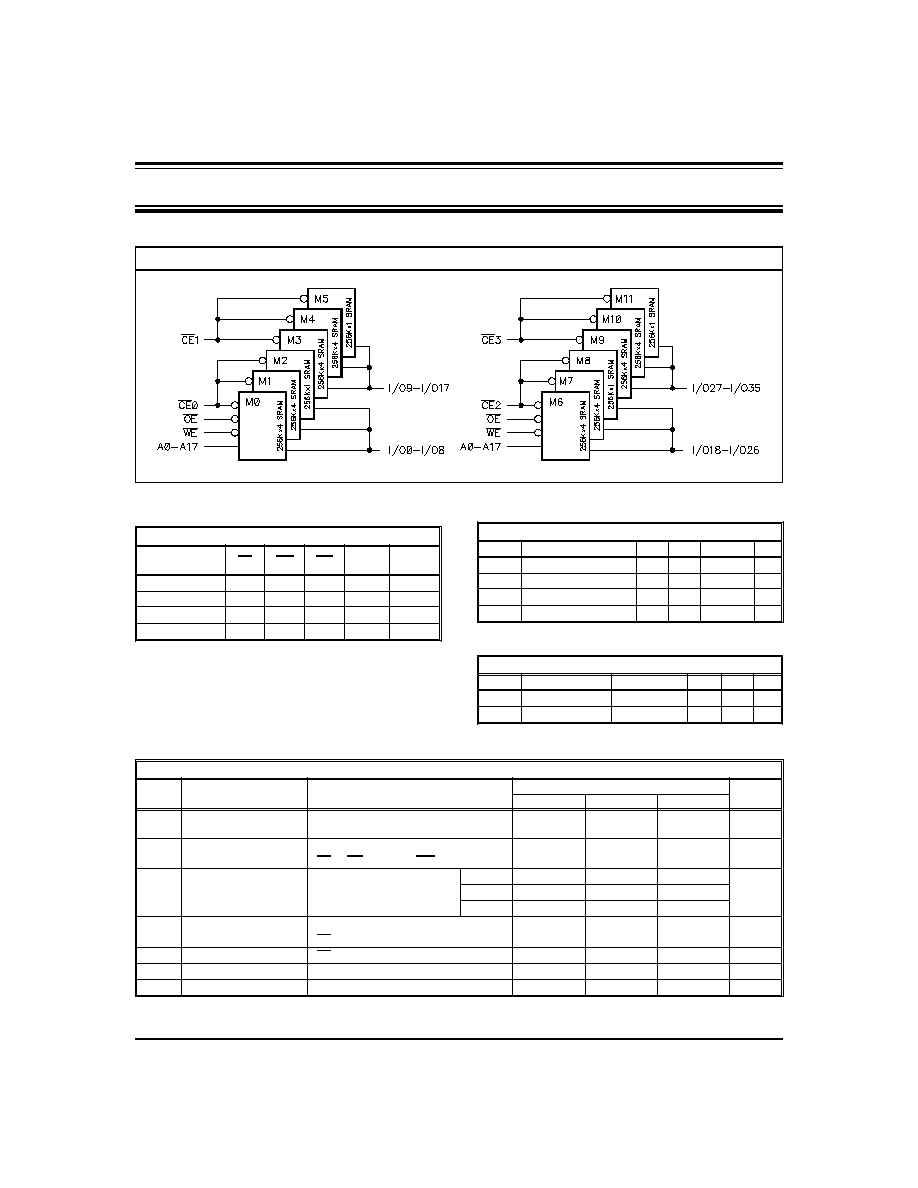

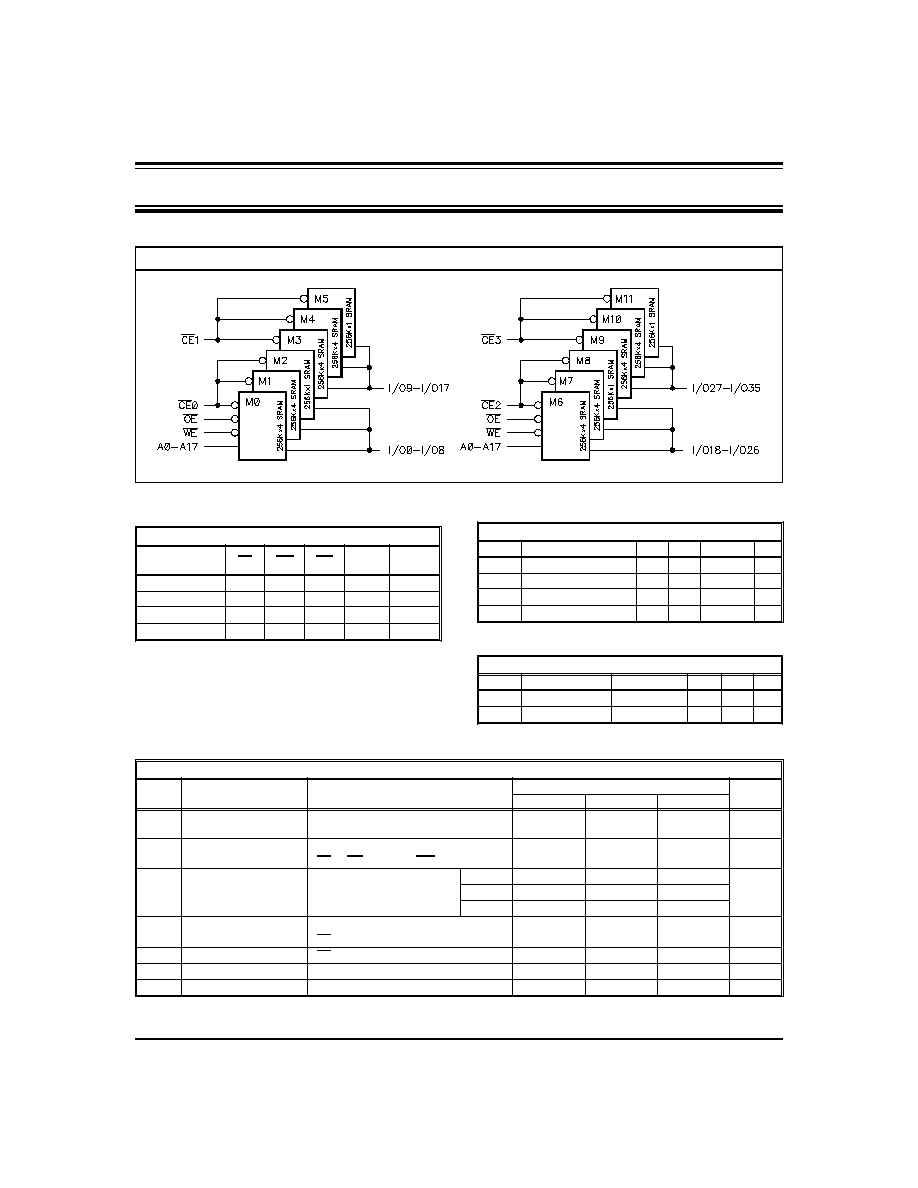

FUNCTIONAL BLOCK DIAGRAM

RECOMMENDED OPERATING RANGE

1

Symbol

Characteristic

Min. Typ.

Max.

Unit

V

DD

Supply Voltage

4.5

5.0

5.5

V

V

IH

Input HIGH Voltage 2.2

V

DD

+0.3 V

V

IL

Input LOW Voltage -0.5

2

0.8

V

T

A

Operating Temp.

-

+25

+70

o

C

TRUTH TABLE

Mode

CE

WE

OE

I/O Pin Supply

Current

Not Selected

H

X

X

High-Z Standby

D

OUT

Disable

L

H

H

High-Z Active

Read

L

H

L

D

OUT

Active

Write

L

L

X

D

IN

Active

H = HIGH L = LOW X = Don't Care

DC OUTPUT CHARACTERISTICS

Symbol

Parameter

Conditions Min. Max. Unit

V

OH

HIGH Voltage I

OH

= -4.0mA 2.4

V

V

OL

LOW Voltage

I

OL

=8.0mA

0.4

V

DC OPERATING CHARACTERISTICS: Over operating ranges

Symbol

Characteristics

Test Conditions

COMMERCIAL

Unit

Min.

TYP.

Max.

I

IN

Input

Leakage Current

V

IN

= 0V to V

DD

-40

+40

µ

A

I

OUT

Output

Leakage Current

V

I/O

= 0V to V

DD

,

CE or OE = V

IH

, or WE = V

IL

-10

+10

µ

A

I

CC

Operating

Supply Current

Cycle=min.,

Duty=100%,

I

OUT

= 0mA

X9

700

mA

X18

1000

X36

1600

I

SB1

Full Standby

Supply Current

V

IN

V

DD

-0.2V or V

IN

V

SS

+0.2V,

CE

V

DD

-0.2V, f = 0Hz

60

mA

I

SB2

Standby Current

CE = V

IH

, V

IN

or V

IN

400

mA

V

OL

Output Low Voltage

I

OUT

= 8.0mA

0.4

V

V

OH

Output High Voltage

I

OUT

= -4.0mA

2.4

V

Typical measurements made at +25

o

C, Cycle = min., V

DD

= 5.0V.

30A112-00

REV. A

2

Dense-Pac Microsystems, Inc.

DPS256X36L

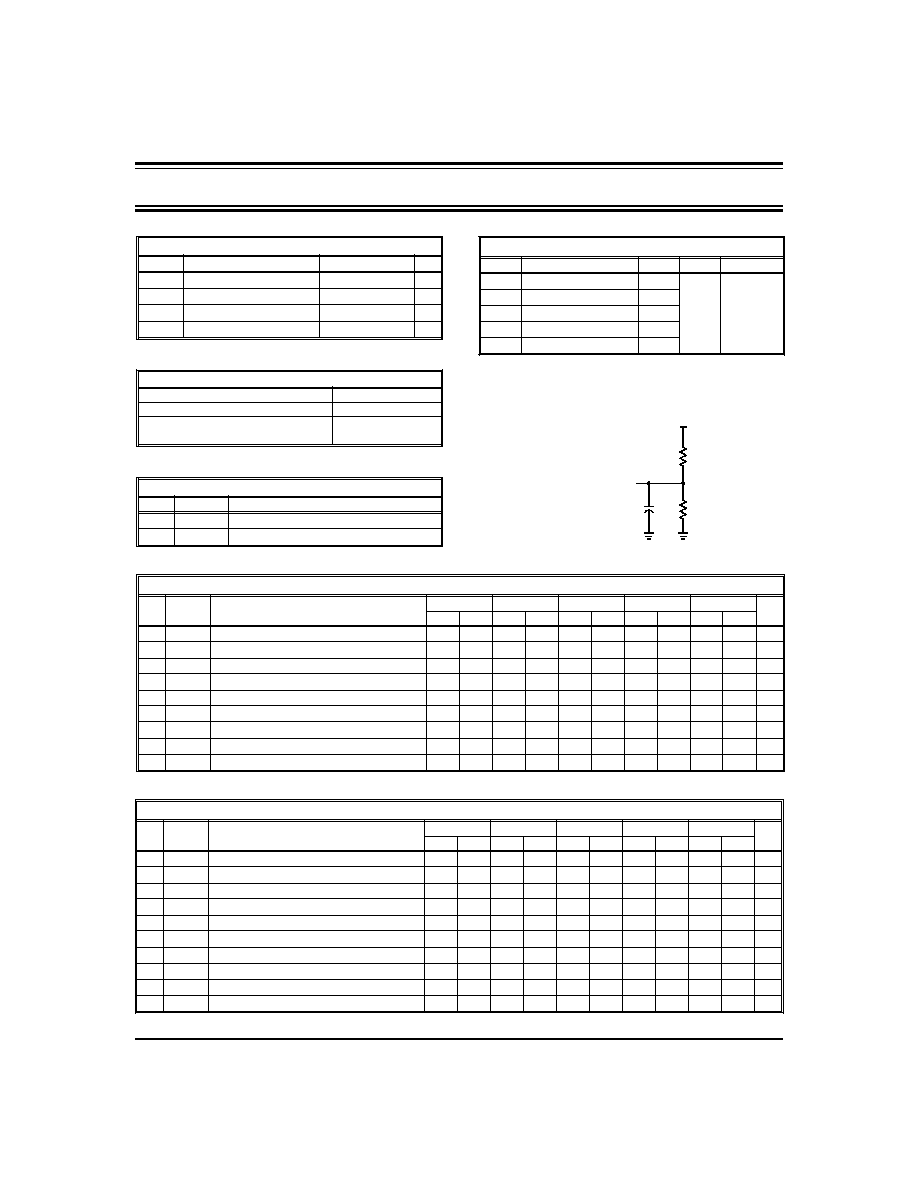

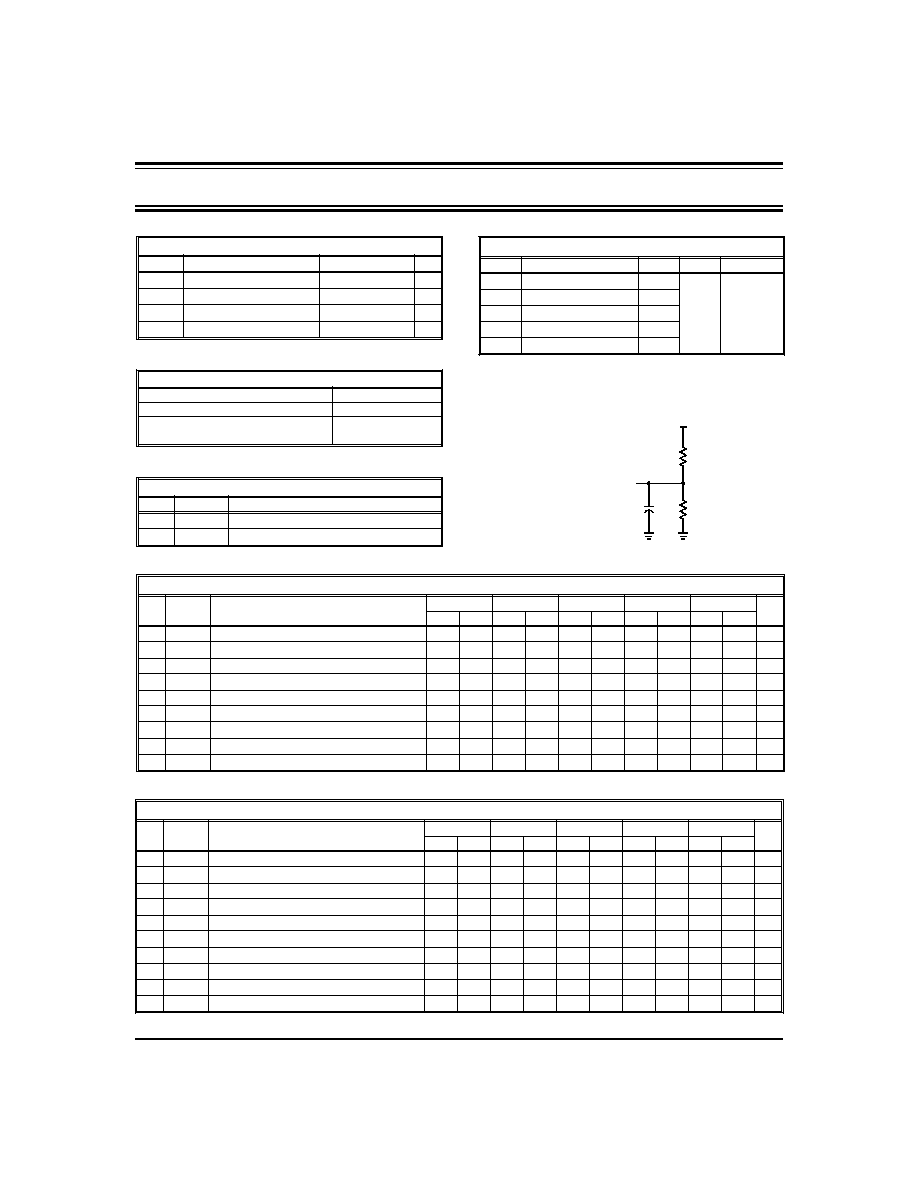

CAPACITANCE

4

: T

A

= 25∞C, F = 1.0MHz

Symbol

Parameter

Max.

Unit Condition

C

ADR

Address Input

900

pF

V

IN

2

= 0V

C

CE

Chip Enable

20

C

WE

Write Enable

90

C

OE

Output Enable

90

C

I/O

Data Input/Output

30

ABSOLUTE MAXIMUM RATINGS

3

Symbol

Parameter

Value

Unit

T

STC

Storage Temperature

-40 to +125

∞

C

T

BIAS

Temperature Under Bias

-10 to +85

∞

C

V

DD

Supply Voltage

1

-0.5 to +7.0

∞

C

V

I/O

Input/Output Voltage

1

-0.5 to V

DD

+0.5

V

AC OPERATING CONDITIONS AND CHARACTERISTICS - READ CYCLE: Over operating ranges

No. Symbol

Parameter

20ns

25ns

30ns

35ns

45ns

Unit

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

1

t

RC

Read Cycle Time

20

25

30

35

45

ns

2

t

AA

Address Access Time

20

25

30

35

45

ns

3

t

CO

Chip Enable to Output Valid

20

25

30

35

45

ns

4

t

OE

Output Enable to Output Valid

6

8

10

12

15

ns

5

t

LZ

Chip Enable to Output in LOW-Z

4, 5

5

5

5

5

5

ns

6

t

OLZ

Output Enable to Output in LOW-Z

4, 5

0

0

0

0

0

ns

7

t

HZ

Chip Enable to Output in HIGH-Z

4, 5

8

10

12

15

20

ns

8

t

OHZ

Output Enable to Output in HIGH-Z

4, 5

6

10

12

12

14

ns

9

t

OH

Output Hold from Address Change

5

5

5

5

5

ns

AC OPERATING CONDITIONS AND CHARACTERISTICS - WRITE CYCLE

6, 7

: Over operating ranges

No. Symbol

Parameter

20ns

25ns

30ns

35ns

45ns

Unit

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

10

t

WC

Write Cycle Time

20

25

30

35

45

ns

11

t

AW

Address Valid to End of Write

12

15

18

20

25

ns

12

t

CW

Chip Enable to End of Write

12

15

18

20

25

ns

13

t

AS

Address Set-Up Time ***

0

0

0

0

0

ns

14

t

WP

Write Pulse Width

12

15

18

20

25

ns

15

t

WR

Write Recovery Time

0

0

0

0

0

ns

16

t

WHZ

Write Enable to Output in HIGH-Z

4, 5

8

10

12

15

15

ns

17

t

DW

Data to Write Time Overlap

8

10

12

15

17

ns

18

t

DH

Data Hold from Write Time

0

0

0

0

0

ns

19

t

OW

Output Active from End of Write

5

5

5

5

5

ns

*** Valid for both Read and Write Cycles.

+5V

255

480

C

L

**

D

OUT

Figure 1. Output Load

** Including Probe and Jig Capacitance.

AC TEST CONDITIONS

Input Pulse Levels

0V to 3.0V

Input Pulse Rise and Fall Times

5ns

Input and Output

Timing Reference Levels

1.5V

* Transision measured between 0.8 and 2.2V.

OUTPUT LOAD

Load

C

L

Parameters Measured

1

30pF

except t

LZ

, t

HZ

, t

OHZ

, t

OLZ

, and t

WHZ

2

5pF

t

LZ

, t

HZ

, t

OHZ

, t

OLZ

, and t

WHZ

30A112-00

REV. A

3

DPS256X36L

Dense-Pac Microsystems, Inc.

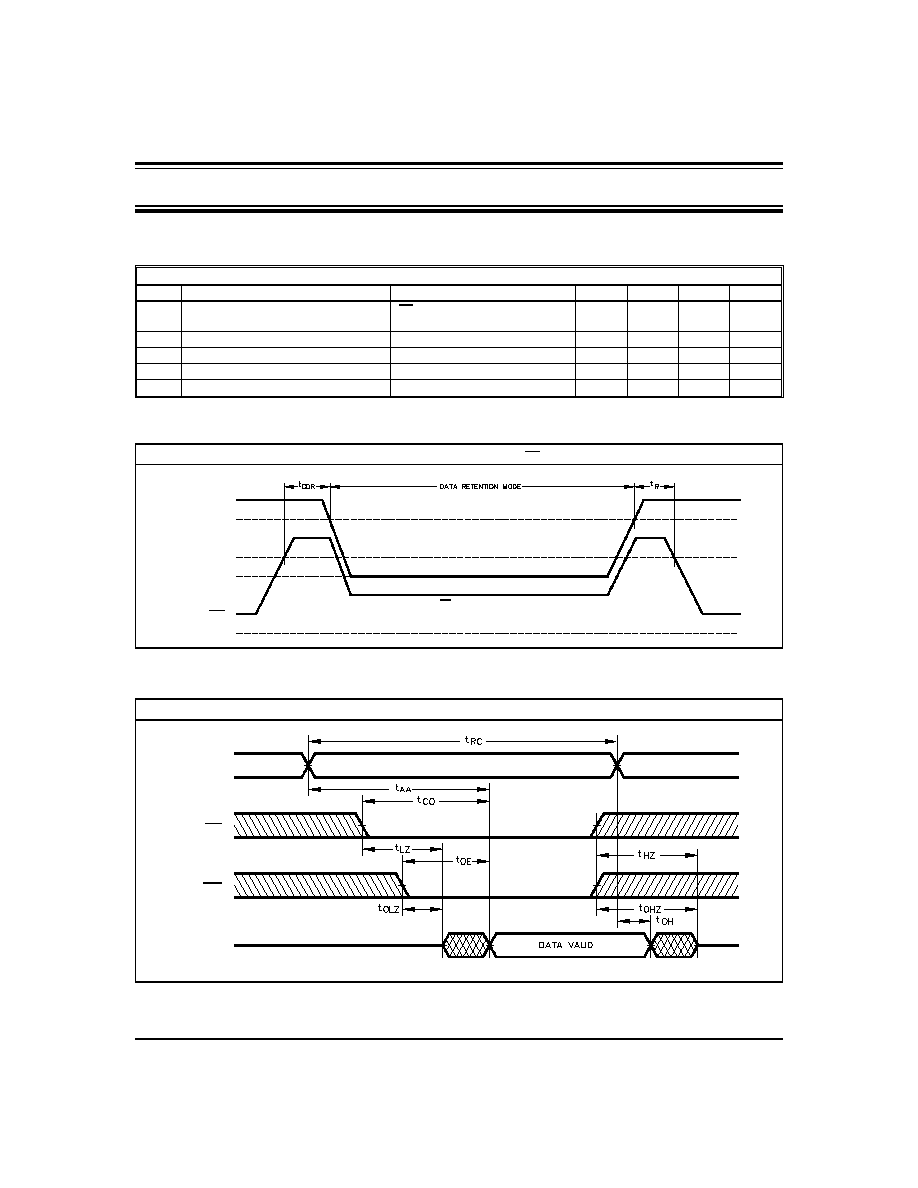

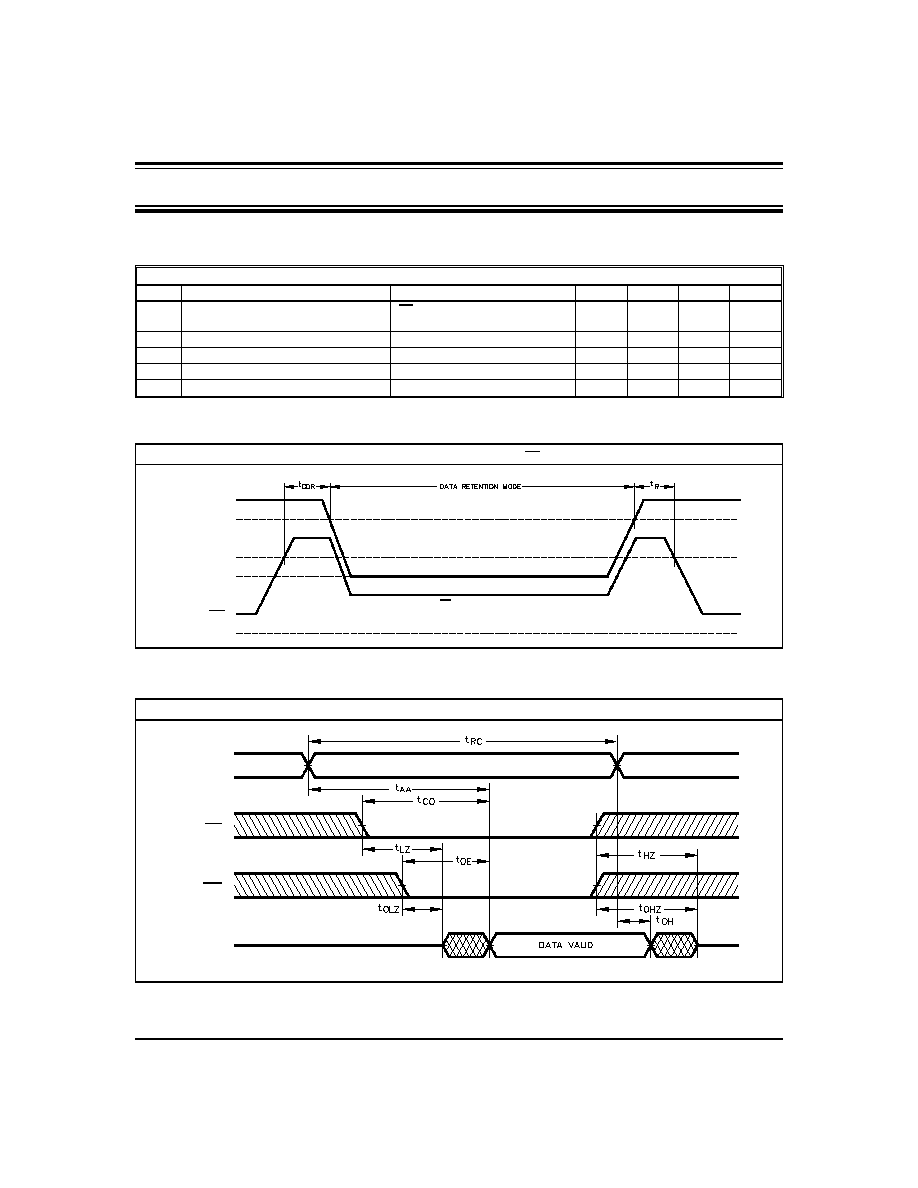

READ CYCLE

ADDRESS

CE

OE

DATA I/O

DATA RETENTION WAVEFORM:

CE Controlled.

V

DD

4.5V

2.3V

V

DR1

CE

0V

CE

V

DD

-0.2V

DATA RETENTION CHARACTERISTICS

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

V

DR

Data Retention Voltage

CE

V

DR

-0.2V,

V

IN

V

DR

-0.2V or V

IN

+0.2V

2.0

5.5

V

I

CCDR2

Data Retention Supply Current

V

DR

= 2.0V

0.28

1.6

mA

I

CCDR3

Data Retention Supply Current

V

DR

= 3.0V

0.56

3.2

mA

t

CDR

Chip Disable to Data Retention Time

0

ns

t

R

Recovery Time

t

RC

= Read Cycle Timing

5

ms

30A112-00

REV. A

4

Dense-Pac Microsystems, Inc.

DPS256X36L

WRITE CYCLE 2:

CE Controlled. OE is LOW.

ADDRESS

CE

WE

DATA OUT

DATA IN

WRITE CYCLE 1:

WE Controlled. OE Clocked.

ADDRESS

CE

WE

DATA OUT

DATA IN

ADDRESS

CE

WE

DATA OUT

DATA IN

ADDRESS

OE

CE

WE

DATA OUT

DATA IN

30A112-00

REV. A

5