| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: NB90234 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DS07-13504-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontroller

CMOS

F

2

MC-16F MB90230 Series

MB90233/234/P234/W234

s

DESCRIPTION

The MB90230 series is a member of general-purpose, 16-bit microcontrollers designed for those applications which

require high-speed realtimeprocessing, proving to be suitable for various industrial machines, camera and video

devices, OA equipment, and for process control. The CPU used in this series is the F

2

MC*-16F. The instruction

set for the F

2

MC-16F CPU core is designed to be optimized for controller applications while inheriting the AT

architecture of the F

2

MC-16/16H series, allowing a wide range of control tasks to be processed efficiently at high

speed.

The peripheral resources integrated in the MB90230 series include: the UART (clock asynchronous/synchronous

transfer)

◊

1 channel, the extended serial I/O interface

◊

1 channel, the A/D converter (8/10-bit precision)

◊

8

channels, the D/A converter (8-bit precision)

◊

2 channels, the level comparator

◊

1 channel, the external interrupt

input

◊

4 lines, the 8-bit PPG timer (PWM/single-shot function)

◊

1 channel, the 8-bit PWM controller

◊

6 channels,

the 16-bit free run timer

◊

1 channel, the input capture unit

◊

4 channels, the output compare unit

◊

6 channels,

and the serial E

2

PROM interface.

*: F

2

MC stands for FUJITSU Flexible Microcontroller.

s

FEATURES

F

2

MC-16F CPU block

∑ Minimum execution time: 62.5 ns (at machine clock frequency of 16 MHz)

∑ Instruction set optimized for controllers

Various data types supported (bit, byte, word, and long-word)

Extended addressing modes: 23 types

High coding efficiency

Higher-precision operation enhanced by a 32-bit accumulator

Signed multiplication and division instructions

(Continued)

s

PACKAGE

100-pin Plastic LQFP

(FPT-100P-M05)

100-pin Ceramic LQFP

(FPT-100C-C01)

MB90230 Series

2

(Continued)

∑ Enhanced instructions applicable to high-level language (C) and multitasking

System stack pointer

Enhanced pointer-indirect instructions

Barrel shift instructions

∑ Increased execution speed: 8-byte instruction queue

∑ 8-level, 32-factor powerful interrupt service functions

∑ Automatic transfer function independent of the CPU (EI

2

OS)

∑ General-purpose ports: Up to 84 lines

Ports with input pull-up resistor available: 24 lines

Ports with output open-drain available: 9 lines

Peripheral blocks

∑ ROM:48 Kbytes (MB90233)

96 Kbytes (MB90234)

EPROM: 96 Kbytes (MB90W234)

One-time PROM: 96 Kbytes (MB90P234)

∑ RAM: 2 Kbytes (MB90233)

3 Kbytes (MB90234/W234/P234)

∑ PWM control circuit: (simple 8 bits): 6 channels

∑ Serial interface

UART: 1 channel

Extended serial I/O interface

Switchable I/O port: 1 channel

Communication prescaler (Source clock generator for the UART, serial I/O interface, CKOT, and level

comparator): 1 channel

∑ Serial E

2

PROM interface: 1 channel

∑ A/D converter with 8/10-bit resolution: input 8 channels

∑ Level comparator: 1 channel

4-bit D/A converter integrated

∑ D/A converter with 8-bit resolution: 2 channels

8-bit PPG timer: 1 channel

∑ Input/output timer

16-bit free run timer: 1 channel

16-bit output compare unit: 6 channels

16-bit input capture unit: 4 channels

∑ 18-bit timebase timer

∑ Watchdog timer function

∑ Standby modes

Sleep mode

Stop mode

3

MB90230 Series

s

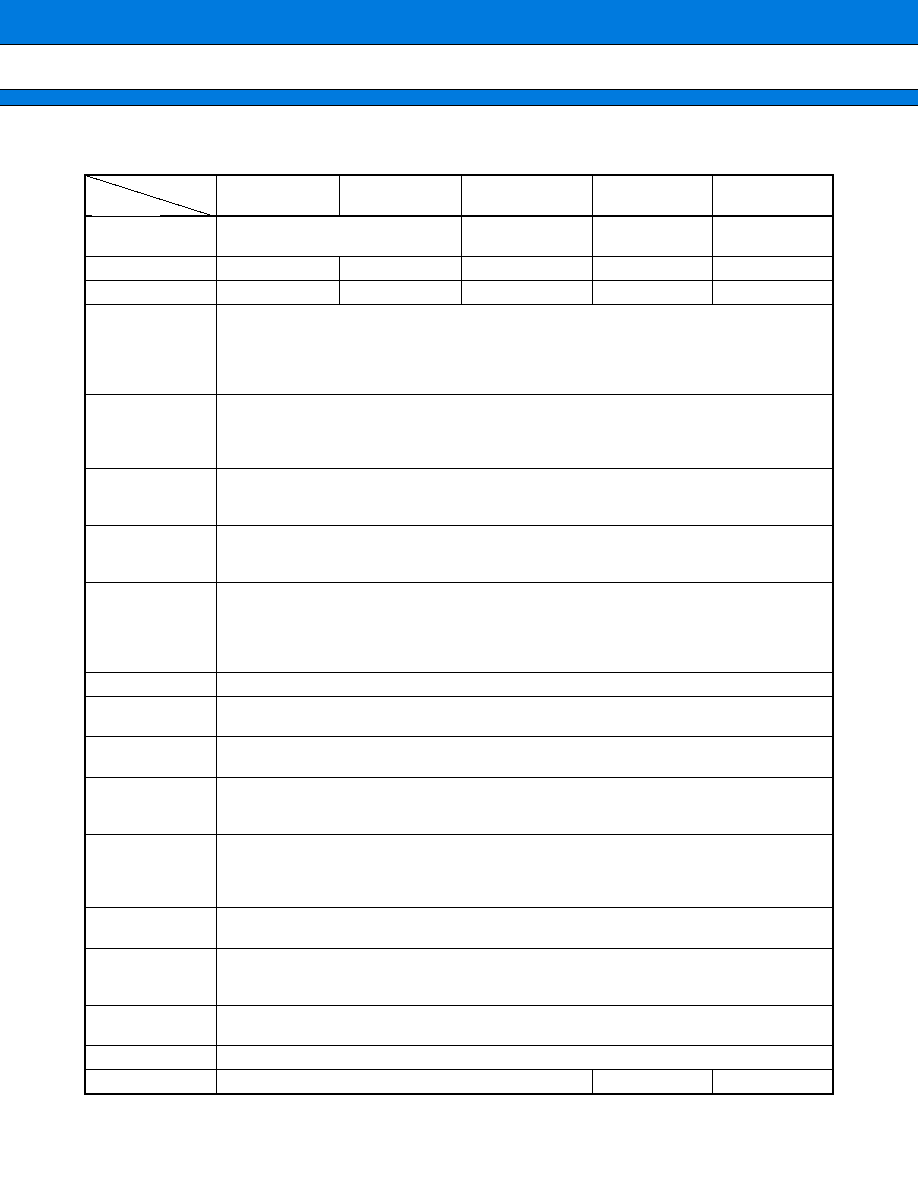

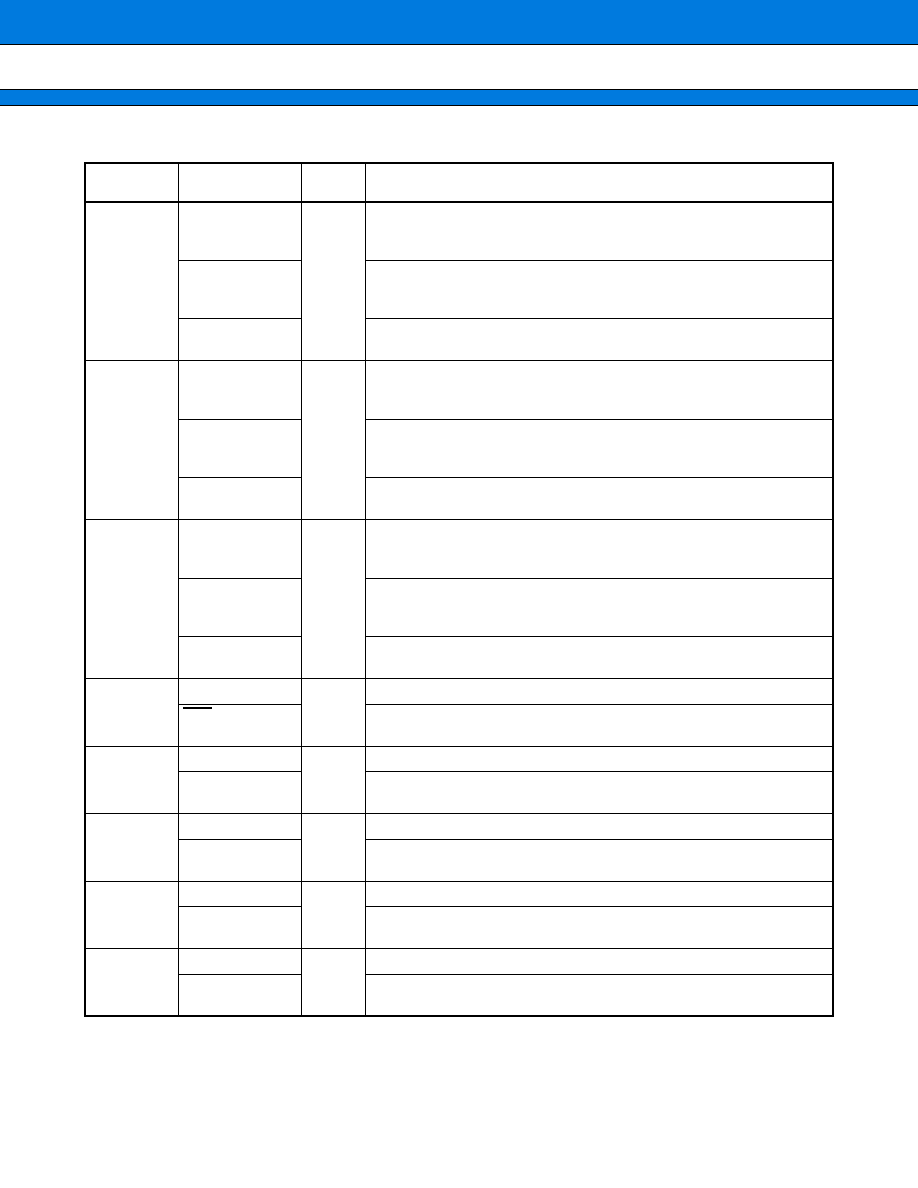

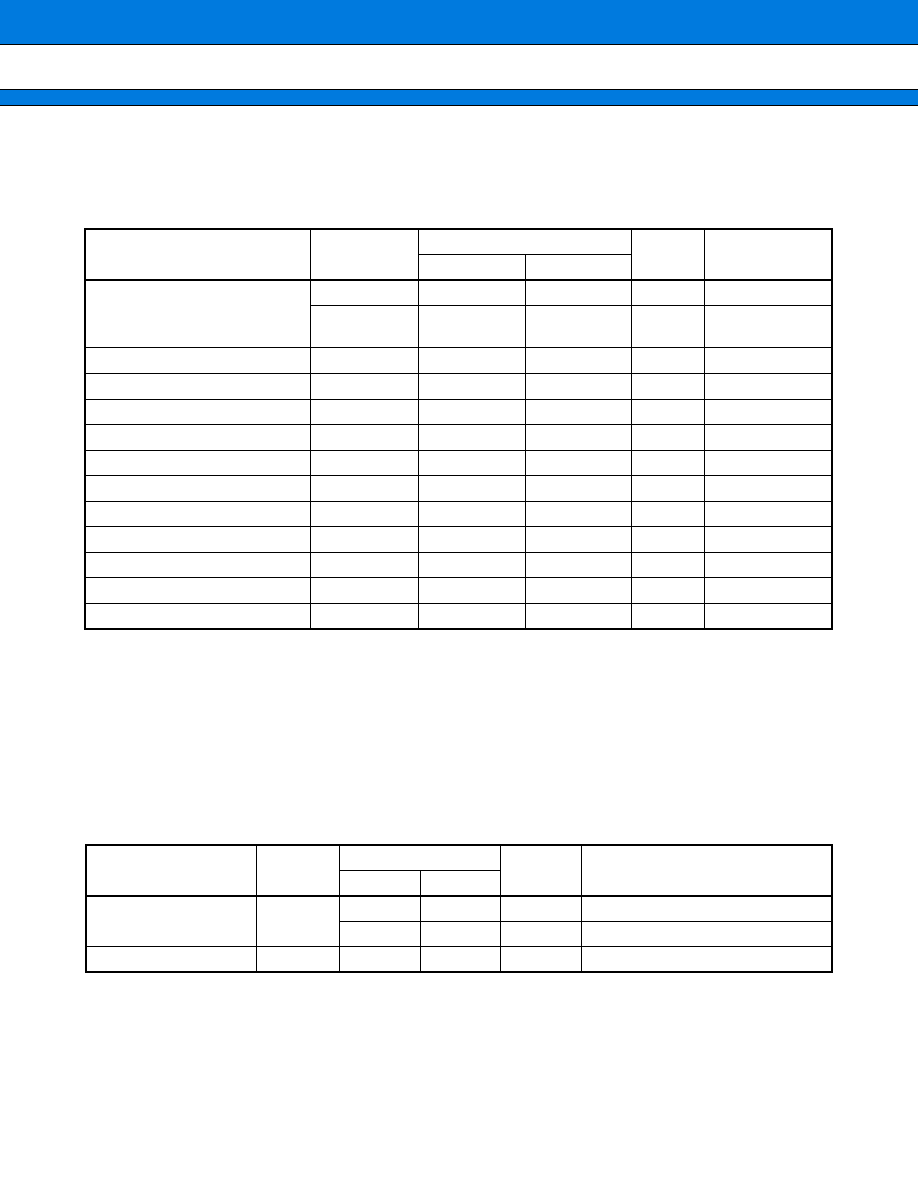

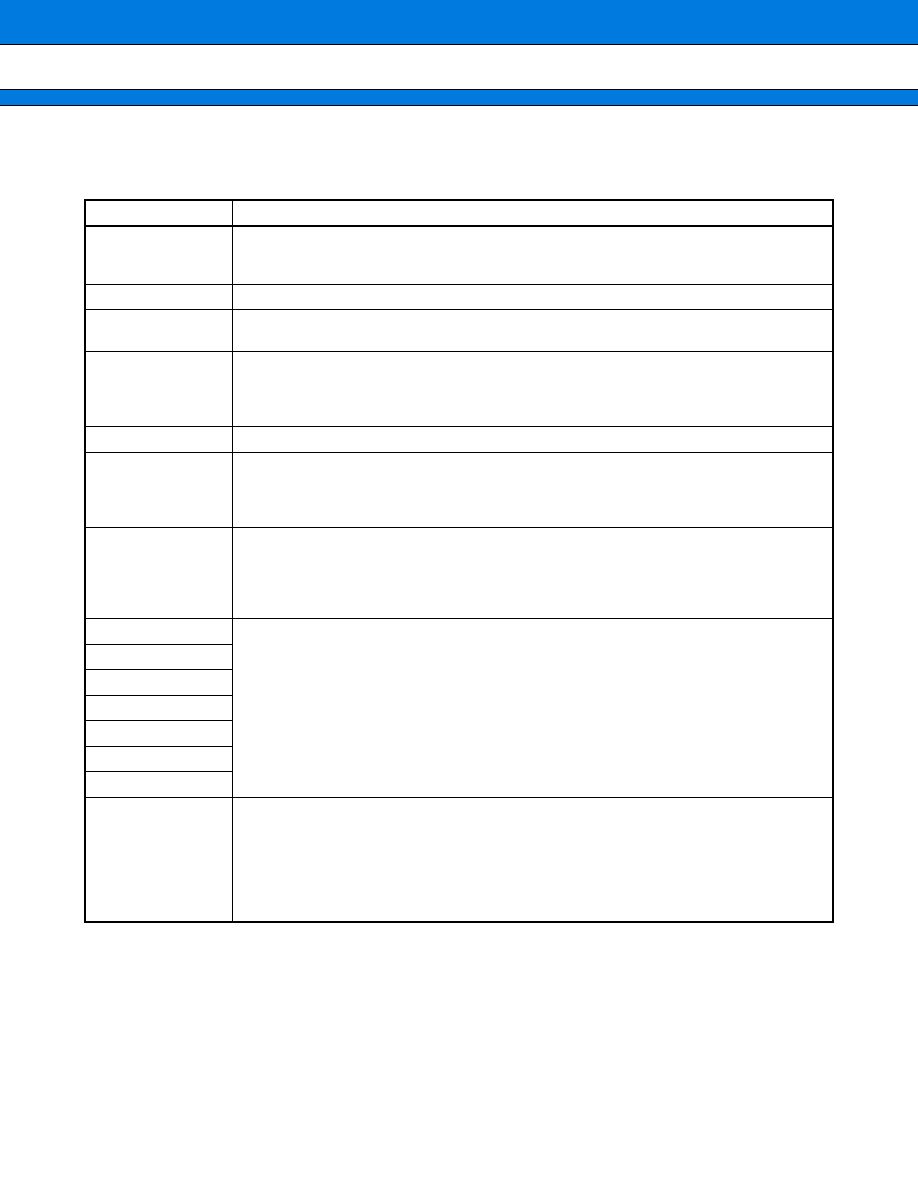

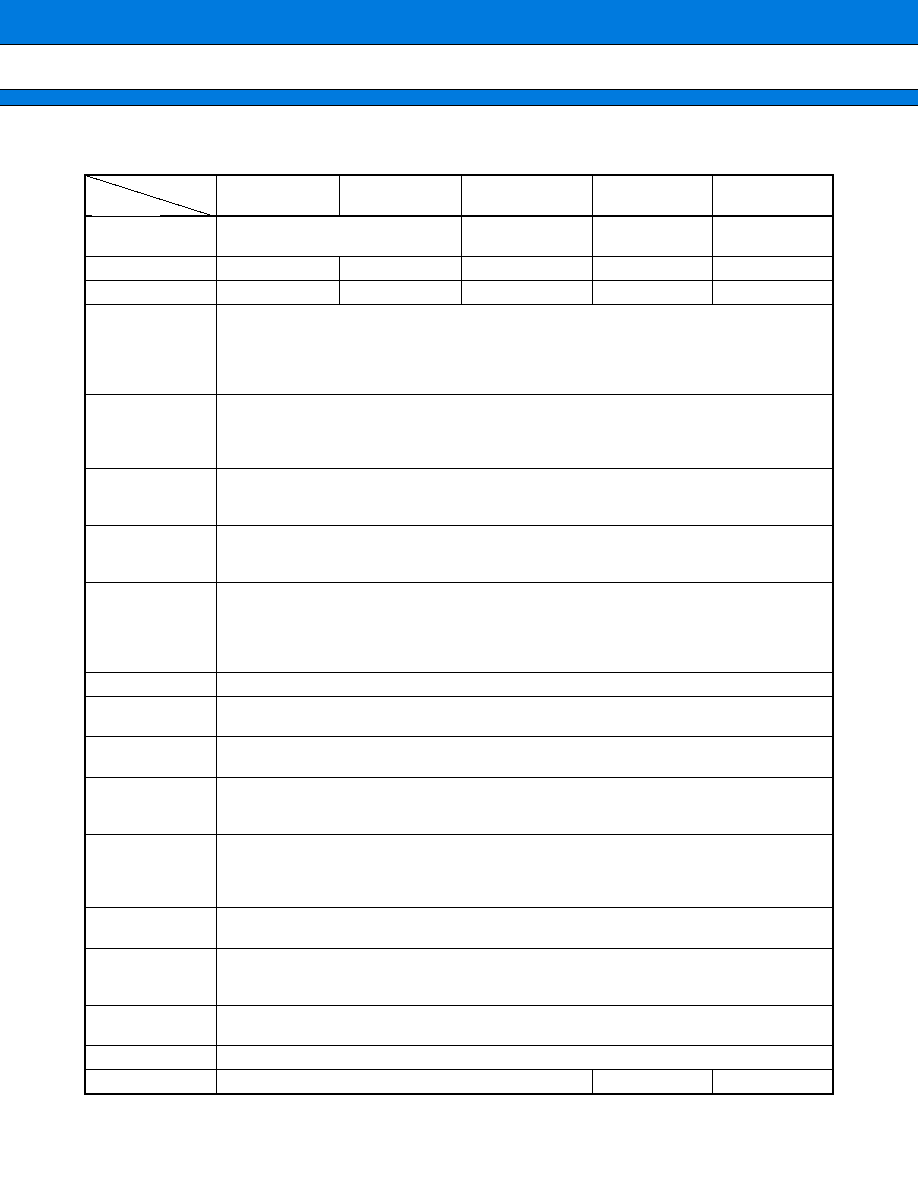

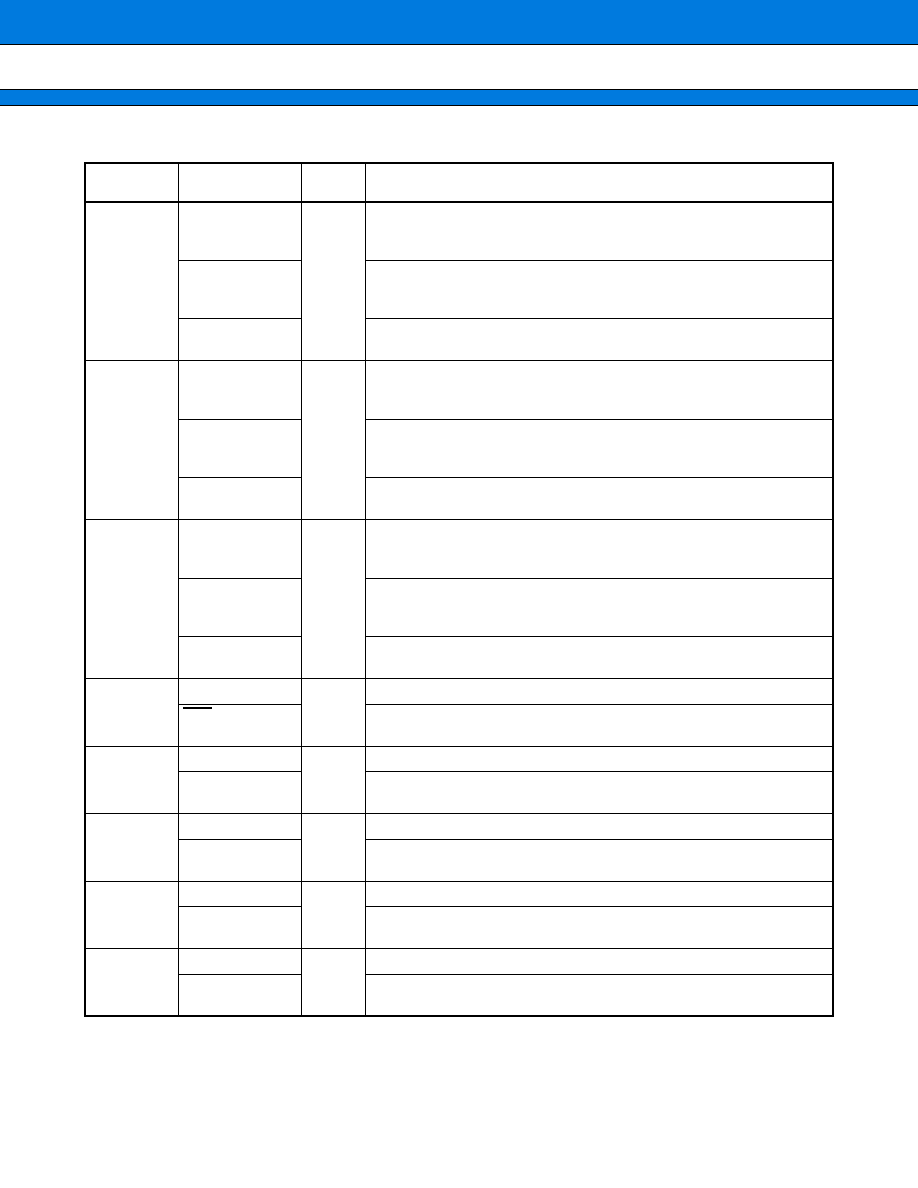

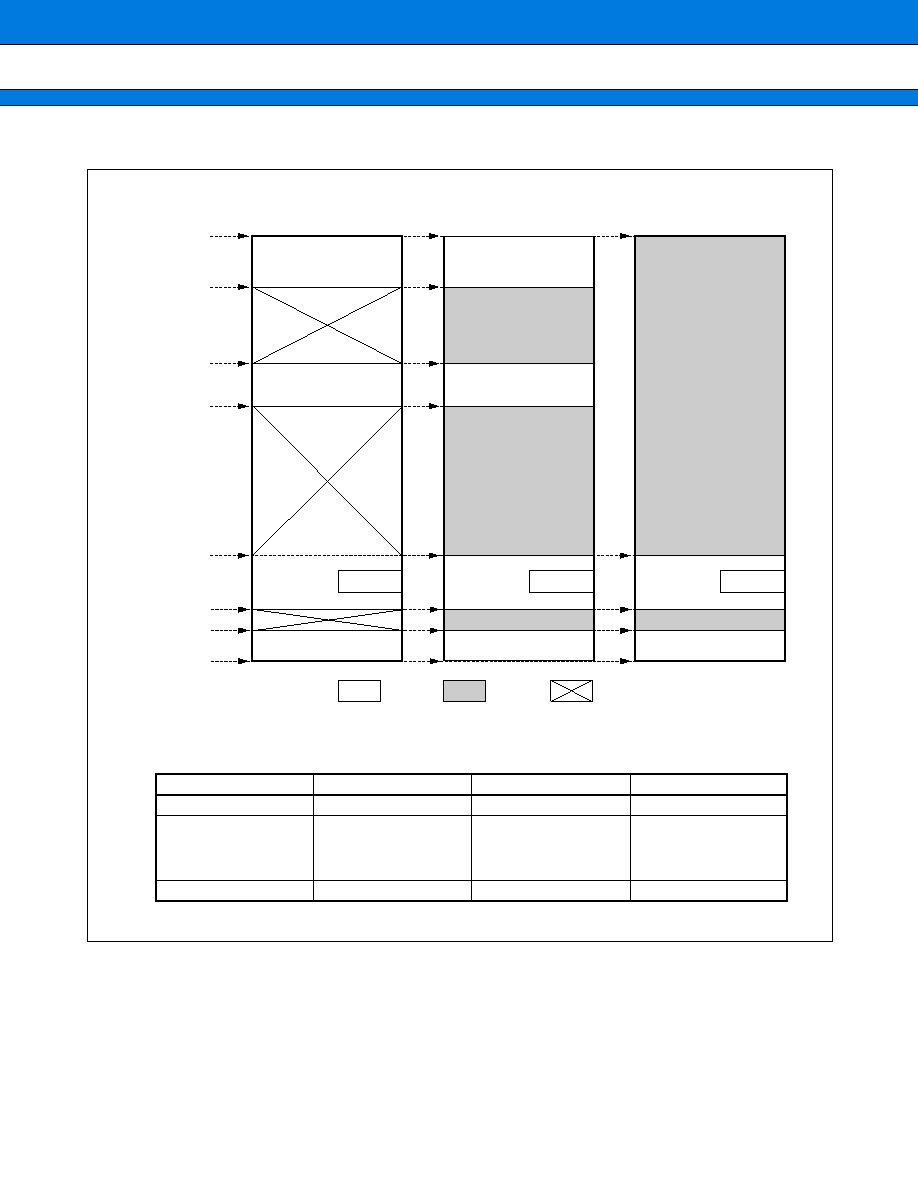

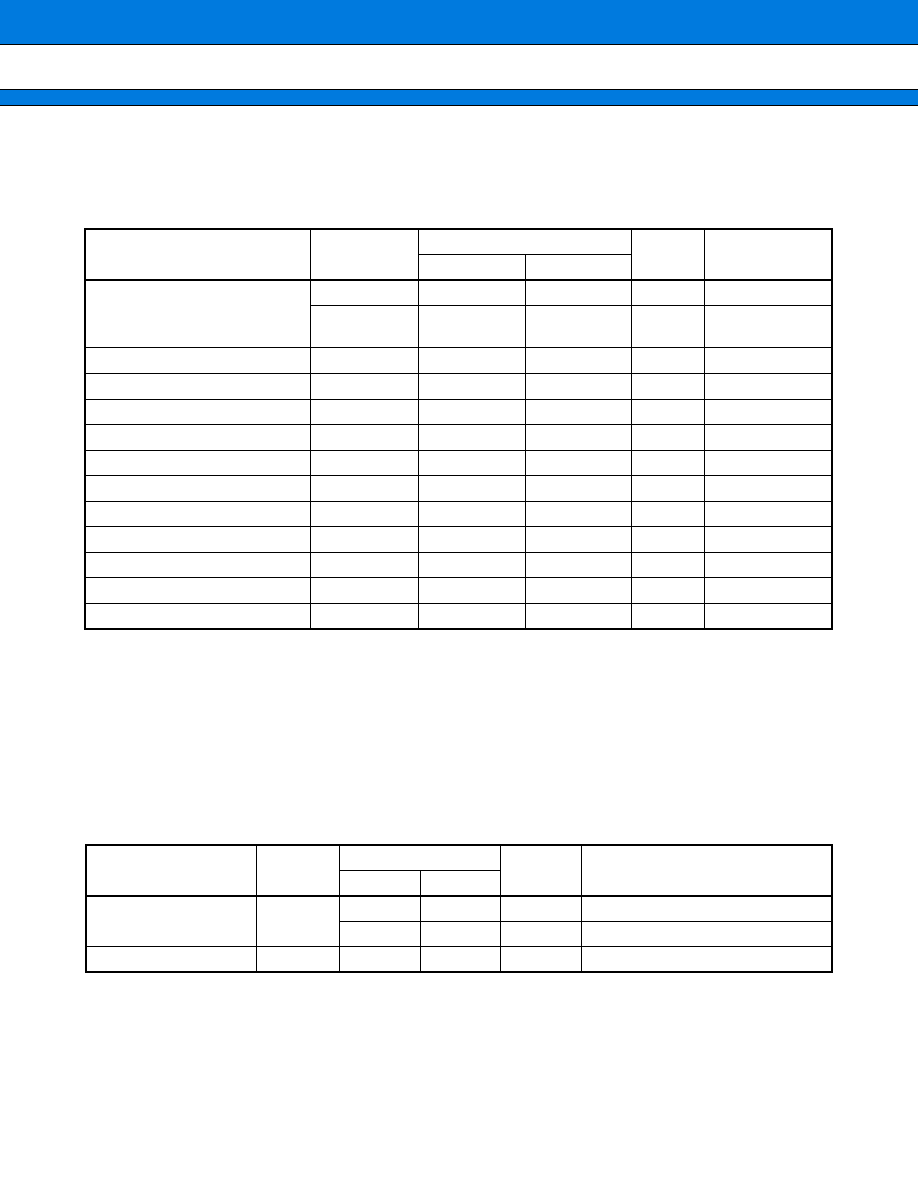

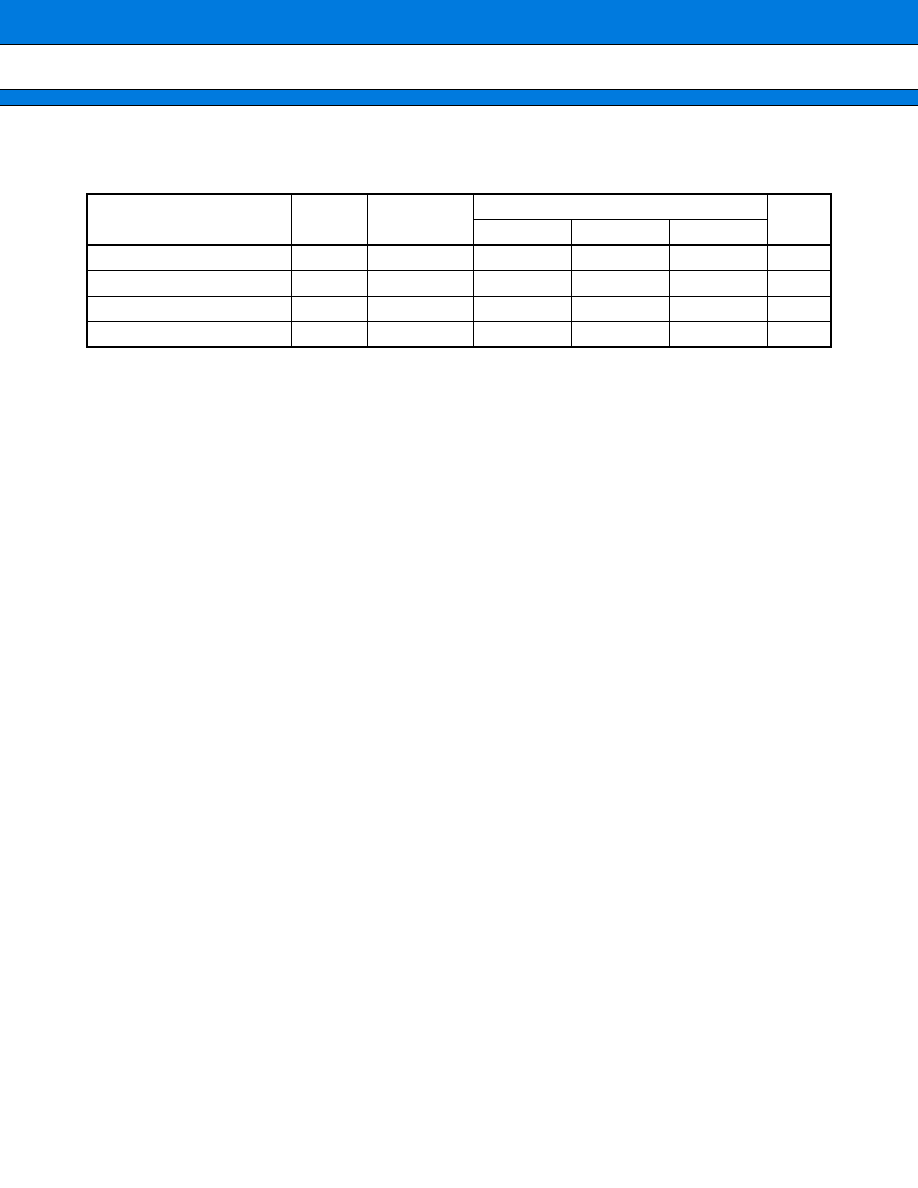

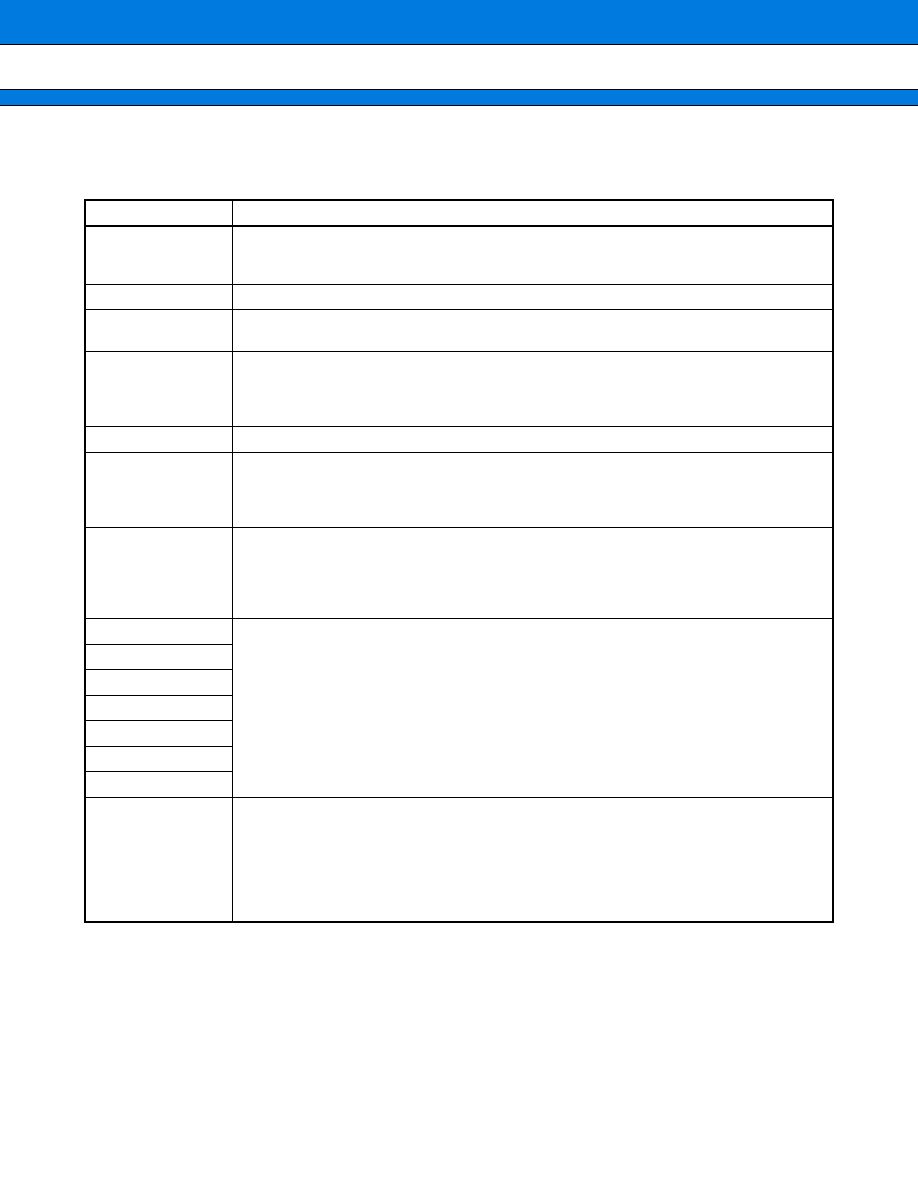

PRODUCT LINEUP

NB90234

MB90P234

MB90W234

MB90V230

Classification

Mask ROM products

One-time PROM

model

EPROM model

Evaluation

model

ROM size

48 Kbytes

96 Kbytes

96 Kbytes

96 Kbytes

--

RAM size

2 Kbytes

3 Kbytes

3 Kbytes

3 Kbytes

4 Kbytes

CPU functions

Number of instructions: 420

Instruction bit length: 8 or 16 bits

Instruction length: 1 to 7 bytes

Data bit length: 1, 4, 8, 16, or 32 bits

Minimum execution time: 62.5 ns at 16 MHz (internal)

Ports

Up to 84 lines

I/O ports (CMOS): 51

I/O ports (CMOS) with pull-up resistor available: 24

I/O ports (open-drain): 9

UART

Number of channels: 1 (switchable I/O)

Clock synchronous communication (2404 to 38460 bps, full-duplex double buffering)

Clock asynchronous communication (500K to 5M bps, full-duplex double buffering)

Serial interface

Number of channels: 1

Internal or external clock mode

Clock synchronous transfer (62.5 kHz to 1 MHz, "LSB first" or "MSB first" transfer)

A/D converter

Resolution: 10 or 8 bits, Number of input lines: 4

Single conversion mode (conversion for a specified input channel)

Scan conversion mode (continuous conversion for specified consecutive channels)

Continuous conversion mode (repeated conversion for a specified channel)

Stop conversion mode (periodical conversion)

D/A converter

Resolution: 8 bits, Number of output pins: 2

Level

comparator

Comparison to internal D/A converter (4-bit resolution)

PWM

Number of channels: 6

8-bit PWM control circuit (operation of 1

◊

, 2

◊

, 16

◊

, 32

◊

)

PPG timer

Number of channels: 1 channel with 8-bit resolution

PWM function: Continuous output of pulse synchronous to trigger

Single-shot function: Output of single pulse by trigger

Serial E

2

PROM

interface

Number of channels: 1

Instruction code (NS type)

Variable address length: 8 to 11 bits (with address increment function)

Variable data length: 8 or 16 bits

Timer

Number of channels: 6

16-bit reload timer operation (operation clock cycle of 0.25

µ

s to 1.05 s)

Free run timer

Number of channels: 1

16-bit input capture unit: 4 channels

16-bit output compare unit: 6 channels

External interrupt

input

Number of input pins: 4

Standby mode

Stop mode and sleep mode

Package

FPT-100P-M05

FPT-100C-C01

PGA256-A02

MB90233

Parameter

Part number

MB90230 Series

4

s

PIN ASSIGNMENT

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

RST

P54/WRH

P53/HRQ

P52/HAK

P51/RDY

P50/CLK

PA5/SCK2

PA4/SOT2

PA3/SIN2

PA2/SCK1

PA1/SOT1

PA0/SIN1

P96/SCK0

P95/SOT0

P94/SIN0

P93/IN3/CKOT

P92/IN2

P91/IN1

P90/IN0

P87/OUT5

P86/OUT4

P85/OUT3

P84/OUT2

P83/OUT1/INT3

P82/OUT0/INT2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

P22/A02

P23/A03

P24/A04

P25/A05

P26/A06

P27/A07

P30/A08

P31/A09

V

SS

P32/A10

P33/A11

P34/A12

P35/A13

P36/A14

P37/A15

PWM0/P40/A16

PWM1/P41/A17

PWM2/P42/A18

PWM3/P43/A19

PWM4/P44/A20

V

CC

PWM5/P45/A21

TRG/P46/A22

PPG/P47/A23

ATG/P70

P71/EDI

P72/EDO

P73/ESK

P74/ECS

P75/DA0

P76/DA1

AV

CC

AVRH

AVRL

AV

SS

P60/AN0

P61/AN1

P62/AN2

P63/AN3

V

SS

P64/AN4

P65/AN5

P66/AN6

P67/AN7/CMP

P80/INT0

P81/INT1

MD0

MD1

MD2

HST

P21/A01

P20/A00

P17/D15

P16/D14

P15/D13

P14/D12

P13/D11

P12/D10

P11/D09

P10/D08

P07/D07

P06/D06

P05/D05

P04/D04

P03/D03

P02/D02

P01/D01

P00/D00

V

CC

X1

X0

V

SS

P57

P56/RD

P55/WRL

(TOP VIEW)

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

(FPT-100P-M05)

(FPT-100C-C01)

5

MB90230 Series

s

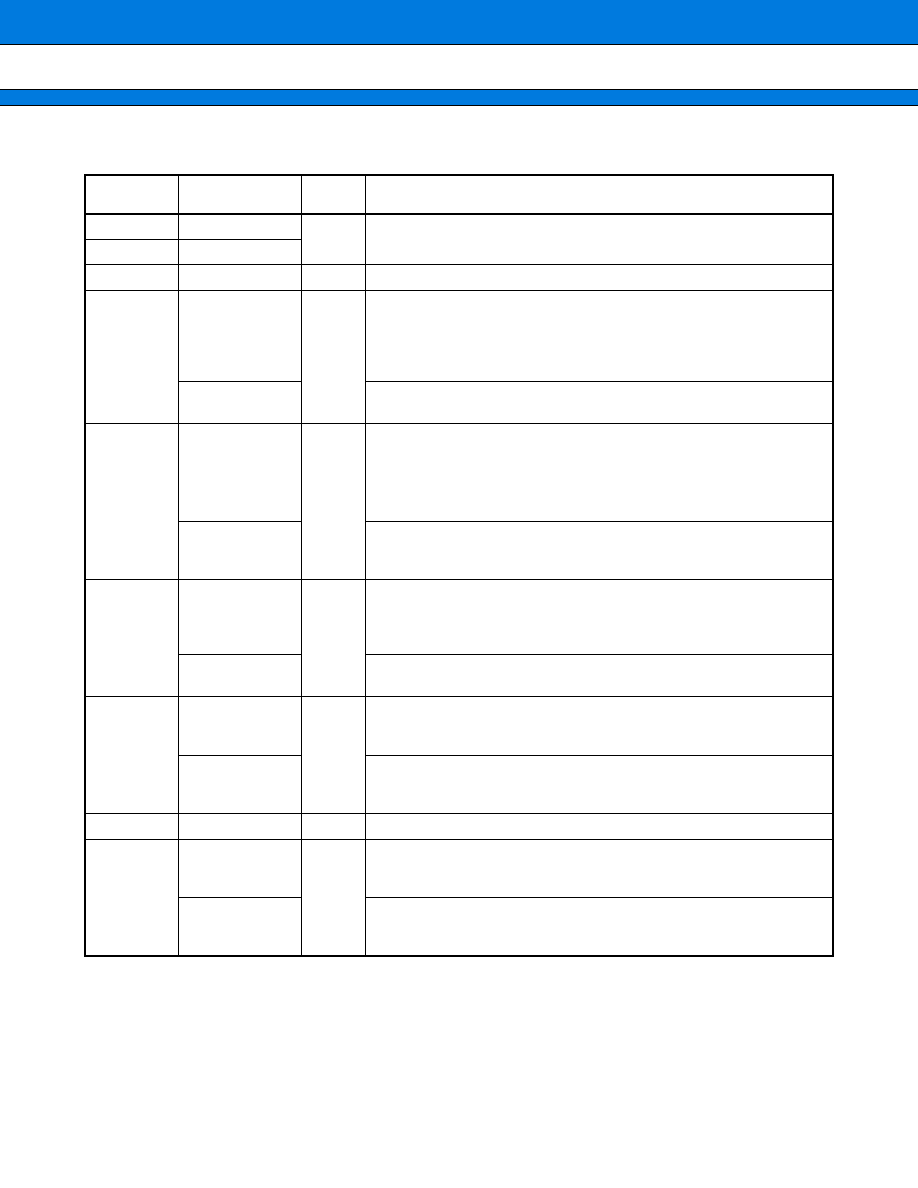

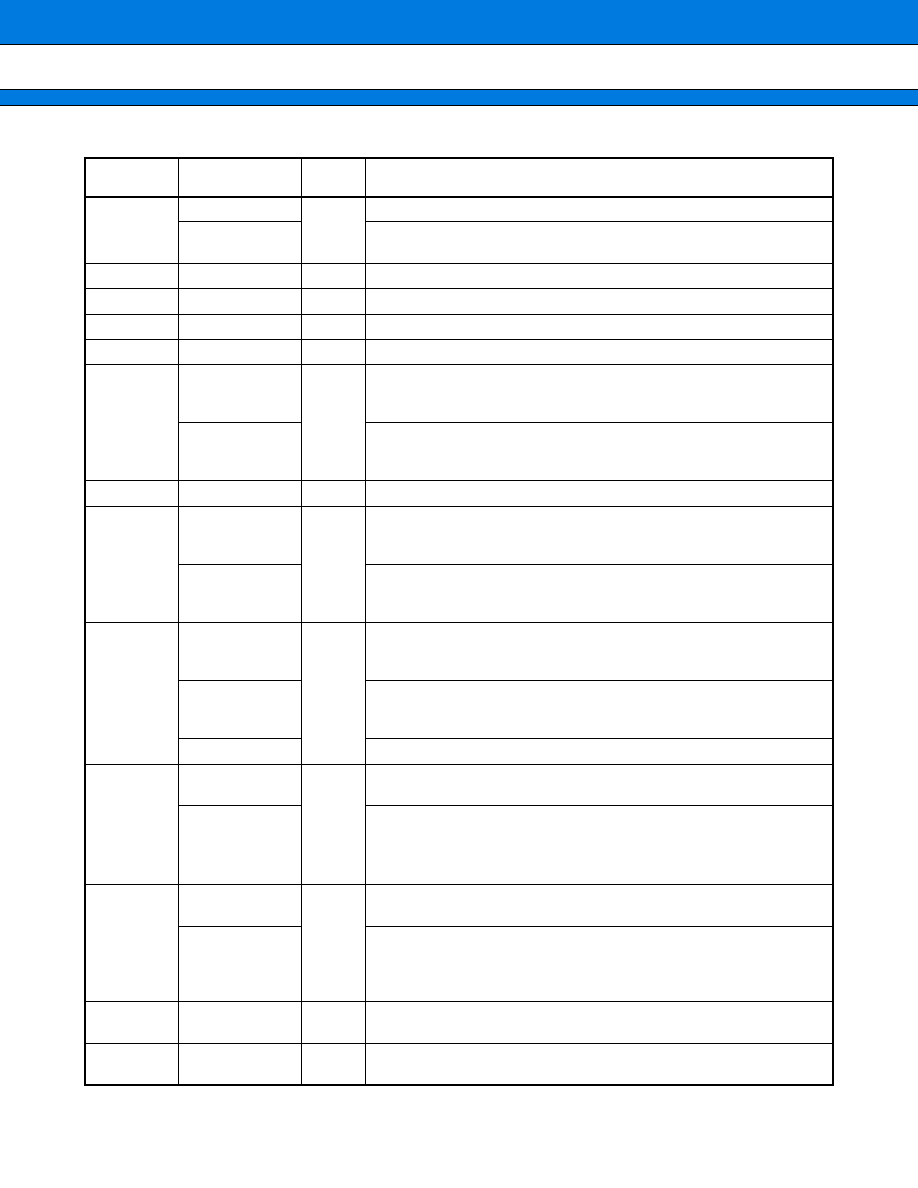

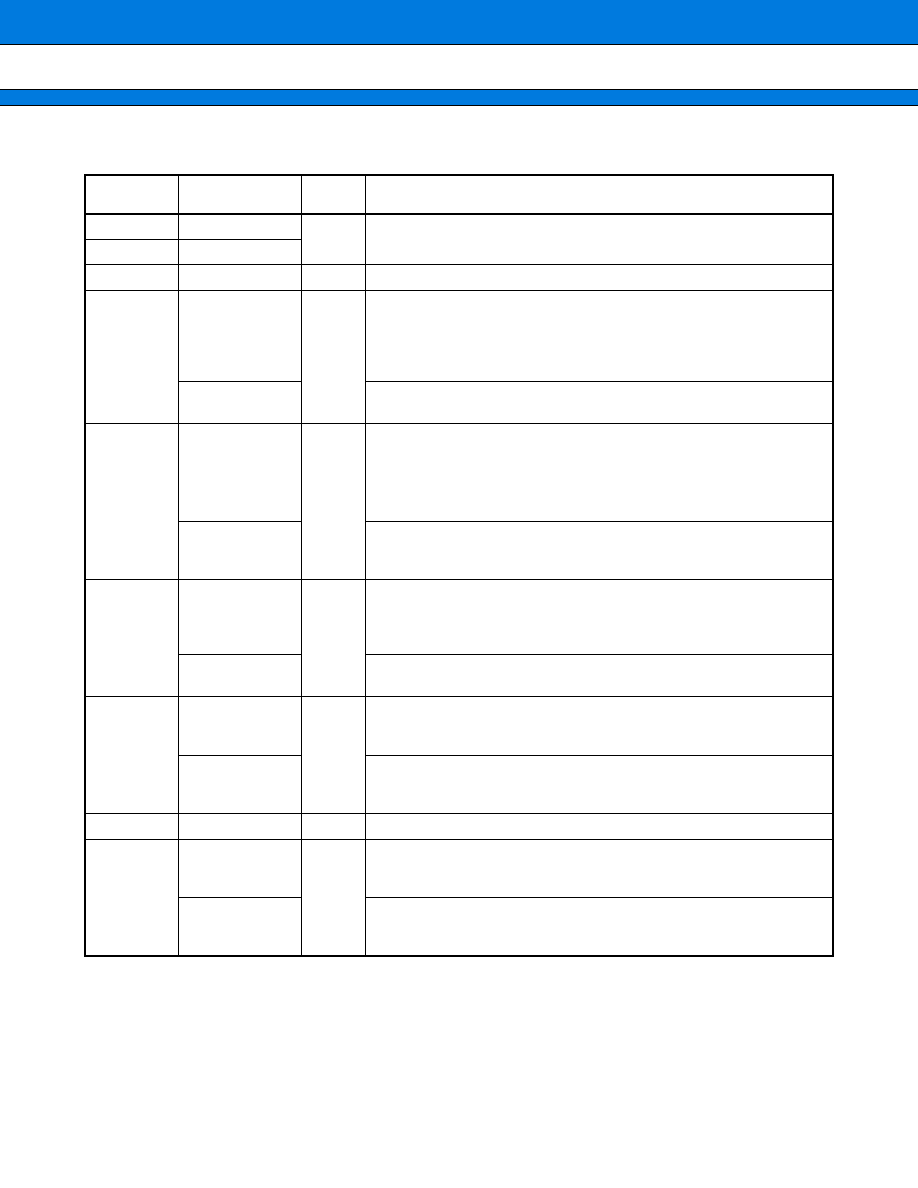

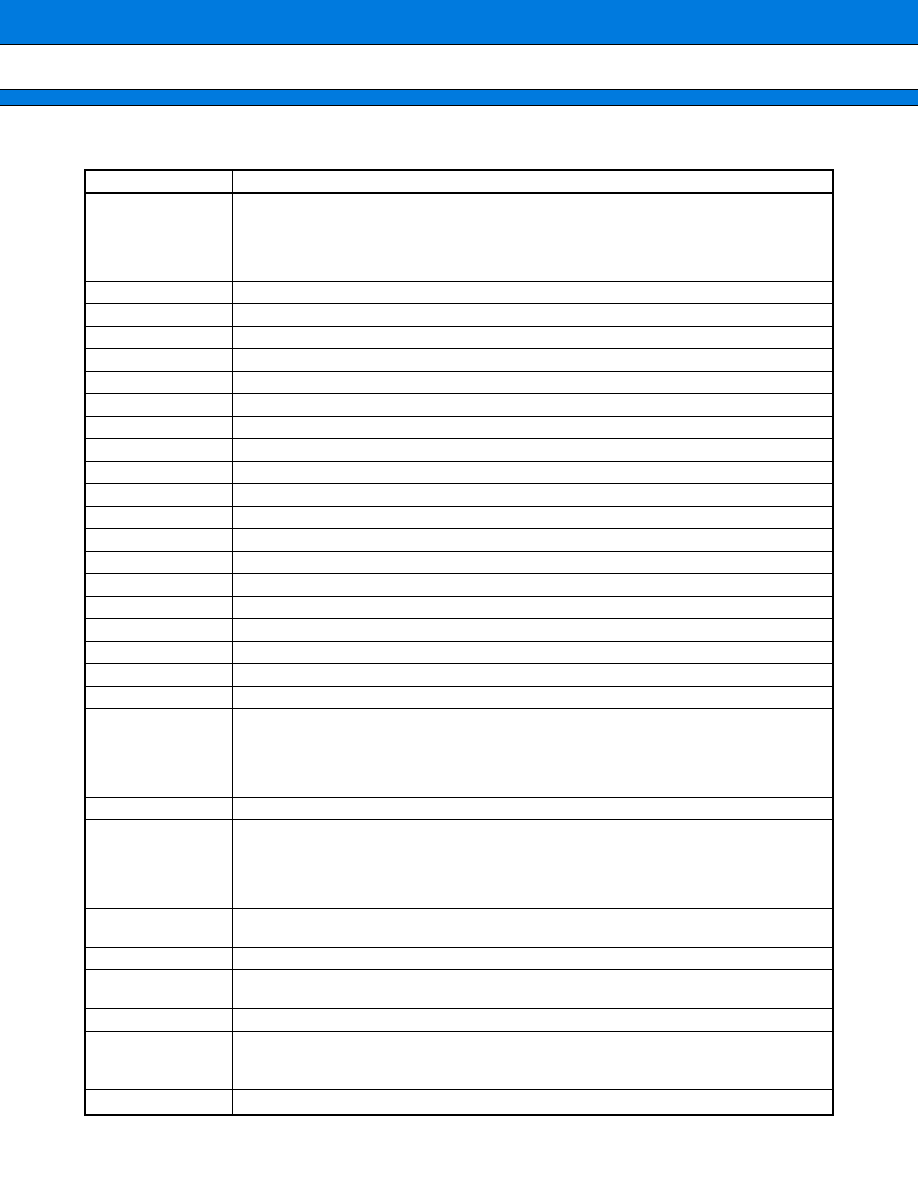

PIN DESCRIPTION

(Continued)

Pin no.

Pin name

Circuit

type

Function

80

X0

A

Oscillator pins

81

X1

82

V

CC

--

Power supply pin

83 to 90

P00 to P07

G

General-purpose I/O port

An input pull-up resistor can be added to the port by setting the

pull-up resistor setting register.

These pins serve as D00 to D07 pins in bus modes other than the

single-chip mode.

D00 to D07

I/O pins for the lower eight bits of the external data bus.

These pins are enabled in an external-bus enabled mode.

91 to 98

P10 to P17

G

General-purpose I/O port

An input pull-up resistor can be added to the port by setting the pull-up

resistor setting register.

These pins are enabled in the single-chip mode with the external-bus

enabled and the 8-bit data bus specified.

D08 to D15

I/O pins for the upper eight bits of the external data bus

These pins are enabled in an external-bus enabled mode with the 16-

bit data bus specified.

99, 100

1 to 6

P20 to P27

G

General-purpose I/O port

An input pull-up resistor can be added to the port by setting the

pull-up resistor setting register.

These pins are enabled in the single-chip mode.

A00 to A07

I/O pins for the lower eight bits of the external data bus

These pins are enabled in an external-bus enabled mode.

7, 8

P30, P31

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the middle

address control register setting is "port."

A08, A09

I/O pins for the middle eight bits of the external data bus

These pins are enabled in an external-bus enabled mode when the

middle address control register setting is "address."

9

V

SS

--

Power supply pin

10 to 15

P32 to P37

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the middle

address control register setting is "port."

A10 to A15

I/O pins for the middle eight bits of the external data bus

These pins are enabled in an external-bus enabled mode when the

middle address control register setting is "address."

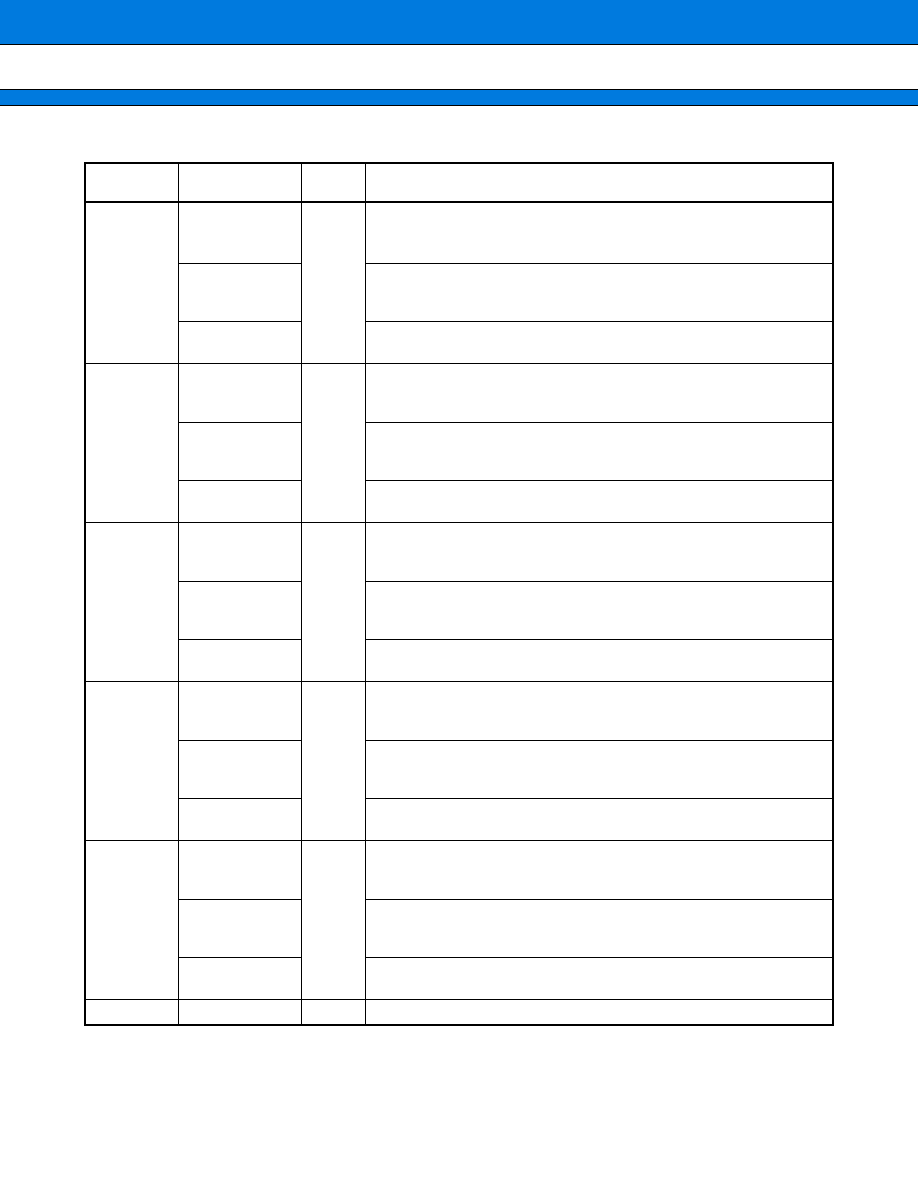

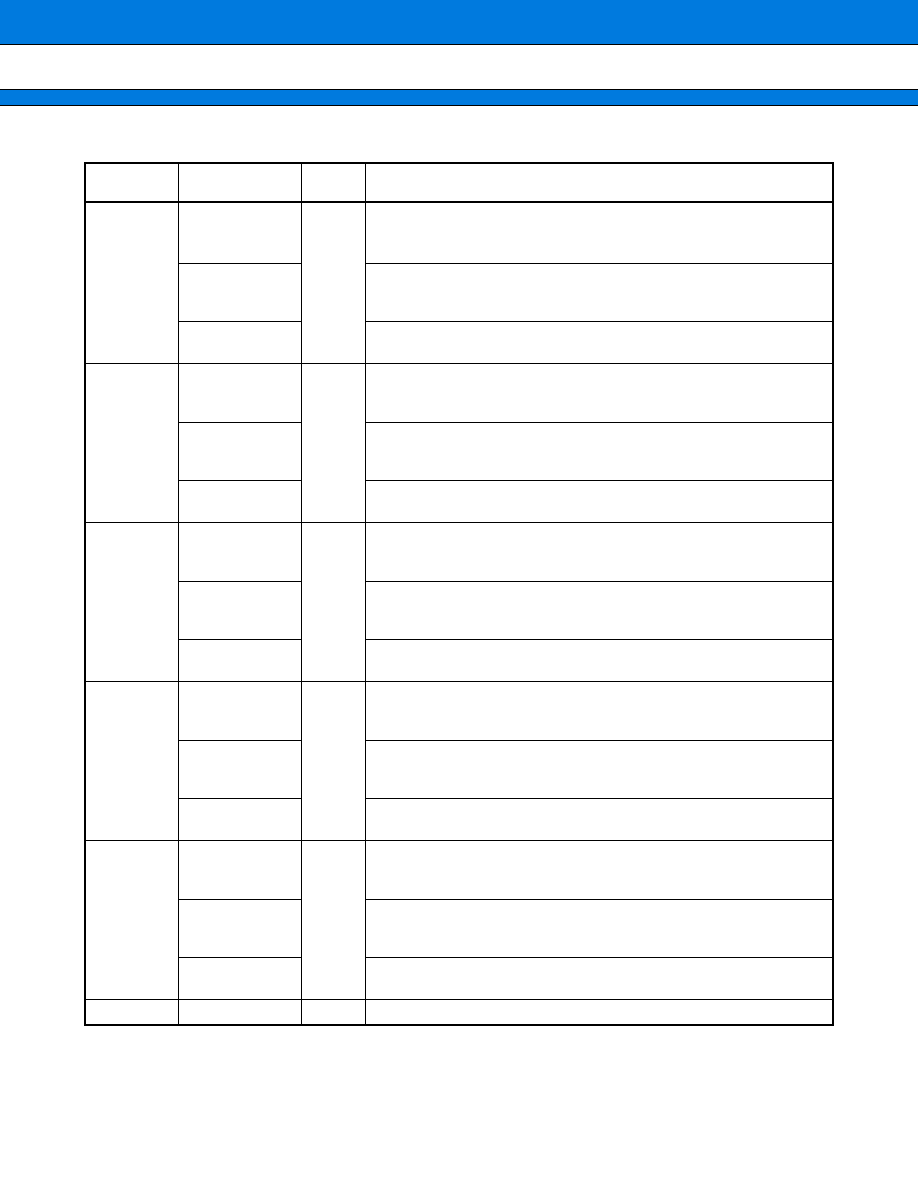

MB90230 Series

6

(Continued)

Pin no.

Pin name

Circuit

type

Function

16

P40

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A16

Output pin for external address A16

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PWM0

This pin serves as the output pin for 8-bit PWM0

The pin is enabled for output by the control status register.

17

P41

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A17

Output pin for external address A17

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PWM1

This pin serves as the output pin for 8-bit PWM1.

The pin is enabled for output by the control status register.

18

P42

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A18

Output pin for external address A18

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PWM2

This pin serves as the output pin for 8-bit PWM2.

This pin is enabled for output by the control status register.

19

P43

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A19

Output pin for external address A19

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PWM3

This pin serves as the output pin for 8-bit PWM3.

This pin is enabled for output by the control status register.

20

P44

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A20

Output pin for external address A20

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PWM4

This pin serves as the output pin for 8-bit PWM4.

The pin is enabled for output by the control status register.

21

V

CC

--

Power supply pin

7

MB90230 Series

(Continued)

Pin no.

Pin name

Circuit

type

Function

22

P45

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A21

Output pin for external address A21

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PWM5

This pin serves as the output pin for 8-bit PWM5.

The pin is enabled for output by the control status register.

23

P46

L*

1

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A22

Output pin for external address A22

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

TRG

This pin serves as the external trigger pin for the 8-bit PPG timer

The pin is enabled for triggering by the control status register.

24

P47

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the upper

address control register setting is "port."

A23

Output pin for external address A23

This pin is enabled in the external-bus enabled mode with the upper

address control register set to "address."

PPG

This pin serves as the output pin for the 8-bit PPG timer.

The pin is enabled for output by the control status register.

25

P70

L*

1

General-purpose I/O port

ATG

External trigger input pin for the A/D converter

This pin functions when enabled by the control status register.

26

P71

F

General-purpose I/O port

EDI

Data input pin for the serial EEPROM interface

This pin functions when enabled by the control status register.

27

P72

E

General-purpose I/O port

EDO

Data output pin for the serial EEPROM interface

This pin functions when enabled by the control status register.

28

P73

E

General-purpose I/O port

ESK

Clock output pin for the serial EEPROM interface

This pin functions when enabled by the control status register.

29

P74

E

General-purpose I/O port

ECS

Chip select signal output pin for the serial EEPROM interface

This pin functions when enabled by the control status register.

MB90230 Series

8

(Continued)

Pin no.

Pin name

Circuit

type

Function

30, 31

P75, P76

K

General-purpose I/O port

DA0

DA1

This pin serves as the D/A converter output pin.

The pin functions when enabled by the control status register.

32

AV

CC

--

A/D converter power supply pin

33

AV

RH

--

"H" reference power supply pin for the A/D converter

34

AV

RL

--

"L" reference power supply pin for the A/D converter

35

AV

SS

--

A/D converter power pin (GND)

36 to 39

P60 to P63

J

General-purpose I/O port

This port is enabled when the analog input enable register setting is

"port."

AN0 to AN3

A/D converter analog input pins

These pins are enabled when the analog input enable register setting

is "analog input."

40

V

SS

--

Power pin (GND)

41 to 43

P64 to P66

J

General-purpose I/O port

This port is enabled when the analog input enable register setting is

"port."

AN4 to AN6

A/D converter analog input pins

These pins are enabled when the analog input enable register setting

is "analog input."

44

P67

J

General-purpose I/O port

This port is enabled when the analog input enable register setting is

"port."

AN7

A/D converter analog input pin

This pin is enabled when the analog input enable register setting is

"analog input."

CMP

Comparator input pin

45

P80

L*

2

General-purpose I/O port

This port is always enabled.

INT0

External interrupt request input 0

Since this pin serves for interrupt request as required when external

interrupt is enabled, other outputs must be off unless used

intentionally.

46

P81

L*

2

General-purpose I/O port

This port is always enabled.

INT1

External interrupt request input 1

Since this pin serves for interrupt request as required when external

interrupt is enabled, other outputs must be off unless used

intentionally.

47

MD0

C

Mode pin

This pin must be fixed to V

CC

or V

SS

.

48

MD1

C

Mode pin

This pin must be fixed to V

CC

or V

SS

.

9

MB90230 Series

(Continued)

Pin no.

Pin name

Circuit

type

Function

49

MD2

C

Mode pin

This pin must be fixed to V

SS

.

50

HST

D

Hardware standby input pin

51, 52

P82, P83

L*

2

General-purpose I/O port

OUT0,

OUT1

Output compare output pins

These pins function when enabled by the control status register.

INT2,

INT3

External interrupt request inputs 2 and 3.

Since these pins serve for interrupt request as required when external

interrupt is enabled, other outputs must be off unless used

intentionally.

53 to 56

P84 to P87

E

General-purpose I/O port

This pin is always enabled.

OUT2 to OUT5

Output compare output pins

These pins function when enabled by the control status register.

57 to 59

P90 to P92

L*

1

General-purpose I/O port

This port is always enabled.

IN0 to IN2

Input capture edge input pins

These pins function when enabled by the control status register.

60

P93

L*

1

General-purpose I/O port

This port is always enabled.

IN3

Input capture edge input pin

This pin functions when enabled by the control status register.

CKOT

Prescaler output pin

This pin functions when enabled by the control status register.

61

P94

I

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SIN0

Serial data input pin for the UART

This pin functions when enabled by the control status register.

62

P95

H

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SOT0

Serial data output pin for the UART

This pin functions when enabled by the control status register.

63

P96

I

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SCK0

UART clock output pin

This pin functions when enabled by the control status register.

MB90230 Series

10

(Continued)

Pin no.

Pin name

Circuit

type

Function

64

PA0

I

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SIN1

Serial data input pin for the extended serial I/O interface

This pin functions when enabled by the control status register and by

the serial port switching register.

65

PA1

H

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SOT1

Serial data output pin for the extended serial I/O interface

This pin functions when enabled by the control status register and by

the serial port switching register.

66

PA2

I

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SCK1

Clock output pin for the extended serial I/O interface

This pin functions when enabled by the control status register and by

the serial port switching register.

67

PA3

I

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SIN2

Serial data input pin for the extended serial I/O interface

This pin functions when enabled by the control status register and by

the serial port switching register.

68

PA4

H

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SOT2

Serial data output pin for the extended serial I/O interface

This pin functions when enabled by the control status register and by

the serial port switching register.

69

PA5

I

General-purpose I/O port

This port is always enabled.

The port serves as an open-drain output depending on the open-drain

setting register.

SCK2

Clock output pin for the extended serial I/O interface

This pin functions when enabled by the control status register and by

the serial port switching register.

The pin is a general-purpose I/O port.

11

MB90230 Series

(Continued)

*1: Enabled in any standby mode

*2: Enabled only in the hardware standby mode

Pin no.

Pin name

Circuit

type

Function

70

P50

H

This pin is enabled in the single-chip mode and when the CLK output

is disabled.

CLK

CLK output pin

This pin is enabled in an external-bus enabled mode with the CLK

output enabled.

71

P51

F

General-purpose I/O port

This port is enabled in the single-chip mode.

RDY

Ready signal input pin

This pin is enabled in an external-bus enabled mode.

72

P52

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the hold function

is disabled.

HAK

Hold acknowledge signal output pin

This pin is enabled in the single-chip mode or when the hold function

is enabled.

73

P53

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the hold function

is disabled.

HRQ

Hold acknowledge signal output pin

This pin is enabled in the single-chip mode or when the hold function

is enabled.

74

P54

E

General-purpose I/O port

This port is enabled in the single-chip mode, in external-bus 8-bit

mode, or when the WR pin output is disabled.

WRH

Write strobe output pin for the upper eight bits of the data bus

This pin is enabled in an external-bus enabled mode and in external

bus 16-bit mode with the WR pin output enabled.

75

RST

B

Reset signal input pin

76

P55

E

This port is enabled in the single-chip mode, in external-bus 8-bit

mode, or when the WR pin output is disabled

WRL

Write strobe output pin for the lower eight bits of the data bus

This pin is enabled in an external-bus enabled mode and in external

bus 16-bit mode with the WR pin output enabled.

The pin is a general-purpose I/O port.

77

P56

E

This pin is enabled in the single-chip mode.

RD

Read strobe output pin for the data bus

This pin is enabled in an external-bus enabled mode.

78

P57

E

General-purpose I/O port

79

V

SS

--

Power pin (GND)

MB90230 Series

12

s

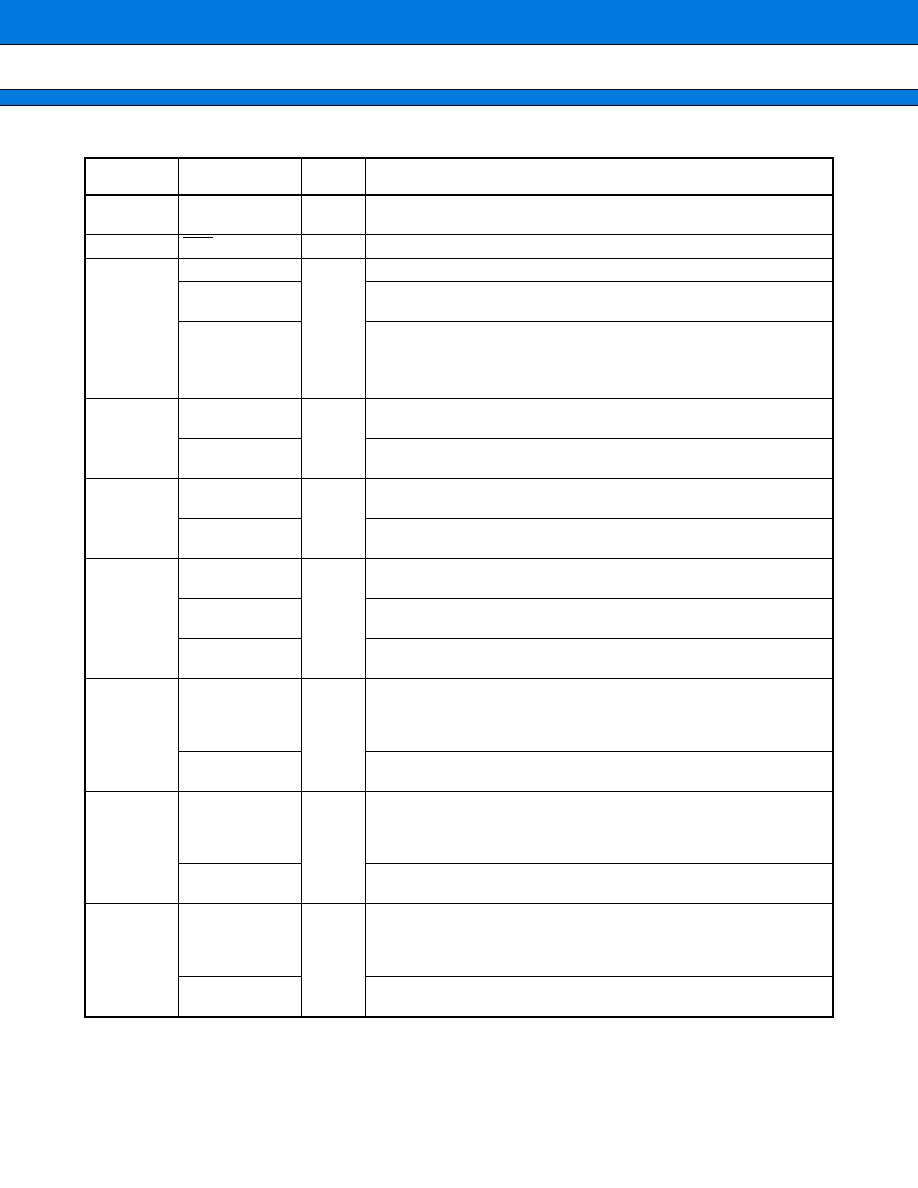

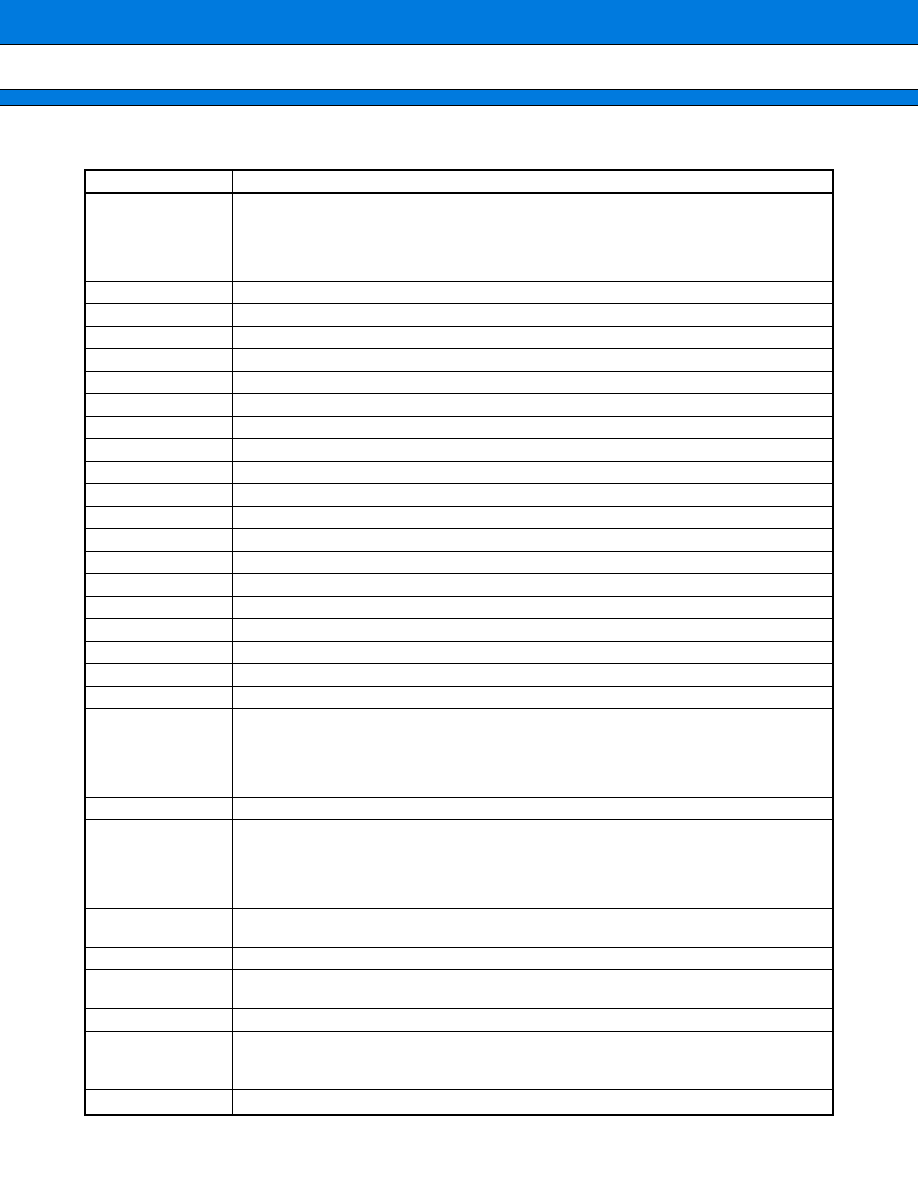

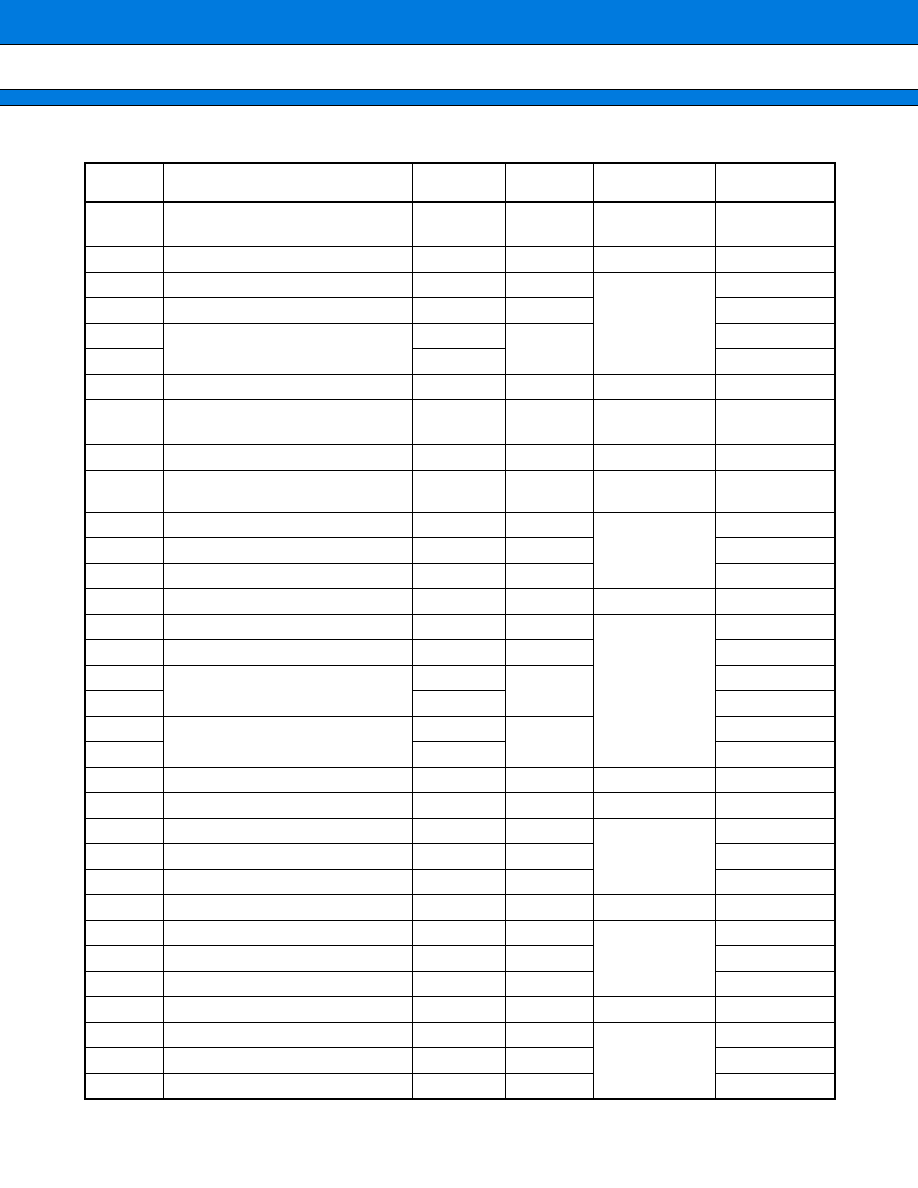

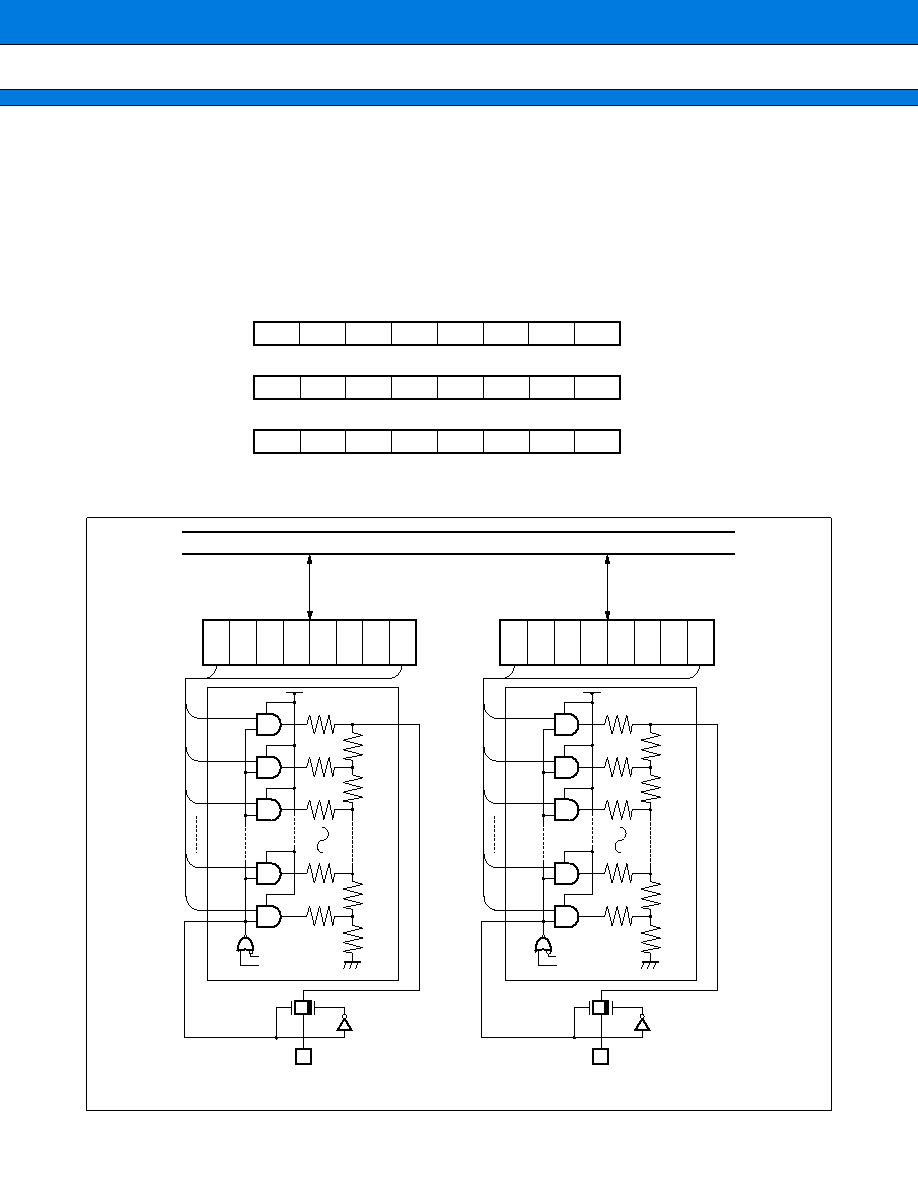

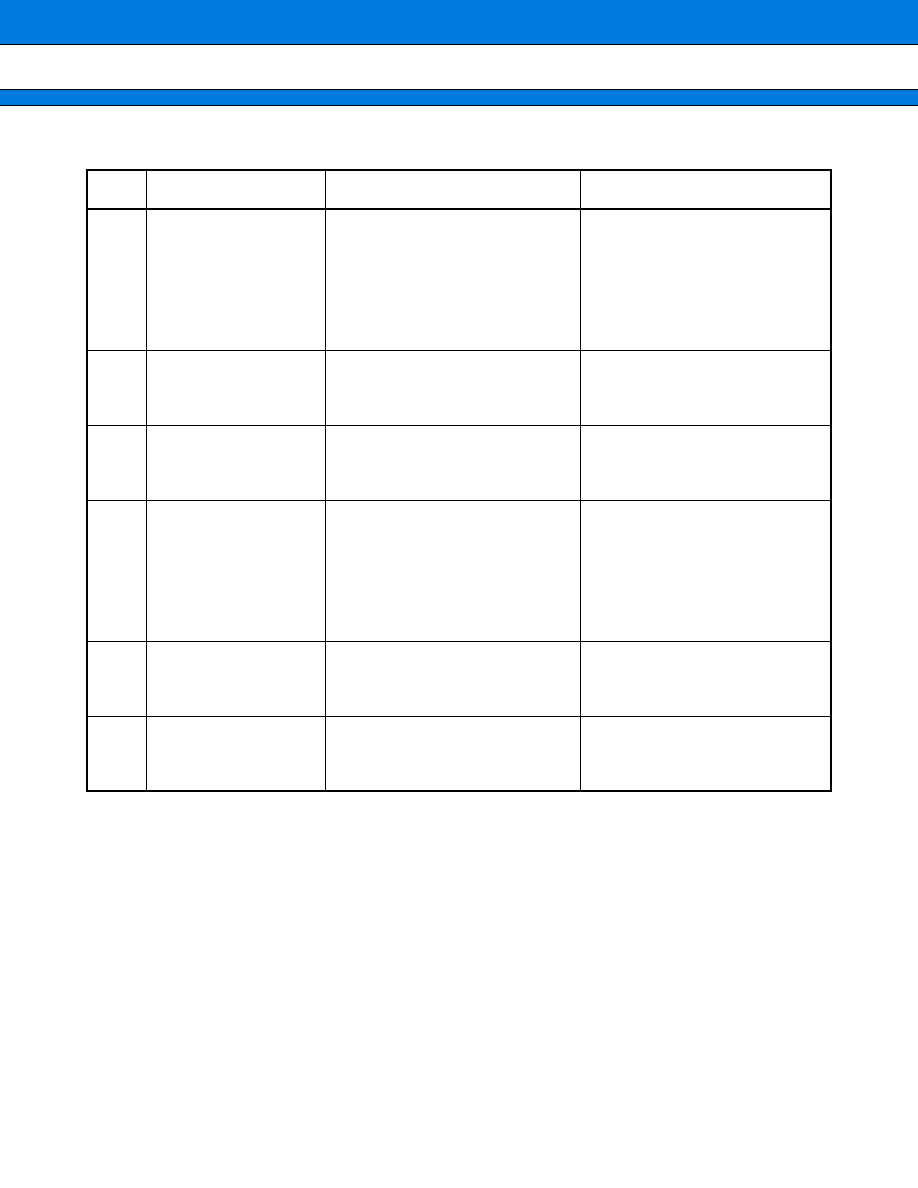

I/O CIRCUIT TYPE

(Continued)

Type

Circuit

Remarks

A

∑ Oscillation feedback resistor:

Approx. 1 M

B

∑ Hysteresis input with pull-up

resistor

C

∑ CMOS input port

D

∑ Hysteresis input port

E

∑ CMOS level output

X1

X0

Standby control

Standby control

CMOS

13

MB90230 Series

(Continued)

Type

Circuit

Remarks

F

∑ CMOS level output

∑ Hysteresis input

G

∑ Input pull-up resistor control

provided

∑ CMOS level input/output

H

∑ CMOS level input/output

∑ Open-drain control provided

Standby control

Standby control

CMOS

Pull-up control

CMOS

Open-drain control signal

Standby control

MB90230 Series

14

(Continued)

Type

Circuit

Remarks

I

∑ CMOS level output

∑ Hysteresis input

∑ Open-drain control provided

J

∑ CMOS level input/output

∑ Analog input

K

∑ CMOS level input/output

∑ Analog output

∑ Also serving for D/A output

L

∑ CMOS level output

∑ Hysteresis input

∑ Open-drain control provided

CMOS

Open-drain control signal

Standby control

CMOS

Analog input

Standby control

CMOS

DA output

Standby control

Standby control

Open-drain control signal

15

MB90230 Series

s

HANDLING DEVICES

1. Preventing Latchup

Latchup may occur on CMOS ICs if voltage higher than V

CC

or lower than V

SS

is applied to input and output pins

other than medium- to high-voltage pins or if higher than the voltage wihich shows on "1. Absolute Maximum

Ratings" in section "

s

Electrical Characteristics" is applied between V

CC

and V

SS

.

When latchup occurs, power supply current increases rapidly and might thermally damage elements. When

using, take great care not to exceed the absolute maximum ratings.

Also, take care to prevent the analog power supply (AV

CC

and AVR) and analog input from exceeding the digital

power supply (V

CC

) when the analog system power supply is turned on and off.

2. Treatment of Unused Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down

resistor.

3. External Reset Input

To reset the internal circuit by the Low-level input to the RST pin, the Low-level input to the RST pin must be

maintained for at least five machine cycles. Pay attention to it if the chip uses external clock input.

4. V

CC

and V

SS

Pins

Apply equal potential to the V

CC

and V

SS

pins.

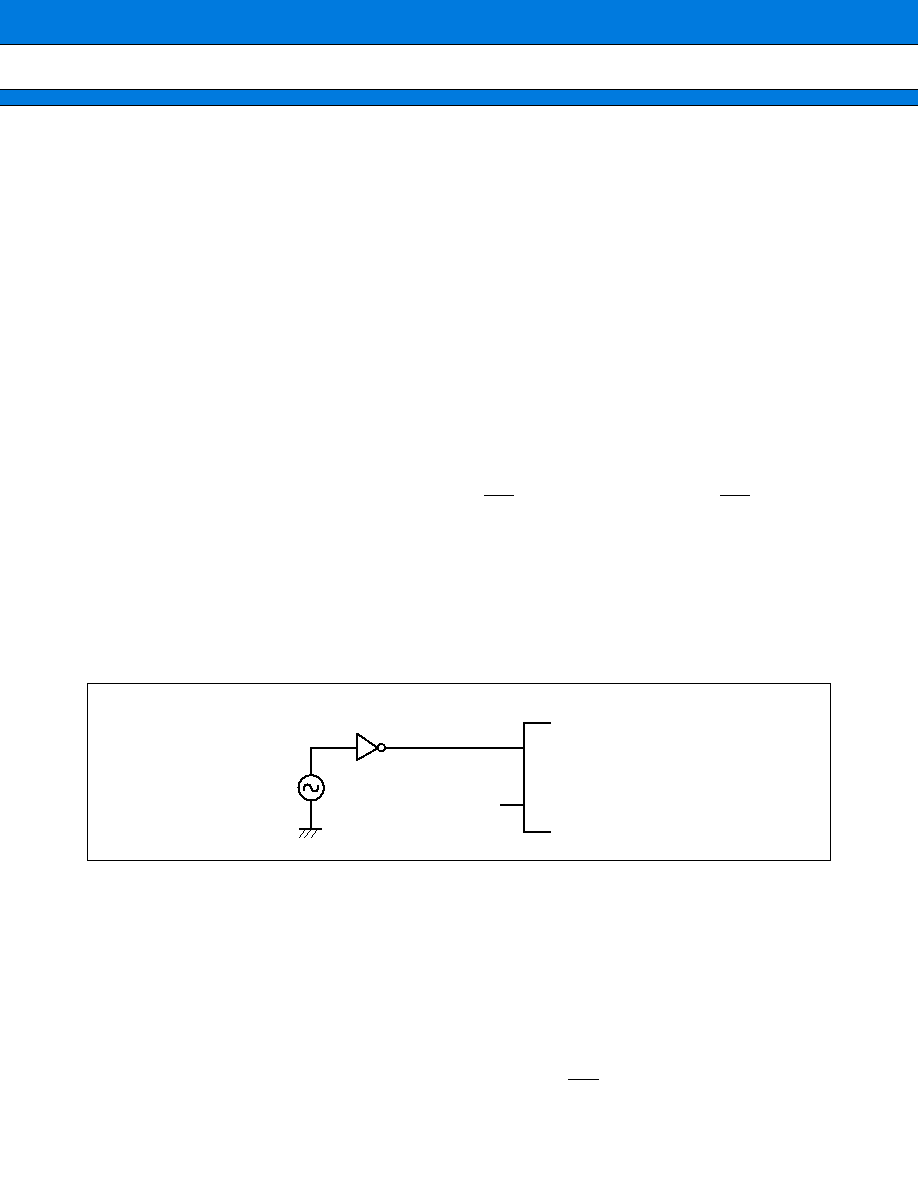

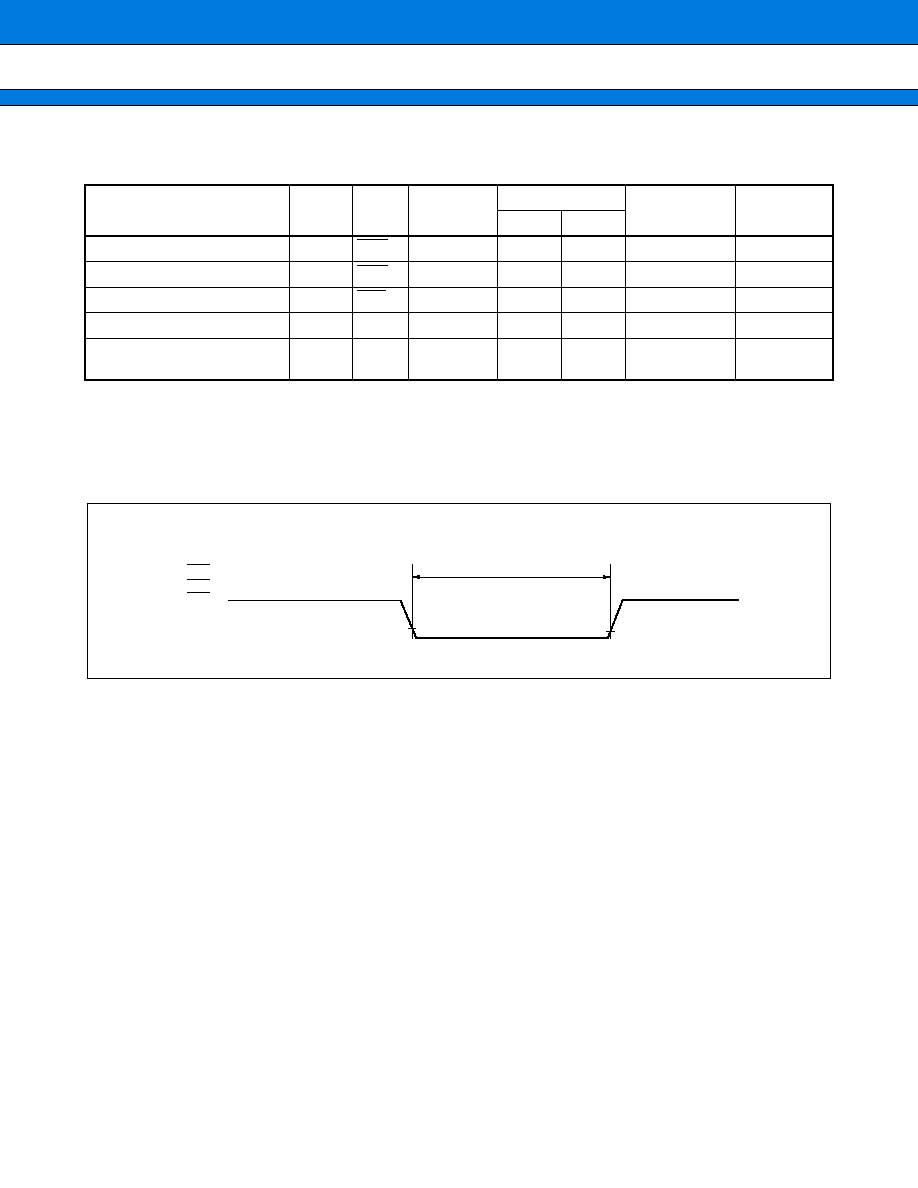

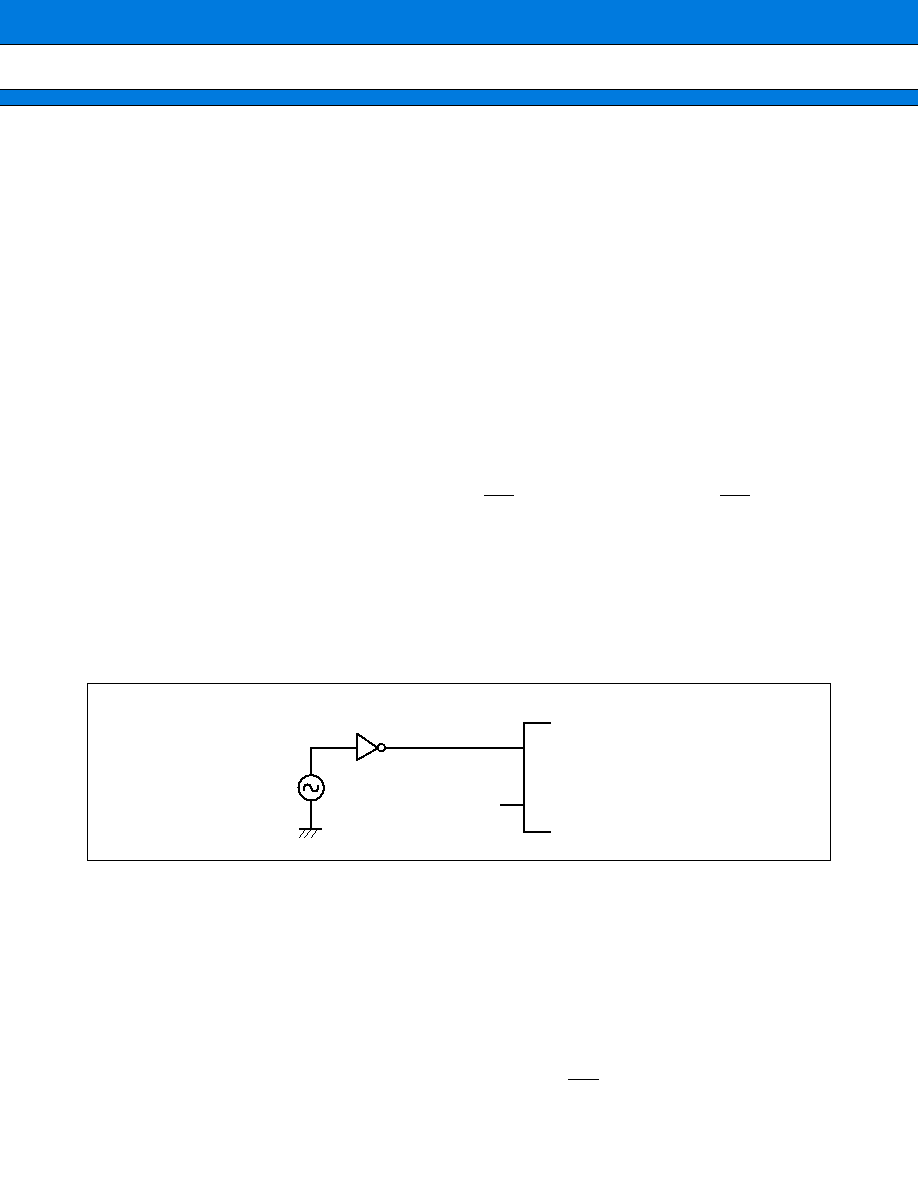

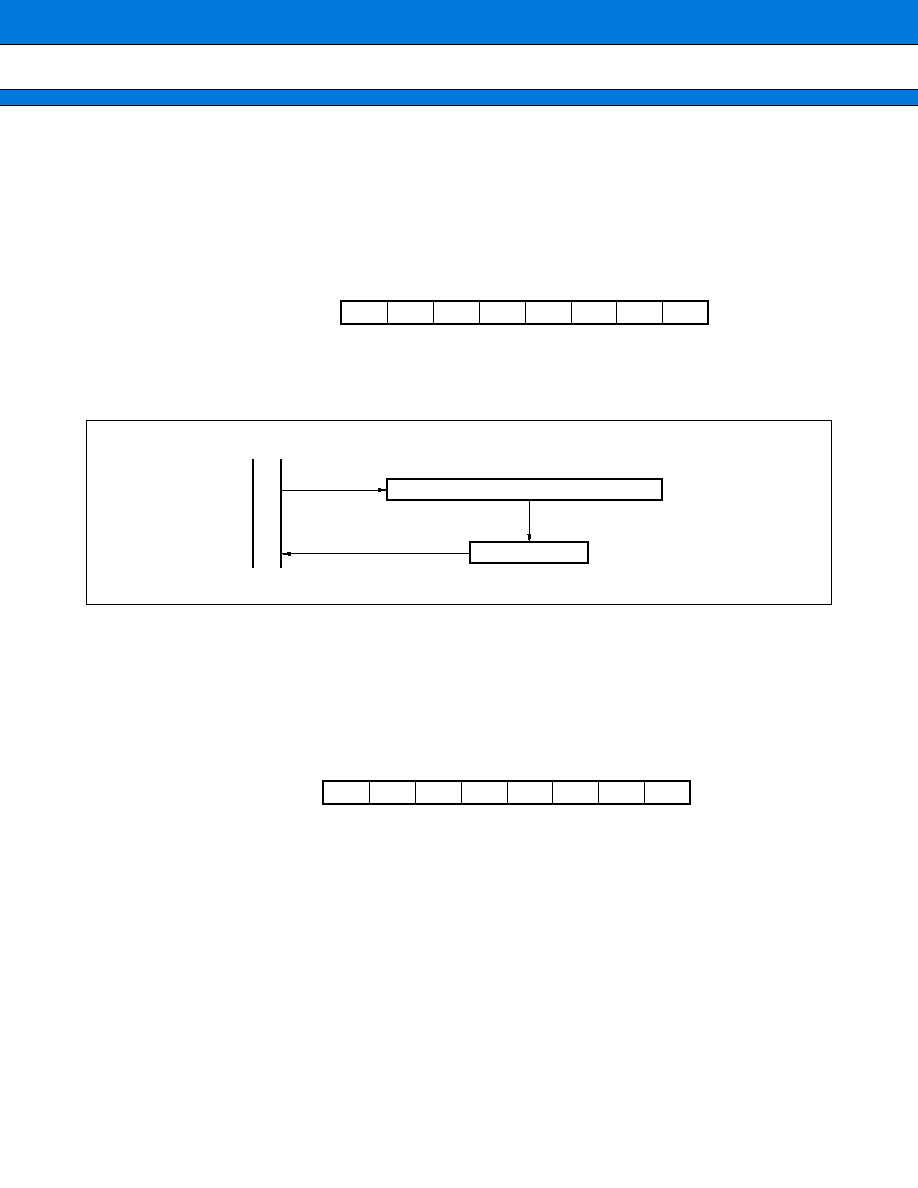

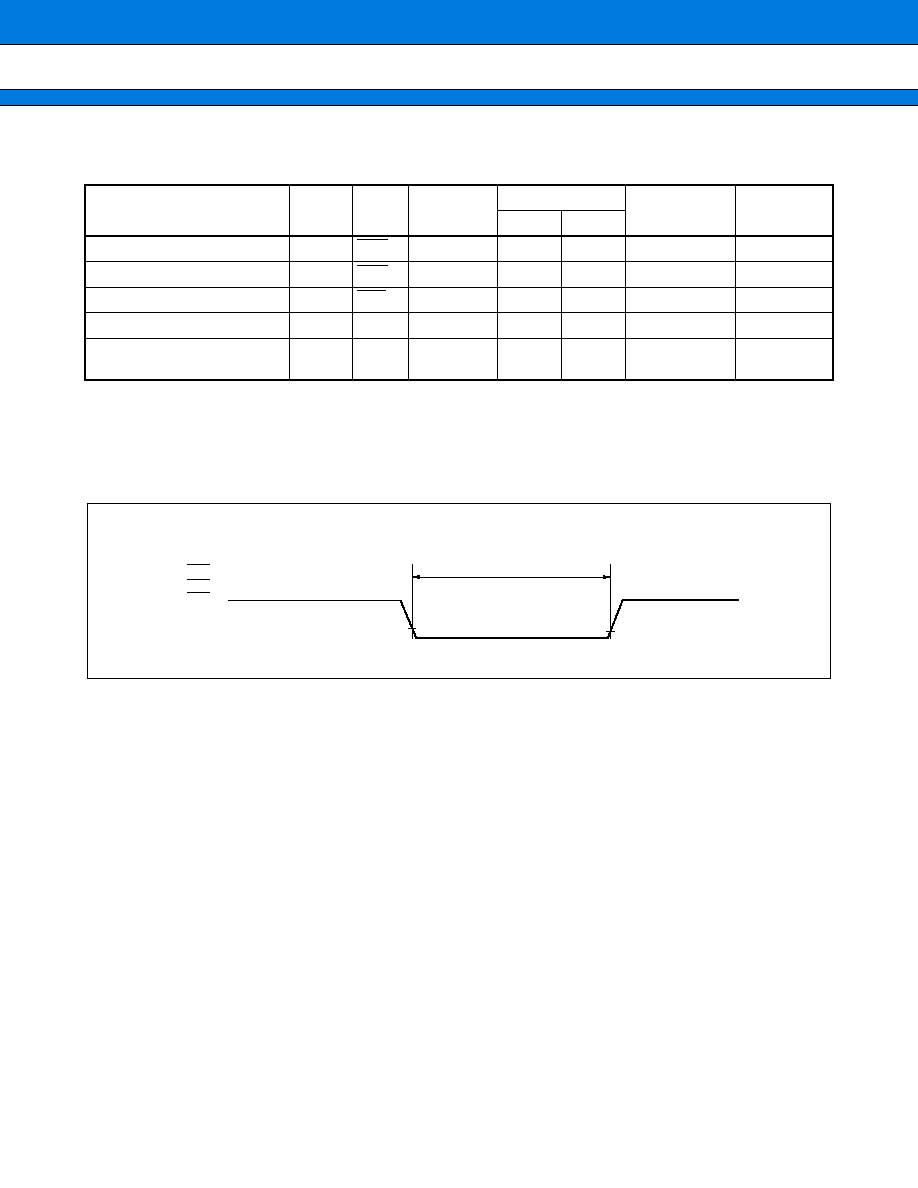

5. Notes on Using an External Clock

When using an external clock, drive the X0 pin as illustrated below:

6. Power-on Sequence for A/D Converter Power Supplies and Analog Inputs

Be sure to turn on the digital power supply (V

CC

) before applying voltage to the A/D converter power supplies

(AV

CC

, AVRH, and AVRL) and analog inputs (AN0 to AN15).

When turning power supplies off, turn off the A/D converter power supplies (AV

CC

, AVRH, and AVRL) and analog

inputs (AN0 to AN15) first, then the digital power supply (AV

CC

).

When turning AVRH on or off, be careful not to let it exceed AV

CC

.

7. Pin set when turning on power supplies

When turning on power supplies, set the hardware standby input pin (HST) to "H".

Use of External Clock

X0

X1

MB90234

MB90230 Series

16

8. Program Mode

When shipped from Fujitsu, and after each erasure, all bits (96K

◊

8 bits) in the MB90W234 and MB90P234 are

in the "1" state. Data is introduced by selectively programming "0's" into the desired bit locations. Bits cannot

be set to 1 electrically.

9. Erasure Procedure

Data written in the MB90W234 is erased (from 0 to 1) by exposing the chip to ultraviolet rays with a wavelength

of 2,537≈ through the translucent cover.

Recommended irradiation dosage for exposure is 10 Wsec/cm

2

. This amount is reached in 15 to 20 minutes

with a commercial ultraviolet lamp positioned 2 to 3 cm above the package (when the package surface

illuminance is 1200

µ

W/cm

2

).

If the ultraviolet lamp has a filter, remove the filter before exposure. Attaching a mirrored plate to the lamp

increases the illuminance by a factor of 1.4 to 1.8, thus shortening the required erasure time. If the translucent

part of the package is stained with oil or adhesive, transmission of ultraviolet rays is degraded, resulting in a

longer erasure time. In that case, clean the translucent part using alcohol (or other solvent not affecting the

package).

The above recommended dosage is a value which takes the guard band into consideration and is a multiple of

the time in which all bits can be evaluated to have been erased. Observe the recommended dosage for erasure;

the purpose of the guard band is to ensure erasure in all temperature and supply voltage ranges. In addition,

check the lifespan of the lamp and control the illuminance appropriately.

Data in the MB90W234 is erased by exposure to light with a wavelength of 4000≈ or less.

Data in the device is also erased even by exposure to fluorescent lamp light or sunlight although the exposure

results in a much lower erasure rate than exposure to 2537≈ ultraviolet rays. Note that exposure to such lights

for an extended period will therefore affect system reliability. If the chip is used where it is exposed to any light

with a wavelength of 4000≈ or less, cover the translucent part, for example, with a protective seal to prevent

the chip from being exposed to the light.

Exposure to light with a wavelength of 4,000 to 5,000≈ or more will not erase data in the device. If the light

applied to the chip has a very high illuminance, however, the device may cause malfunction in the circuit for

reasons of general semiconductor characteristics. Although the circuit will recover normal operation when

exposure is stopped, the device requires proper countermeasures for use in a place exposed continuously to

such light even though the wavelength is 4,000≈ or more.

17

MB90230 Series

10. Recommended Screening Conditions

High-temperature aging is recommended for screening before packaging.

11. Write Yield

OTPROM products cannot be write-tested for all bits due to their nature. Therefore the write yield cannot always

be guaranteed to be 100%.

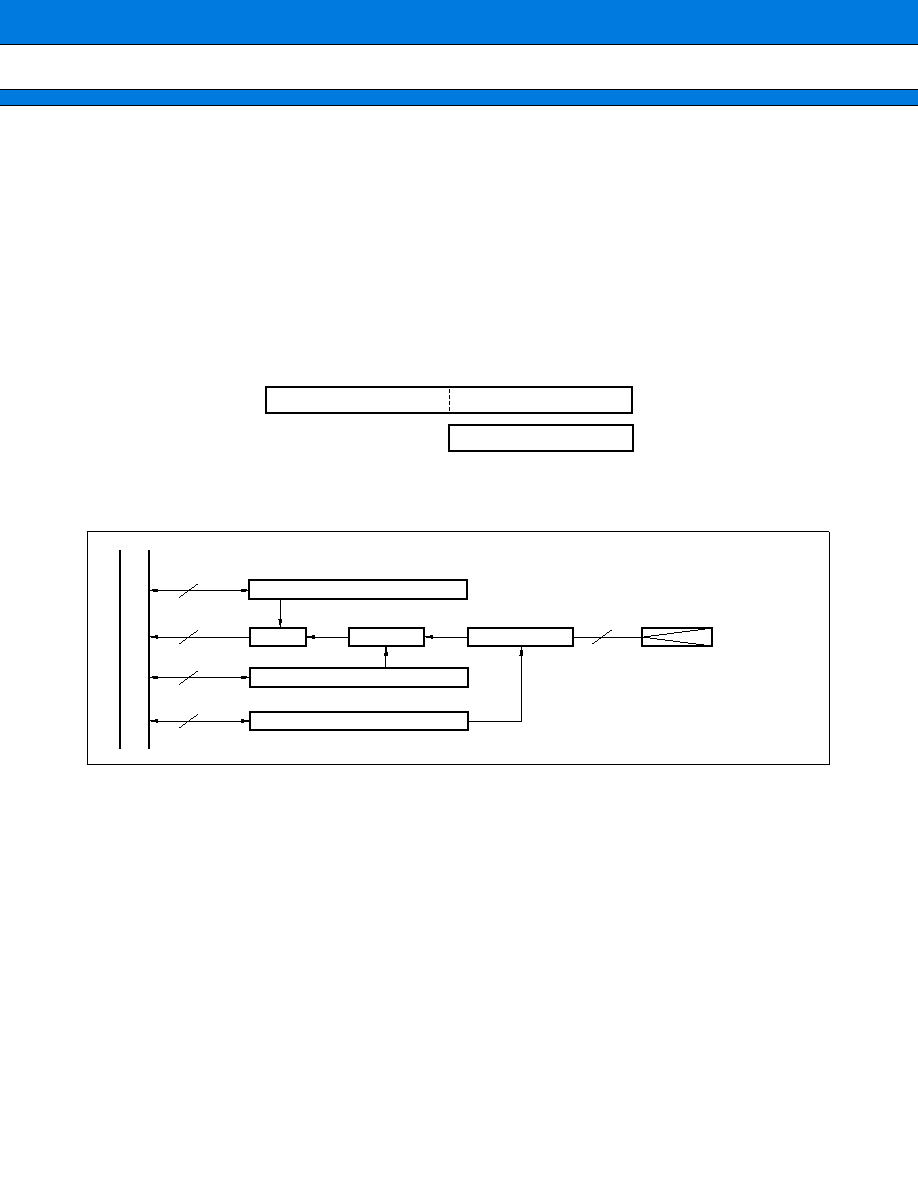

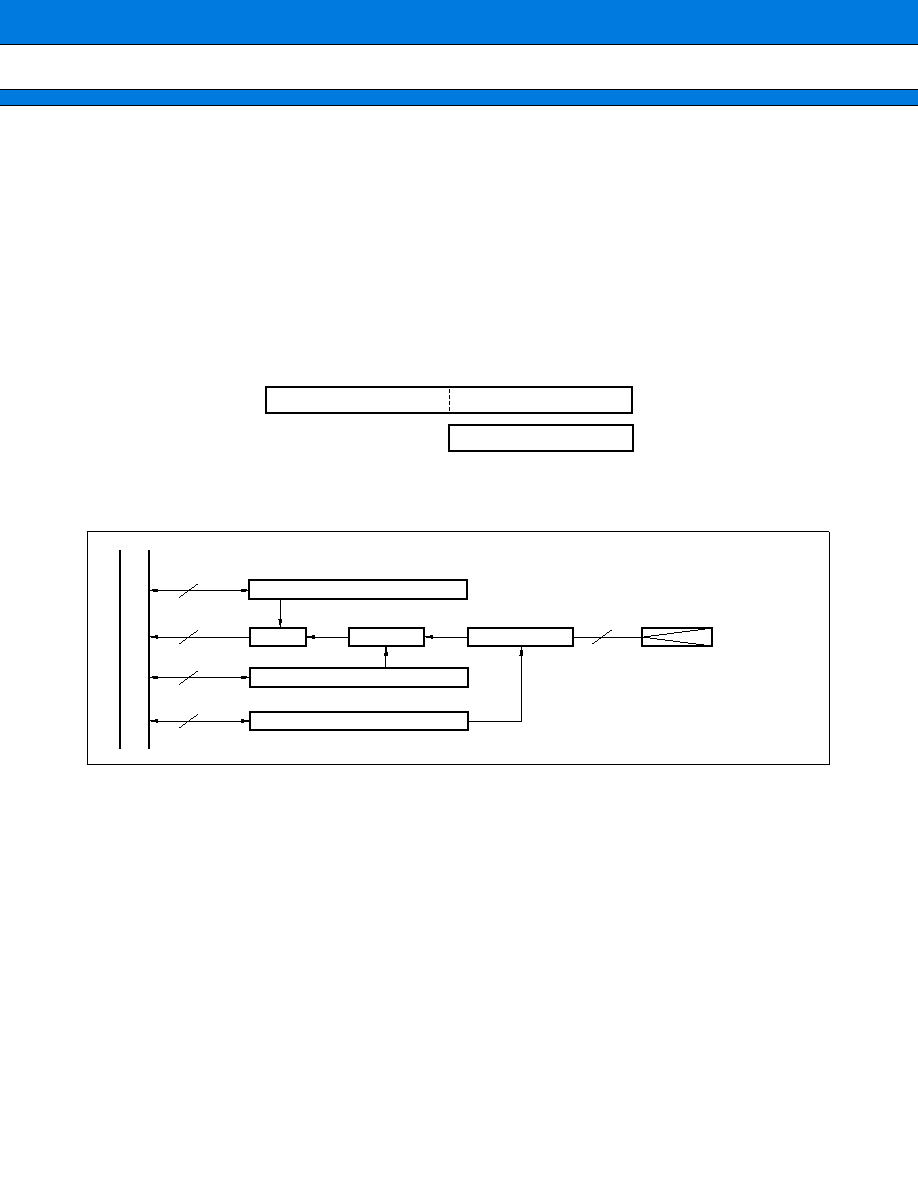

Program, verify

Aging

+150∞C, 48 Hrs.

Data verification

Assembly

MB90230 Series

18

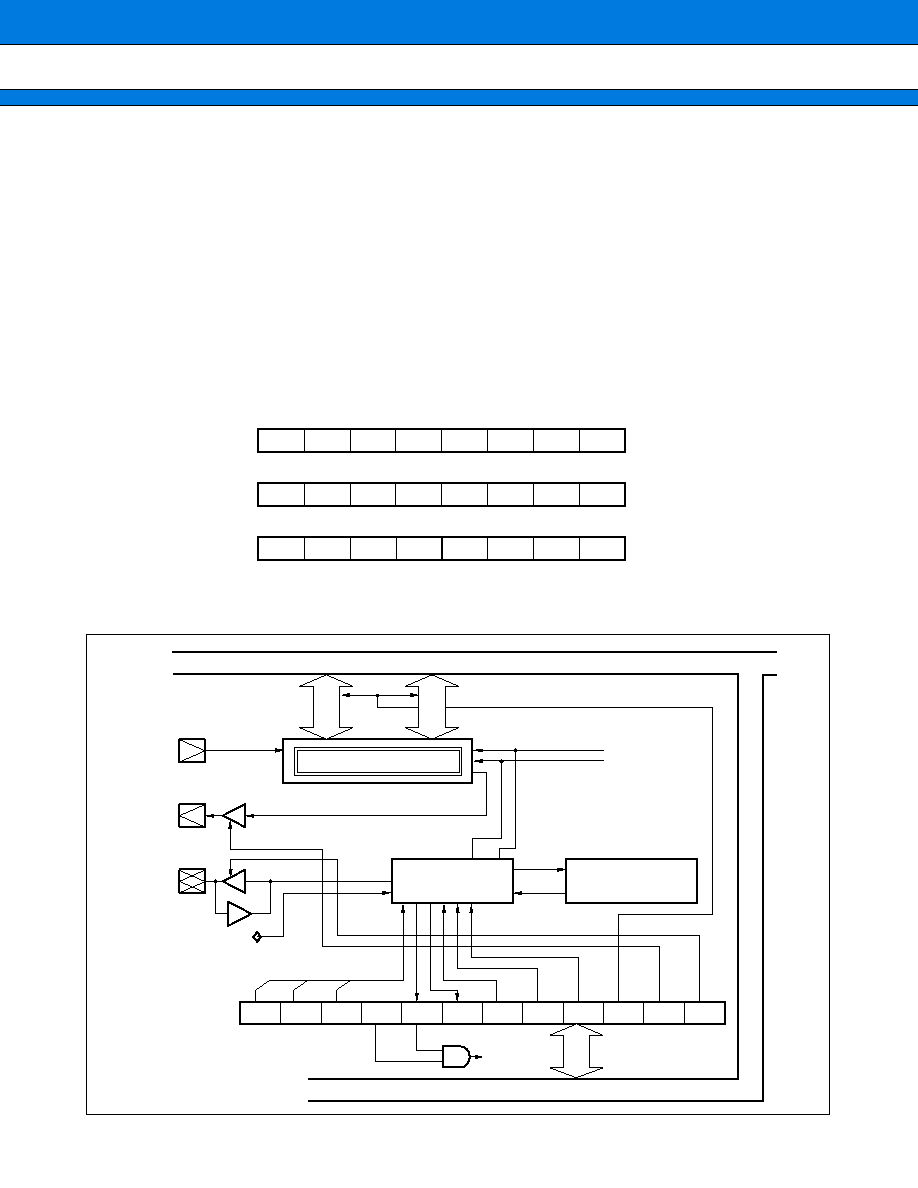

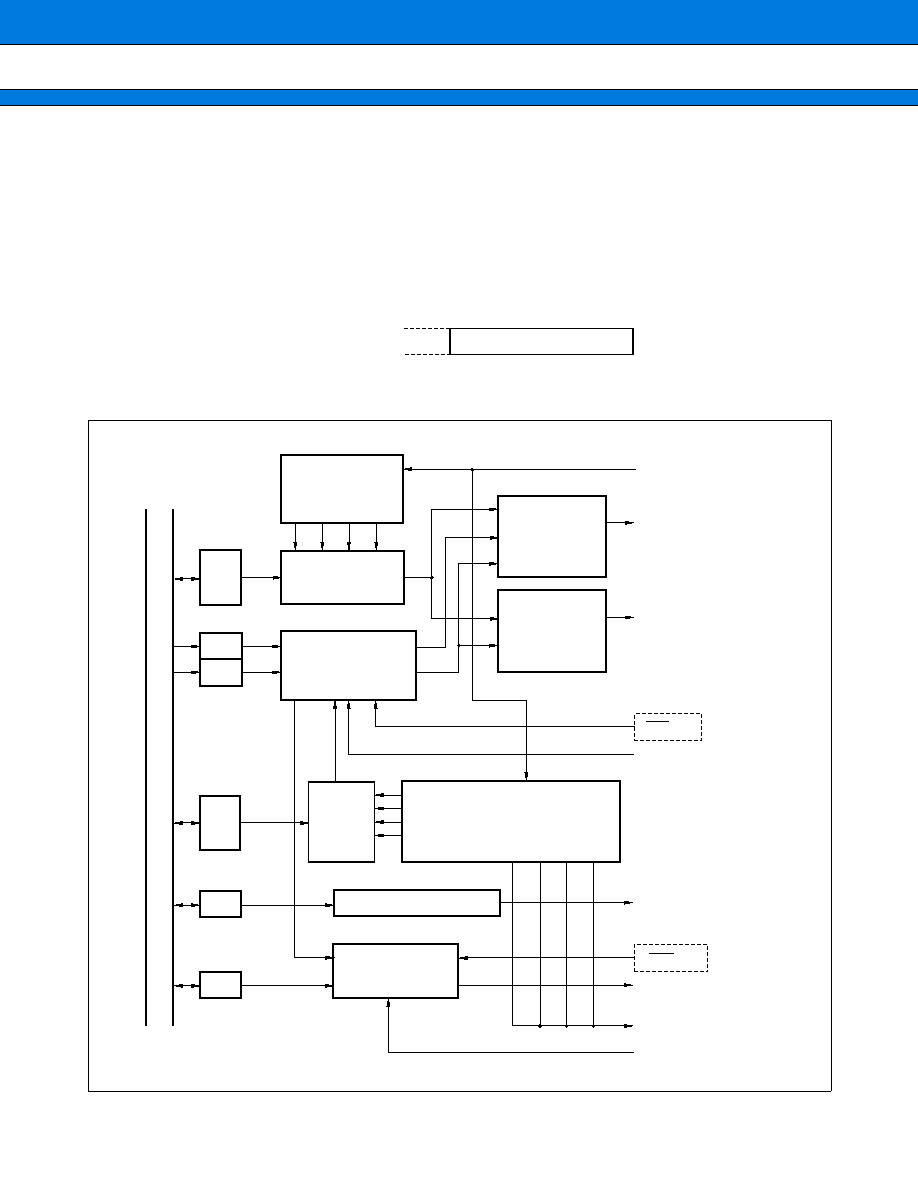

s

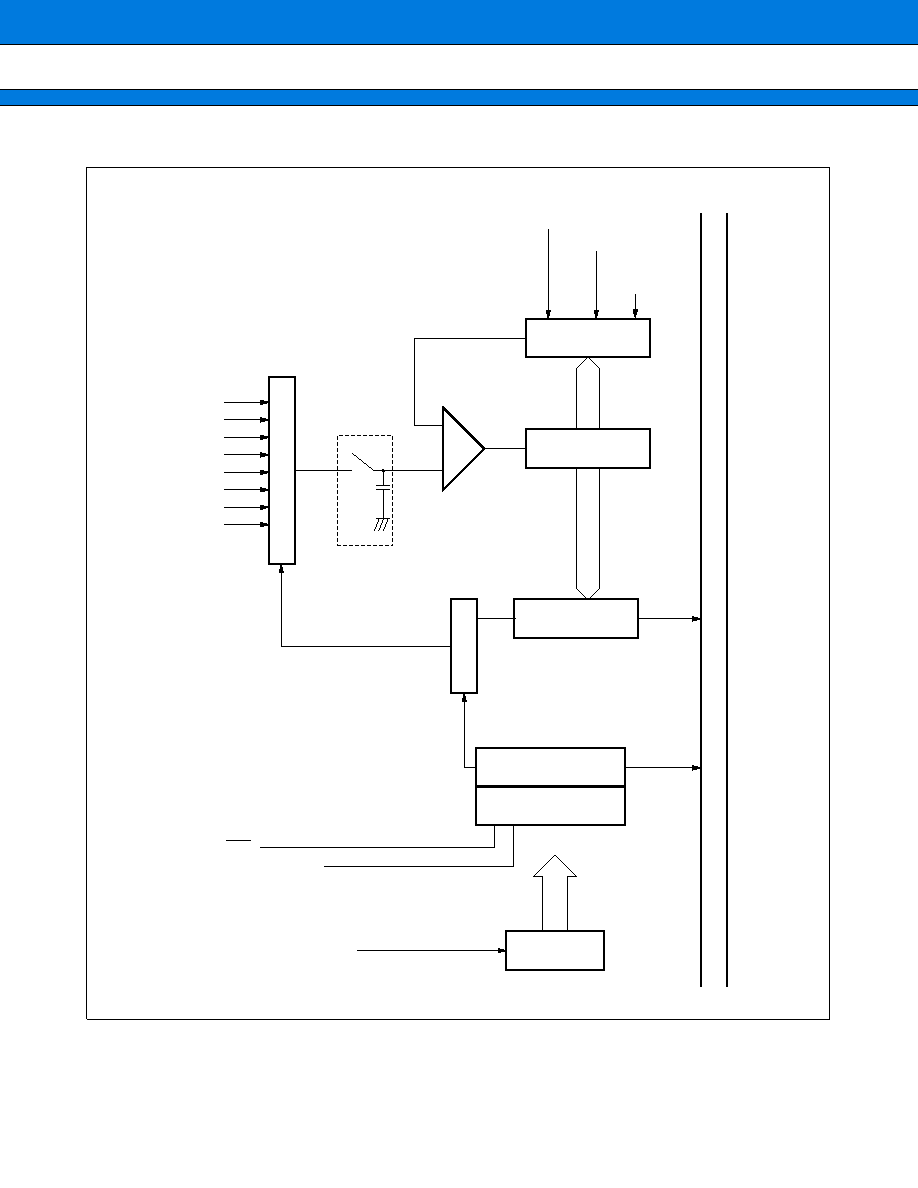

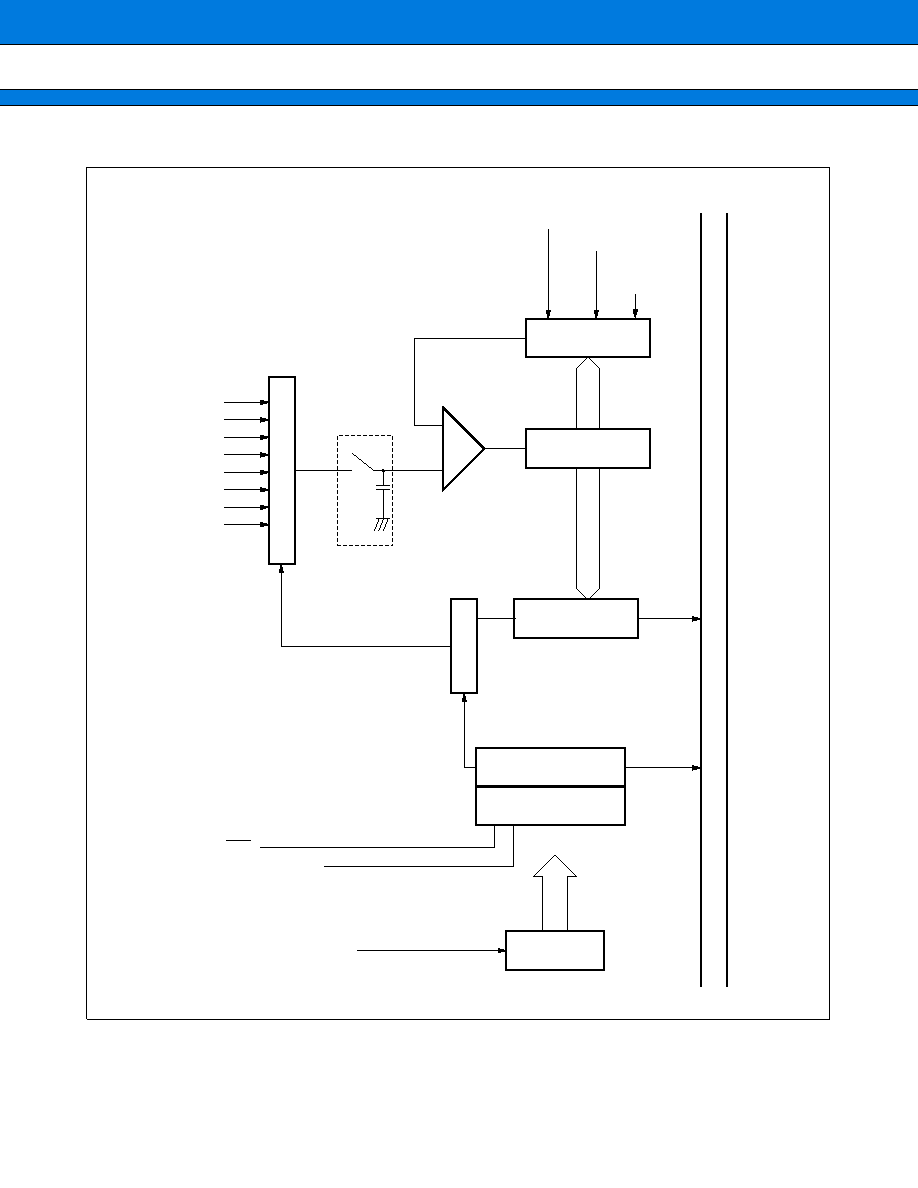

BLOCK DIAGRAM

RAM

Interrupt controller

F

2

MC-16 bus

8

8

8

8

8

8

8

7

8

P00

to

P07

P10

to

P17

P20

to

P27

P30

to

P37

P40

to

P47

P50

to

P57

P60

to

P67

P70

to

P76

P80

to

P87

I/O ports (84 lines)

CPU

F

2

MC-16F

ROM

8-bit PPG timer

I/O timer

IN0, 1

IN2, 3

Level comparator

7

P90

to

P96

CMP

6

PA0

to

PA5

4

X0, X1

RST

HST

TRG

PPG

External interrupt

UART

SIN0

SOT0

SCK0

CKOT

Extended serial

I/O interface

SIN1, 2

SOT1, 2

SCK1, 2

10-bit A/D converter

AVcc

AVRH, AVRL

AVss

ATG

AN0 to AN7

D/A converter

16-bit input capture

◊

4

16-bit output compare

◊

6

16-bit free run timer

DA0

DA1

P00 to P27 (24 lines): Provided with input pull-up resistor setting registers

P94 to P96, PA0 to PA5 (9 lines): Provided with open-drain setting registers

INT0

to

INT3

Communication prescaler

4

8-bit PWM

PWM0

to

PWM5

6 ch

OUT0, 1

OUT2, 3

OUT4, 5

Serial E

2

PROM interface

2

ECS, ESK

EDO

EDI

Clock controller

19

MB90230 Series

s

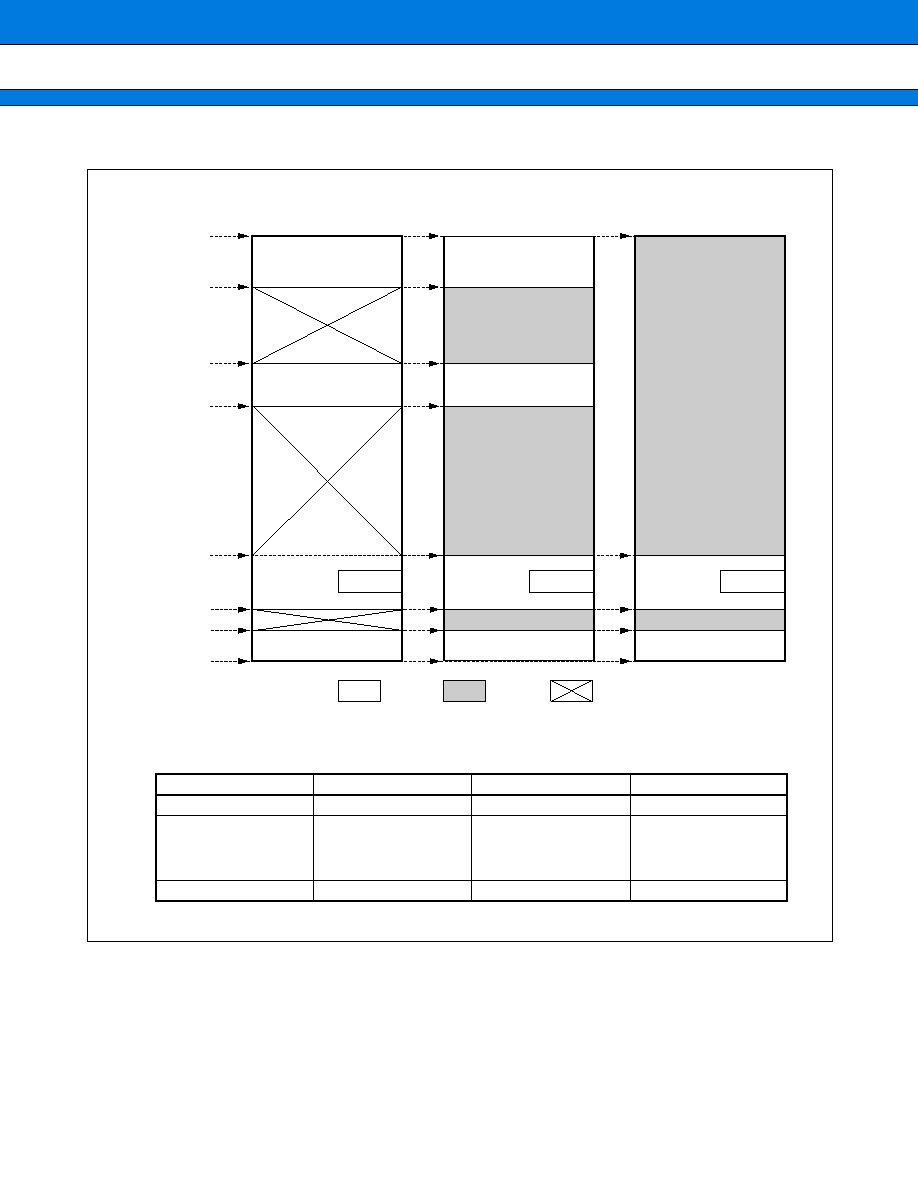

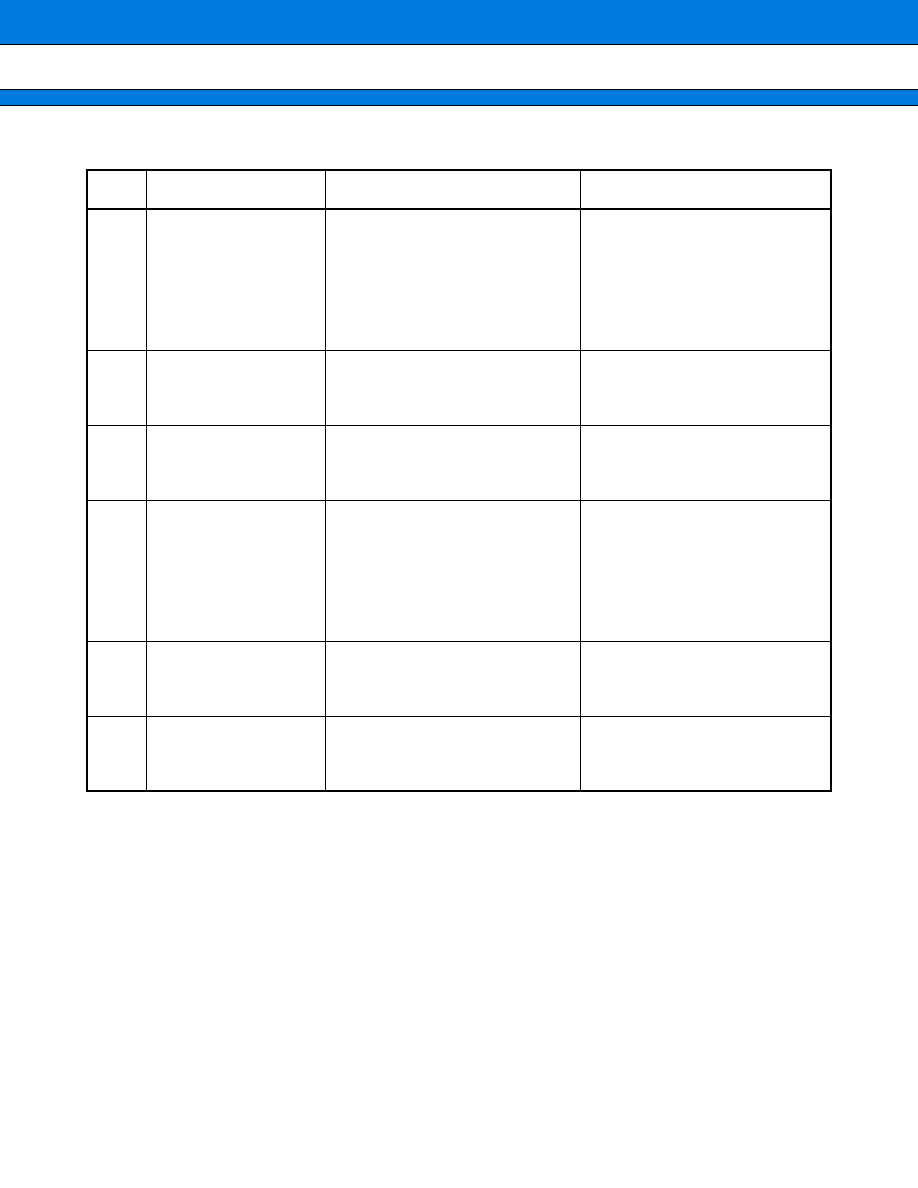

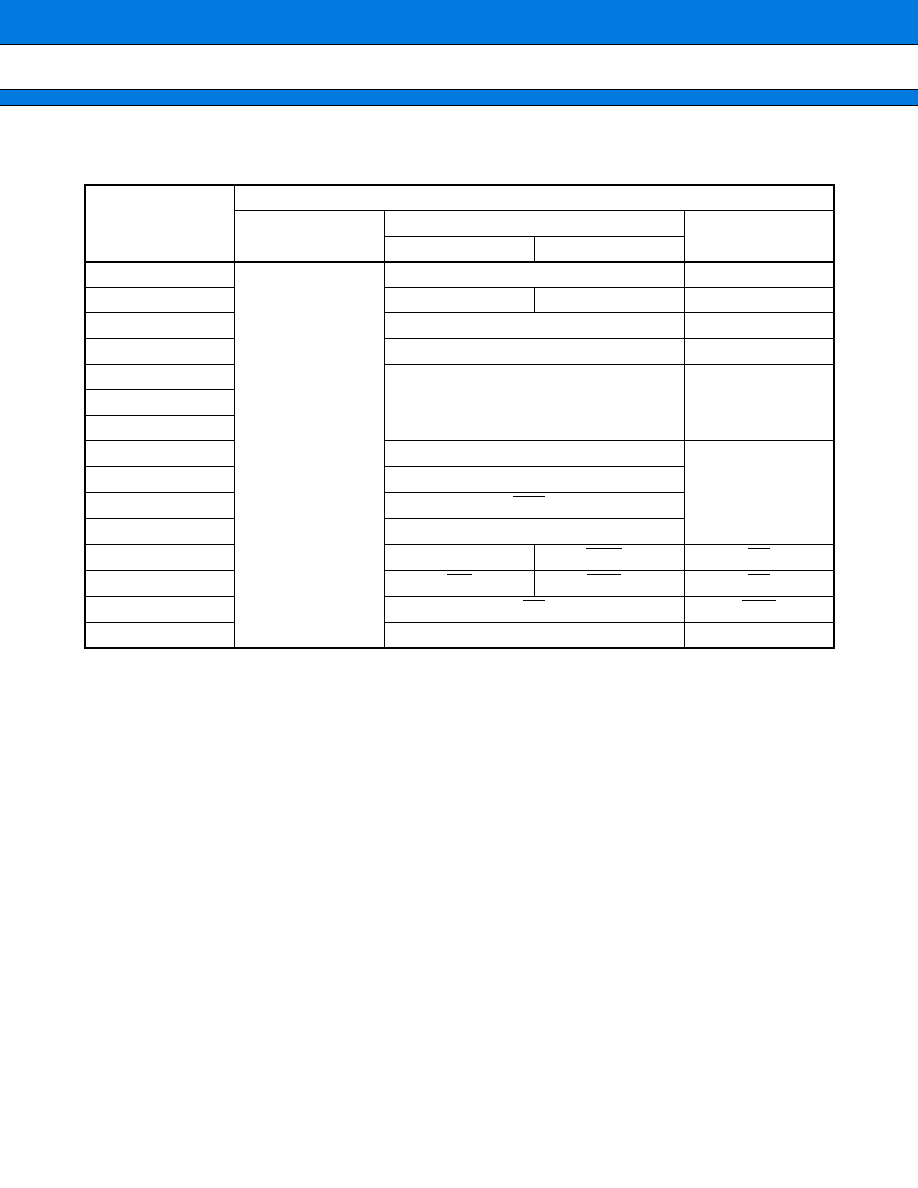

MEMORY MAP

The MB90230 series can access the 00 bank to read ROM data written to the upper 48-KB locations in the FF

bank. An advantage of reading written to data addresses FFFFFF

H

-FF4000

H

from addresses 00FFFF

H

-004000

H

is

that you can use the small model of a C compiler.

Note, however, that the products with more than 48KB ROM space (MB90V230, MB90P/W234, MB90234) cannot

read data in addresses other than FFFFFF

H

to FF4000

H

from the 00 bank.

FFFFFF

H

Address1#

00FFFF

H

Address#2

Address#3

000100

H

0000C0

H

000000

H

Single-chip mode

Internal ROM and

external bus

External ROM and

external bus

ROM area

ROM area

ROM area

(FF bank image)

ROM area

(FF bank image)

RAM

Registers

RAM

Registers

RAM

Registers

Peripherals

Peripherals

Peripherals

Internal

External

Inhibited area

000000

H

to 000005

H

and 000010

H

to 000015

H

are allocated for external use

when the external bus is enabled.

Note:

Address#3

Address#2

Address#1

Product type

MB90233

MB90V230

MB90234

MB90P234

MB90W234

FF4000

H

(FE0000

H

)

FE8000

H

FE8000

H

004000

H

(004000

H

)

004000

H

004000

H

000900

H

(001100

H

)

000D00

H

000D00

H

MB90230 Series

20

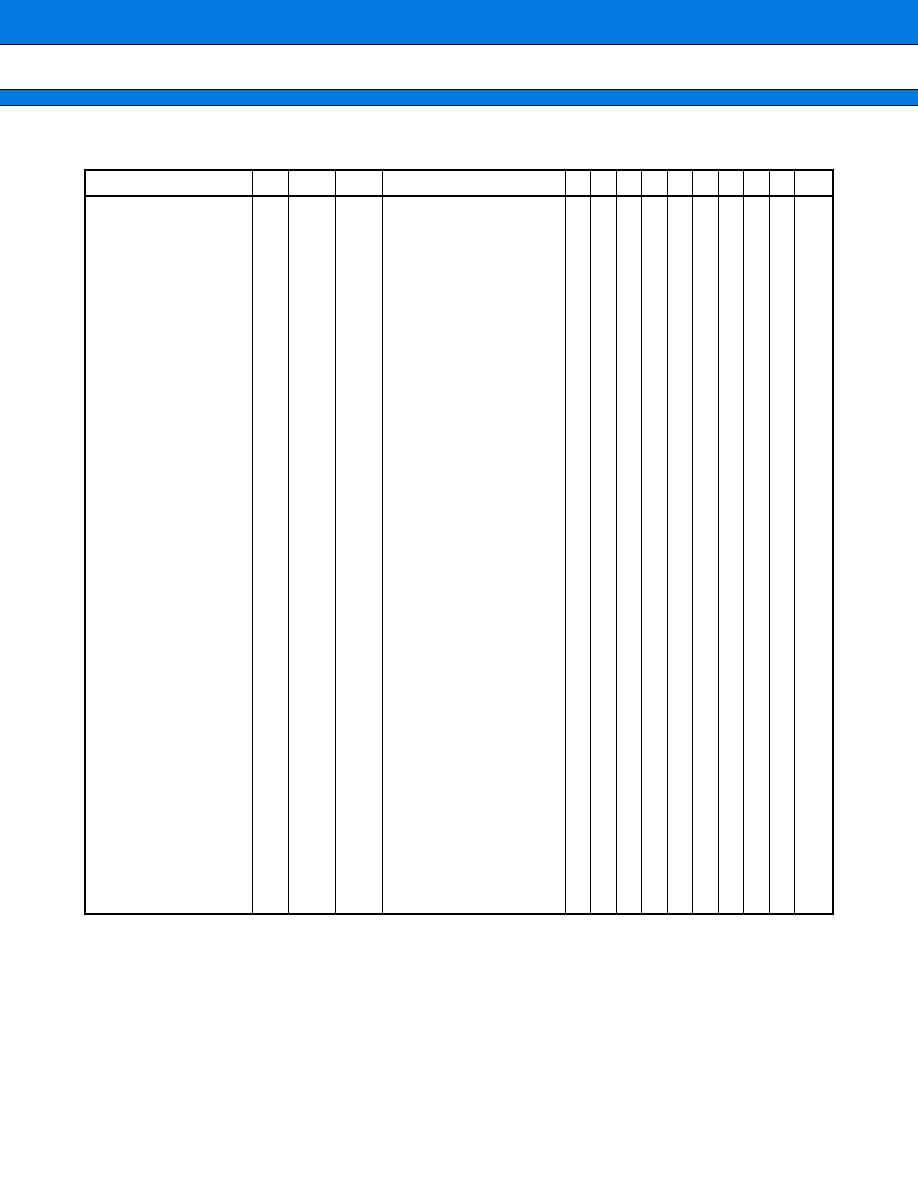

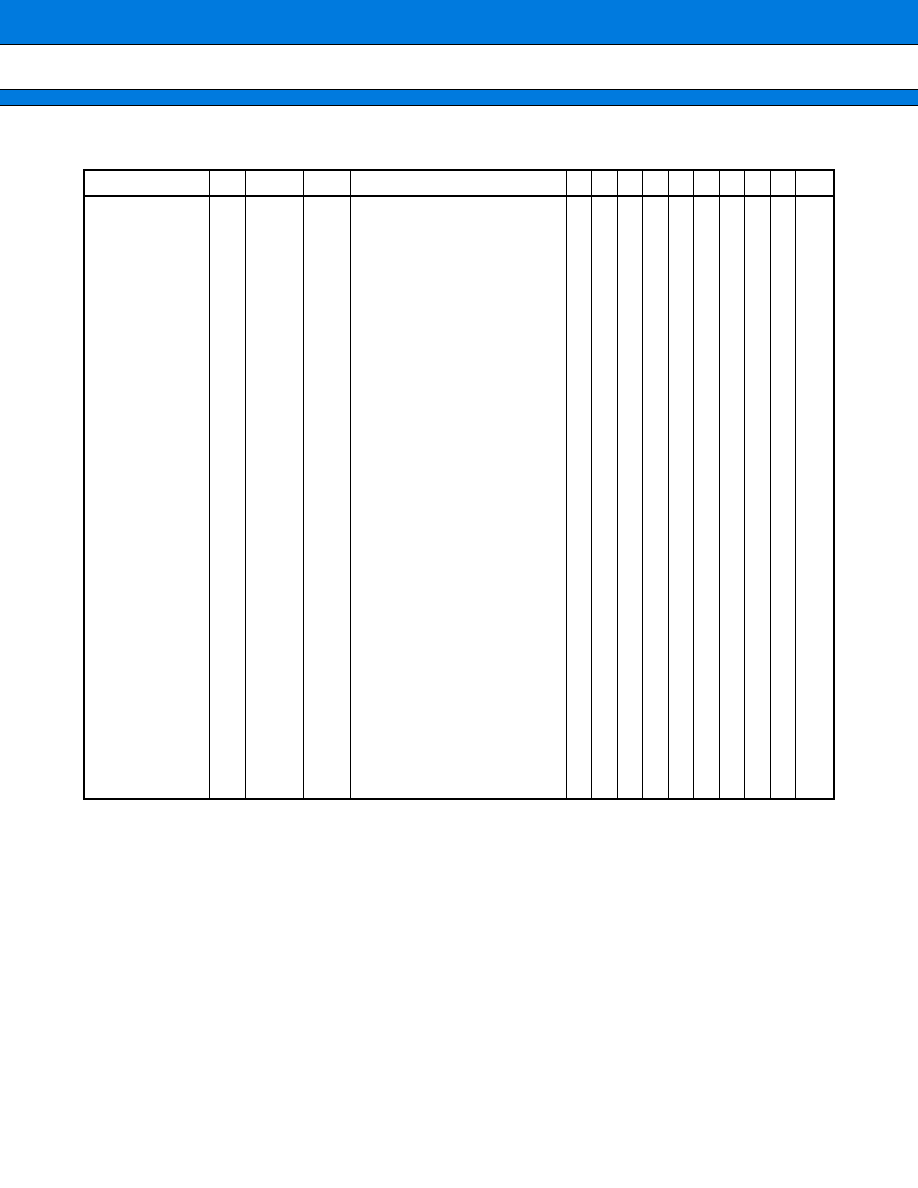

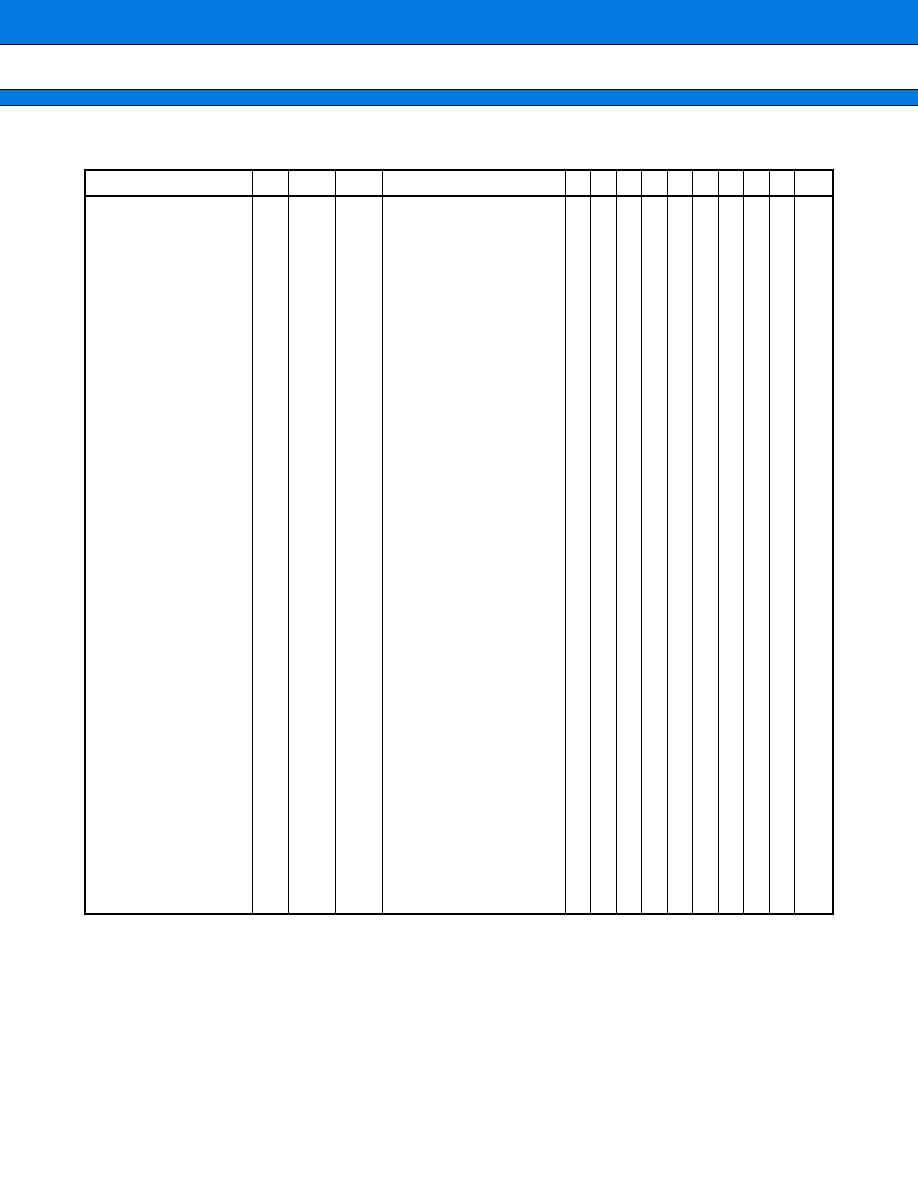

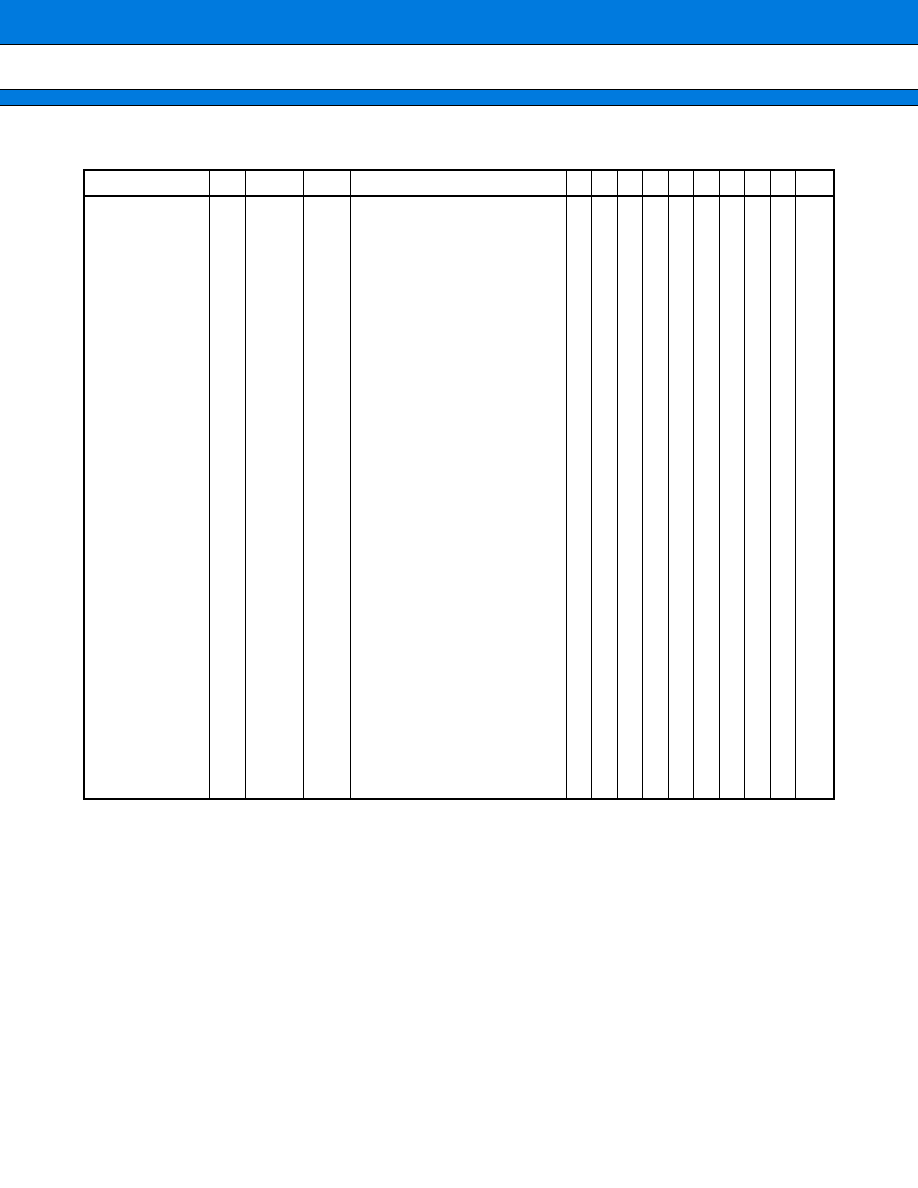

s

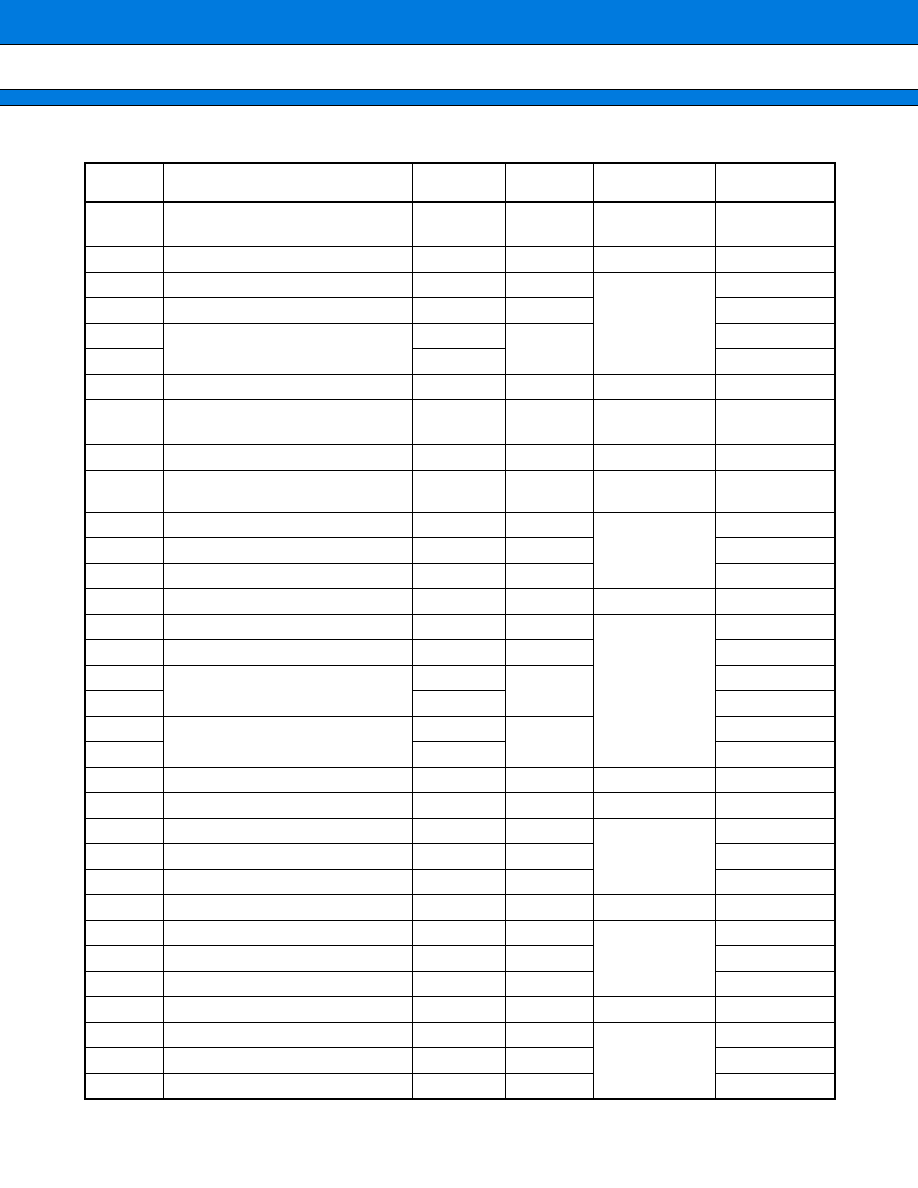

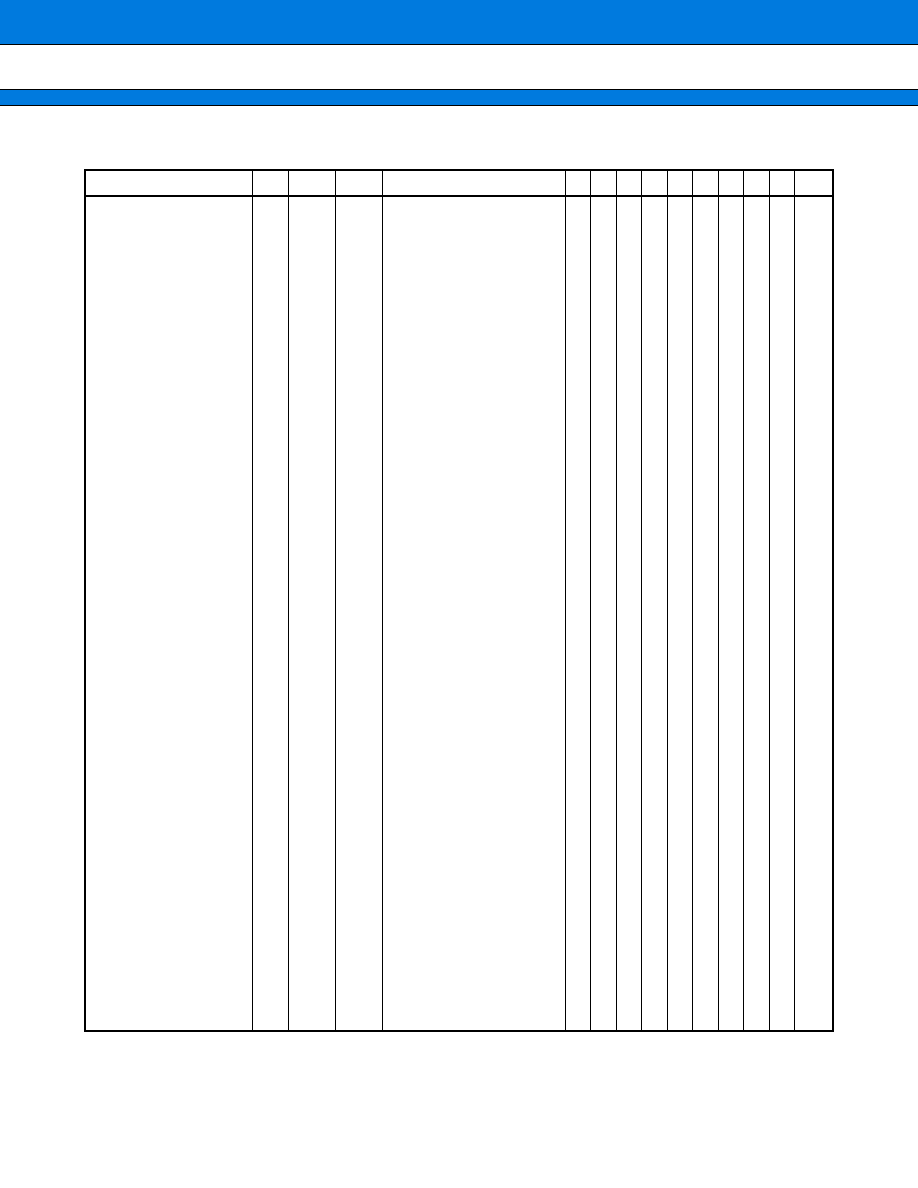

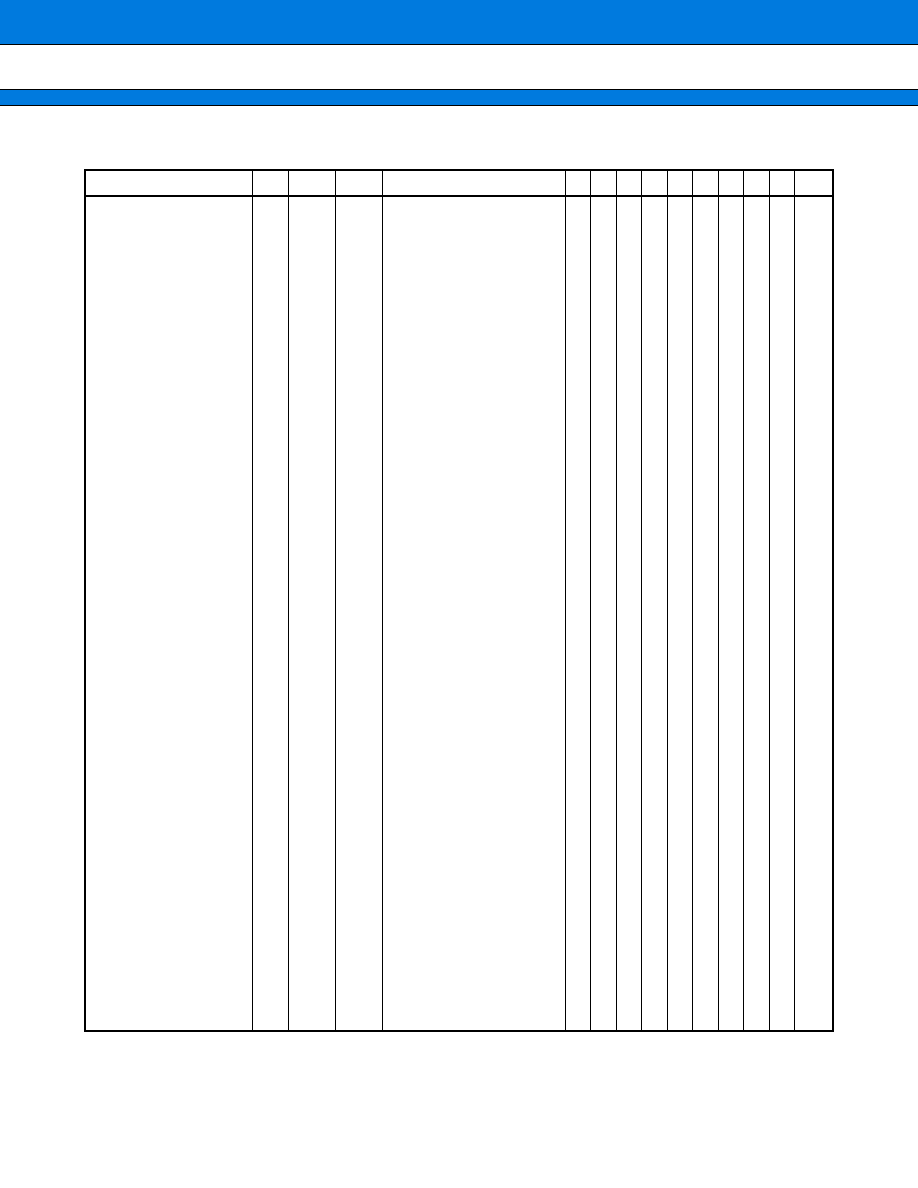

I/O MAP

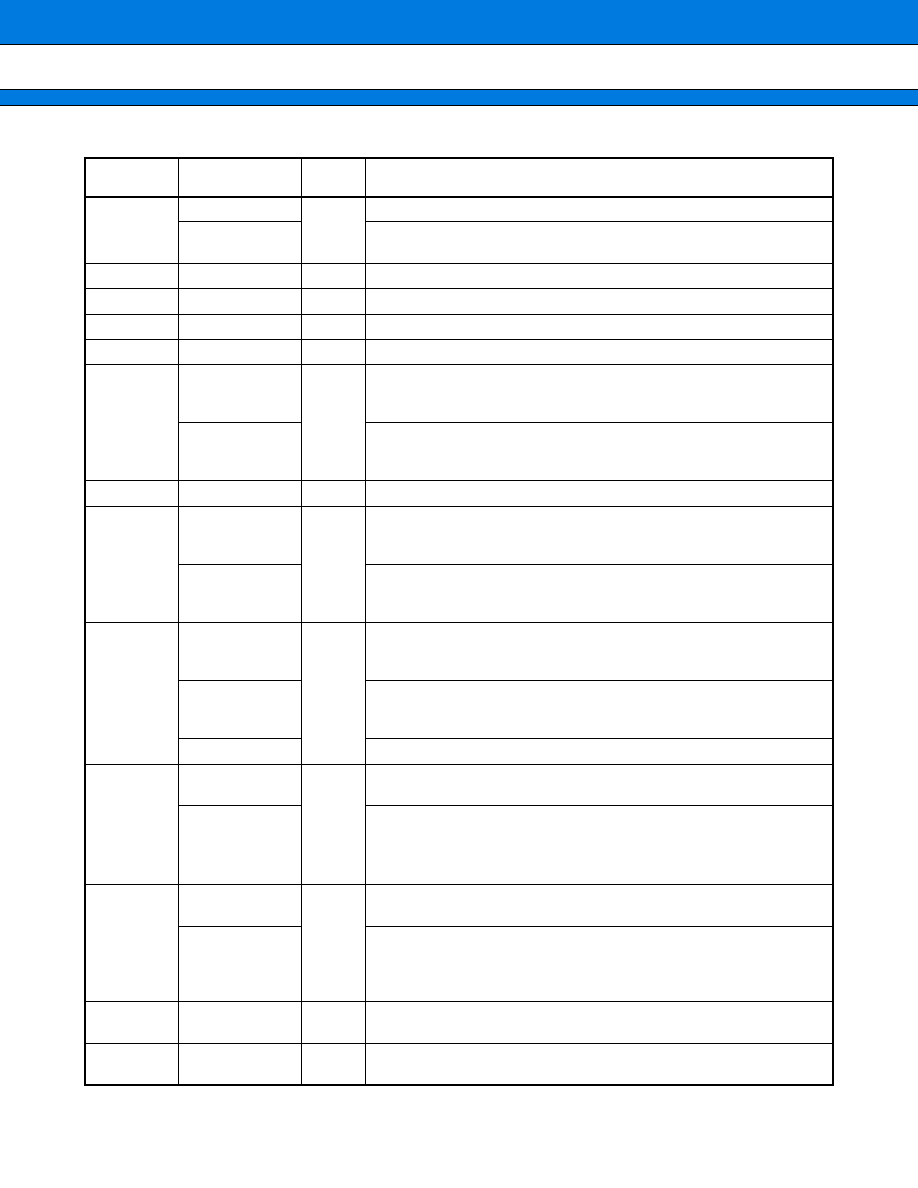

(Continued)

Address

Register

Register

name

Access

Resouce

name

Initial value

00

H

Port 0 data register

PDR0

R/W

Port 0

X X X X X X X X

01

H

Port 1 data register

PDR1

R/W

Port 1

X X X X X X X X

02

H

Port 2 data register

PDR2

R/W

Port 2

X X X X X X X X

03

H

Port 3 data register

PDR3

R/W

Port 3

X X X X X X X X

04

H

Port 4 data register

PDR4

R/W

Port 4

X X X X X X X X

05

H

Port 5 data register

PDR5

R/W

Port 5

X X X X X X X X

06

H

Port 6 data register

PDR6

R/W

Port 6

X X X X X X X X

07

H

Port 7 data register

PDR7

R/W

Port 7

≠ X X X X X X X

08

H

Port 8 data register

PDR8

R/W

Port 8

X X X X X X X X

09

H

Port 9 data register

PDR9

R/W

Port 9

≠ X X X X X X X

0A

H

Port A data register

PDRA

R/W

Port A

≠ ≠ X X X X X X

10

H

Port 0 direction register

DDR0

R/W

Port 0

0 0 0 0 0 0 0 0

11

H

Port 1 direction register

DDR1

R/W

Port 1

0 0 0 0 0 0 0 0

12

H

Port 2 direction register

DDR2

R/W

Port 2

0 0 0 0 0 0 0 0

13

H

Port 3 direction register

DDR3

R/W

Port 3

0 0 0 0 0 0 0 0

14

H

Port 4 direction register

DDR4

R/W

Port 4

0 0 0 0 0 0 0 0

15

H

Port 5 direction register

DDR5

R/W

Port 5

0 0 0 0 0 0 0 0

16

H

Port 6 direction register

DDR6

R/W

Port 6

0 0 0 0 0 0 0 0

17

H

Port 7 direction register

DDR7

R/W

Port 7

≠ 0 0 0 0 0 0 0

18

H

Port 8 direction register

DDR8

R/W

Port 8

0 0 0 0 0 0 0 0

19

H

Port 9 direction register

DDR9

R/W

Port 9

≠ 0 0 0 0 0 0 0

1A

H

Port A direction register

DDRA

R/W

Port A

≠ ≠ 0 0 0 0 0 0

1B

H

Port 0 resistor register

RDR0

R/W

Port 0

0 0 0 0 0 0 0 0

1C

H

Port 1 resistor register

RDR1

R/W

Port 1

0 0 0 0 0 0 0 0

1D

H

Port 2 resistor register

RDR2

R/W

Port 2

0 0 0 0 0 0 0 0

1E

H

Port 9 pin register

ODR9

R/W

Port 9

≠ 0 0 0 ≠ ≠ ≠ ≠

1F

H

Port A pin register

ODRA

R/W

Port A

≠ ≠ 0 0 0 0 0 0

20

H

Mode control register

UMC

R/W

UART

0 0 0 0 0 1 0 0

21

H

Status register

USR

R/W

0 0 0 1 0 0 0 0

22

H

Serial input register

/Serial output register

UIDR

/UODR

R/W

X X X X X X X X

23

H

Rate and data register

URD

R/W

0 0 0 0 ≠ ≠ 0 0

24

H

Serial mode control status register

SMCS

R/W

Extended serial

I/O interface

≠ ≠ ≠ 0 0 0 0 0

25

H

0 0 0 0 0 0 1 0

21

MB90230 Series

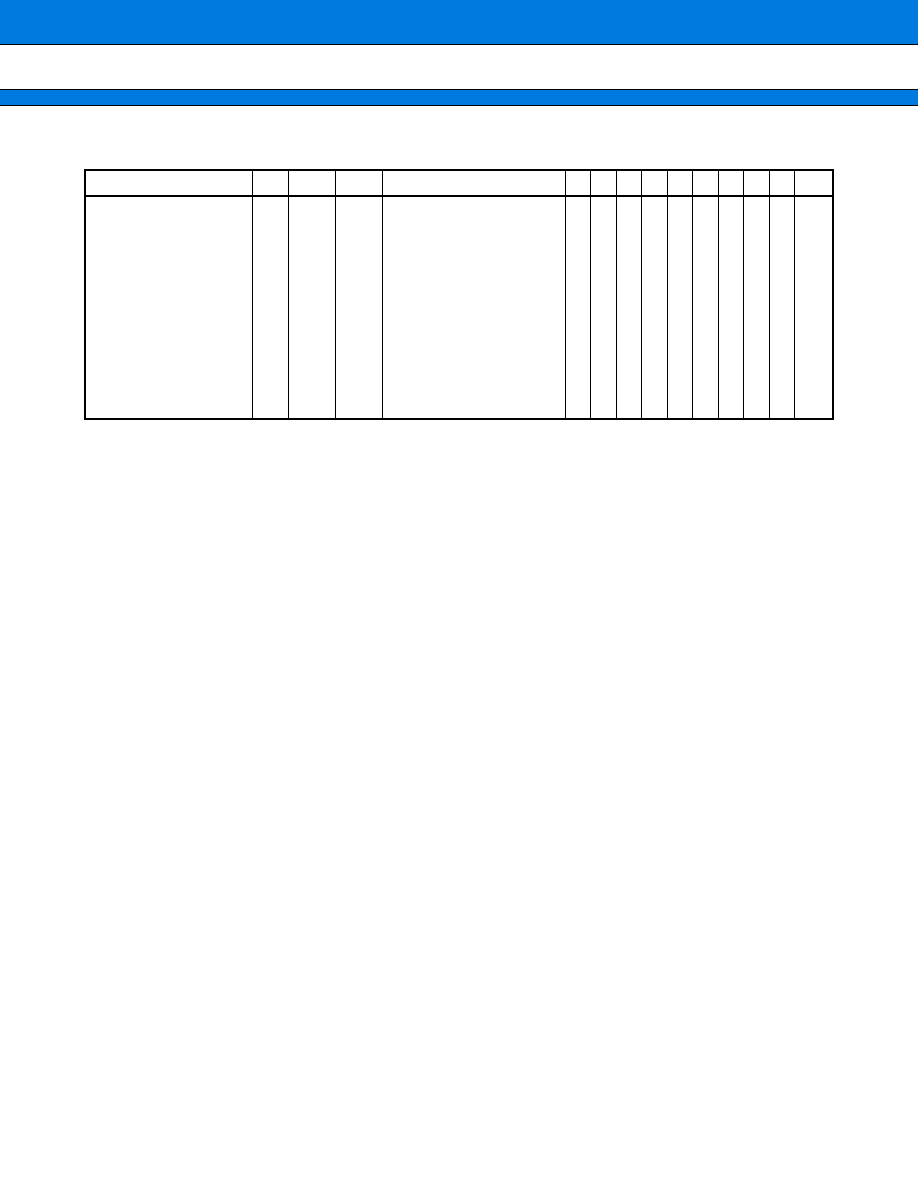

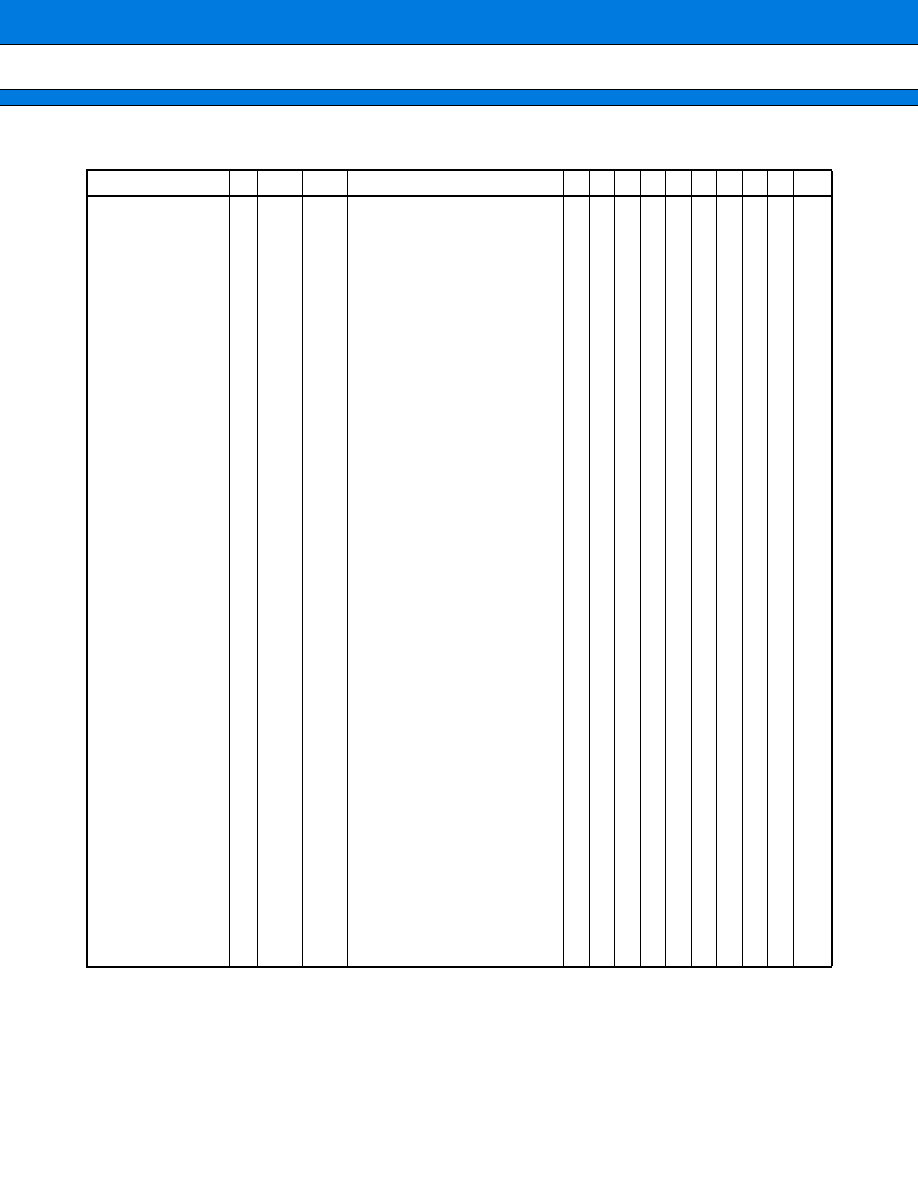

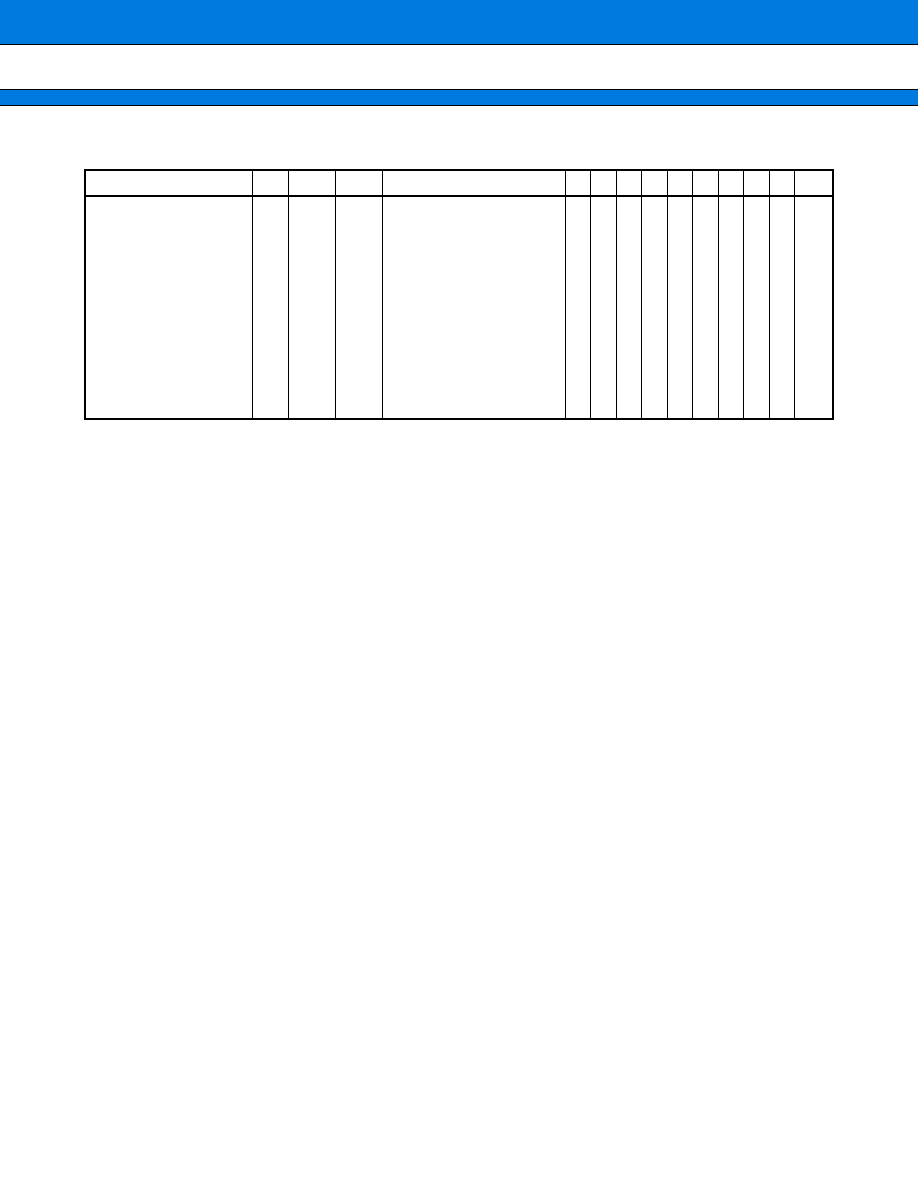

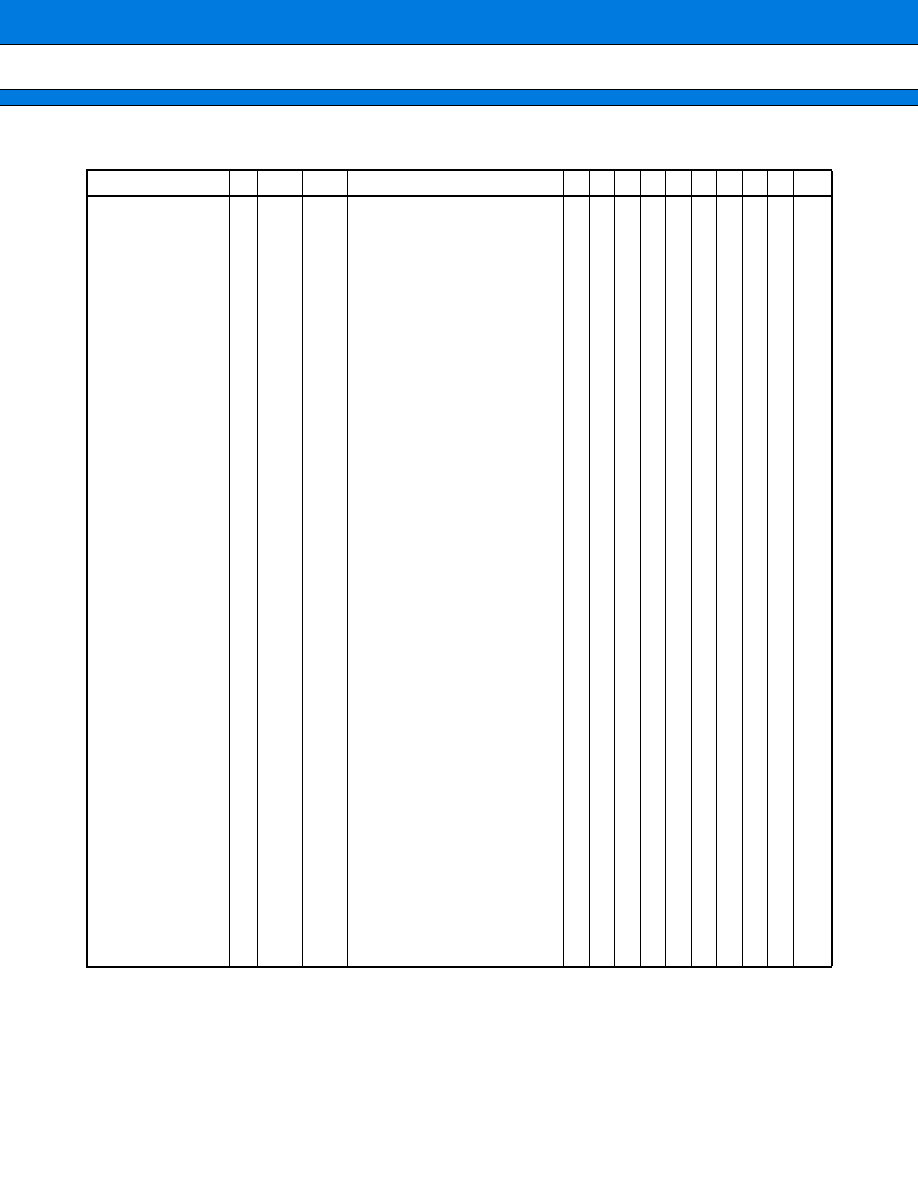

(Continued)

Address

Register

Register

name

Access

Resouce

name

Initial value

26

H

Serial data register

SDR

R/W

Extended serial

I/O interface

X X X X X X X X

27

H

Reserved area

--

--

--

--

28

H

Cycle setting register

PCSR

W

8-bit

PPG timer

X X X X X X X X

29

H

Duty factor setting register

PDUT

W

X X X X X X X X

2A

H

Control status register

PCNTL

R/W

0 0 0 0 0 0 0 0

2B

H

PCNTH

0 0 0 0 0 0 0 ≠

2C

H

Reserved area

--

--

--

--

2D

H

Communication prescaler

CDCR

R/W

UART, CKOT,

I/O, serial IF

0 ≠ ≠ ≠ 1 1 1 1

2E

H

Clock control register

CLKR

R/W

CKOT output

≠ ≠ ≠ ≠ ≠ 0 0 0

2F

H

Level comparator

LVLC

R/W

Level

comparator

X X X X 0 0 0 0

30

H

Interrupt/DTP enable register

ENIR

R/W

DTP/external

interrupt

≠ ≠ ≠ ≠ 0 0 0 0

31

H

Interrupt/DTP factor register

EIRR

R/W

≠ ≠ ≠ ≠ 0 0 0 0

32

H

Request level setting register

ELVR

R/W

0 0 0 0 0 0 0 0

33

H

Reserved area

--

--

--

--

34

H

Analog input enable register

ADER

R/W

10-bit A/D

converter

1 1 1 1 1 1 1 1

35

H

Reserved area

--

--

--

36

H

Control status data register

ADCS0

R/W

0 0 0 0 0 0 0 0

37

H

ADCS1

0 0 0 0 0 0 0 0

38

H

Data register

ADCR0

R

X X X X X X X X

39

H

ADCR1

0 0 0 0 0 0 X X

3A

H

Reserved area

--

--

--

--

3B

H

Reserved area

--

--

--

--

3C

H

D/A converter data register 0

DAT0

R/W

8-bit D/A

converter

X X X X X X X X

3D

H

D/A converter data register 1

DAT1

R/W

0 0 0 0 0 0 0 0

3E

H

D/A control register

DACR

R/W

≠ ≠ ≠ ≠ ≠ ≠ 0 0

3F

H

Reserved area

--

--

--

--

40

H

PWM data register 0

PWD0

R/W

8-bit

PWM0, 1

0 0 0 0 0 0 0 0

41

H

PWM data register 1

PWD1

R/W

0 0 0 0 0 0 0 0

42

H

Control status data register 0, 1

PWC01

R/W

0 0 0 0 0 0 0 0

43

H

Reserved area

--

--

--

--

44

H

PWM data register 2

PWD2

R/W

8-bit

PWM2, 3

0 0 0 0 0 0 0 0

45

H

PWM data register 3

PWD3

R/W

0 0 0 0 0 0 0 0

46

H

Control status register 2, 3

PWC23

R/W

0 0 0 0 0 0 0 0

MB90230 Series

22

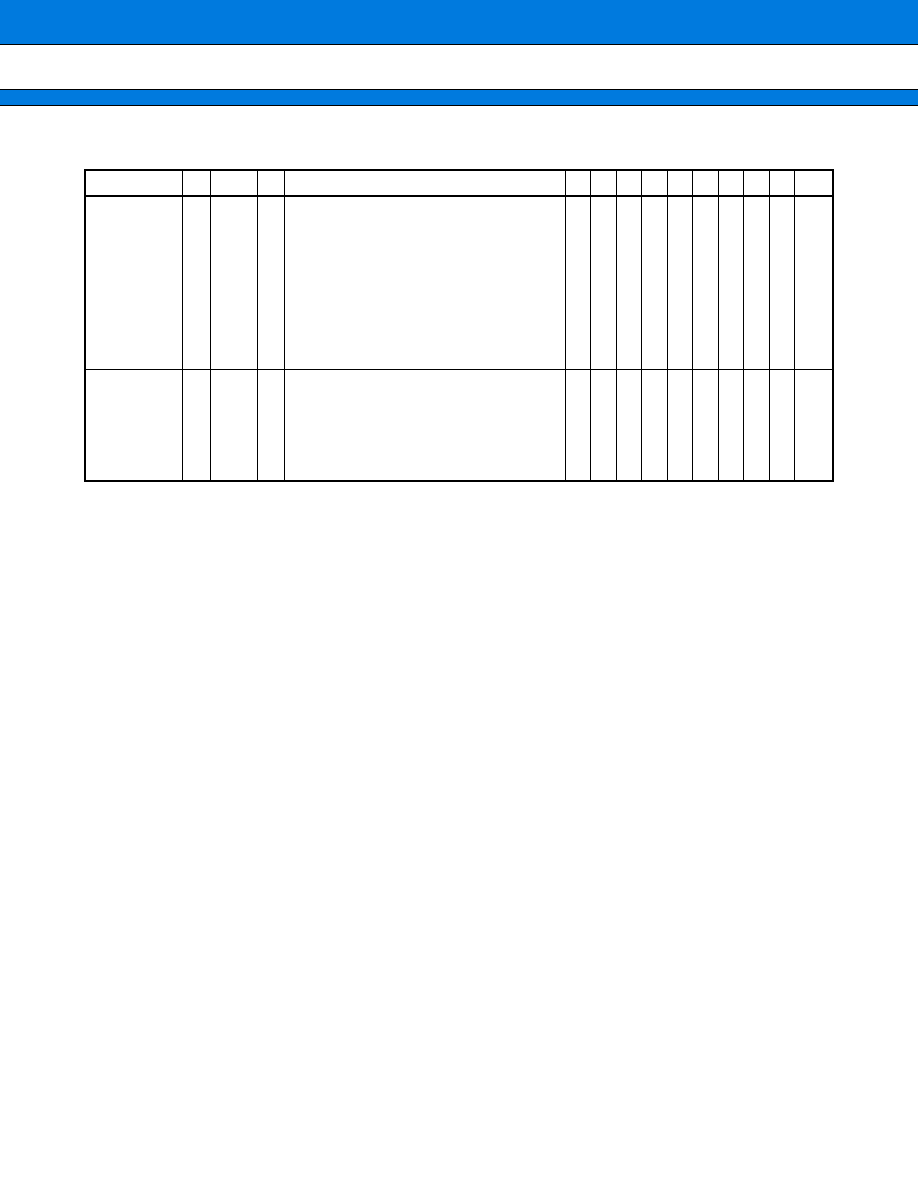

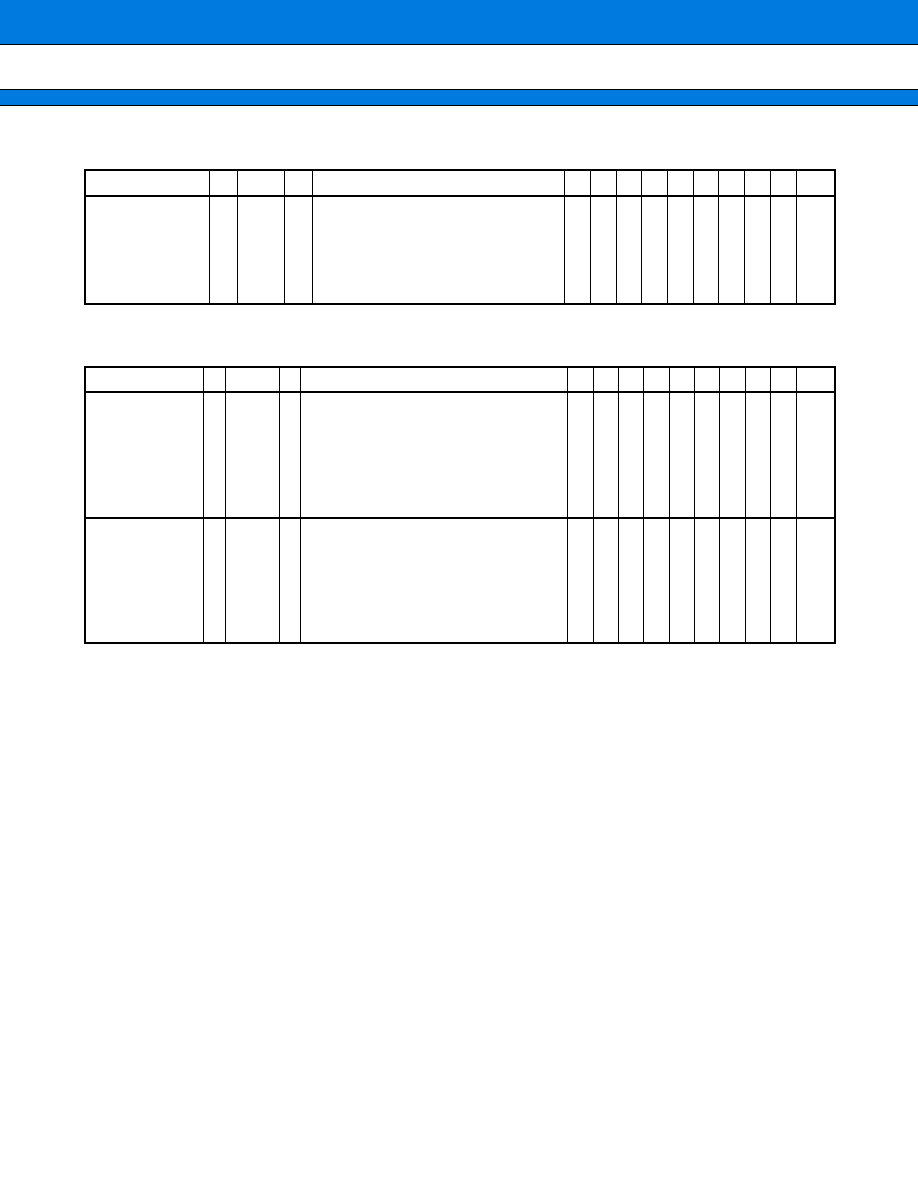

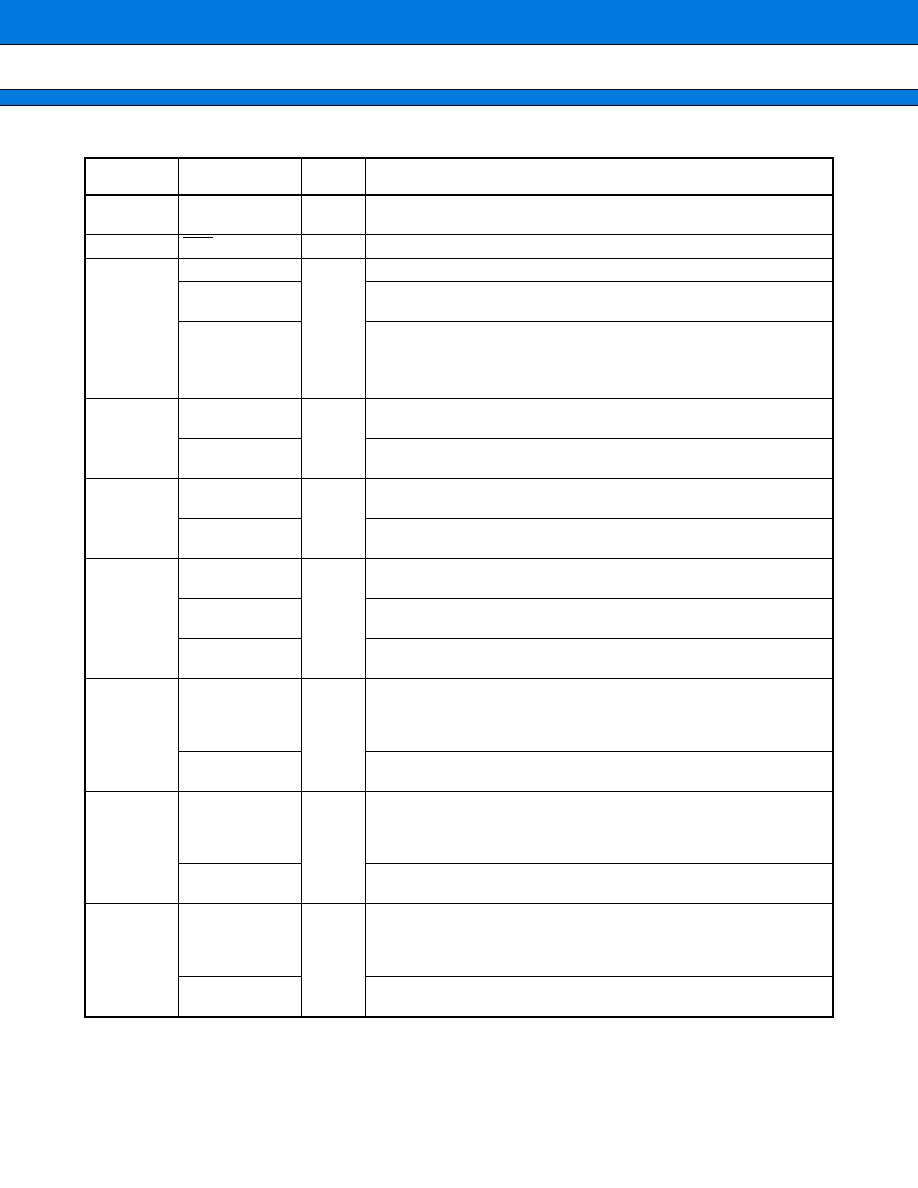

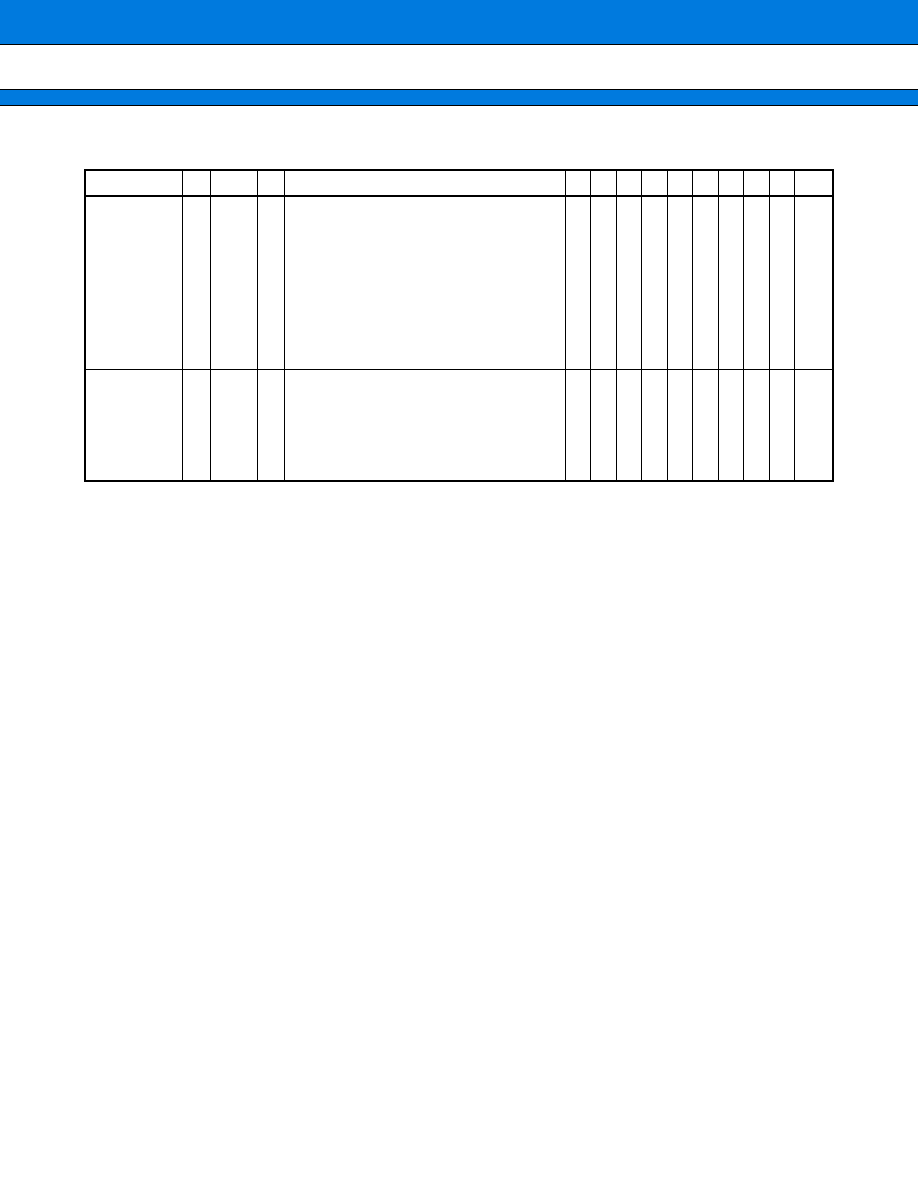

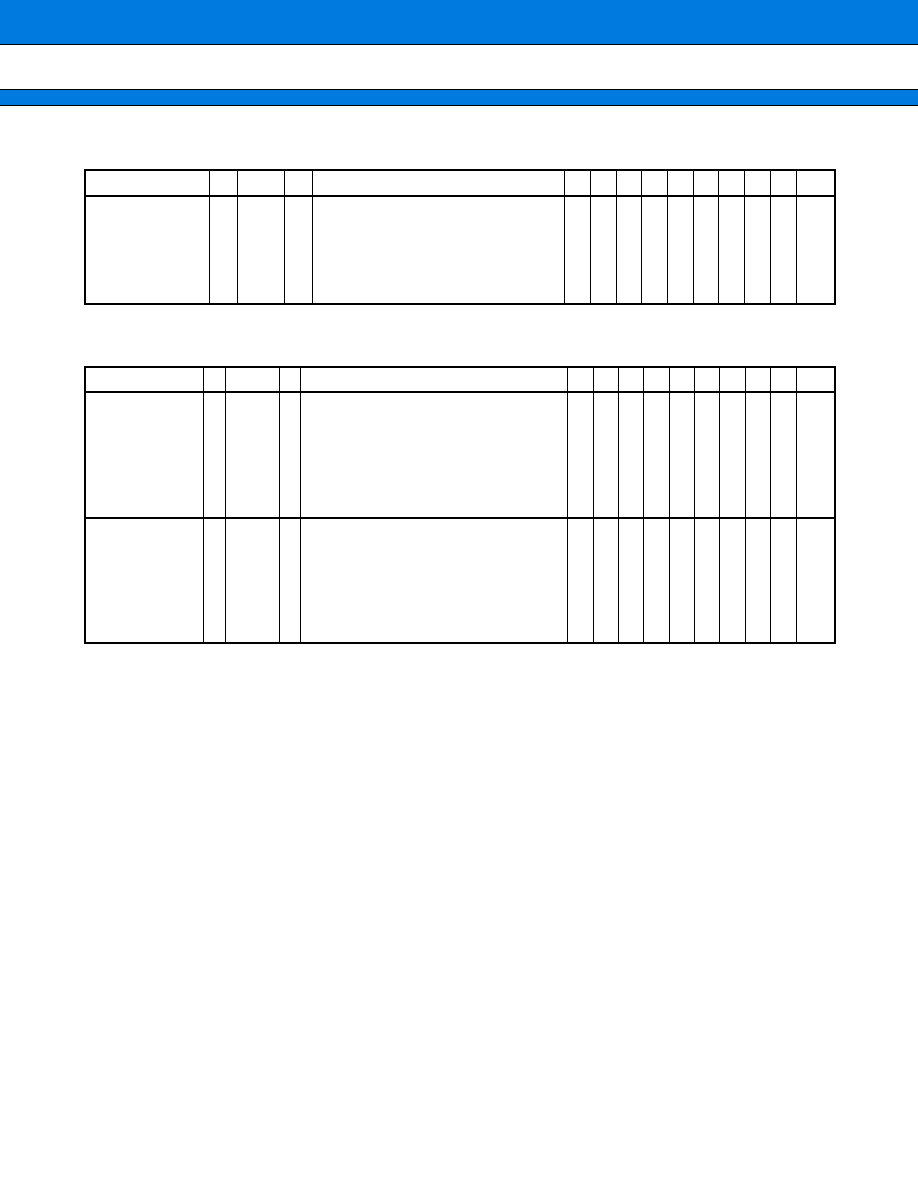

(Continued)

Address

Register

Register

name

Access

Resouce

name

Initial value

47

H

Reserved area

--

--

--

--

48

H

PWM data register 4

PWD4

R/W

8-bit

PWM4, 5

0 0 0 0 0 0 0 0

49

H

PWM data register 5

PWD5

R/W

0 0 0 0 0 0 0 0

4A

H

Control status register 4, 5

PWC45

R/W

0 0 0 0 0 0 0 0

4B

H

Reserved area

--

--

--

--

4C

H

Data register

TCDT

R

16-bit free

run timer

0 0 0 0 0 0 0 0

4D

H

0 0 0 0 0 0 0 0

4E

H

Control status register

TCCS

R/W

0 0 0 0 0 0 0 0

4F

H

Reserved area

--

--

--

--

50

H

Compare register 0

OCP0

R/W

Output

compare 0, 1

X X X X X X X X

51

H

X X X X X X X X

52

H

Compare register 1

OCP1

R/W

X X X X X X X X

53

H

X X X X X X X X

54

H

Control status register 0, 1

CS00

R/W

0 0 0 0 ≠ ≠ 0 0

55

H

CS01

≠ ≠ ≠ 0 0 0 0 0

56

H

Reserved area

--

--

--

--

57

H

Reserved area

--

--

--

--

58

H

Compare register 2

OCP2

R/W

Output

compare 2, 3

X X X X X X X X

59

H

X X X X X X X X

5A

H

Compare register 3

OCP3

R/W

X X X X X X X X

5B

H

X X X X X X X X

5C

H

Control status register 2, 3

CS10

R/W

0 0 0 0 ≠ ≠ 0 0

5D

H

CS11

≠ ≠ ≠ 0 0 0 0 0

5E

H

Reserved area

--

--

--

--

5F

H

Reserved area

--

--

--

--

60

H

Compare register 4

OCP4

R/W

Output

compare 4, 5

X X X X X X X X

61

H

X X X X X X X X

62

H

Compare register 5

OCP5

R/W

X X X X X X X X

63

H

X X X X X X X X

64

H

Control status register 4, 5

CS20

R/W

0 0 0 0 ≠ ≠ 0 0

65

H

CS21

≠ ≠ ≠ 0 0 0 0 0

66

H

Reserved area

--

--

--

--

67

H

to

6F

H

Reserved area

--

--

--

--

23

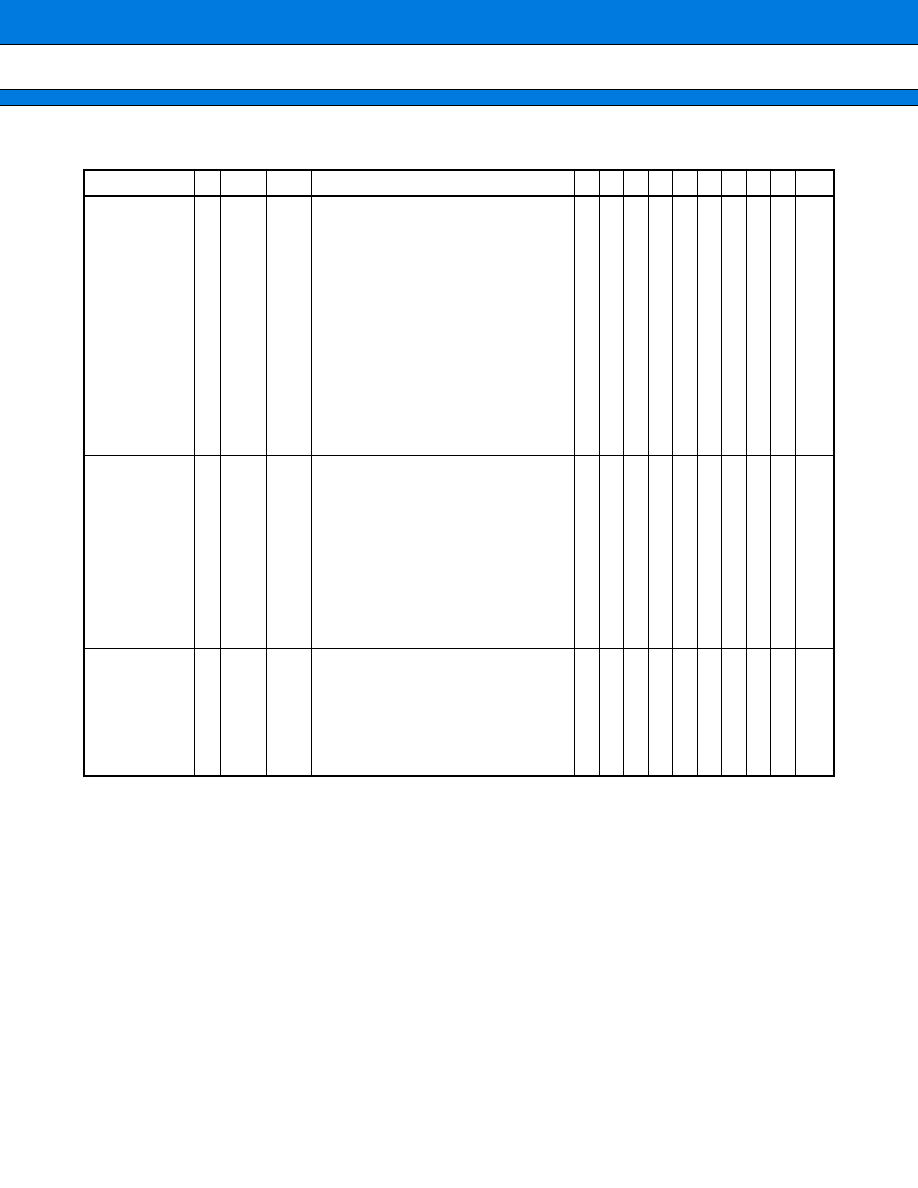

MB90230 Series

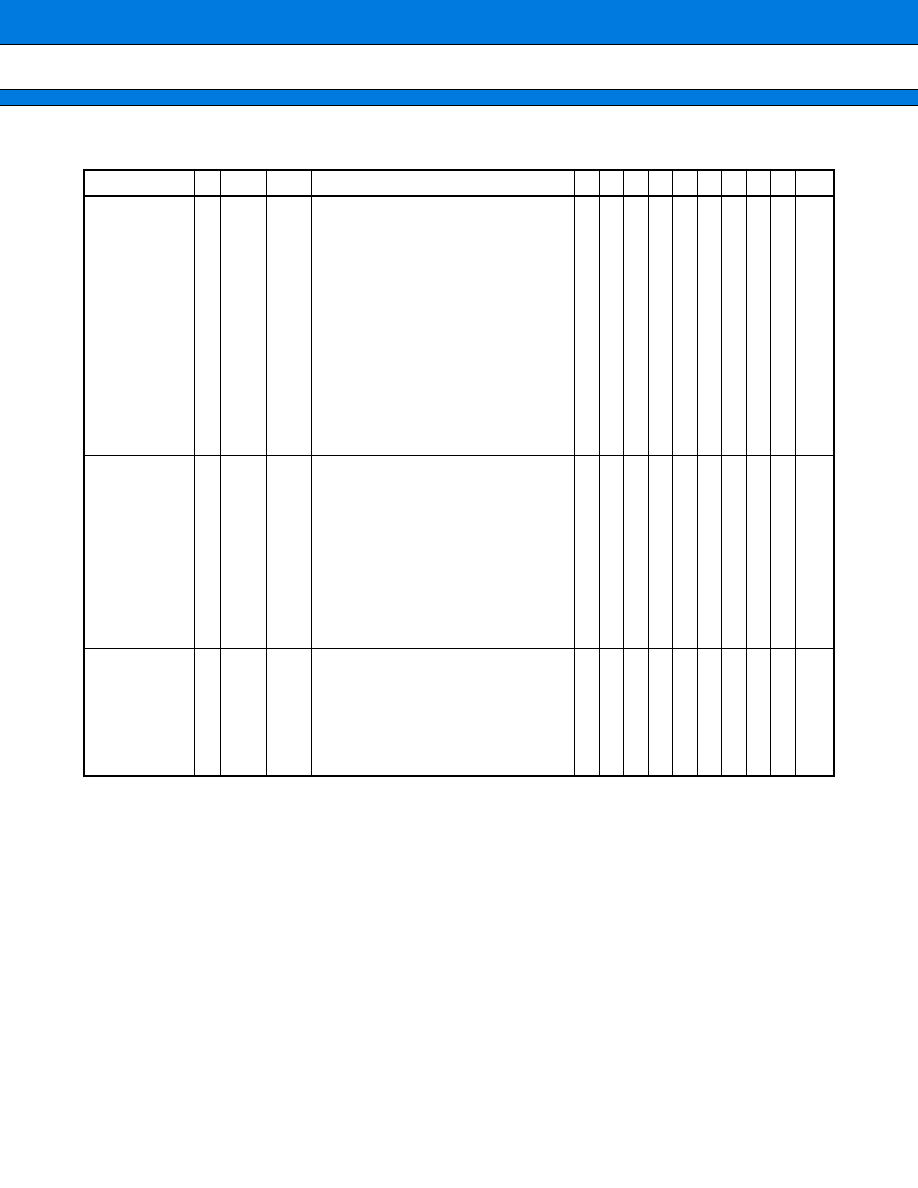

(Continued)

Address

Register

Register

name

Access

Resouce

name

Initial value

70

H

Capture register 0

ICP0

R/W

Input capture 0,

1

X X X X X X X X

71

H

X X X X X X X X

72

H

Capture register 1

ICP1

R/W

X X X X X X X X

73

H

X X X X X X X X

74

H

Control status register 0, 1

ICS0

R/W

0 0 0 0 0 0 0 0

75

H

to

77

H

Reserved area

--

--

--

--

78

H

Capture register 2

ICP2

R/W

Input capture 2,

3

X X X X X X X X

79

H

X X X X X X X X

7A

H

Capture register 3

ICP3

R/W

X X X X X X X X

7B

H

X X X X X X X X

7C

H

Control status register 2, 3

ICS1

R/W

0 0 0 0 0 0 0 0

7D

H

to

7F

H

Reserved area

--

--

--

--

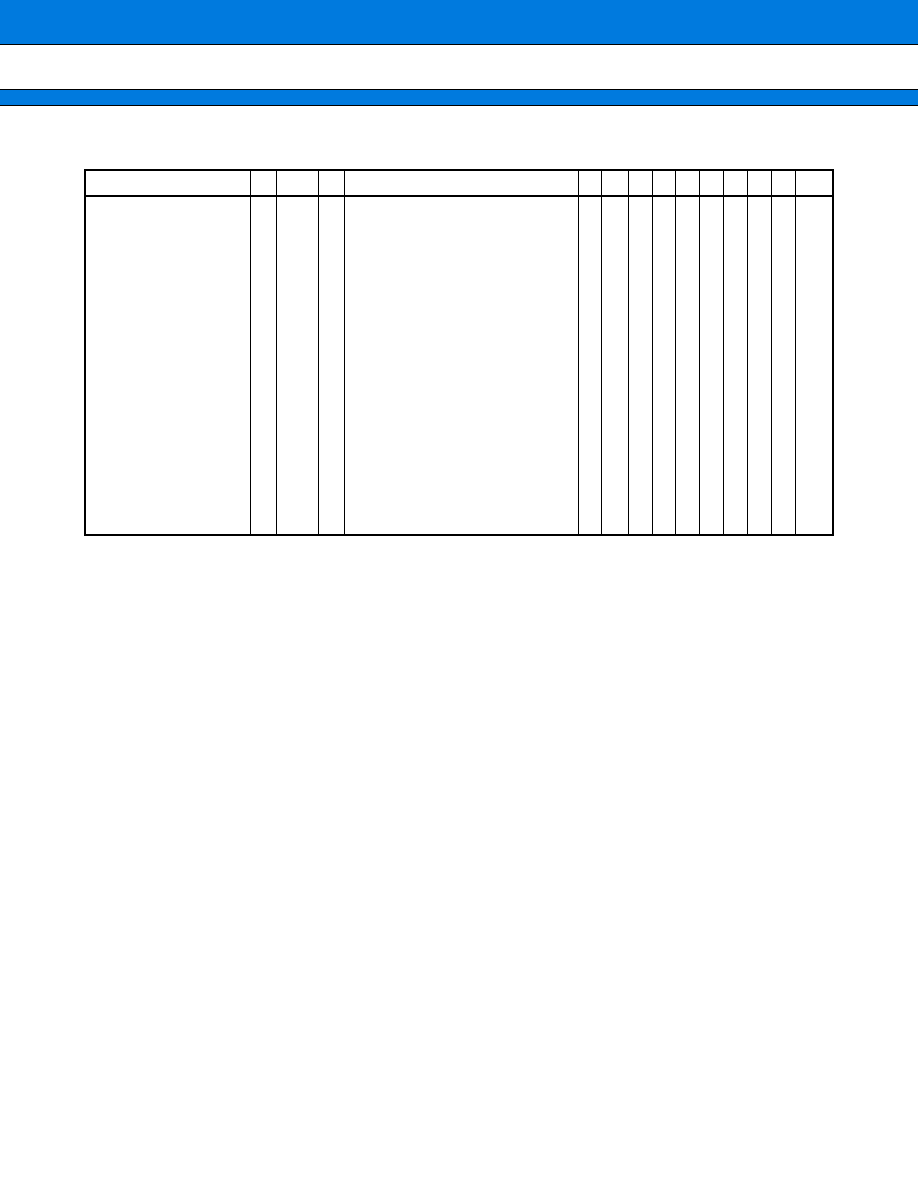

80

H

OP code register

EOPC

R/W

Serial E

2

PROM

interface

≠ ≠ ≠ ≠ 0 0 0 0

81

H

Format status register

ECTS

R/W

0 0 0 0 0 0 0 0

82

H

Data register

EDAT

R/W

X X X X X X X X

83

H

X X X X X X X X

84

H

Address register

EADR

R/W

0 0 0 0 0 0 0 0

85

H

0 0 ≠ ≠ ≠ 0 0 0

86

H

to

8F

H

Reserved area

--

--

--

--

90

H

to

9E

H

System reserved area

--

*1

--

--

9F

H

Delayed interrupt source generate/

release register

DIRR

R/W

Delayed interrupt

generation module

≠ ≠ ≠ ≠ ≠ ≠ ≠ 0

A0

H

Standby control register

STBYC

R/W

Low-power

consumption

mode

0 0 0 1 X X X X

A1

H

Reserved area

--

--

--

--

A2

H

Reserved area

--

--

--

--

A3

H

Middle address control register

MACR

W

External pin

*2

A4

H

Upper address control register

HACR

W

External pin

*2

A5

H

External pin control register

EPCR

W

External pin

*2

A6

H

Reserved area

--

--

--

--

A7

H

Reserved area

--

--

--

--

A8

H

Watchdog timer control register

TWC

R/W

Watchdog timer/

reset

X X X X X X X X

MB90230 Series

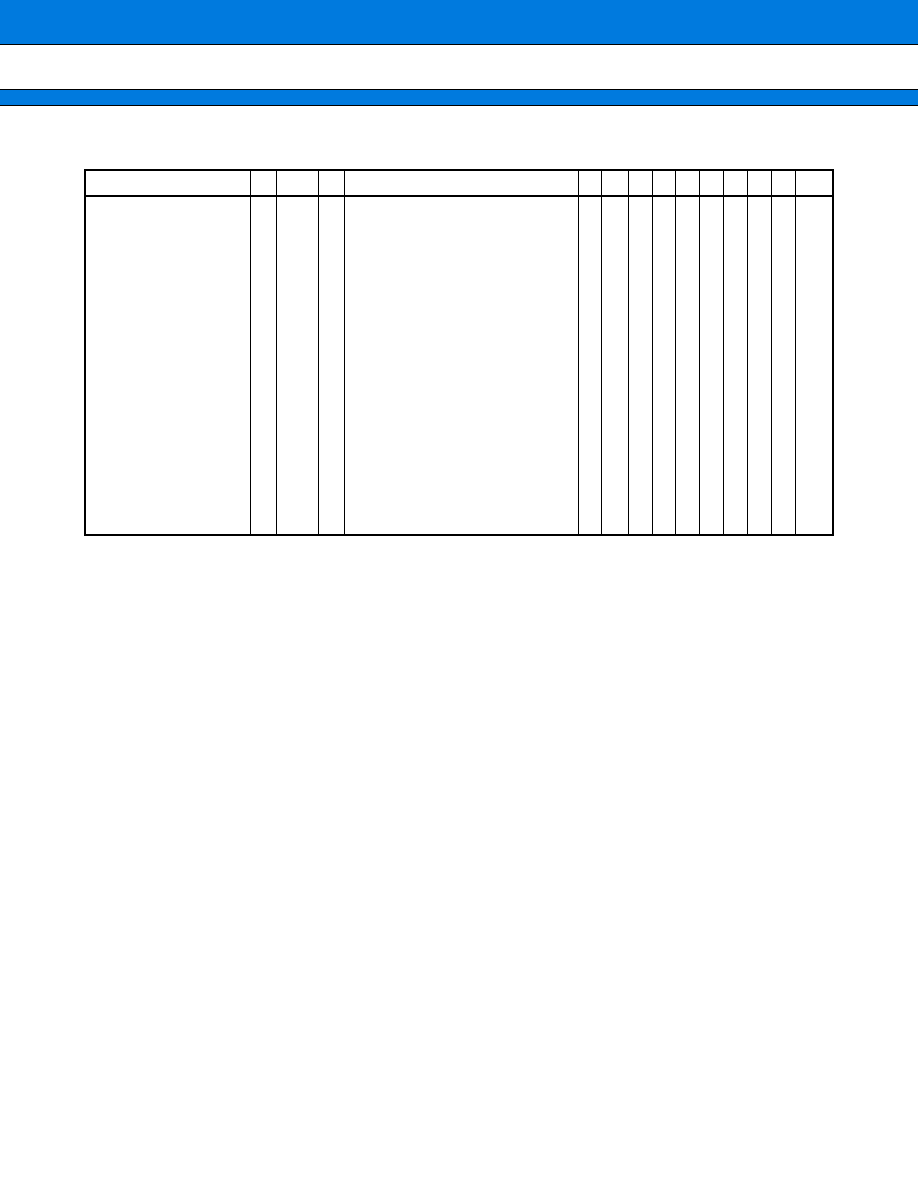

24

Initial values

0: The initial value for the bit is "0."

1: The initial value for the bit is "1."

X: The initial value for the bit is undefined.

≠: The bit is not used; the initial value is undefined.

*1: Access inhibited

*2: The initial value depends on each bus mode.

*3: Only this area can be used as the external access area in the area that follows address 0000FF

H

. Access to

any address in reserved areas specified in the I/O map table is handled as access to an internal area. An

access signal to the external bus is not generated.

Address

Register

Register

name

Access

Resouce

name

Initial value

A9

H

Timebase timer control register

TBTC

R/W

Timebase

timer

≠ ≠ ≠ 0 0 0 0 0

AA

H

to

AF

H

Reserved area

--

--

--

--

B0

H

Interrupt control register 00

ICR00

R/W

Interrupt

controller

0 0 0 0 0 1 1 1

B1

H

Interrupt control register 01

ICR01

R/W

0 0 0 0 0 1 1 1

B2

H

Interrupt control register 02

ICR02

R/W

0 0 0 0 0 1 1 1

B3

H

Interrupt control register 03

ICR03

R/W

0 0 0 0 0 1 1 1

B4

H

Interrupt control register 04

ICR04

R/W

0 0 0 0 0 1 1 1

B5

H

Interrupt control register 05

ICR05

R/W

0 0 0 0 0 1 1 1

B6

H

Interrupt control register 06

ICR06

R/W

0 0 0 0 0 1 1 1

B7

H

Interrupt control register 07

ICR07

R/W

0 0 0 0 0 1 1 1

B8

H

Interrupt control register 08

ICR08

R/W

0 0 0 0 0 1 1 1

B9

H

Interrupt control register 09

ICR09

R/W

0 0 0 0 0 1 1 1

BA

H

Interrupt control register 10

ICR10

R/W

0 0 0 0 0 1 1 1

BB

H

Interrupt control register 11

ICR11

R/W

0 0 0 0 0 1 1 1

BC

H

Interrupt control register 12

ICR12

R/W

0 0 0 0 0 1 1 1

BD

H

Interrupt control register 13

ICR13

R/W

0 0 0 0 0 1 1 1

BE

H

Interrupt control register 14

ICR14

R/W

0 0 0 0 0 1 1 1

BF

H

Interrupt control register 15

ICR15

R/W

0 0 0 0 0 1 1 1

C0

H

to

FF

H

External area

--

--

--

*3

25

MB90230 Series

s

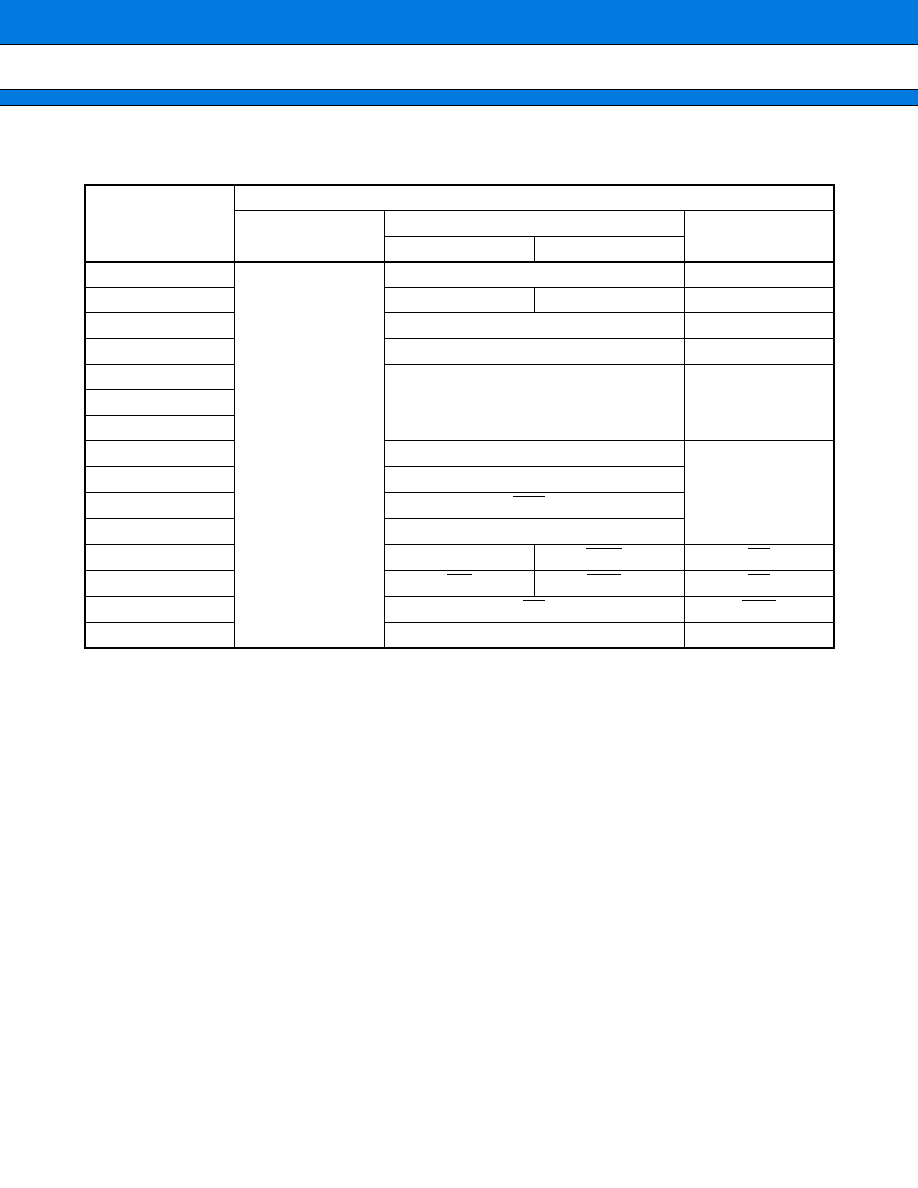

INTERRUPT VECTORS AND INTERRUPT CONTROL REGISTERS FOR INTERRUPT

SOURCES

: The request flag is cleared by the EI

2

OS interrupt clear signal.

: The request flag is cleared by the EI

2

OS interrupt clear signal. The stop request is available.

: The request flag is not cleared by the EI

2

OS interrupt clear signal.

Interrupt source

I

2

OS

support

Interrupt vector

Interrupt control

register

No.

Address

ICR

Address

Reset

◊

#08

08

H

FFFFDC

H

--

--

INT9 instruction

◊

#09

09

H

FFFFD8

H

--

--

Exceptional

◊

#10

0A

H

FFFFD4

H

--

--

External interrupt (INT0) 0 ch

#11

0B

H

FFFFD0

H

ICR00

0000B0

H

External interrupt (INT1) 1 ch

#12

0C

H

FFFFCC

H

External interrupt (INT2) 2 ch

#13

0D

H

FFFFC8

H

ICR01

0000B1

H

External interrupt (INT3) 3 ch

#14

0E

H

FFFFC4

H

Extended serial I/O interface

#15

0F

H

FFFFC0

H

ICR02

0000B2

H

Serial E

2

PROM interface

#17

11

H

FFFFB8

H

ICR03

0000B3

H

Input capture channel 0

#19

13

H

FFFFB0

H

ICR04

0000B4

H

Input capture channel 1

#21

15

H

FFFFA8

H

ICR05

0000B5

H

Input capture channel 2

#23

17

H

FFFFA0

H

ICR06

0000B6

H

Input capture channel 3

#24

18

H

FFFF9C

H

Output compare channel 0

#25

19

H

FFFF98

H

ICR07

0000B7

H

Output compare channel 1

#26

1A

H

FFFF94

H

Output compare channel 2

#27

1B

H

FFFF90

H

ICR08

0000B8

H

Output compare channel 3

#28

1C

H

FFFF8C

H

Output compare channel 4

#29

1D

H

FFFF88

H

ICR09

0000B9

H

Output compare channel 5

#30

1E

H

FFFF84

H

16-bit free run timer overflow

#31

1F

H

FFFF80

H

ICR10

0000BA

H

Timebase timer overflow

#32

20

H

FFFF7C

H

8-bit PPG timer

#33

21

H

FFFF78

H

ICR11

0000BB

H

Level comparator

#34

22

H

FFFF74

H

UART reception

#35

23

H

FFFF70

H

ICR12

0000BC

H

UART transmission

#37

25

H

FFFF68

H

ICR13

0000BD

H

End of A/D conversion

#39

27

H

FFFF60

H

ICR14

0000BE

H

Delayed interrupt

◊

#42

2A

H

FFFF54

H

ICR15

0000BF

H

Stack fault

◊

#256

FF

H

FFFC00

H

--

--

MB90230 Series

26

s

PERIPHERAL RESOURCES

1. I/O Ports

Each pin in each port can be specified for input or output by setting the direction register when the corresponding

peripheral resource is not set to use that pin. When the data register is read, the value depending on the pin

level is read whenever the pin serves for input. When the data register is read with the pin serving for output,

the latch value of the data register is read. This also applies to read operation by the read modify write instruction.

Data register

Direction register

Data register read

Data register write

Direction register write

Direction register read

Pin

Internal data bus

Data register

Direction register read

Port input/output

Pull-up resistor (Approx. 50 k

)

Internal data bus

Resistor register

∑ General-purpose I/O port

∑ Port with pull-up resistor setting register

27

MB90230 Series

Data register

Direction register

Port input/output

Pin register

Internal data bus

∑ Port with open-drain setting register

MB90230 Series

28

(1) Register Configuration

15/7

14/6

13/5

12/4

11/3

10/2

9/1

8/0

Address: 000000

H

Address: 000001

H

Address: 000002

H

Address: 000003

H

Address: 000004

H

Address: 000005

H

Address: 000006

H

Address: 000007

H

Address: 000008

H

Address: 000009

H

Address: 00000A

H

bit

P06

P05

P04

P03

P02

P01

P00

P07

P16

P15

P14

P13

P12

P11

P10

P17

P26

P25

P24

P23

P22

P21

P20

P27

P36

P35

P34

P33

P32

P31

P30

P37

P46

P45

P44

P43

P42

P41

P40

P47

P56

P55

P54

P53

P52

P51

P50

P57

P66

P65

P64

P63

P62

P61

P60

P67

P76

P75

P74

P73

P72

P71

P70

--

P86

P85

P84

P83

P82

P81

P80

P87

P96

P95

P94

P93

P92

P91

P90

--

--

PA5

PA4

PA3

PA2

PA1

PA0

--

Port 0 data register (PDR0)

Port 1 data register (PDR1)

Port 2 data register (PDR2)

Port 3 data register (PDR3)

Port 4 data register (PDR4)

Port 5 data register (PDR5)

Port 6 data register (PDR6)

Port 7 data register (PDR7)

Port 8 data register (PDR8)

Port 9 data register (PDR9)

Port A data register (PDRA)

15/7

14/6

13/5

12/4

11/3

10/2

9/1

8/0

Address: 000010

H

Address: 000011

H

Address: 000012

H

Address: 000013

H

Address: 000014

H

Address: 000015

H

Address: 000016

H

Address: 000017

H

Address: 000018

H

Address: 000019

H

Address: 00001A

H

bit

P06

P05

P04

P03

P02

P01

P00

P07

P16

P15

P14

P13

P12

P11

P10

P17

P26

P25

P24

P23

P22

P21

P20

P27

P36

P35

P34

P33

P32

P31

P30

P37

P46

P45

P44

P43

P42

P41

P40

P47

P56

P55

P54

P53

P52

P51

P50

P57

P66

P65

P64

P63

P62

P61

P60

P67

P76

P75

P74

P73

P72

P71

P70

--

P86

P85

P84

P83

P82

P81

P80

P87

P96

P95

P94

P93

P92

P91

P90

--

--

PA5

PA4

PA3

PA2

PA1

PA0

--

Port 0 direction register (DDR0)

Port 1 direction register (DDR1)

Port 2 direction register (DDR2)

Port 3 direction register (DDR3)

Port 4 direction register (DDR4)

Port 5 direction register (DDR5)

Port 6 direction register (DDR6)

Port 7 direction register (DDR7)

Port 8 direction register (DDR8)

Port 9 direction register (DDR9)

Port A direction register (DDRA)

15

14

13

12

11

10

9

8

Address: 000034

H

bit

ADE6 ADE5 ADE4 ADE3 ADE2 ADE1 ADE0

ADE7

Analog input enable register (ADER)

15/7

14/6

13/5

12/4

11/3

10/2

9/1

8/0

Address: 00001B

H

Address: 00001C

H

Address: 00001D

H

bit

P06

P05

P04

P03

P02

P01

P00

P07

P16

P15

P14

P13

P12

P11

P10

P17

P26

P25

P24

P23

P22

P21

P20

P27

Port 0 resistor register (RDR0)

Port 1 resistor register (RDR1)

Port 2 resistor register (RDR2)

15/7

14/6

13/5

12/4

11/3

10/2

9/1

8/0

Address: 00001E

H

Address: 00001F

H

bit

P96

P95

P94

--

--

--

--

--

--

PA5

PA4

PA3

PA2

PA1

PA0

--

Port 9 pin register (ODR9)

Port A pin register (ODRA)

29

MB90230 Series

Ports 0 to 5 in the MB90230 series share the external bus and pins. Each pin function is selected depending on

the bus mode and register settings.

*1: The pin can be used as an I/O port by setting the upper and middle address control registers.

*2: The pin can be used as an I/O port by setting the external pin control register.

Pin name

Function

Single-chip mode

External bus extended mode

EPROM write

8 bits

16 bits

P07 to P00

Port

D07 to D00

D07 to D00

P17 to P10

Port

D15 to D08

D15 to D08

P27 to P20

A07 to A00

A07 to A00

P37 to P30

A15 to A08*

1

A15 to A08

P47 to P45

A23 to A16*

1

A23 to A16

P44

P43 to P40

P50

CLK*

2

Not used

P51

RDY*

2

P52

HAK*

2

P53

HRQ*

2

P54

Port

WRH*

2

CE

P55

WR

WRL*

2

OE

P56

RD

PGM

P57

Port

"0"

MB90230 Series

30

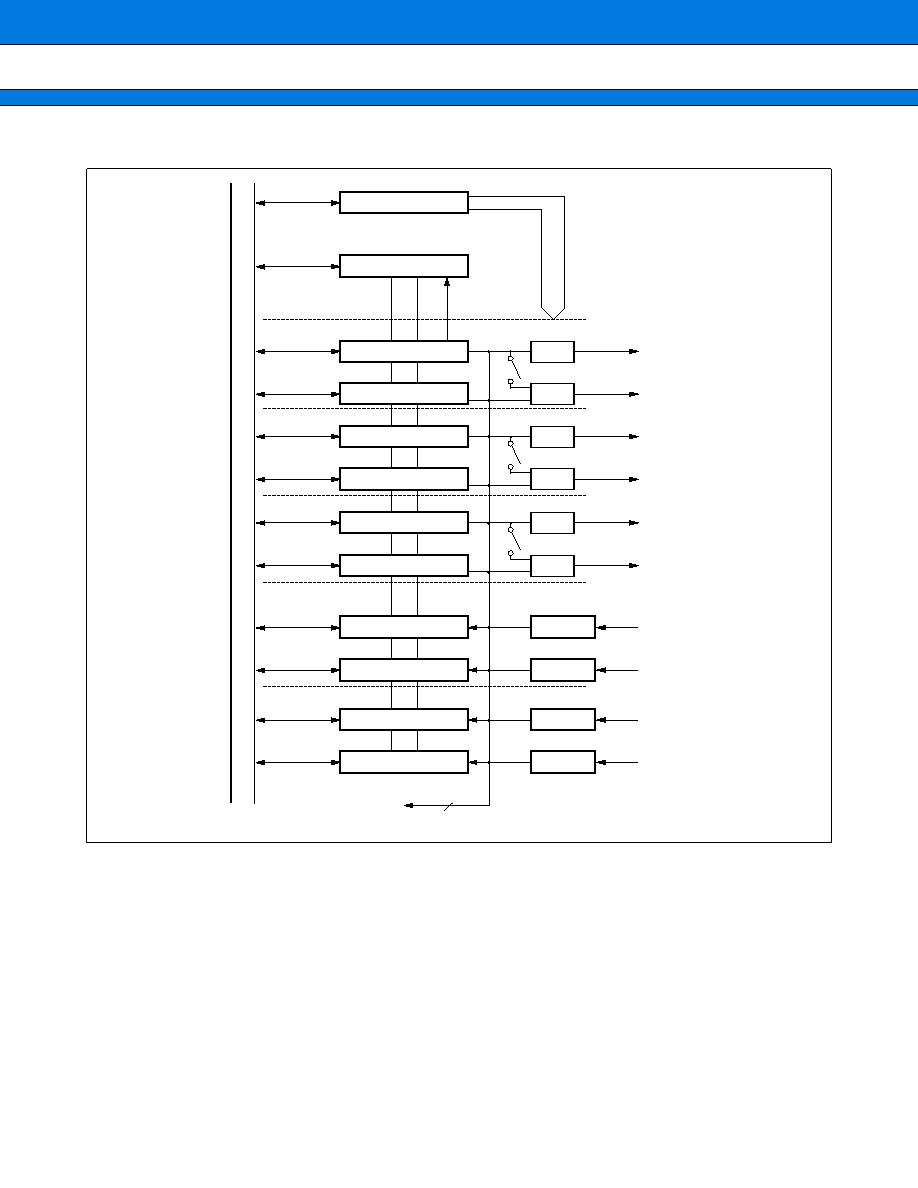

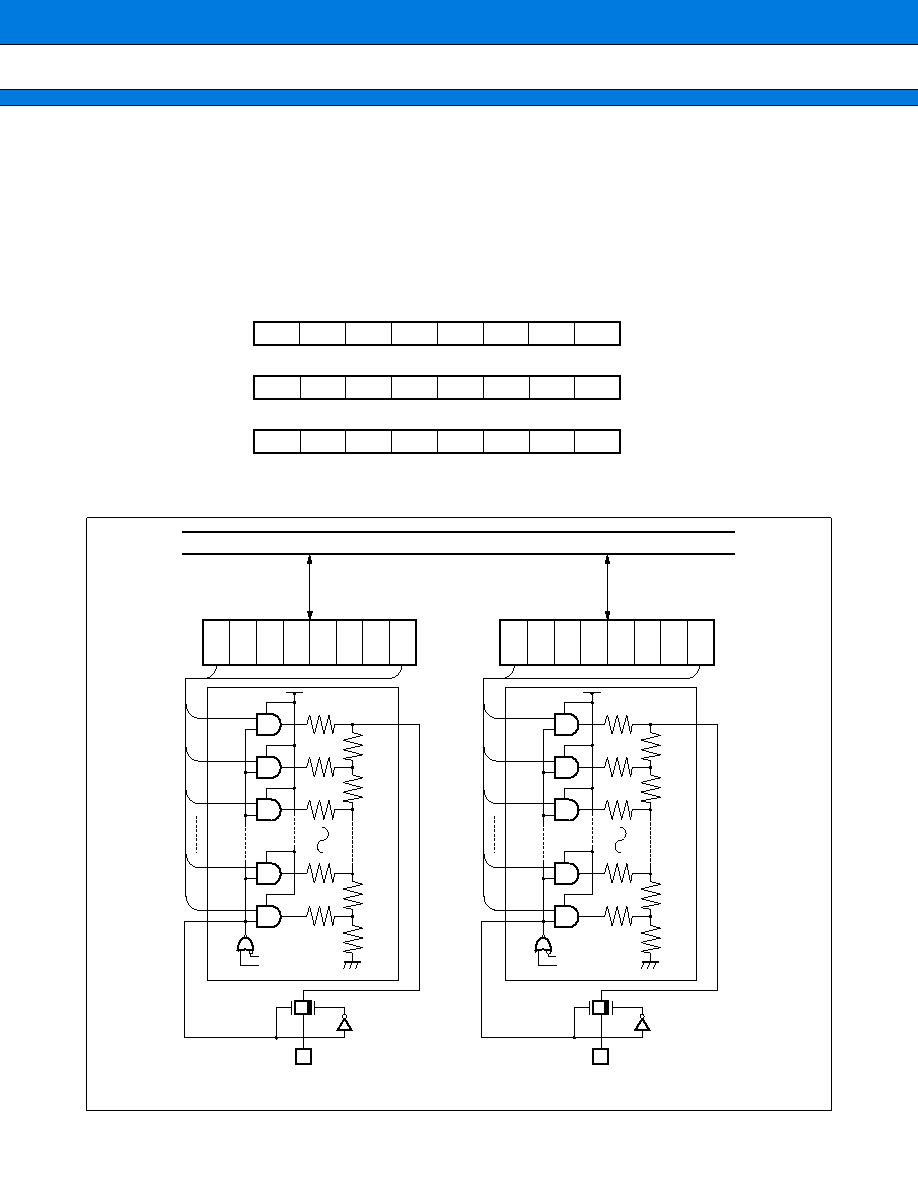

2. 8-bit PWM (with 6 channels in this series)

The PWM module consists of a pair of 8-bit PWM output circuits. The MB90230 series incorporates a set of

three PWM modules. They can output a waveform continuously from the port at an arbitrary duty factor according

to the register settings.

∑ 8-bit down counter

∑ 8-bit data registers

∑ Compare circuit

∑ Control registers

(1) Register Configuration

(2) Block Diagram

000041, 40

H

000045, 44

H

000049, 48

H

15

PWDx

PWDx

8 7

0

PWCxx

7

0

PWM data registers 0 to 5

Control registers 0 to 5

000042

H

000046

H

00004A

H

bit

8-bit down counter

Comparator, PWM output section

8-bit data registers

Control registers

Bus

PWM output

31

MB90230 Series

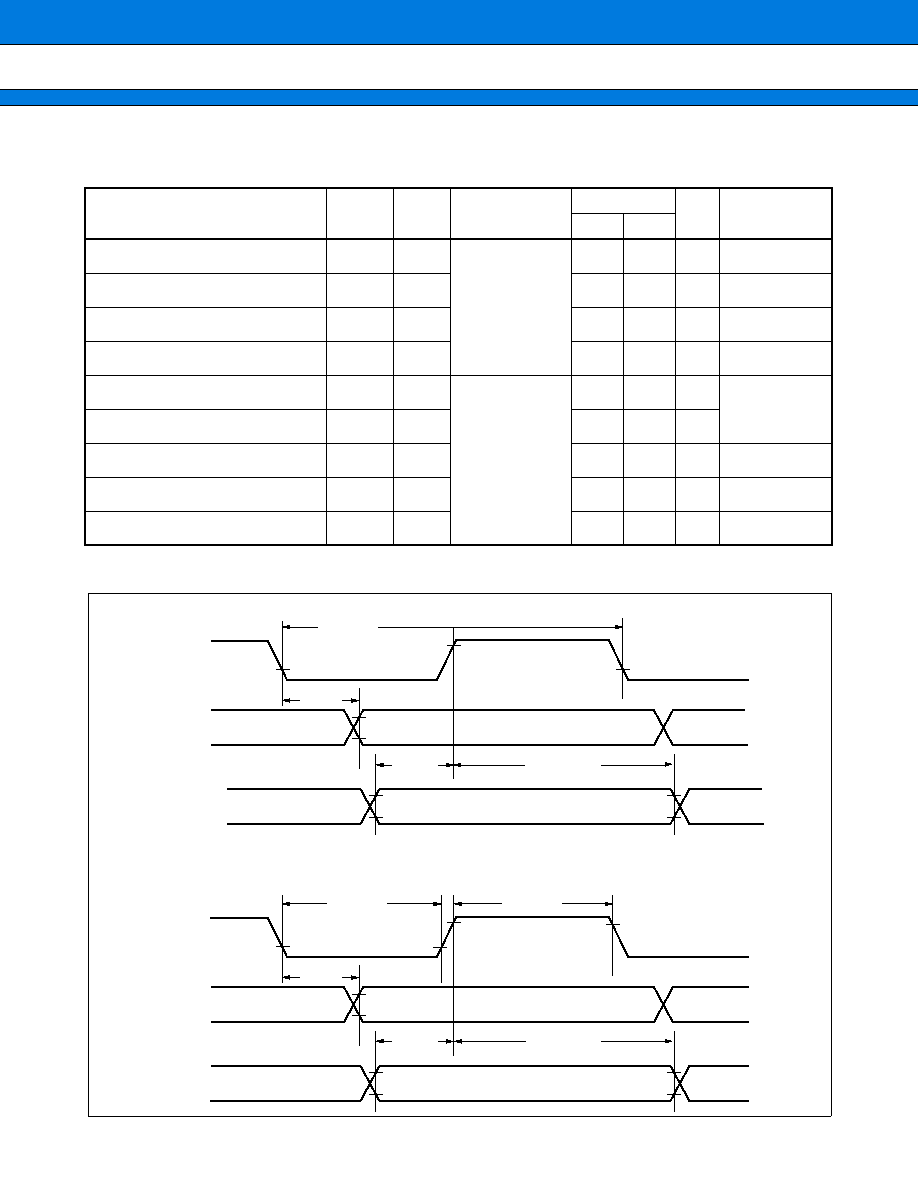

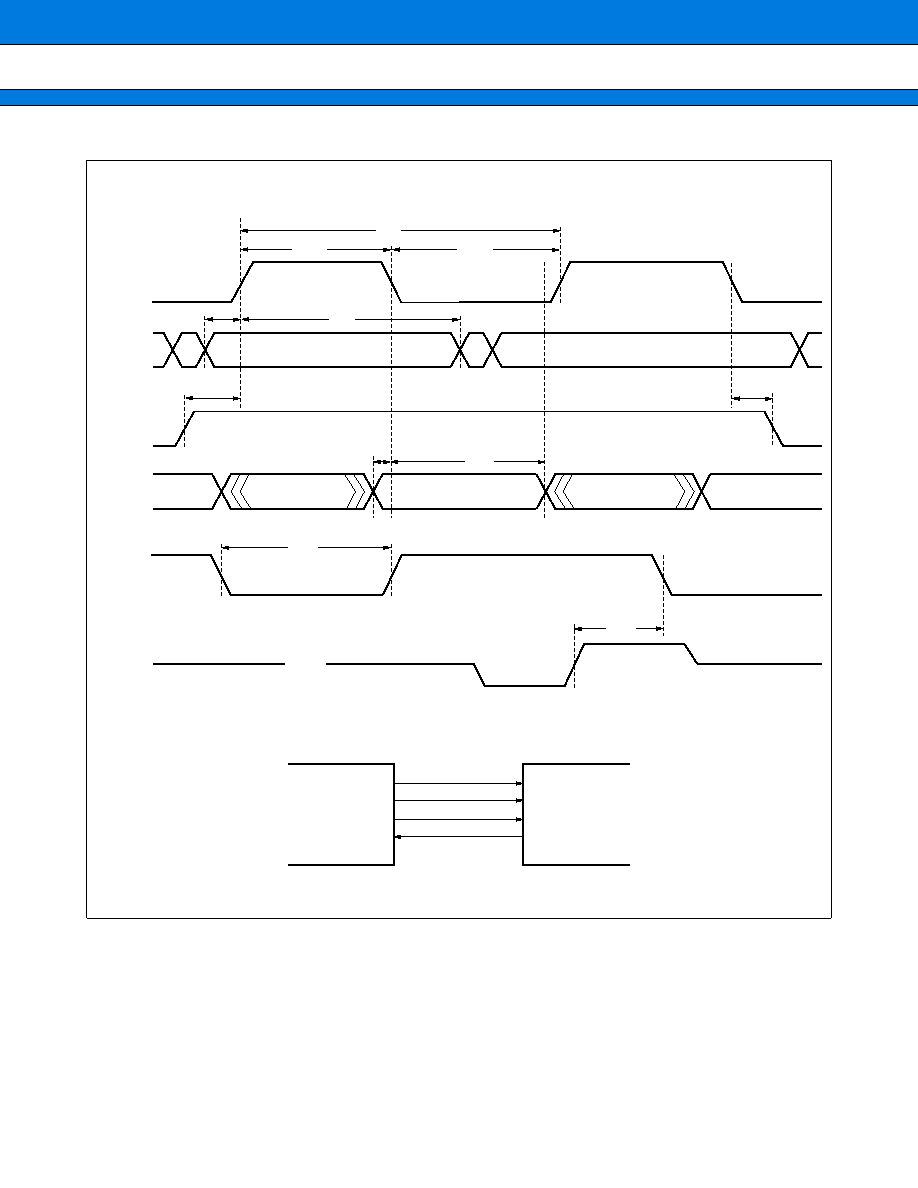

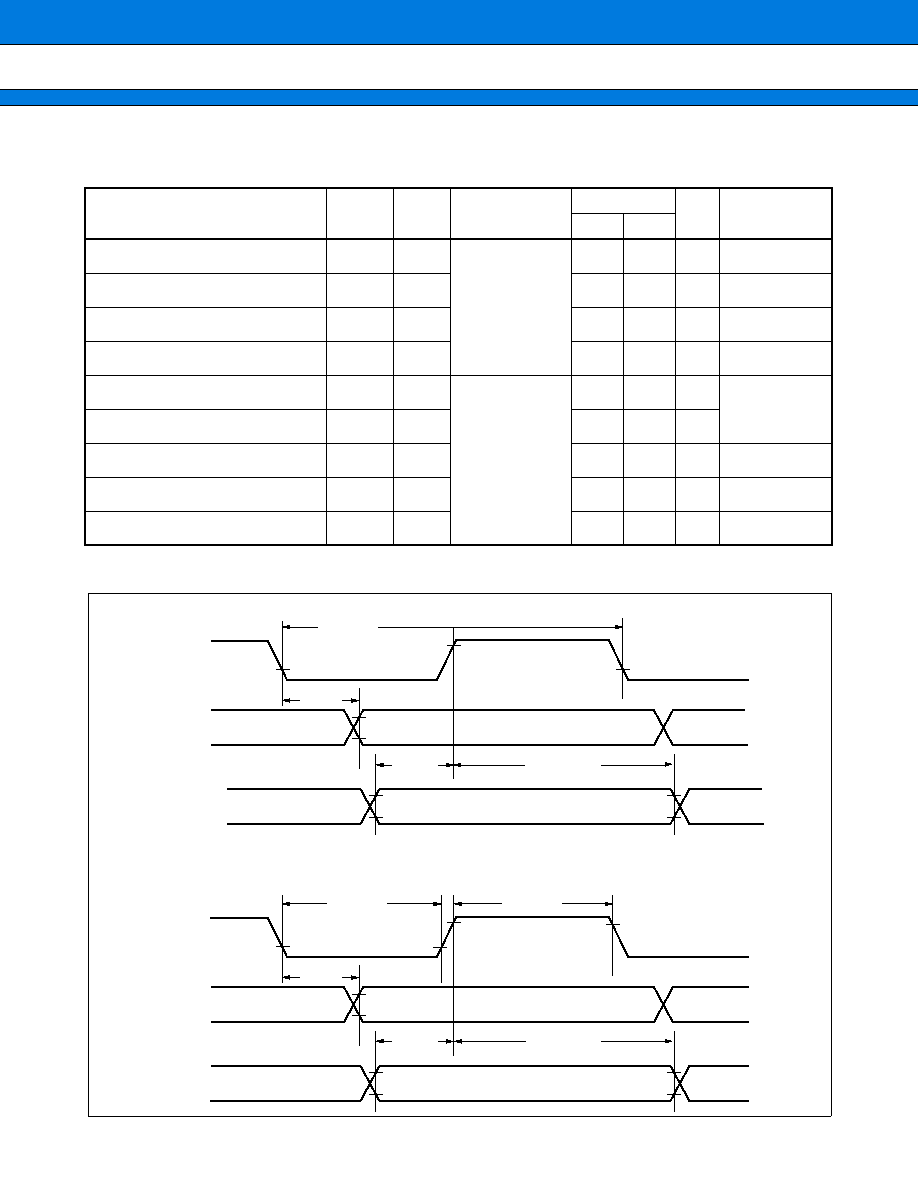

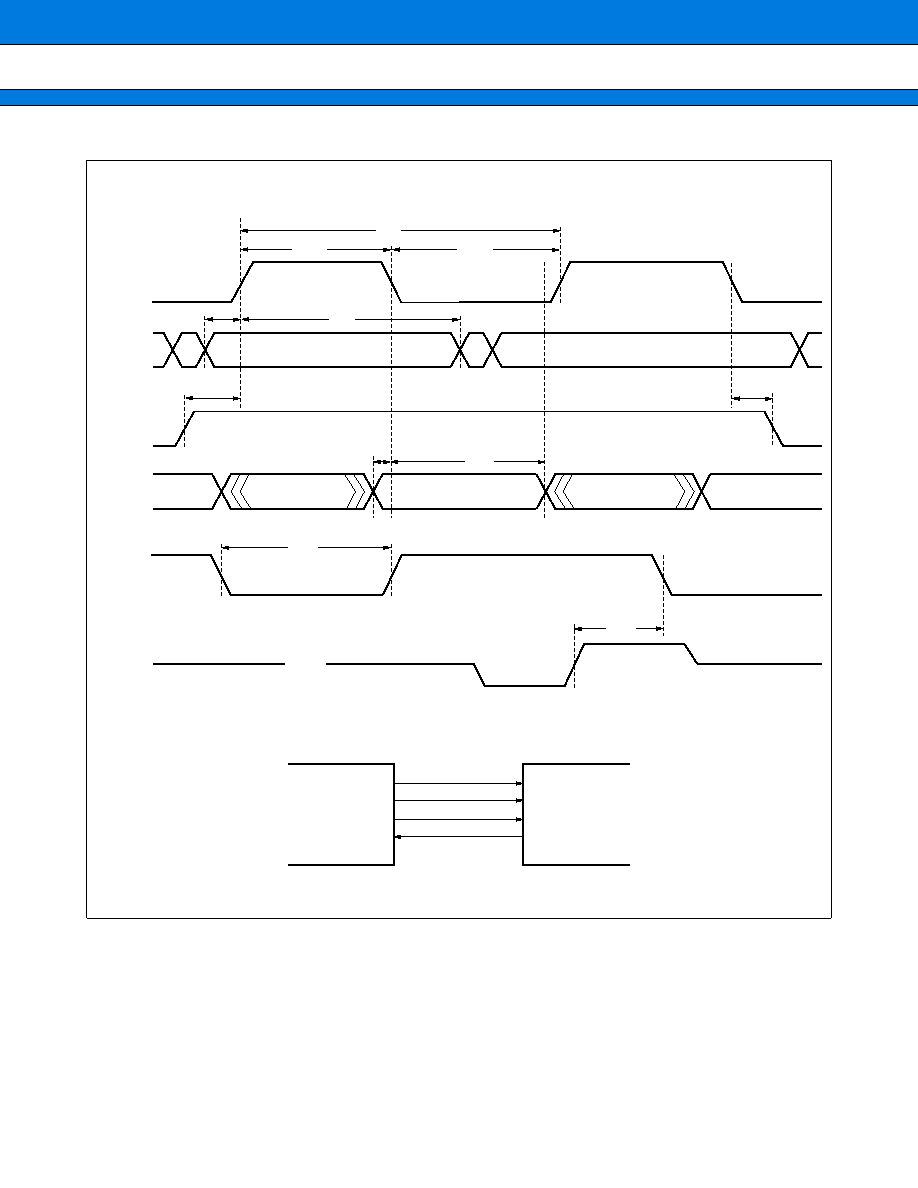

3. UART

The UART is a serial I/O port for synchronous or asynchronous communication with external resources. It has

the following features:

∑ Full-duplex double buffering

∑ Data transfer synchronous or asynchronous with clock pulses

∑ Multiprocessor mode support (Mode 2)

∑ Internal dedicated baud-rate generator

∑ Arbitrary baud-rate setting from external clock input or internal timer

∑ Variable data length (7 to 9 bits (without parity bit); 6 to 8 bits (with parity bit))

∑ Error detection function (Framing, overrun, parity)

∑ Interrupt function (Two sources for transmission and reception)

∑ Transfer in NRZ format

(1) Register Configuration

8 bits

8 bits

USR

URD

UMC

UIDR (R)/UODR (W)

15

8

7

0

(R/W)

(R/W)

PEN

SBL

MC1

MC0

SMDE

RFC

SCKE

SOE

7

6

5

4

3

2

1

0

RDRF ORFE

PE

TDRE

RIE

TIE

RBF

TBF

15

14

13

12

11

10

9

8

D7

D6

D5

D4

D3

D2

D1

D0

7

6

5

4

3

2

1

0

--

RC2

RC1

RC0

--

--

P

D8

15

14

13

12

11

10

9

8

MD

--

--

--

DIV3

DIV2

DIV1

DIV0

15

14

13

12

11

10

9

8

Address: 000020

H

Address: 000021

H

Address: 000022

H

Address: 000023

H

Address: 00002D

H

bit

bit

bit

bit

bit

Mode control register

(UMC)

Status register

(USR)

Serial input data register

Serial output data register

(UIDR/UODR)

Rate and data register

(URD)

Communication prescaler

(CDCR)

MB90230 Series

32

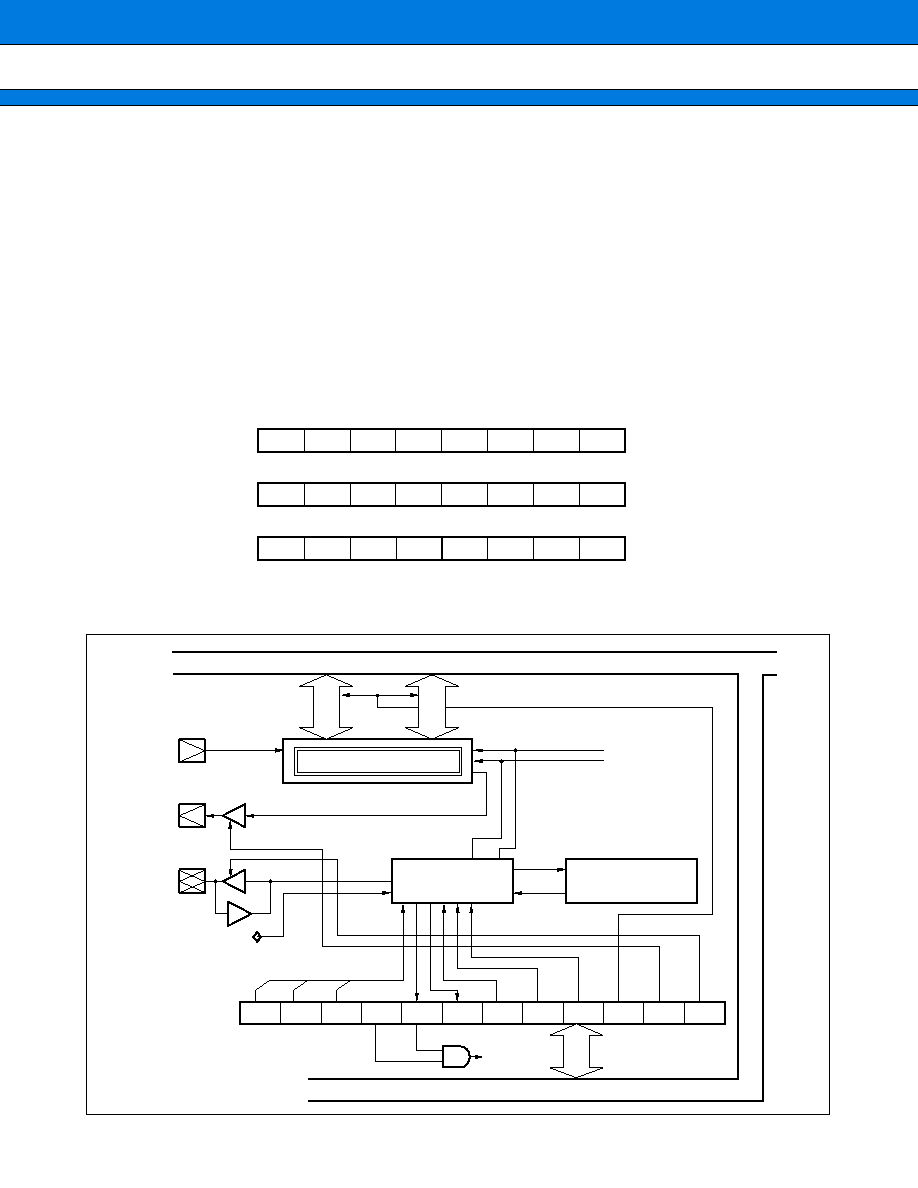

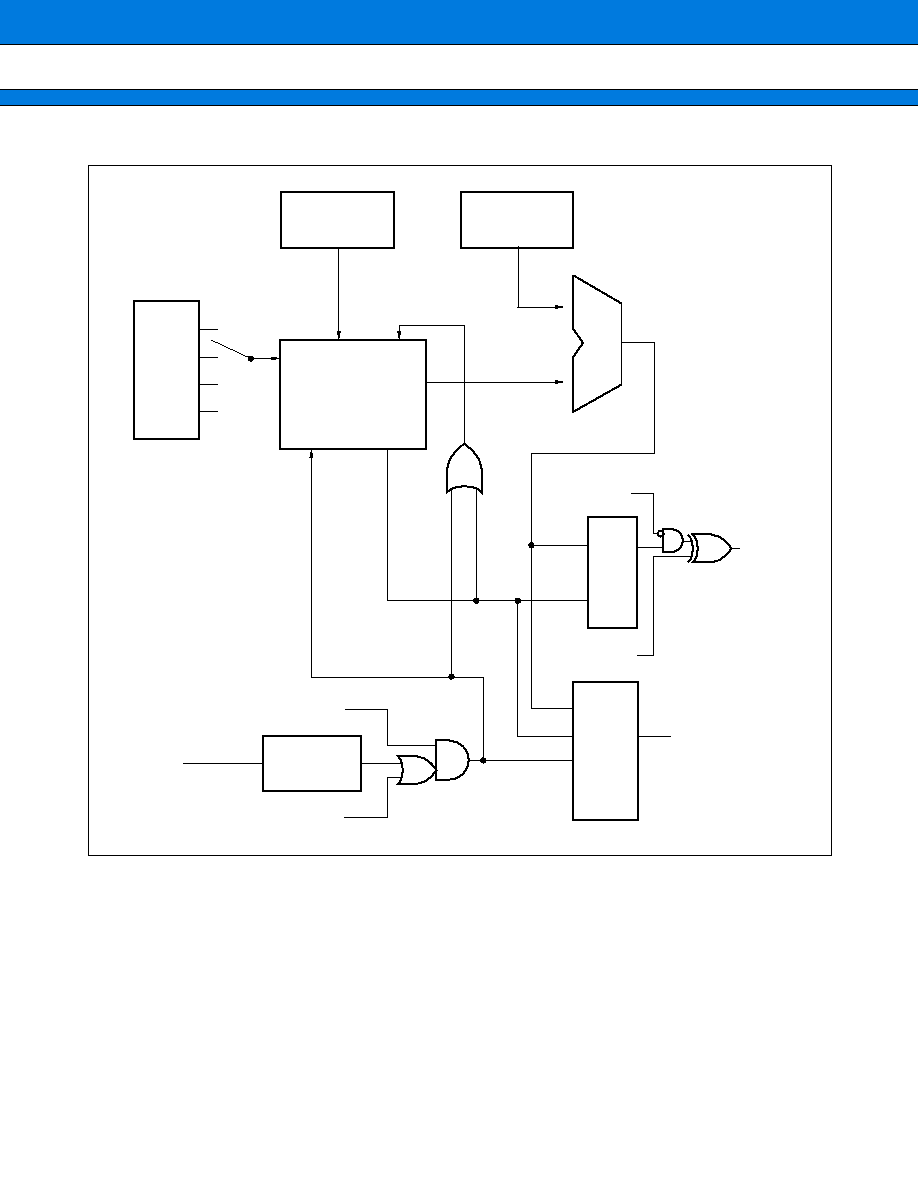

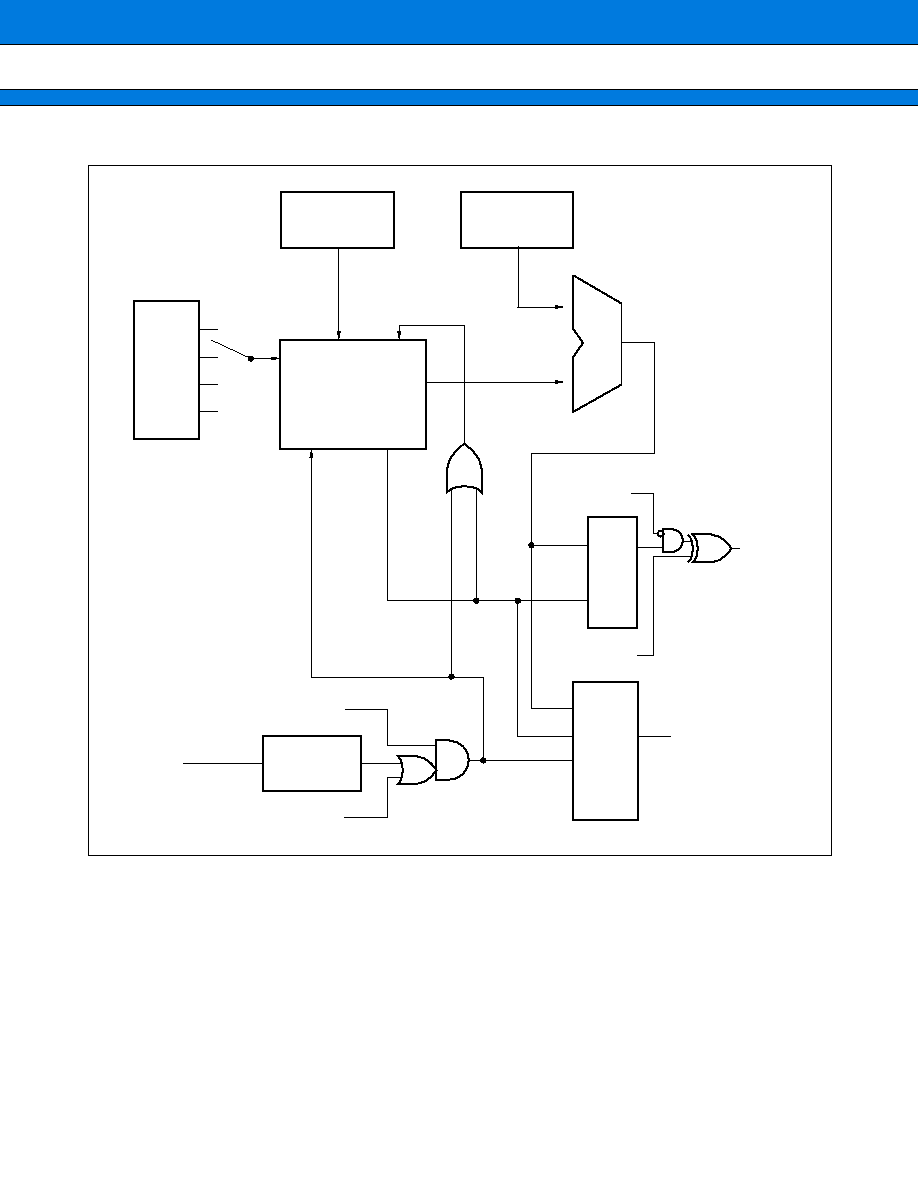

(2) Block Diagram

CONTROL BUS

Dedicated baud-rate clock

Internal timer

External clock

Clock selector

circuit

Receiving clock

Transmitting clock

Reception interrupt

(To CPU)

SCK0

Transmission interrupt

(To CPU)

Transmission control circuit

Transmission start circuit

Transmission bit counter

Transmission parity counter

SOT0

Transmission shifter

UODR

Reception control circuit

Start bit detector

Received parity counter

Reception shifter

End of reception

UIDR

Reception status

detection circuit

Reception error

occurrence signal for EI

2

OS

(To CPU)

Data bus

UMC

register

USR

register

PEN

SBL

MC1

MC0

SMDE

RFC

SCKE

SOE

RDRF

ORFE

PE

TDRE

RIE

TIE

RBF

TBF

URD

register

BCH

RC2

RC1

RC0

P

D8

CONTROL BUS

SIN0

Received bit counter

Start of transmission

33

MB90230 Series

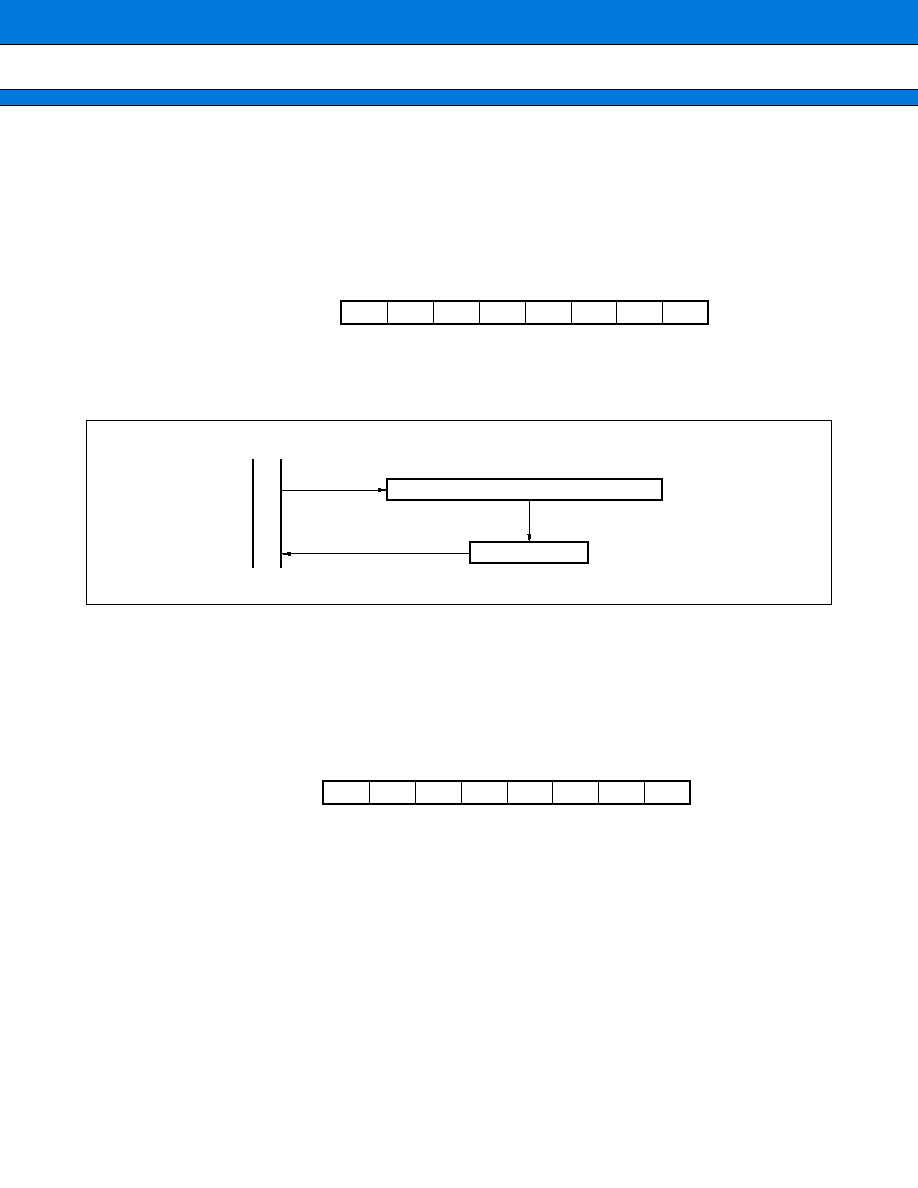

4. Extended Serial I/O Interface

This block is a serial I/O interface implemented on a single 8-bit channel that can transfer data in synchronization

with clock pulses. It allows the "LSB first" or "MSB first" option to be selected for data transfer. The serial I/O

port to be used can also be selected.

There are two serial I/O operation modes available:

∑ Internal shift clock mode: Transfers data in synchronization with internal clock pulses.

∑ External shift clock mode: Transfers data in synchronization with clock pulses entered from an external pin

(SCKx). In this mode, data can be transferred by instructions from the CPU by

operating the general-purpose port that shares the external pin (SCKx).

(1) Register Configuration

(2) Block Diagram

SMD2 SMD1

SMD0

SIE

SIR

BUSY

STOP

STRT

15

14

13

12

11

10

9

8

--

--

--

OUTC

MODE

BDS

SOE

SCOE

7

6

5

4

3

2

1

0

D7

D6

D5

D4

D3

D2

D1

D0

7

6

5

4

3

2

1

0

Address: 000025

H

Address: 000024

H

Address: 000026

H

bit

bit

bit

Serial mode control status

register (SMCS)

Serial data register

(SDR)

Internal data bus

(MSB first) D0 to D7

Selecting transfer direction

Read

Write

SDR (Serial data register)

Internal clock

Control circuit

Shift clock counter

Interrupt

request

SIN1, 2

SOT1, 2

SCK1, 2

SMD2 SMD1 SMD0

SIE

SIR

BUSY STOP STRT MODE BDS

D7 to D0 (LSB first)

2

1

0

SOE

Internal data bus

SCOE

MB90230 Series

34

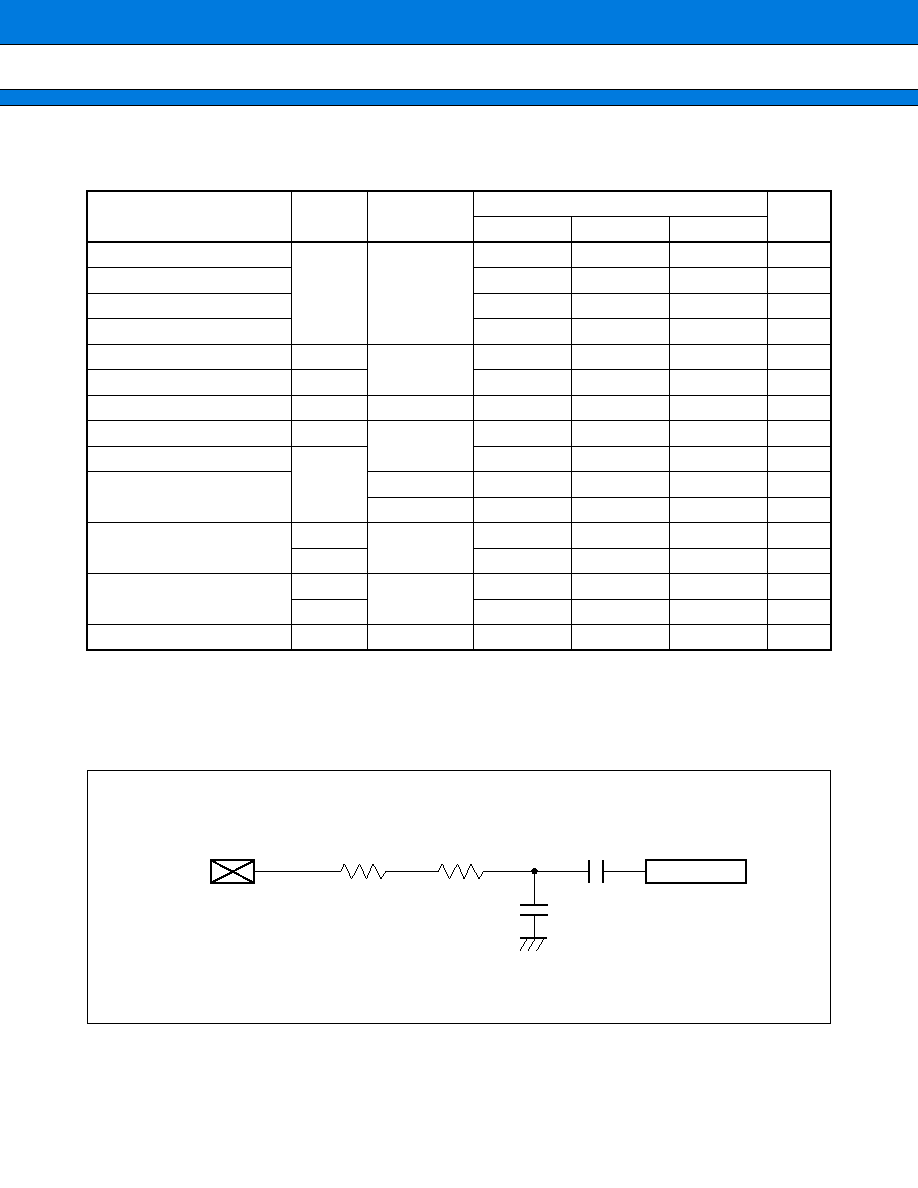

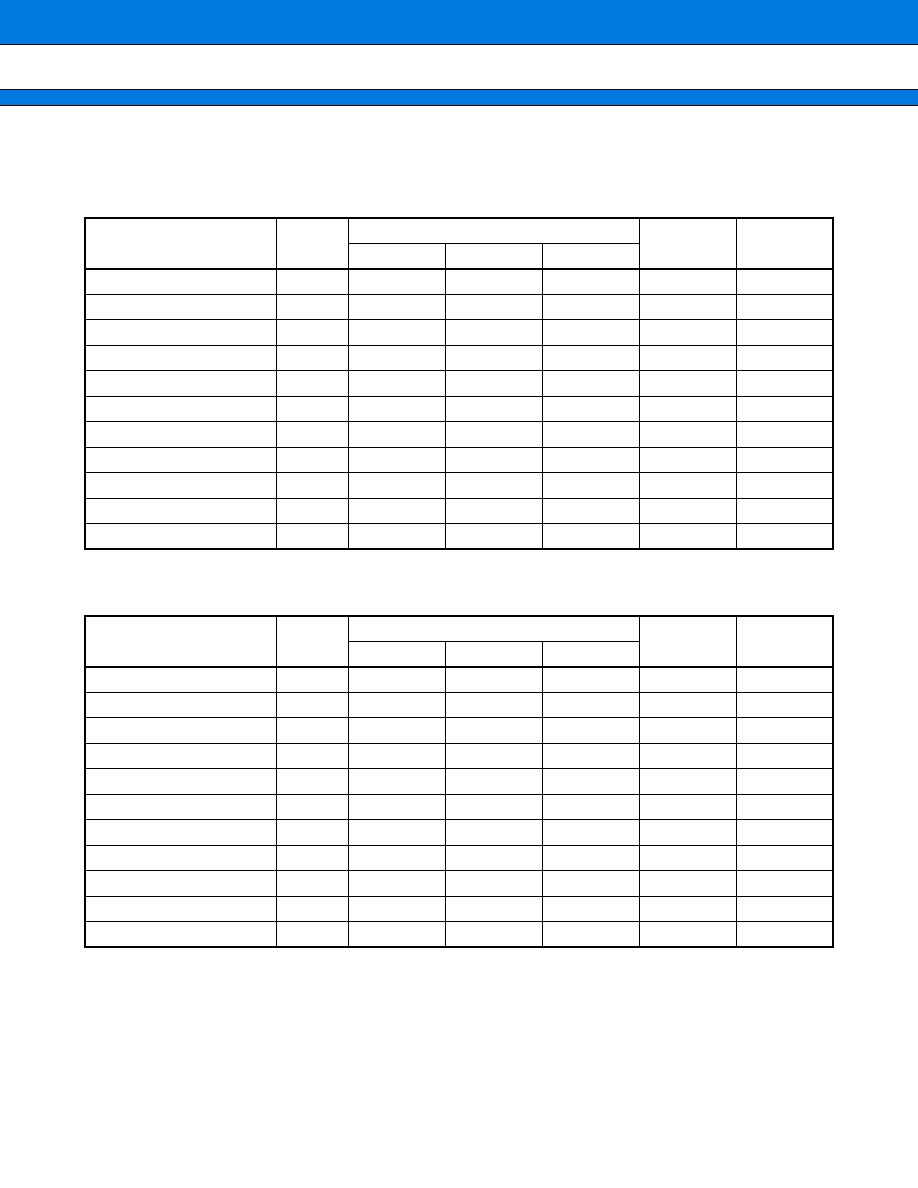

5. A/D Converter

The A/D converter converts the analog input voltage to a digital value. It has the following features:

∑ Conversion time: 5

µ

s min. per channel (at 16 MHz machine clock)

∑ RC-type successive approximation with sample-and-hold circuit

∑ 8-bit or 10-bit resolution

∑ Eight analog input channels programmable for selection

∑ A/D conversion mode selectable from the following three:

One-shot conversion mode: Converts a specified channel once.

Consecutive conversion mode: Converts a specified channel repeatedly.

Stop conversion mode: Converts one channel and suspends its own operation until the next activation (allowing

synchronized conversion start).

∑ Conversion mode:

Single conversion mode: Converts one channel (when the start and stop channels are the same).

Scan conversion mode: Converts multiple consecutive channels (when the start and stop channels are

different).

∑ On completion of A/D conversion, the converter can generate an interrupt request for termination of A/D

conversion to the CPU. This interrupt generation can activate the EI

2

OS to transfer the A/D conversion result

to memory, making the converter suitable for continuous operation.

∑ Conversion can be activated by software, external trigger (falling edge), and/or timer (rising edge) as selected.

(1) Register Configuration

ADCS1

ADCS0

15

8

7

0

Control status register

bit

000037, 36

H

ADCR1

ADCR0

Data register

000039, 38

H

ADER

Analog input enable register

000034

H

35

MB90230 Series

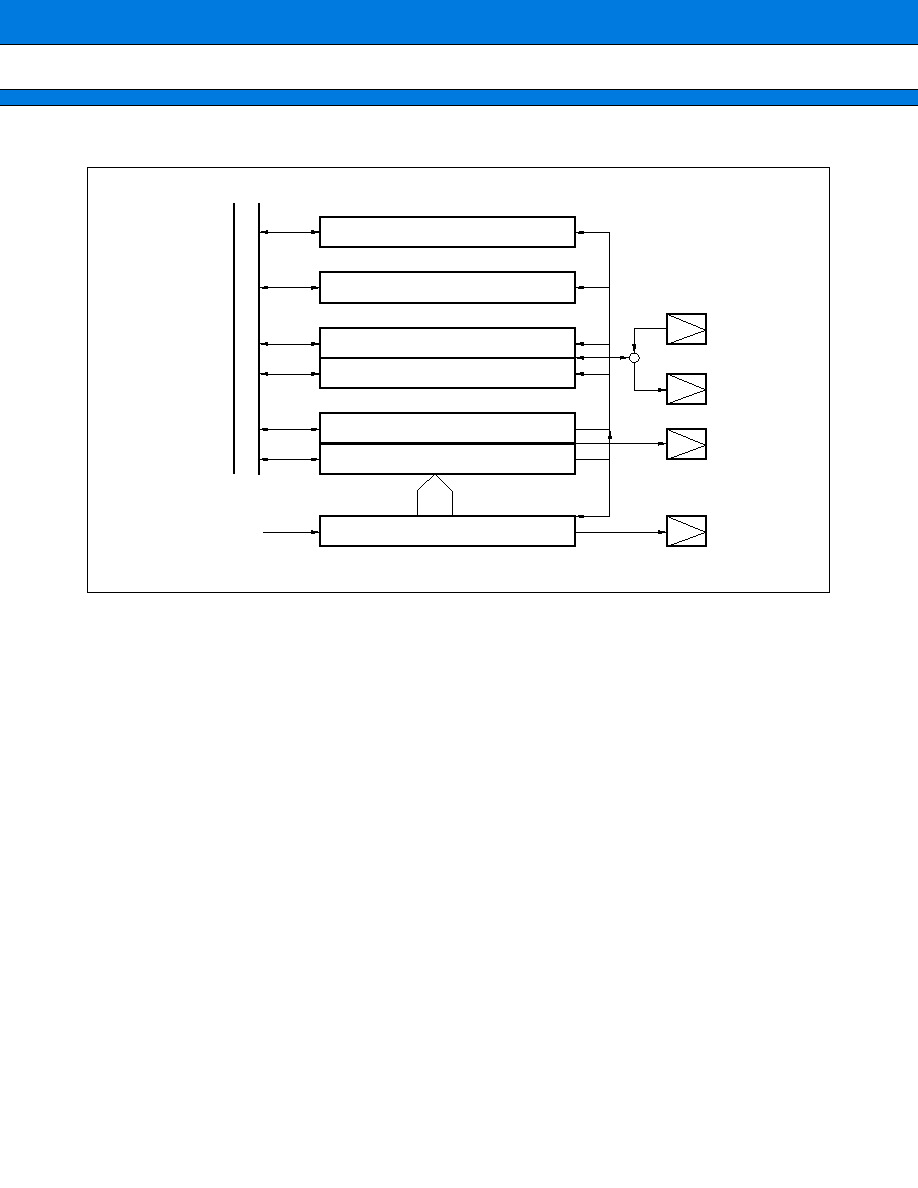

(2) Block Diagram

AV

CC

AVRH,

AVRL

AN0

AN1

AN2

AN3

AN4

AN5

AN6

AN7

MPX

Input circuit

Sample-and-hold circuit

Comparator

D/A converter

Successive

approximation register

Data register

Decoder

A/D control register 0

A/D control register 1

ADCR1, 0

ADCS1, 0

ATG

Timer

Interlocked with PPG timer

Activation by timer

Activation trigger

Operation clock

Prescaler

Data bus

AV

SS

MB90230 Series

36

6. 16-bit I/O Timer

The 16-bit I/O timer consists of 16-bit free run timer, 6-line output compare, and 4-line input capture modules.

The 16-bit I/O timer can output six independent waveforms based on the 16-bit free run timer, allowing the input

pulse width and external clock cycle to be measured.

(1) Outline of Functions

16-bit free run timer (

◊

1)

The 16-bit free run timer consists of a 16-bit up-count timer, a control register, and a prescaler. The value output

from this timer/counter is used as the base time by the input capture and output compare modules.

∑ The counter operation clock cycle can be selected from the following four:

Four internal clock cycles (

/4,

/16,

/32,

/64)

∑ The interrupt counter value can be generated by compare/match operation with the overflow register and

compare register 0 (compare/match operation requires the mode setting).

∑ The counter value can be initialized to "0000

H

" by compare/match operation with the reset register, software

clear register, and compare register 0.

Output compare module (

◊

6)

The output compare module consists of six 16-bit compare registers, compare output latches, and control

registers. When the compare value matches the 16-bit free run timer value, this module can generates an

interrupt while inverting the output level.

∑ Six compare registers can operate independently, and have each output pin and interrupt flag.

∑ Two compare resisters can be used to control the same output pin.

∑ The initial value for each output pin can be set.

∑ The interrupt can be generated by compare/match operation.

Input capture module (

◊

4)

The input capture module consists of four external input pins and associated capture and control registers. This

module can detect an arbitrary edge of the signal input from each external input pin to generate an interrupt

while holding the 16-bit free run timer value in the capture register.

∑ The external input signal edge can be selected from the rising edge, failing edge or both edges.

∑ Four input capture lines can operate independently.

∑ The interrupts can be generated by a valid edge of external input signals. The extended intelligent I/O service

(EI

2

OS) can be activated.

37

MB90230 Series

(2) Register Configuration

TCDT

15

0

Timer data register

bit

00004C

H

TCCS

Control status register

00004E

H

OCP0 to 5

Compare register 0 to 5

bit

000050, 52, 58, 5A

H

000060, 62

H

CS

◊

1

CS

◊

0

Control status register 0 to 5

000054, 55

H

00005C, 5D

H

000064, 65

H

15

0

IPCP0 to 3

Compare register 0 to 3

bit

000070, 72, 78, 7A

H

ICS0 to 3

Control status register 0 to 3

000074, 7C

H

15

0

∑ 16-bit free run timer

∑ 16-bit output compare module

∑ 16-bit input capture module

MB90230 Series

38

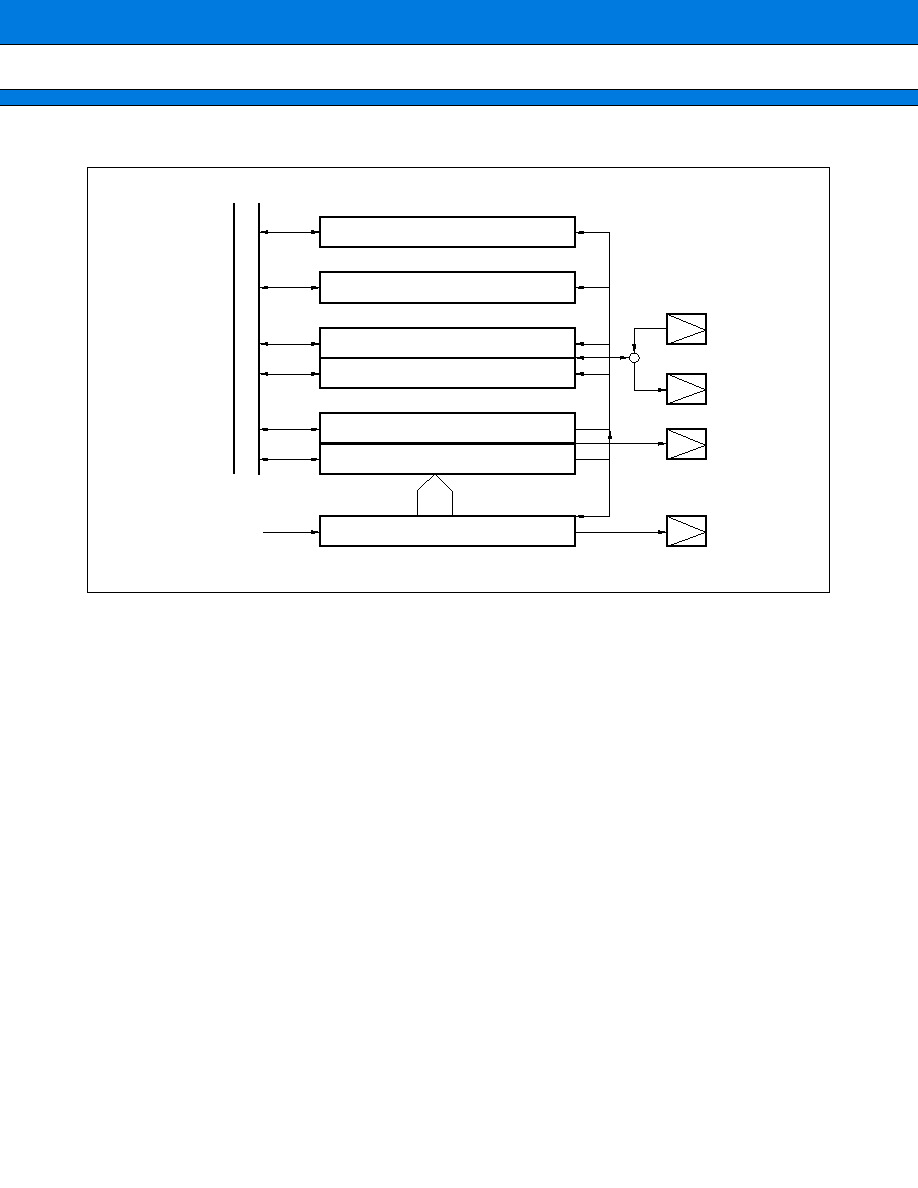

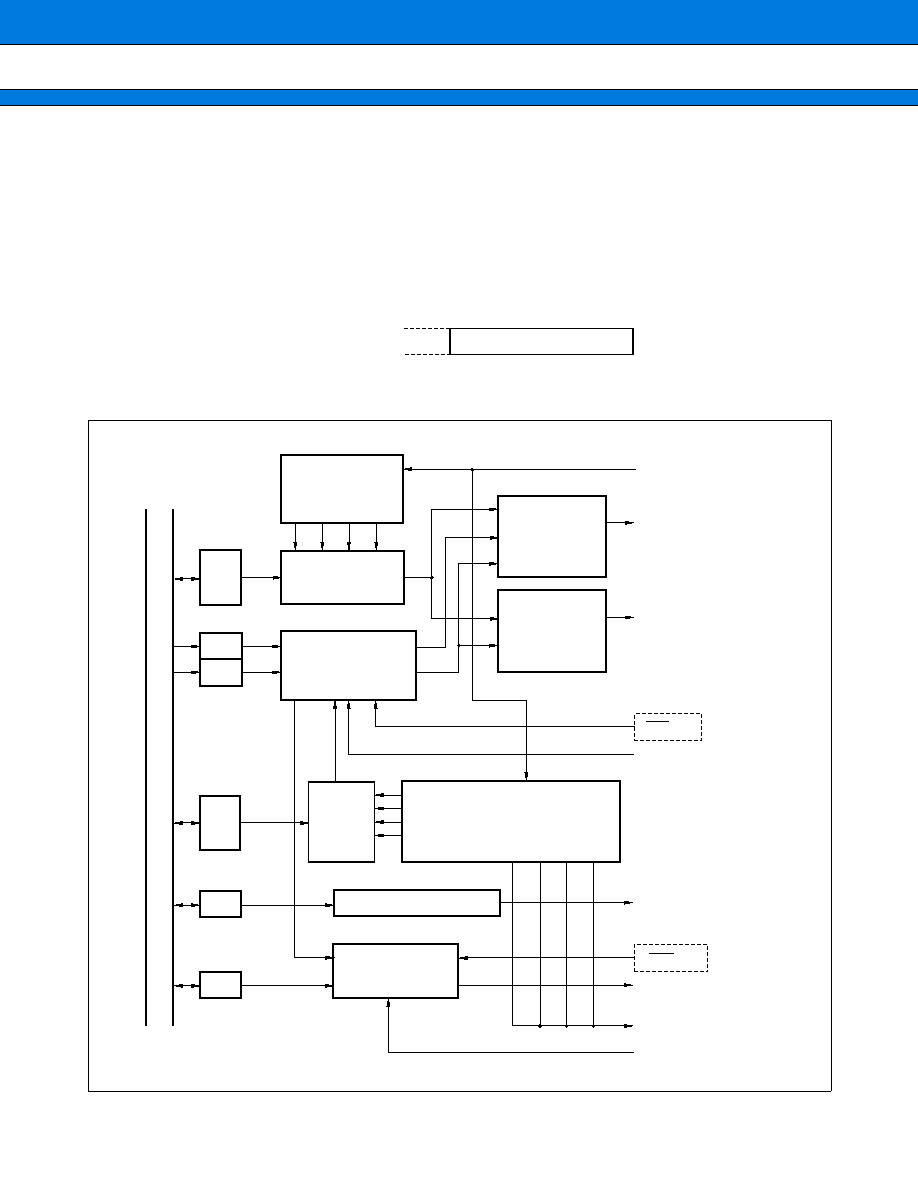

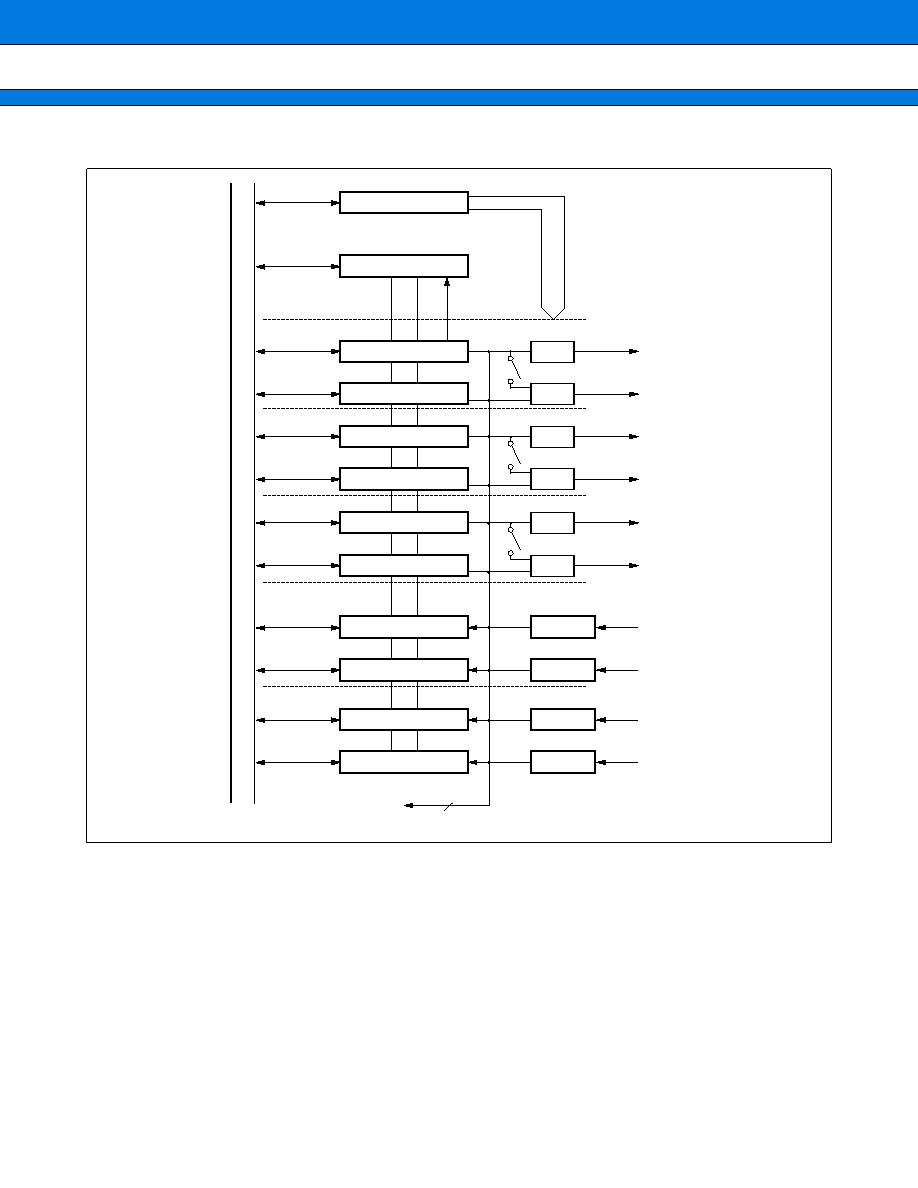

(3) Block Diagram

16-bit free run timer

Control logic

16-bit timer

Compare register 0

Capture register 0

Output compare 0

Input capture 0

TQ

TQ

TQ

TQ

Edge selection

Bus

Interrupt

T

o

each block

OUT 0

OUT 1

OUT 2

OUT 3

IN 0

IN 1

Clear

TQ

TQ

OUT 4

OUT 5

IN 2

IN 3

10

Compare register 1

Compare register 2

Compare register 3

Compare register 4

Compare register 5

Output compare 1

Output compare 2

Input capture 1

Capture register 1

Capture register 2

Capture register 3

Edge selection

Edge selection

Edge selection

39

MB90230 Series

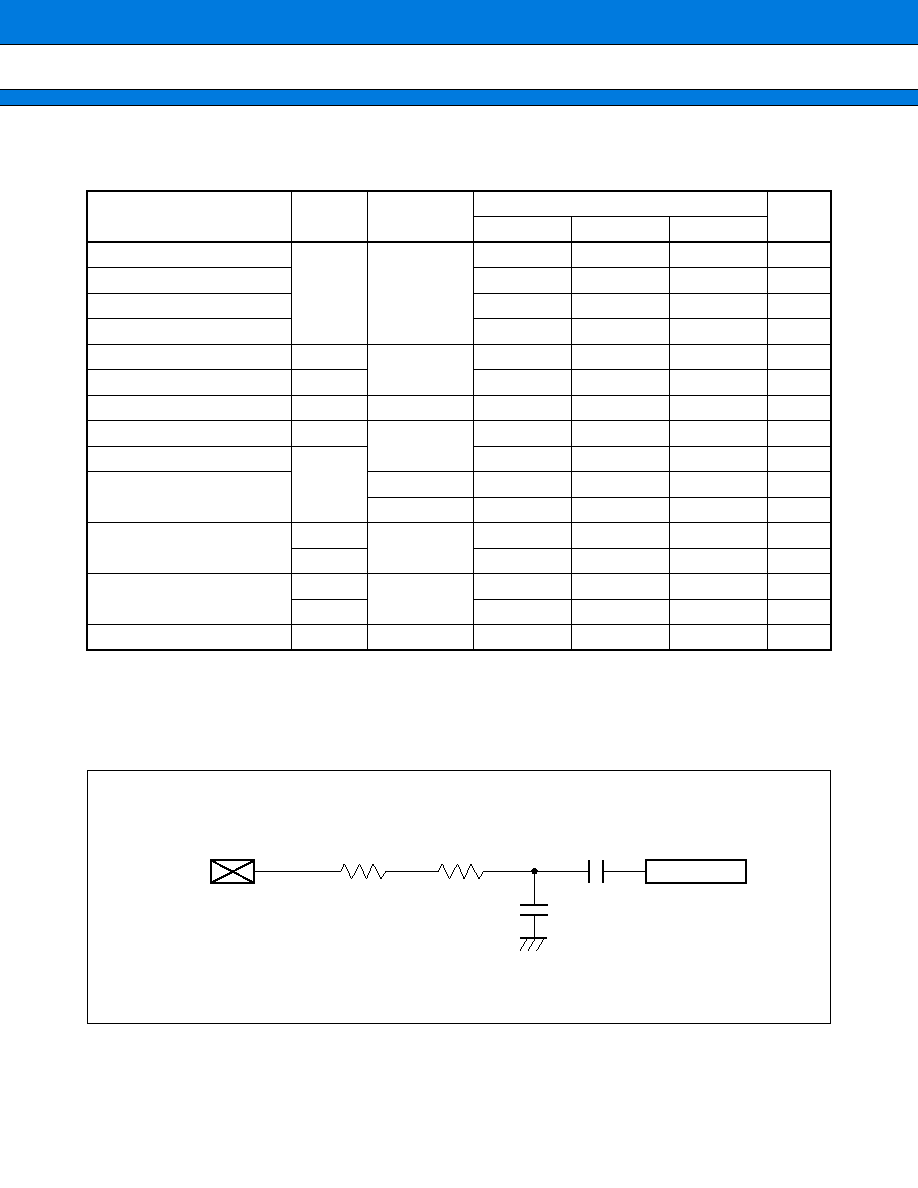

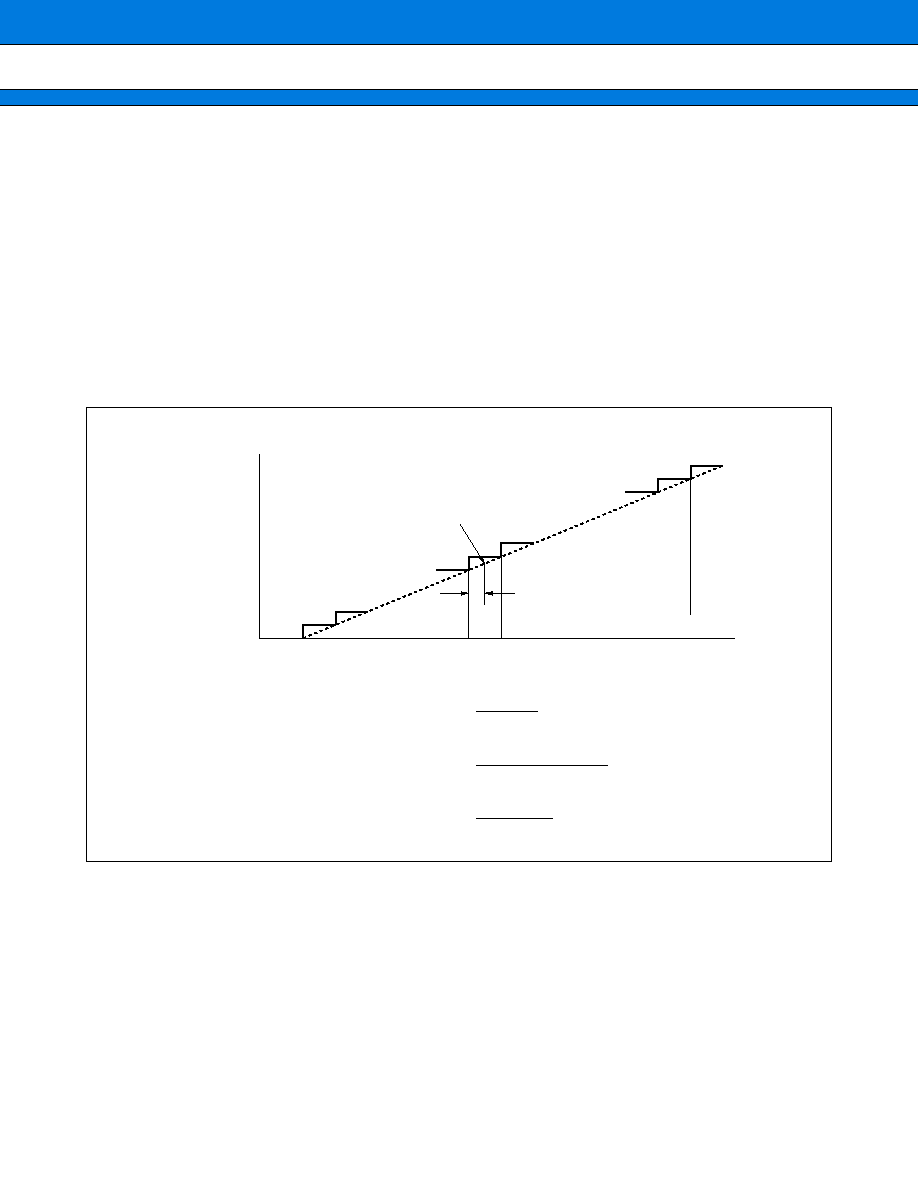

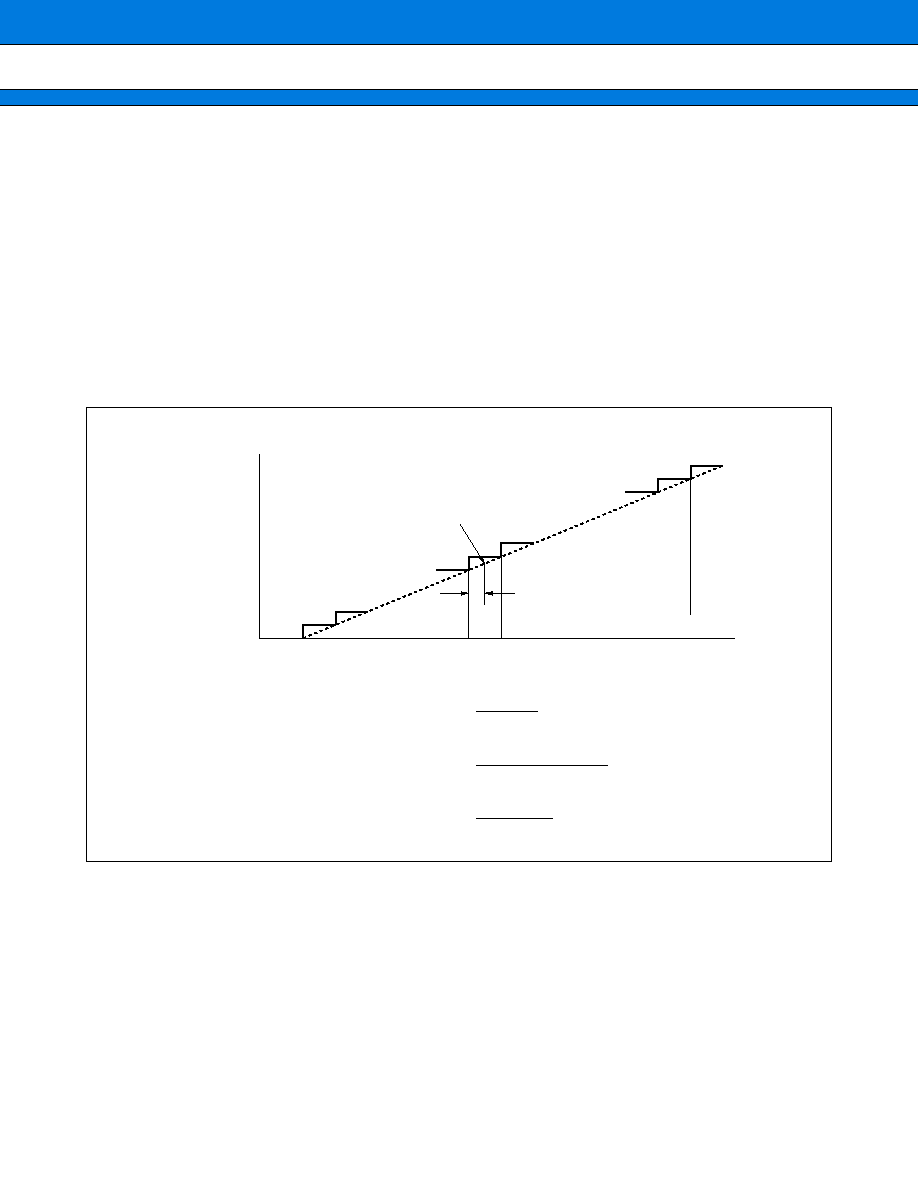

7. PPG Timer (Programmable Pulse Generator)

This module can output the pulse synchronized with an external or software trigger. The cycle and duty factor

of the output pulse can be changed arbitrarily by changing the values in two 8-bit registers.

PWM function: Outputs a pulse in programmable mode while changing the values in the two registers in

synchronization with the input trigger.

This module can also be used as a D/A converter using an external circuit.

Single-shot function: Detects the trigger input edge to output a single pulse.

(1) Module Configuration

This module consists of an 8-bit down counter, prescaler, 8-bit cycle setting register, 8-bit duty factor setting

register, 16-bit control register, external trigger input pin, and PPG output pin.

(2) Register Configuration

15

8

7

0

000028

H

PCSR

Cycle setting register

000029

H

PDUT

Duty factor setting register

PCNTH

PCNTL

Control status register

00002B

H

, 2A

H

Address:

bit

MB90230 Series

40

(3) Block Diagram

Prescaler

TRG input

Edge detection

Software trigger

Enable

Interrupt selection

IRQ

Inverted bit

PPG output

S Q

R

PPG mask

cmp

P D U T

P C S R

ck

Load

8-bit

down counter

Start

Borrow

1 /

4 /

16 /

64 /

41

MB90230 Series

8. Serial E

2

PROM Interface

This module is the interface circuit dedicated to external bit-serial E

2

PROM.

(1) Features

∑ Instruction code support (compatible with the MB8557).

∑ Selectable address length: 8 to 11 bits

∑ Selectable data length: 8 or 16 bits

∑ Automatic address increment function

∑ Transmit/receive data transfer enabled by EI

2

OS