| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: IH6208MJE | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

12-129

Semiconductor

April 1999

IH6208

8-Channel

CMOS Analog Multiplexer

Features

∑ Ultra Low Leakage - I

D(OFF)

100pA (Typ)

∑ r

DS(ON)

< 400

Over Full Signal and Temperature

Range

∑ Power Supply Quiescent Current Less Than 100

µ

A

∑

±

14V Analog Signal Range

∑ No SCR Latchup

∑ Break-Before-Make Switching

∑ Binary Address Control (2 Address Inputs Control 2

Out of 8 Channels)

∑ TTL and CMOS Compatible Address Control

∑ Pin Compatible with DG509A, HI-509 and ADG509A

∑ Internal Diode in Series with V+ for Fault Protection

Description

The IH6208 is a CMOS 2 of 8 multiplexer. The part is a

plug-in replacement for the DG509A. Two-line binary

decoding is used so that the 8 channels can be controlled in

pairs by the binary inputs; additionally a third input is

provided for use as a system enable. When the ENABLE

input is high (5V), the channels are sequenced by the 2 line

binary inputs, and when low (0V) all channels are off. The 2

Address inputs arecontrolled by TTL logic or CMOS logic

elements with a "0" corresponding to any voltage less than

0.8V and a "1" corresponding to any voltage greater than

2.4V. Note that the ENABLE input must be taken to 5V to

enable the system, and less than 0.8V to disable the system.

Pinout

IH6208

(CERDIP, PDIP)

TOP VIEW

Functional Diagram

Part Number Information

PART

NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG.

NO.

IH6208MJE

-55 to 125

16 Ld CERDIP

F16.3

IH6208MJE/883B

-55 to 125

16 Ld CERDIP

F16.3

IH6208MFE/883B

-55 to 125

16 Ld Flat Pack

K16.A

IH6208CJE

0 to 70

16 Ld CERDIP

F16.3

IH6208CPE

0 to 70

16 Ld PDIP

E16.3

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

A

0

EN

V-

S

2a

S3a

S

4a

A

1

V+

S

2b

S

3b

S

4b

GND

D

b

S

1b

S

1a

D

a

TRUTH TABLE

A

1

A

0

EN

ON SWITCH PAIR

x

x

0

None

0

0

1

1a, 1b

0

1

1

2a, 2b

1

0

1

3a, 3b

1

1

1

4a, 4b

NOTE: A

0

, A

1

Logic "1" = V

AH

2.4V, V

ENH

4.5V

Logic "0" = V

AL

0.8V.

S

1a

S

2a

S

3a

S

4a

S

1b

S

3b

S

4b

S

2b

D

a

Db

ADDRESS DECODER

1 OF 4

ENABLE

INPUT

A

0

A

1

EN

2 LINE BINARY ADDRESS INPUTS

ABOVE EXAMPLE SHOWS

(0 0) AND EN = 5V (EN = "1" for +5V, "0" for 0V)

CHANNELS 1a AND 1b ON.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

©

Harris Corporation 1997

File Number

3157.2

OBSOLETE PR

ODUCT

POSSIBLE SUBSTITUTE PR

ODUCT

DG409, DG509A, HI-0509(A)

12-130

Absolute Maximum Ratings

Thermal Information

V

IN

(A, EN) to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . -15V to 15V

V

S

or V

D

to V+ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V, -36V

V

S

to V

D

to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V, 36V

V+ to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18V

V- to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-18V

Current (Any Terminal) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30mA

Current (Analog Source or Drain) . . . . . . . . . . . . . . . . . . . . . . 20mA

Operating Conditions

Temperature Range

C Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0

o

C to 70

o

C

M Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

JC

(

o

C/W)

CERDIP Package . . . . . . . . . . . . . . . .

80

22

Ceramic Flatpack Package . . . . . . . . .

85

25

PDIP Package . . . . . . . . . . . . . . . . . . .

100

N/A

Maximum Junction Temperature (Hermetic Package) . . . . . . . . 175

o

C

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

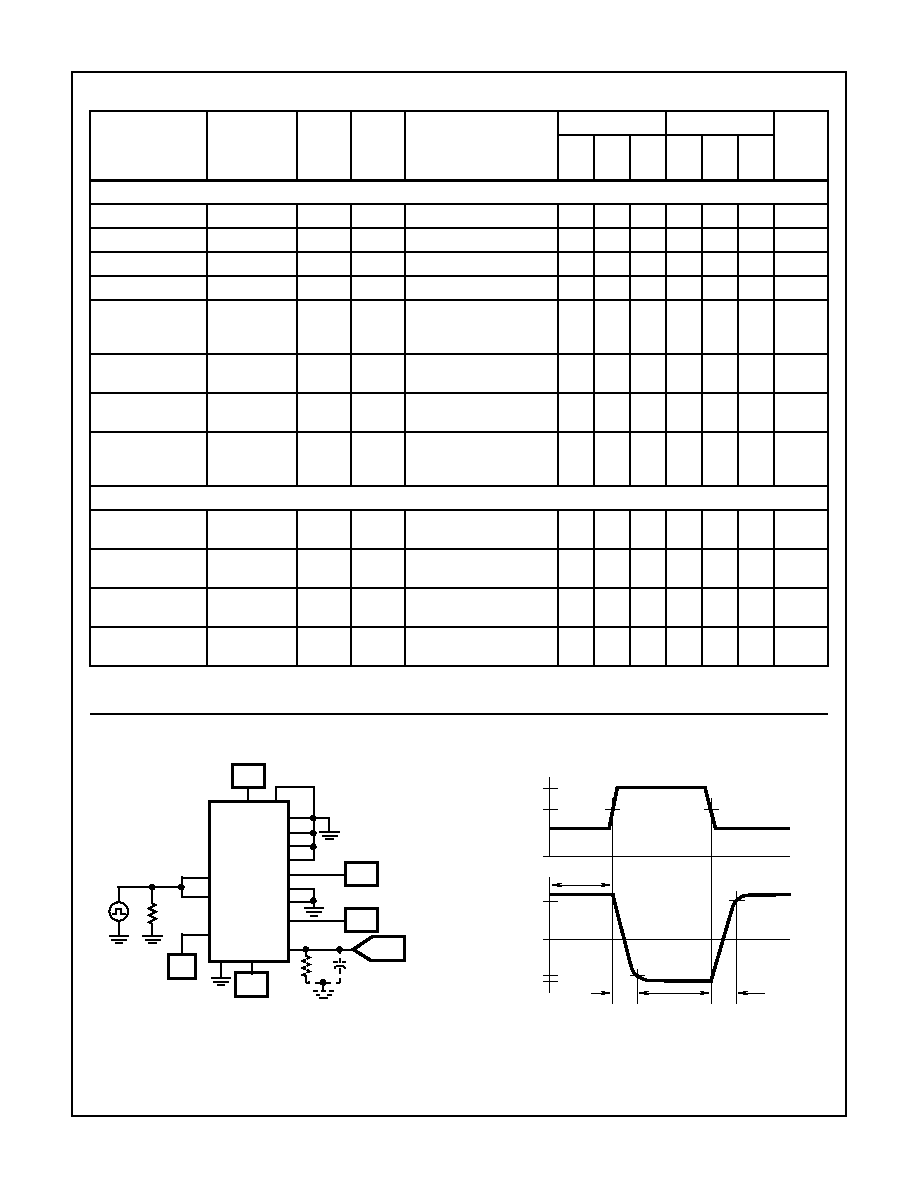

Electrical Specifications

V+ = 15V, V- = -15V, V

EN

= +5V, Ground = 0V, Unless Otherwise Specified, (Note 4)

PARAMETER

MEASURED

TERMINAL

NO

TESTS

PER

TEMP

TYP

25

o

C

TEST CONDITIONS

M SUFFIX (

o

C)

C SUFFIX (

o

C)

UNITS

-55

25

125

0

25

70

SWITCH

r

DS(ON)

S to D

8

180

V

D

= +10V, I

S

= -1.0mA

Sequence Each Switch On

V

AL

= 0.8V, V

AH

= 2.4V

300

300

400

350

350

450

8

150

V

D

= -10V, I

S

= -1.0mA

Sequence Each Switch On

V

AL

= 0.8V, V

AH

= 2.4V

300

300

400

350

350

450

r

DS(ON)

20

r

DS(ON)

=

V

S

=

±

10V

-

-

-

-

-

-

%

I

S(OFF)

S

8

0.002

V

S

= 10V, V

D

= -10V

-

±

0.5

±

50

-

±

1

±

50

nA

8

0.002

V

S

= -10V, V

D

= 10V,

V

EN

= 0.8V

-

±

0.5

±

50

-

±

1

±

50

nA

I

D(OFF)

D

2

0.03

V

D

= 10V, V

S

= -10V,

V

EN

= 0.8V

-

±

2

±

50

-

±

5

±

100

nA

2

0.03

V

D

= -10V, V

S

= 10V,

V

EN

= 0.8V

-

±

2

±

50

-

±

5

±

100

nA

I

D(ON)

D

8

0.1

V

S(ALL)

= V

D

= 10V,

Sequence Each Switch On

V

AL

= 0.8V, V

AH

= 2.4V

-

±

2

±

50

-

±

5

±

100

nA

8

0.1

V

S(ALL)

= -10V,

Sequence Each Switch On

V

AL

= 0.8V, V

AH

= 2.4V

-

±

2

±

50

-

±

5

±

100

nA

INPUT

I

AN(ON)

A

0

, A

1

2

0.01

V

A

= 0V

-

-10

-30

-

-10

-30

µ

A

I

AN(OFF)

2

0.01

V

A

= 14V

-

10

30

-

10

30

µ

A

I

A

A

0

, A

1

2

0.01

V

EN

= 5V, All V

A

= 0V

(Address Pins)

-

-10

-30

-

-10

-30

µ

A

EN

1

0.01

V

EN

= 0V, All V

A

= 0V

(Address Pins)

-

-10

-30

-

-10

-30

µ

A

r

DS ON

(

)

MAX

r

DS ON

(

)

M I N

≠

r

DS ON

(

)

AV G

-----------------------------------------------------------------------------------,

IH6208

12-131

DYNAMIC

t

TRANSITION

D

0.3

See Figure 1

-

1

-

-

-

-

µ

s

t

OPEN

D

0.2

See Figure 2

-

-

-

-

-

-

µ

s

t

EN(ON)

D

0.6

See Figure 3

-

1.5

-

-

-

-

µ

s

t

EN(OFF)

D

0.4

See Figure 3

-

1

-

-

-

-

µ

s

"OFF" Isolation

D

60

V

EN

= 0V, R

L

= 200

,

C

L

= 3pF, V

S

= 3V

RMS

,

f = 500kHz

-

-

-

-

-

-

dB

C

S(OFF)

S

5

V

S

= 0V, V

EN

= 0V,

f = 140kHz to 1MHz

-

-

-

-

-

-

pF

C

D(OFF)

D

12

V

D

= 0V, V

EN

= 0V,

f = 140kHz to 1MHz

-

-

-

-

-

-

pF

C

DS(OFF)

D to S

1

V

S

= 0V, V

D

= 0V,

V

EN

= 0V,

f = 140kHz to 1MHz

-

-

-

-

-

-

pF

SUPPLY

Positive Supply

Current

V+

1

40

V

EN

= 5V,

All V

A

= 0V or 5V

-

-

200

-

-

1000

µ

A

Negative Supply

Current

V-

1

2

V

EN

= 5V,

All V

A

= 0V or 5V

-

-

100

-

-

1000

µ

A

Positive Standby

Current

V+

1

1

V

EN

= 0V,

All V

A

= 0V or 5V

-

-

100

-

-

1000

µ

A

Negative Standby

Current

V-

1

1

V

EN

= 0V,

All V

A

= 0V or 5V

-

-

100

-

-

1000

µ

A

NOTE:

2. See "Enable Input Strobing Levels" in Application Section.

Electrical Specifications

V+ = 15V, V- = -15V, V

EN

= +5V, Ground = 0V, Unless Otherwise Specified, (Note 4) (Continued)

PARAMETER

MEASURED

TERMINAL

NO

TESTS

PER

TEMP

TYP

25

o

C

TEST CONDITIONS

M SUFFIX (

o

C)

C SUFFIX (

o

C)

UNITS

-55

25

125

0

25

70

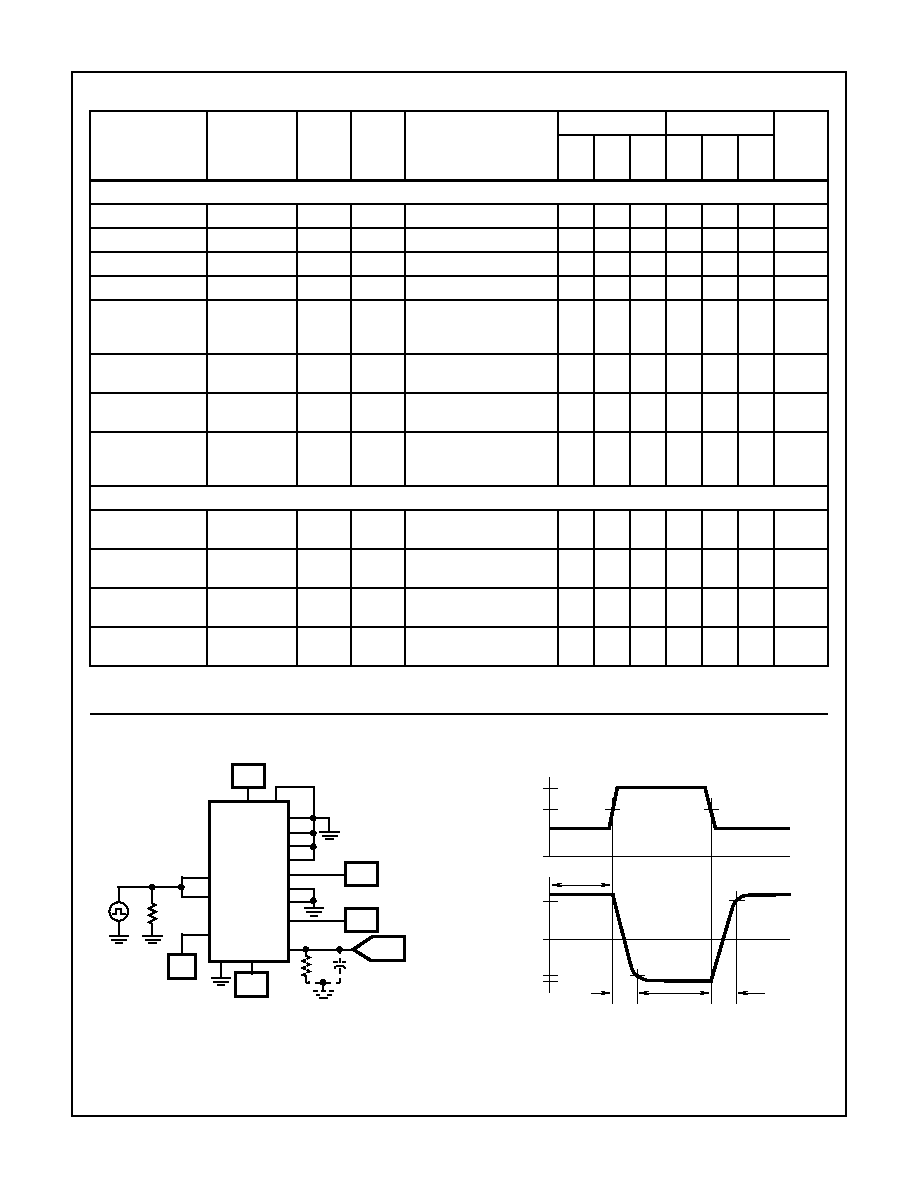

Switching Information

FIGURE 1. t

TRANSITION

SWITCHING TEST CIRCUIT AND WAVEFORMS

S

1a

A

1

A

0

±

10V

±

10V

+15V

-15V

PROBE

D

2

V

OUT

V+

IH6208

EN

PROBE IMPEDANCE

C

P

R

P

V-

GND

V

A

50

0.8V

t

trans

D1

S

2a

S

3a

S

4a

S

1b

S

2b

S

3b

S

4b

+5V

1.4V

3.0V

0

0

V

S1b

0.9V

S1b

V

S4b

0.9V

S4b

S

1b(ON)

S

4b(ON)

t

trans

R

P

1M

C

P

30pF

IH6208

12-132

IH6208 Application Information

ENABLE Input Strobing Levels

The ENABLE input on the IH6208 requires a minimum of

+4.5V to trigger to the "1" state and a maximum of +0.8V to

trigger to the "0" state. If the ENABLE input is being driven

from TTL logic, a pull-up resistor of 1k

to 3k

is required

from the gate output to +5V supply. (See Figure 4)

When the EN in put is driven from CMOS logic, no pullup is

necessary, see Figure 5.

The supply voltage of the CD4009 affects the switching

speed of the IH6208; the same is true for TTL supply voltage

levels. The following chart shows the effect, on t

trans

for a

supply varying from +4.5V to +5.5V.

The throughput rate can therefore be maximized by using a

+5V to +5.5V supply for the ENABLE Strobe Logic.

The examples shown in Figure 4 and 5 deal with ENABLE

strobing when expansion to more than eight channels is

required. In these cases the EN terminal acts as a fourth

address input. If eight channels or less are being

multiplexed, the EN terminal can be directly connected to

+5V logic supply to enable the IH6208 at all times.

Using the IH6208 with Supplies Other Than

±

15V

The IH6208 can be used with power supplies ranging from

±

6V to

±

16V. The switch r

DS(ON)

will increase as the supply

voltages decrease, however, the multiplexer error term (the

product of leakage times r

DS(ON)

) will remain approximately

constant since leakage decreases as the supply voltages

are reduced.

Caution must be taken to ensure that the enable (EN)

voltage is at least 0.7V below V+ at all times. If this is not

done, the Address input strobing levels will not function

properly. This may be achieved quite simply by connecting

EN (pin 2) to V+ (pin 14) via a silicon diode as shown in

Figure 6. When using this type of configuration, a further

requirement must be met: the strobe levels of A0 and A1

must be within 2.5V of the EN voltage in order to define a

binary "1" state. For the case shown in Figure 6 the EN

voltage is 11.3V which means that logic high at A0 and A1 is

+8.8V (logic low continues to be 0.8V). In this configuration

the IH6208 cannot be driven by TTL (+5V) or CMOS (+5V)

logic. It can be driven by TTL open collector logic or CMOS

logic with +12V supplies.

If the logic and the IH6208 have common supplies, the EN

pin should again be connected to the supply through a

silicon diode. In this case, tying EN to the logic supply

directly will not work since it violates the 0.7V differential

voltage required between V+ and EN, (See Figure 7). A 1

µ

F

capacitor can be placed across the diode to minimize

switching glitches.

FIGURE 2. t

OPEN

(BREAK-BEFORE-MAKE) SWITCHING TEST CIRCUIT AND WAVEFORMS

FIGURE 3. t

ON

AND t

OFF

SWITCHING TEST CIRCUIT AND WAVEFORMS

Switching Information

(Continued)

-2V

S

2b

THRU

S

3b

S

4b

A

1

A

0

+15V

-15V

D

2

V

OUT

IH6208

EN

35pF

GND

V

A

200

+5V

S

1b

V

A

+0.8V

+3V

0.9V

O

V

O

50%

0

V

S

SWITCH

V

OUT

OUTPUT

(SEE PINOUT)

t

OPEN

t

OPEN

-5V

ALL

OTHERS

S

4b

A

1

A

0

+15V

-15V

D

2

V

OUT

IH6208

EN

35pF

GND

V

EN

200

S

1b

V

EN

+0.8V

+5V

0.9V

O

V

O

50%

SWITCH

V

OUT

OUTPUT

(SEE FIGURE 1)

t

EN(ON)

t

EN(OFF)

0.1V

O

0V

t

r

and t

f

100ns

-5V

CMOS OR TTL

SUPPLY VOLTAGE

TYPICAL T

TRANS

AT 25

o

C

+4.5V

400ns

+4.75V

300ns

+5.00V

250ns

+5.25V

200ns

+5.50V

175ns

IH6208

12-133

Switching Information

FIGURE 4. ENABLE INPUT STROBING FROM TTL LOGIC

FIGURE 5. CMOS LOGIC DRIVING ENABLE PIN

FIGURE 6. IH6208 CONNECTION DIAGRAM FOR LESS THAN

±

15V SUPPLY OPERATION

+5V

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

A

0

EN

-15V

S

2a

S

3a

S

4a

A

1

S

2b

S

3b

S

4b

D

2

+15V

S

1a

D

1

1k

1

2

3

4

5

6

7

14

13

12

11

10

9

8

DM7404N

TTL LOGIC

IH6208

0V

+3V

S

1b

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

+5V

CD4009

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

A

0

EN

-15V

S

2a

S

3a

S

4a

A

1

S

2b

S

3b

S

4b

D

2

+15V

S

1a

D

1

IH6208

S

1b

CMOS LOGIC

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

A

0

EN

-12V

A

1

+12V

A CHANNELS COMMON DRAIN OUTPUT = D

1

IH6208

B CHANNEL SOURCE INPUTS

A CHANNEL SOURCE INPUTS

1N914

D

2

= B CHANNEL DRAIN OUTPUT (COMMON)

IH6208