| ÐлекÑÑоннÑй компоненÑ: HT46R52 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

HT46R51/HT46R52

A/D Type 8-Bit OTP MCU

Rev. 1.40

1

July 12, 2005

General Description

The HT46R51/HT46R52 are 8-bit high performance,

RISC architecture microcontroller devices specifically

designed for A/D applications that interface directly to

analog signals, such as those from sensors. The advan-

tages of low power consumption, I/O flexibility, timer

functions, oscillator options, multi-channel A/D con-

verter, Pulse Width Modulation function, HALT and

wake-up functions, watchdog timer, as well as low cost,

enhance the versatility of these devices to suit a wide

range of A/D application possibilities such as sensor

signal processing, chargers, motor driving, industrial

control, consumer products, subsystem controllers, etc.

Features

·

Low-power fully static CMOS design

·

Operating voltage:

f

SYS

=4MHz: 2.2V~5.5V

f

SYS

=8MHz: 3.3V~5.5V

·

Program Memory:

1K

´14 OTP (HT46R51)

2K

´14 OTP (HT46R52)

·

Data memory: 88

´8 RAM

·

A/D converter: 12bits

´5Ch

External A/D converter reference voltage input pin

·

14 bidirectional I/O lines

·

1 interrupt input shared with an I/O line

·

8-bit programmable timer/event counter with over-

flow interrupt and 7-stage prescaler

·

On-chip crystal and RC oscillator

·

6-level subroutine nesting

·

Watchdog Timer

·

Low voltage reset function

·

HALT function

·

Up to 0.5

ms instruction cycle with 8MHz system clock

at V

DD

=5V

·

1-channel 8-bit PWM output shared with an I/O line

·

PFD function

·

Bit manipulation instruction

·

Table read instruction

·

63 powerful instructions

·

All instructions in one or two machine cycles

·

18-pin DIP, 20-pin SOP/SSOP package

Technical Document

·

Tools Information

·

FAQs

·

Application Note

-

HA0003E Communicating between the HT48 & HT46 Series MCUs and the HT93LC46 EEPROM

-

HA0004E HT48 & HT46 MCU UART Software Implementation Method

-

HA0084E NiMH Battery Charger Demo Board - Using the HT46R52

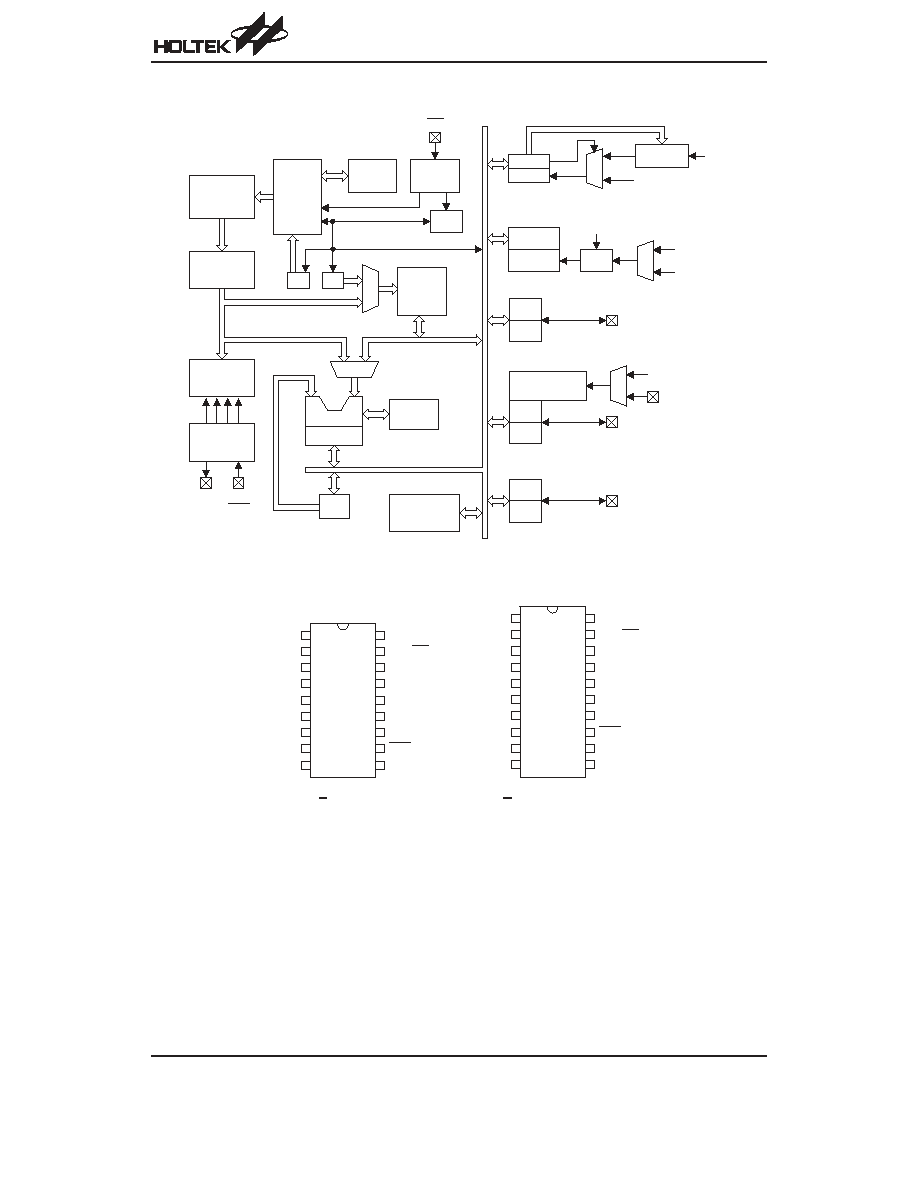

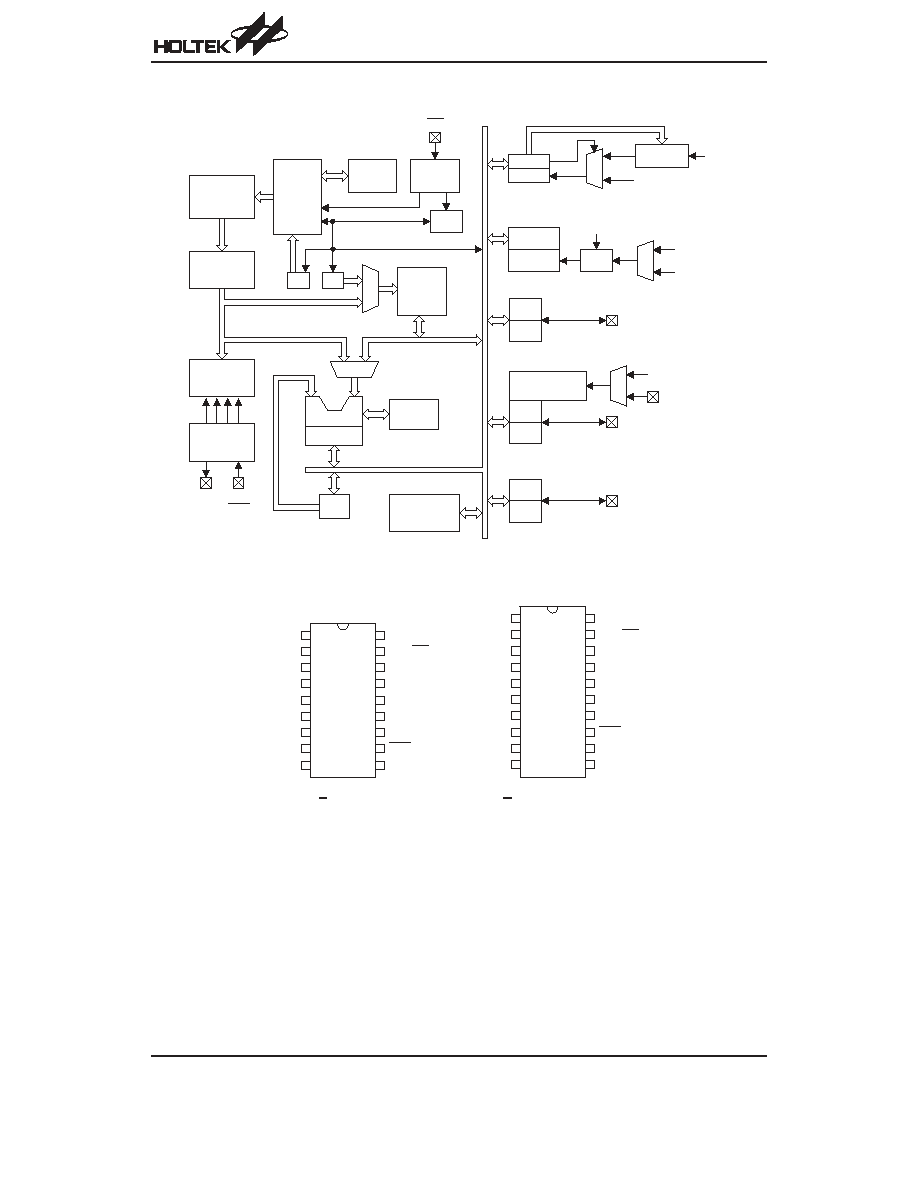

Block Diagram

Pin Assignment

HT46R51/HT46R52

Rev. 1.40

2

July 12, 2005

O S C 2 O S C 1

R E S

V D D

M U X

V S S

P r o g r a m

R O M

P r o g r a m

C o u n t e r

I n t e r r u p t

C i r c u i t

I N T C

D A T A

M e m o r y

I n s t r u c t i o n

R e g i s t e r

M

U

X

I n s t r u c t i o n

D e c o d e r

S T A T U S

A L U

S h i f t e r

T i m i n g

G e n e r a t o r

A C C

M P

B P

M

U

X

f

S Y S

P r e s c a l e r

T M R

T M R C

T M R

M

U

X

W D T O S C

W D T

f

S Y S

/ 4

W D T S

W D T

P r e s c a l e r

E N / D I S

P o r t A

P A

P A C

P A 0 ~ P A 2 , P A 3 / P F D

P A 4 / T M R , P A 5 / I N T

P A 6 ~ P A 7

M

U

X

V R E F

V D D

P o r t B

P B

P B C

P B 0 / A N 0 ~ P B 4 / A N 4

A / D C o n v e r t e r

P o r t D

P D

P D C

P D 0 / P W M

O p t i o n R O M

O T P O n l y

I N T

S T A C K

H T 4 6 R 5 1 / H T 4 R 5 2

1 8 D I P - A

P A 4 / T M R

P A 5 / I N T

P A 6

P A 7

O S C 2

O S C 1

V D D

R E S

P B 3 / A N 3

P A 3 / P F D

P A 2

P A 1

P A 0

P D 0 / P W M

P B 2 / A N 2

P B 1 / A N 1

P B 0 / A N 0

V S S

1 8

1 7

1 6

1 5

1 4

1 3

1 2

1 1

1 0

1

2

3

4

5

6

7

8

9

2 0

1 9

1 8

1 7

1 6

1 5

1 4

1 3

1 2

1 1

1

2

3

4

5

6

7

8

9

1 0

H T 4 6 R 5 1 / H T 4 R 5 2

2 0 S O P - A / S S O P - A

P A 4 / T M R

P A 5 / I N T

P A 6

P A 7

O S C 2

O S C 1

V D D

R E S

P B 4 / A N 4

P A 3 / P F D

P A 2

P A 1

P A 0

P D 0 / P W M

P B 2 / A N 2

P B 1 / A N 1

P B 0 / A N 0

V S S

V R E F

P B 3 / A N 3

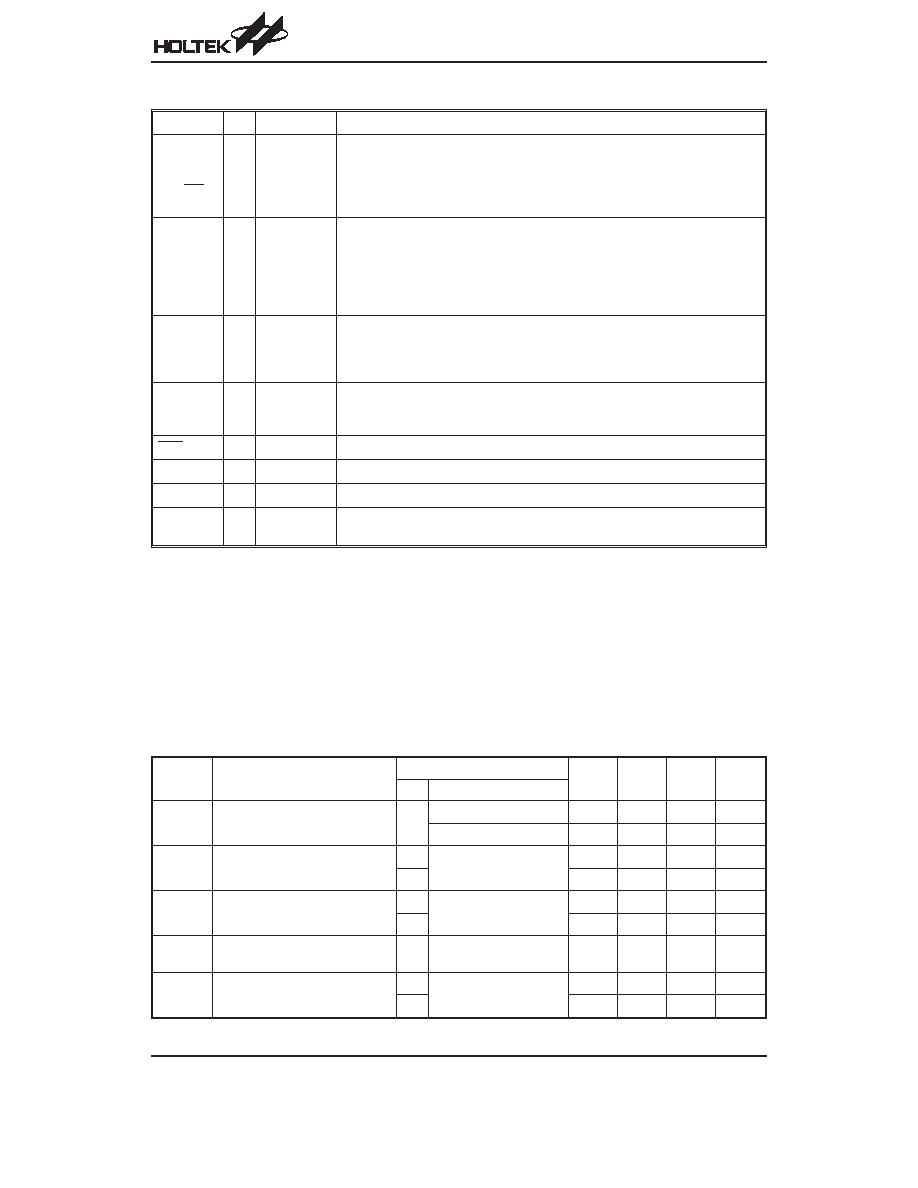

Pin Description

Pin Name

I/O

Options

Description

PA0~PA2

PA3/PFD

PA4/TMR

PA5/INT

PA6~PA7

I/O

Pull-high

Wake-up

PA3 or PFD

Bidirectional 8-bit input/output port. Each individual bit on this port can be config-

ured as a wake-up input by configuration option. Software instructions determine

if the pin is a CMOS output or Schmitt trigger input. Configuration options deter-

mine which pins on this port have pull-high resistors. The PFD, TMR and external

interrupt input are pin-shared with PA3, PA4, and PA5 respectively.

PB0/AN0

PB1/AN1

PB2/AN2

PB3/AN3

PB4/AN4

I/O

Pull-high

Bidirectional 5-bit input/output port. Software instructions determine the CMOS

output or Schmitt trigger input with or without pull-high resistor. Configuration op-

tions determine which pins on this port have pull-high resistors. PB is pin-shared

with the A/D input pins. The A/D inputs are selected via software instructions

Once selected as an A/D input, the I/O function and pull-high resistor functions

are disabled automatically.

PD0/PWM

I/O

Pull-high

PD0 or PWM

Bidirectional 1-bit input/output port. Software instructions determine the CMOS

output or Schmitt trigger input with or without pull-high resistor. One configuration

option determines which pin on this port has pull-high resistor. PD0 is pin-shared

with the PWM output selected via configuration option.

OSC1

OSC2

I

O

Crystal or RC

OSC1, OSC2 are connected to an external RC network or external crystal (deter-

mined by configuration option) for the internal system clock. For external RC sys-

tem clock operation, OSC2 is an output pin for 1/4 system clock.

RES

I

¾

Schmitt trigger reset input, active low

VDD

¾

¾

Positive power supply

VSS

¾

¾

Negative power supply, ground

VREF

I

¾

A/D Converter Reference Input voltage pins. Connect this pin to the desired A/D

reference voltage. The VREF pin is connected to V

DD

for the 18-pin DIP package

Absolute Maximum Ratings

Supply Voltage ...........................V

SS

-0.3V to V

SS

+6.0V

Storage Temperature ............................

-50°C to 125°C

Input Voltage..............................V

SS

-0.3V to V

DD

+0.3V

Operating Temperature...........................

-40°C to 85°C

Note: These are stress ratings only. Stresses exceeding the range specified under

²Absolute Maximum Ratings² may

cause substantial damage to the device. Functional operation of this device at other conditions beyond those

listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliabil-

ity.

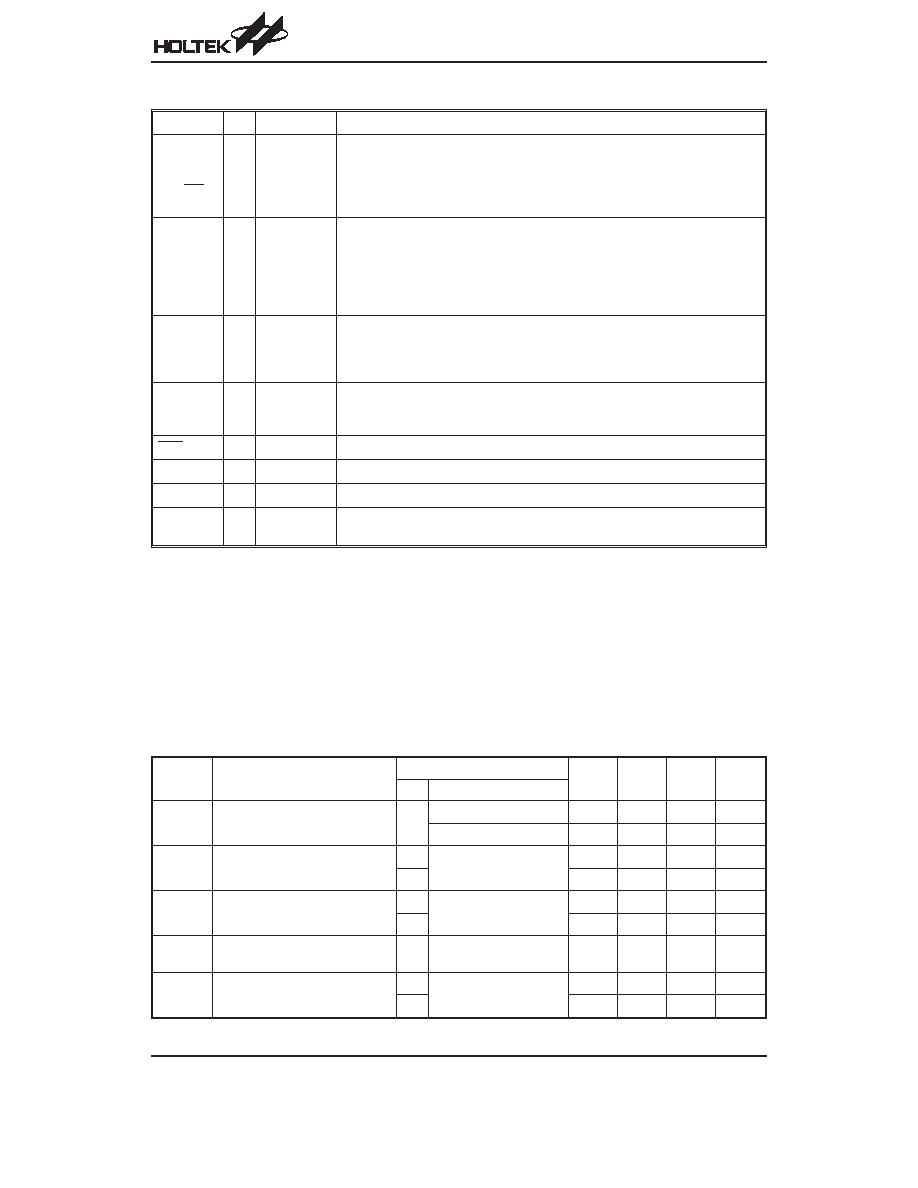

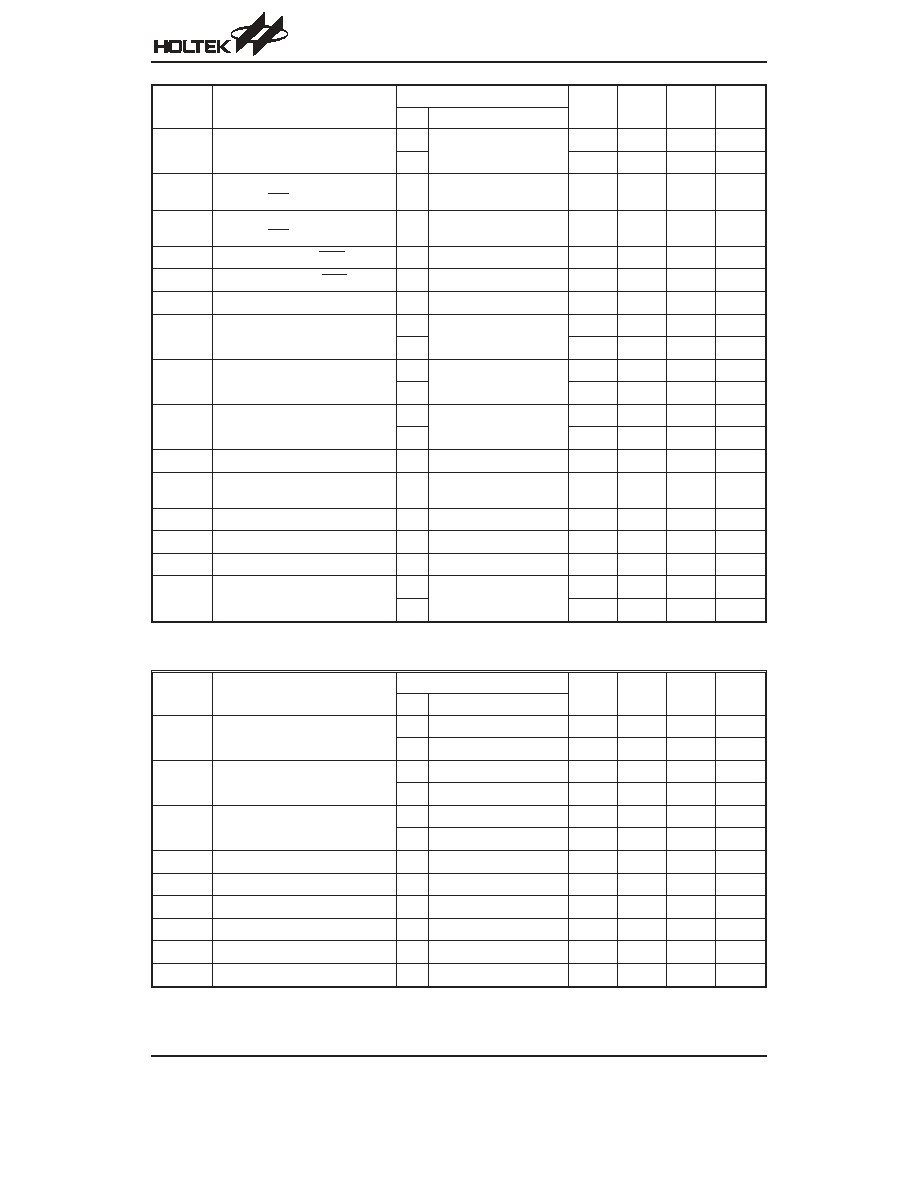

D.C. Characteristics

Ta=25

°C

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

DD

Conditions

V

DD

Operating Voltage

¾

f

SYS

=4MHz

2.2

¾

5.5

V

f

SYS

=8MHz

3.3

¾

5.5

V

I

DD1

Operating Current (Crystal OSC)

3V

No load, f

SYS

=4MHz

ADC disabled

¾

0.6

1.5

mA

5V

¾

2

4

mA

I

DD2

Operating Current (RC OSC)

3V

No load, f

SYS

=4MHz

ADC disabled

¾

0.8

1.5

mA

5V

¾

2.5

4

mA

I

DD3

Operating Current

5V

No load, f

SYS

=8MHz

ADC disabled

¾

4

8

mA

I

STB1

Standby Current (WDT Enabled)

3V

No load, system HALT

¾

¾

5

mA

5V

¾

¾

10

mA

HT46R51/HT46R52

Rev. 1.40

3

July 12, 2005

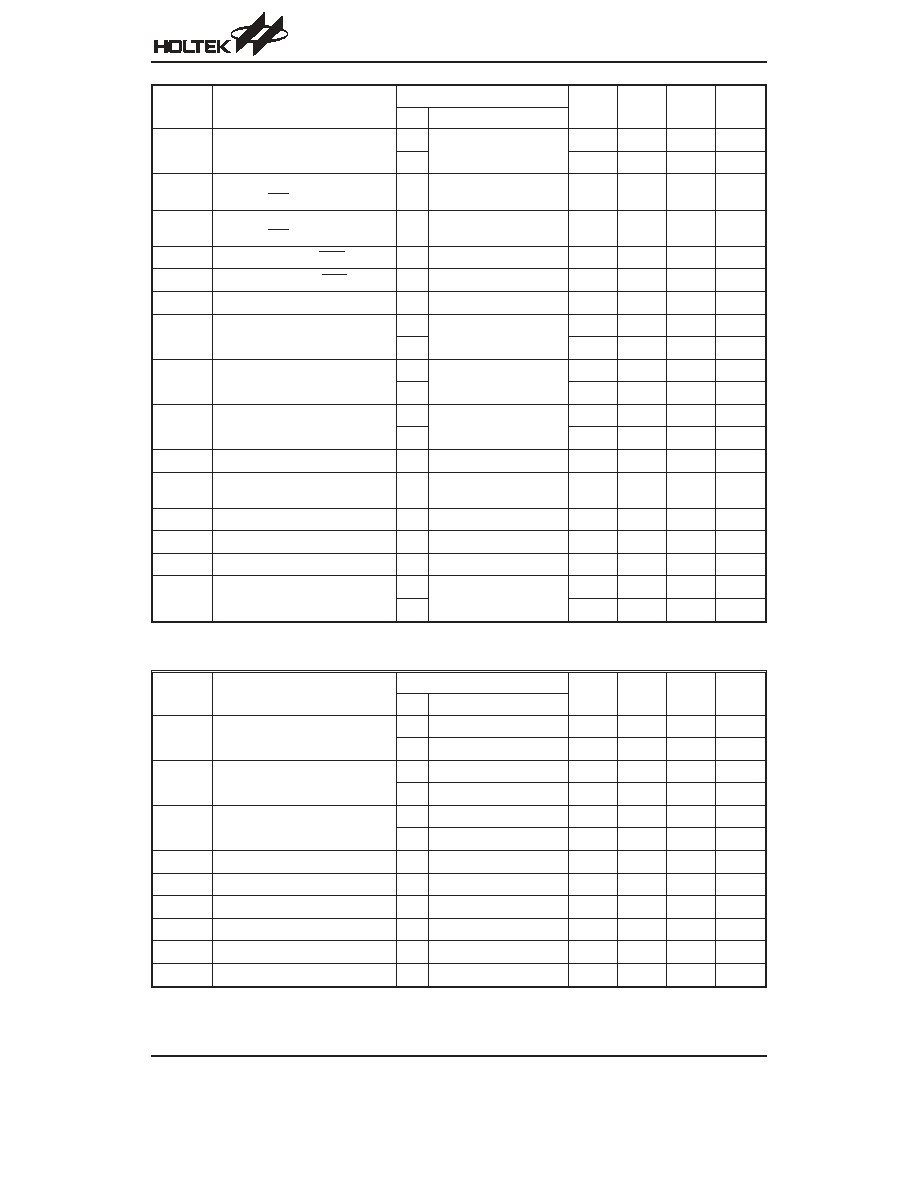

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

DD

Conditions

I

STB2

Standby Current

(WDT & AD Disabled)

3V

No load, system HALT

¾

¾

1

mA

5V

¾

¾

2

mA

V

IL1

Input Low Voltage for I/O Ports,

TMR and INT

¾

¾

0

¾

0.3V

DD

V

V

IH1

Input High Voltage for I/O Ports,

TMR and INT

¾

¾

0.7V

DD

¾

V

DD

V

V

IL2

Input Low Voltage (RES)

¾

¾

0

¾

0.4V

DD

V

V

IH2

Input High Voltage (RES)

¾

¾

0.9V

DD

¾

V

DD

V

V

LVR

Low Voltage Reset Voltage

¾ Configuration option: 3V

2.7

3

3.3

V

I

OL

I/O Port Sink Current

3V

V

OL

=0.1V

DD

4

8

¾

mA

5V

10

20

¾

mA

I

OH

I/O Port Source Current

3V

V

OH

=0.9V

DD

-2

-4

¾

mA

5V

-5

-10

¾

mA

R

PH

Pull-high Resistance of I/O Ports

3V

¾

20

60

100

k

W

5V

10

30

50

k

W

V

AD

A/D Input Voltage

¾

¾

0

¾

V

REF

V

V

REF

ADC Input Reference Voltage

Range

¾

¾

1.2

¾

VDD

V

DNL

ADC Differential Non-Linear

¾

¾

¾

¾

±2

LSB

INL

ADC Integral Non-Linear

¾

¾

¾

±2.5

±4

LSB

RESOLU Resolution

¾

¾

¾

¾

12

Bits

I

ADC

Additional Power Consumption

if A/D Converter is Used

3V

¾

¾

0.5

1

mA

5V

¾

1.5

3

mA

A.C. Characteristics

Ta=25

°C

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

DD

Conditions

f

SYS

System Clock (Crystal OSC)

¾ 2.2V~5.5V

400

¾

4000

kHz

¾ 3.3V~5.5V

400

¾

8000

kHz

f

TIMER

Timer I/P Frequency (TMR)

¾ 2.2V~5.5V

0

¾

4000

kHz

¾ 3.3V~5.5V

0

¾

8000

kHz

t

WDTOSC

Watchdog Oscillator Period

3V

¾

45

90

180

ms

5V

¾

32

65

130

ms

t

RES

External Reset Low Pulse Width

¾

¾

1

¾

¾

ms

t

SST

System Start-up Timer Period

¾ Wake-up from HALT

¾

1024

¾

t

SYS

t

INT

Interrupt Pulse Width

¾

¾

1

¾

¾

ms

t

AD

A/D Clock Period

¾

¾

1

¾

¾

ms

t

ADC

A/D Conversion Time

¾

¾

¾

80

¾

t

AD

t

ADCS

A/D Sampling Time

¾

¾

¾

32

¾

t

AD

Note: t

SYS

=1/f

SYS

HT46R51/HT46R52

Rev. 1.40

4

July 12, 2005

HT46R51/HT46R52

Rev. 1.40

5

July 12, 2005

Functional Description

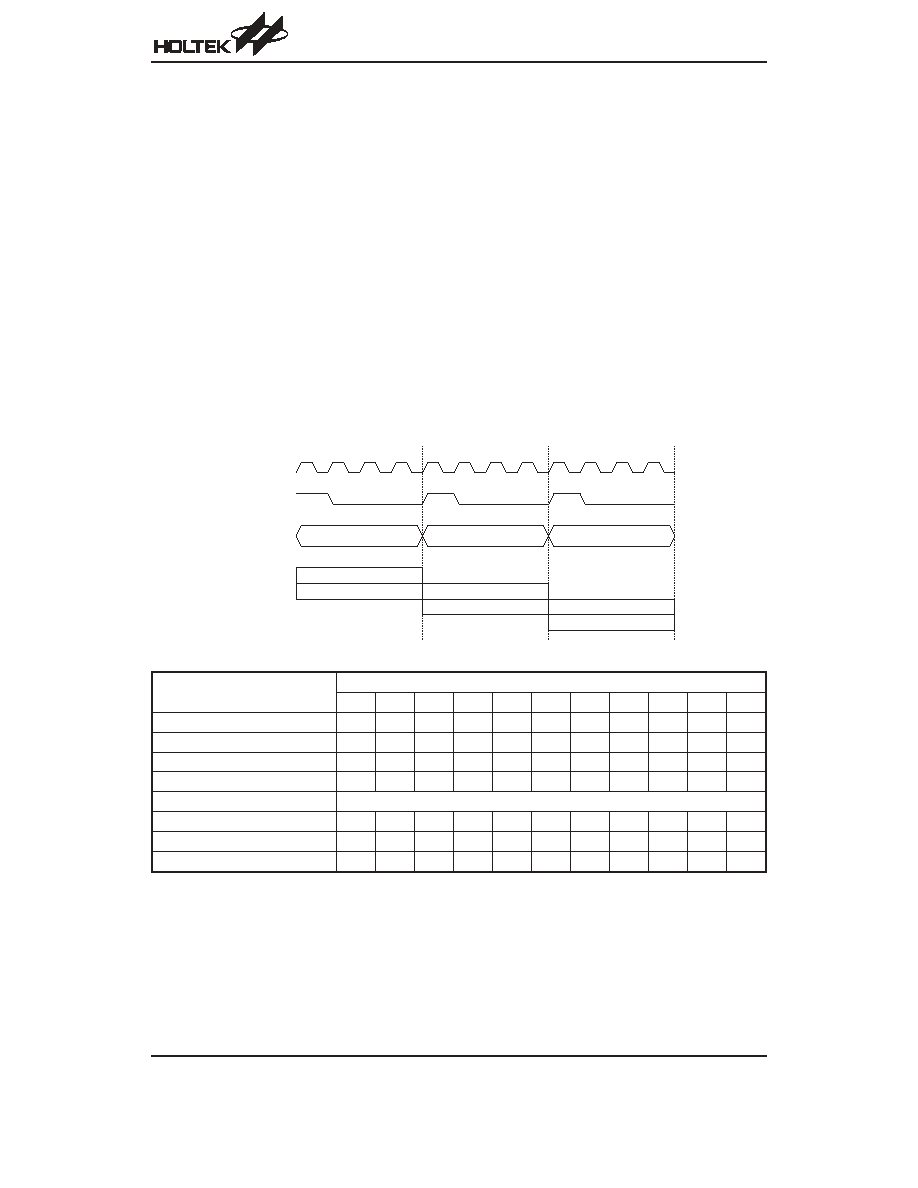

Execution Flow

The system clock for the microcontroller is derived from

either a crystal or an RC oscillator. The system clock is

internally divided into four non-overlapping clocks. One

instruction cycle consists of 4 system clock cycles.

Instruction fetching and execution are pipelined in such

a way that a fetch and decoding takes an instruction cy-

cle while execution take the next instruction cycle. The

pipelining scheme causes each instruction to effectively

execute in a cycle. If an instruction changes the program

counter, two cycles are required to complete the instruc-

tion.

Program Counter

- PC

For HT46R51, the program counter (PC) is 10 bits wide

and controls the sequence in which the instructions

stored in the program ROM are executed. The contents

of the PC can specify a maximum of 1024 addresses.

For HT46R52, the program counter (PC) is 11 bits wide

and controls the sequence in which the instructions

stored in the program ROM are executed. The contents

of the PC can specify a maximum of 2048 addresses.

After accessing a program memory word to fetch an in-

struction code, the contents of the program counter are

incremented by one. The program counter then points to

the memory word containing the next instruction code.

When executing a jump instruction, conditional skip ex-

ecution, loading register, subroutine call or return from

subroutine, initial reset, internal interrupt, external inter-

rupt or return from interrupts, the PC manipulates the

program transfer by loading the address corresponding

to each instruction.

The conditional skip is activated by instructions. Once

the condition is met, the next instruction, fetched during

the current instruction execution, is discarded and a

dummy cycle replaces it to get the proper instruction.

Otherwise proceed to the next instruction.

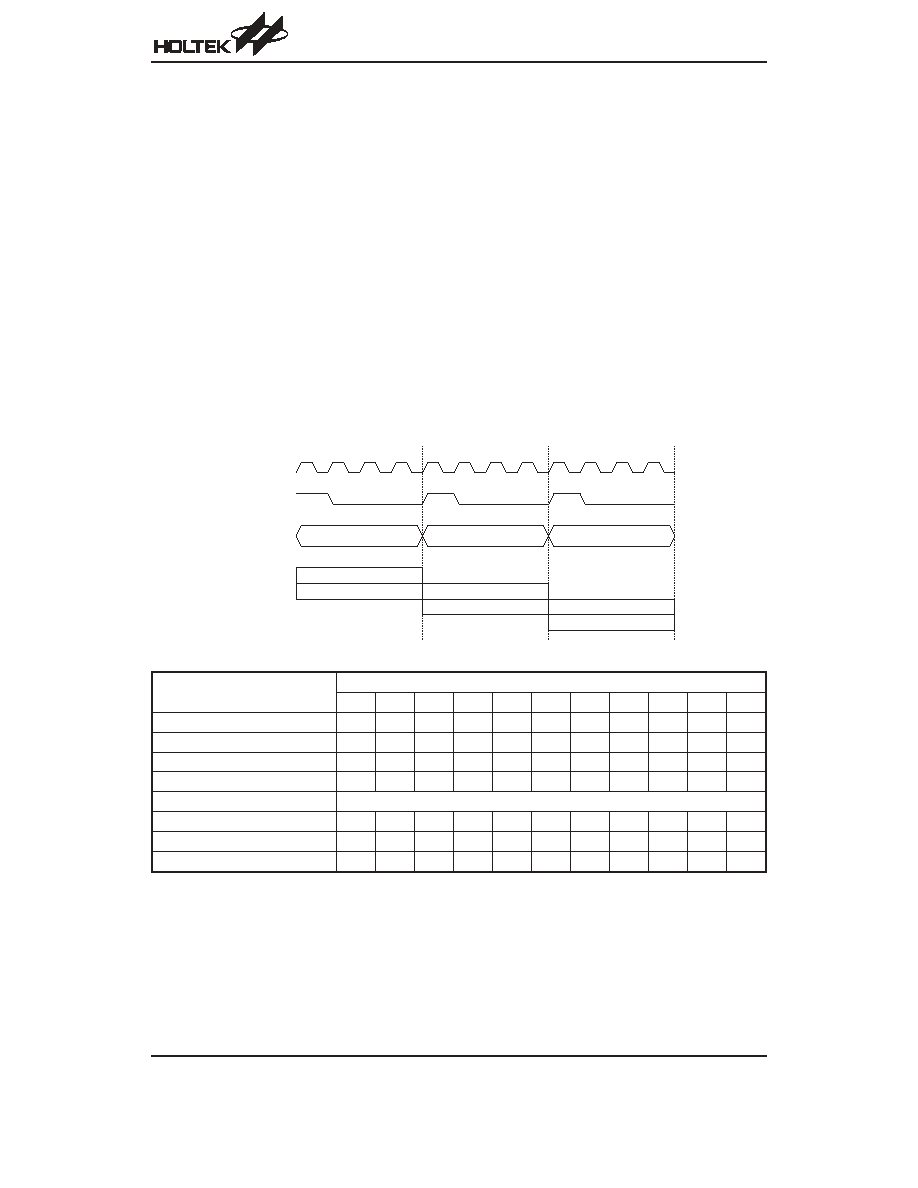

T 1

T 2

T 3

T 4

T 1

T 2

T 3

T 4

T 1

T 2

T 3

T 4

F e t c h I N S T ( P C )

E x e c u t e I N S T ( P C - 1 )

F e t c h I N S T ( P C + 1 )

E x e c u t e I N S T ( P C )

F e t c h I N S T ( P C + 2 )

E x e c u t e I N S T ( P C + 1 )

P C

P C + 1

P C + 2

S y s t e m C l o c k

O S C 2 ( R C o n l y )

P C

Execution Flow

Mode

Program Counter

*b10

*b9

*b8

*b7

*b6

*b5

*b4

*b3

*b2

*b1

*b0

Initial Reset

0

0

0

0

0

0

0

0

0

0

0

External Interrupt

0

0

0

0

0

0

0

0

1

0

0

Timer/Event Counter Overflow

0

0

0

0

0

0

0

1

0

0

0

A/D Converter Interrupt

0

0

0

0

0

0

0

1

1

0

0

Skip

Program Counter+2

Loading PCL

PC10

PC9

PC8

@7

@6

@5

@4

@3

@2

@1

@0

Jump, Call Branch

#10

#9

#8

#7

#6

#5

#4

#3

#2

#1

#0

Return from Subroutine

S10

S9

S8

S7

S6

S5

S4

S3

S2

S1

S0

Program Counter

Note:

*b10~*b0: Program counter bits

S10~S0: Stack register bits

#10~#0: Instruction code bits

@7~@0: PCL bits, PC10~PC8: Original PC counter, remain unchanged

For the HT46R51, since the program counter is 10 bits wide (b0~b9), the b10 columns in the table are not ap-

plicable.

For the HT46R52, since the program counter is 11 bits wide (b0~b10)

Document Outline

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ

- þÿ