| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HT9302A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

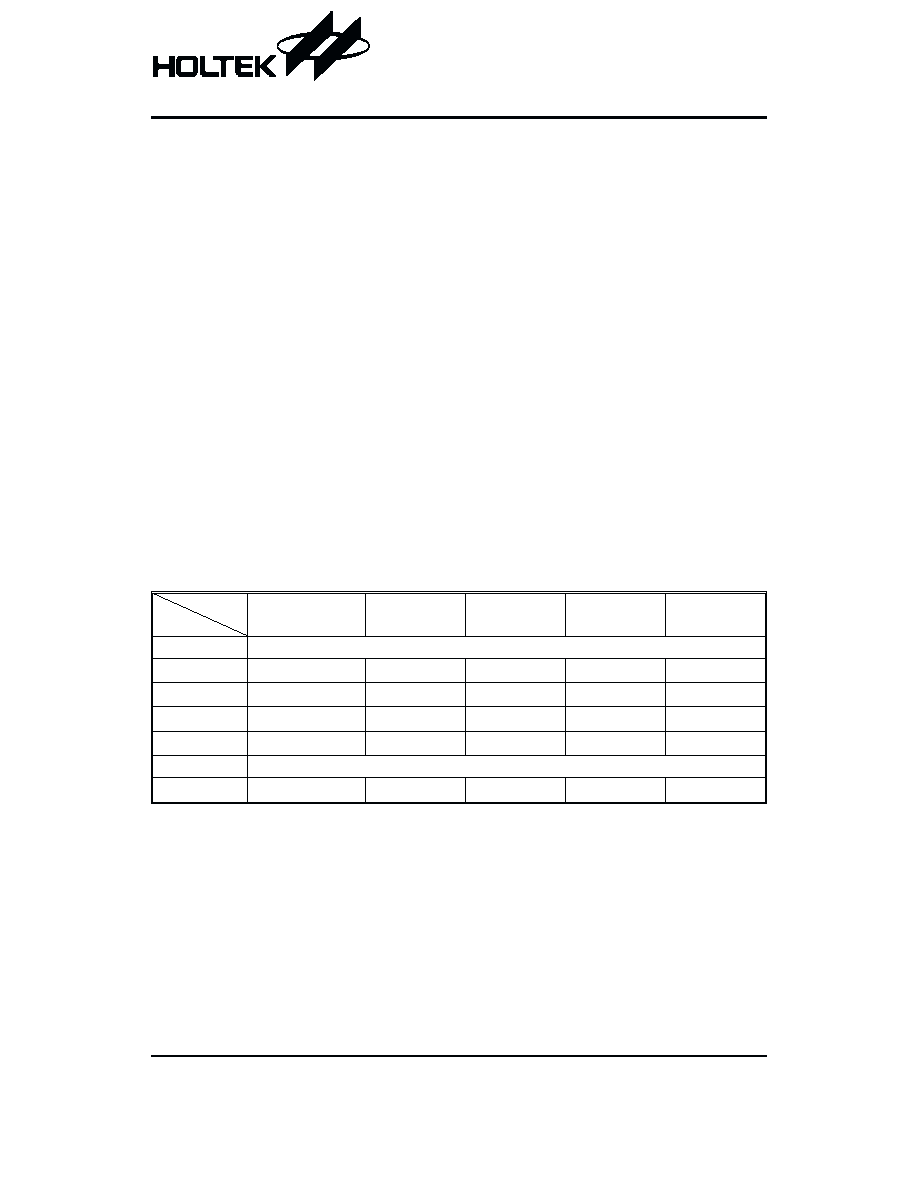

HT9302 Series

1-Memory/2-Memory Tone/Pulse Dialer

Selection Table

Function

Part No.

Lock Function

(Pin Selection)

Hold Line

Hand Free

LCD Interface

Package

HT9302x

(Normal version)

HT9302A

÷

æ

æ

æ

18 DIP

HT9302B

÷

÷

÷

æ

22 SKDIP

HT9302C

÷

æ

æ

÷

20 DIP

HT9302D

÷

÷

÷

÷

24 SKDIP

HT9302G

(Simple version)

HT9302G

æ

æ

æ

æ

16 DIP

Rev. 1.20

1

September 30, 2002

Features

∑

Universal specification

∑

Operating voltage: 2.0V~5.5V

∑

Low standby current

∑

Low memory retention current: 0.1

mA (typ.)

∑

Tone/pulse switchable

∑

Interface with LCD driver

∑

32 digits for redialing

∑

32 digits for SA memory dialing

∑

One-key redialing

∑

Pause and P

ÆT key for PBX

∑

4

¥4 keyboard matrix

∑

3.58MHz crystal or ceramic resonator

∑

Hand-free control

∑

Hold-line control

∑

Pause, P

ÆT can be saved for redialing

∑

Lock function

∑

Resistor options

-

M/B ratio

-

Flash function and flash time

-

Pause and P

ÆT duration

-

Pulse number

∑

HT9302A: 18-pin DIP package

HT9302B: 22-pin SKDIP package

HT9302C: 20-pin DIP package

HT9302D: 24-pin SKDIP package

HT9302G: 16-pin DIP package

General Description

The HT9302 series tone/pulse dialers are CMOS LSIs

for telecommunication systems. They are designed to

meet various dialing specifications through resistor op-

tion matrix.

The HT9302 series provide the pin-selected lock func-

tion, Hold-line, Hand-free and LCD dialing number

display interface, all of which are suitable for feature

phone applications. HT9302G is simpler than HT9302X

version. It provides only a redialing memory for simple

low-cost system applications.

Patent Number: 64097, 86474, 64529, 113235 (R.O.C.)

5424740 (U.S.A.)

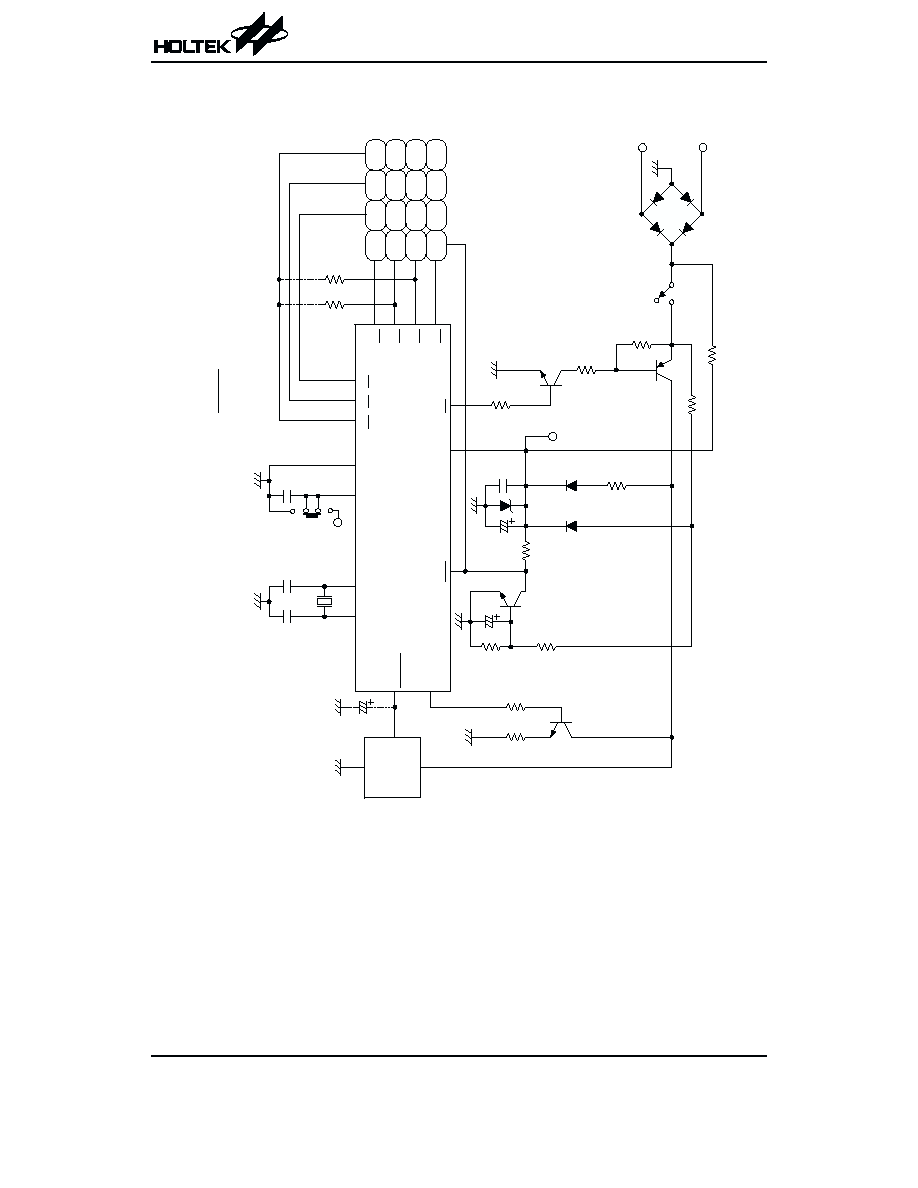

Block Diagram

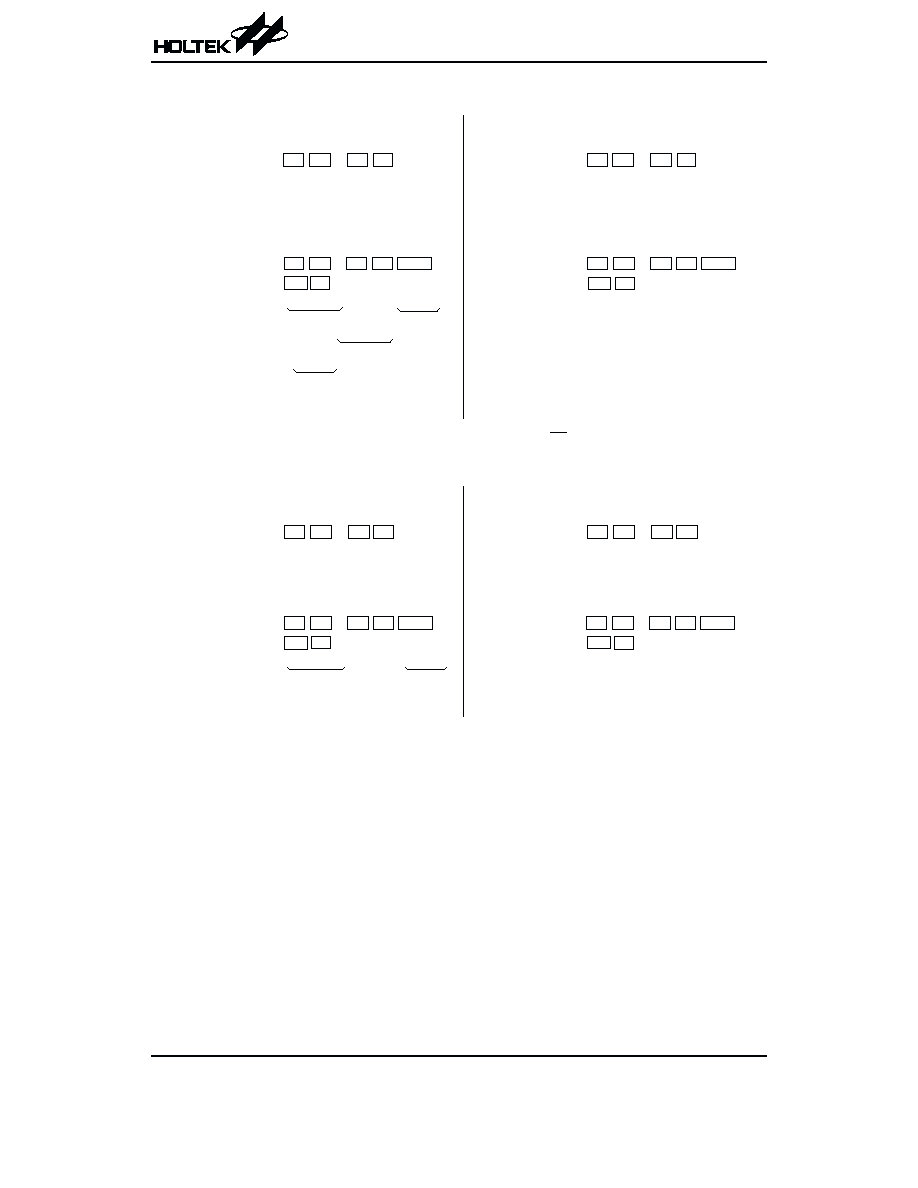

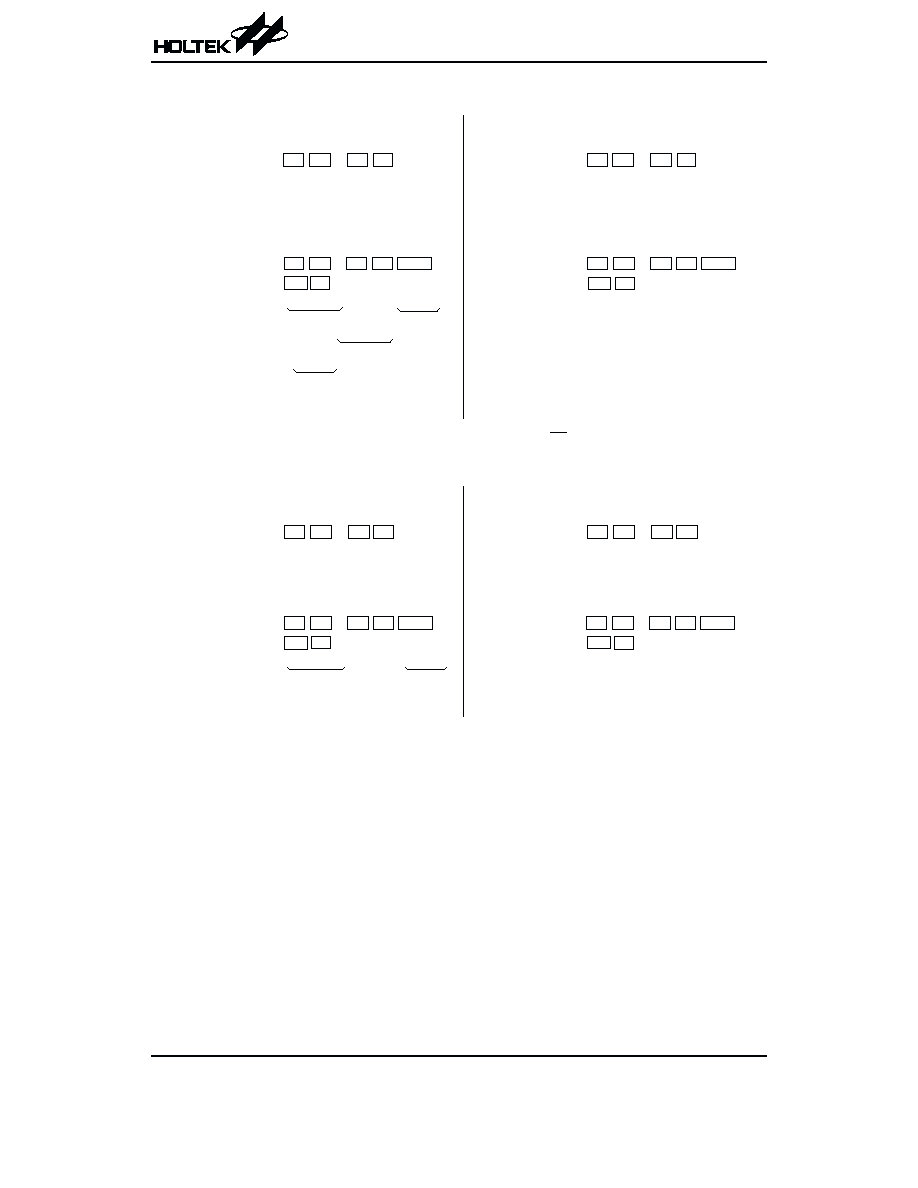

Pin Assignment

HT9302x normal version

HT9302G simple version

HT9302 Series

Rev. 1.20

2

September 30, 2002

C 1

R 1

P O

H K S

H D I

K e y

C o l u m n

. S M

K e y

. u n c t i o n

E n c o d e r

E n c o d e r

C o n t r o l

W R M

C o u n t e r

A D D R L

K e y R o w

S R A M

D e b o u n c e

D i v i d e r

C l o c k

G e n e r a t o r

M / B

. l a s h

T i m e r

C h e c k

T o n e

E n c o d e r

C o n v e r t e r

T o n e

O u t

P u l s e

O u t

D T M .

H . I

M O D E

D O U T

C L O C K

X M U T E

C 4

R 4

X 1

X 2

K e y t o n e

G e n e r a t o r

C l o c k

C o n t r o l

L O C K

M o d e I n

H D / H .

H D O

H . O

R 4

R 3

R 2

R 1

M O D E

D T M .

P O

H K S

1 6

1 5

1 4

1 3

1 2

1 1

1 0

9

1

2

3

4

5

6

7

8

C 1

C 2

C 3

X 1

X 2

X M U T E

V S S

V D D

H T 9 3 0 2 G

1 6 D I P - A

H D I

C 1

C 2

C 3

C 4

L O C K

X 1

X 2

X M U T E

V S S

H . I

D O U T

C 1

C 2

C 3

C 4

L O C K

X 1

X 2

X M U T E

V S S

1 8

1 7

1 6

1 5

1 4

1 3

1 2

1 1

1 0

1

2

3

4

5

6

7

8

9

R 4

R 3

R 2

R 1

M O D E

D T M .

P O

H K S

V D D

H D I

C 1

C 2

C 3

C 4

L O C K

X 1

X 2

X M U T E

V S S

H . I

2 2

2 1

2 0

1 9

1 8

1 7

1 6

1 5

1 4

1 3

1 2

1

2

3

4

5

6

7

8

9

1 0

1 1

H D O

R 4

R 3

R 2

R 1

M O D E

D T M .

P O

H K S

V D D

H . O

C 1

C 2

C 3

C 4

L O C K

X 1

X 2

X M U T E

V S S

D O U T

2 0

1 9

1 8

1 7

1 6

1 5

1 4

1 3

1 2

1 1

1

2

3

4

5

6

7

8

9

1 0

R 4

R 3

R 2

R 1

M O D E

D T M .

P O

H K S

V D D

C L O C K

2 4

2 3

2 2

2 1

2 0

1 9

1 8

1 7

1 6

1 5

1 4

1 3

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

H D O

R 4

R 3

R 2

R 1

M O D E

D T M .

P O

H K S

V D D

H . O

C L O C K

H T 9 3 0 2 D

2 4 S K D I P - A

H T 9 3 0 2 C

2 0 D I P - A

H T 9 3 0 2 B

2 2 S K D I P - A

H T 9 3 0 2 A

1 8 D I P - A

Keyboard Information

Pin Description

Pin Name

I/O

Internal

Connection

Description

C1~C4

R1~R4

I/O

CMOS IN/OUT

These pins form a 4

¥4 keyboard matrix which can perform keyboard input detec-

tion and dialing specification setting functions. When on-hook (HKS=high) all the

pins are set high. While off-hook the column group (C1~C4) remains low and the

row group (R1~R4) is set high for key input detection.

An inexpensive single contact 4

¥4 keyboard can be used as an input device.

Pressing a key connects a single column to a single row, and actuates the system

oscillator that results in a dialing signal output. If more than two keys are pressed at

the same time, no response occurs. The key-in debounce time is 20ms. Refer to

the keyboard information for keyboard arrangement and to the functional descrip-

tion for dialing specification selection.

X1

I

OSCILLATOR

The system oscillator consists of an inverter, a bias resistor and the necessary

load capacitor on chip. Connecting a standard 3.579545MHz crystal or ceramic

resonator to the X1 and X2 terminals can implement the oscillator function. The

oscillator is turned off in the standby mode, and is actuated whenever a key-

board entry is detected.

X2

O

XMUTE

O

NMOS OUT

XMUTE is an NMOS open drain structure pulled to VSS during dialing signal

transmission. Otherwise, it is an open circuit. The XMUTE is used to mute the

speech circuit when transmitting the dial signal.

HKS

I

CMOS IN

This pin is used to monitor the status of the hook-switch and its combination

with HFI/HDI can control the PO pin output to make or break the line.

HKS=VDD: On-hook state (PO=low). Except for HFI/HDI

(hand-free/hold-line control input), other functions are all disabled.

HKS=VSS: Off-hook state (PO=high). The chip is in the standby mode and

ready to receive the key input.

PO

O

CMOS OUT

This pin is a CMOS output structure, which by receiving HKS and HFO/HDO

signals, control the dialer to connect or disconnect the telephone line.

PO outputs a low to break the line when HKS is high (on-hook) and HFO/HDO

is low. PO outputs a high to make the line when HKS is low (off-hook) or HFO is

high or HDO is high.

During the off-hook state, the pin also outputs the dialing pulse train in pulse

mode dialing. While in the tone mode, this pin is always high.

MODE

I/O

CMOS IN/OUT

This is a three-state input/output pin, used for dialing mode selection whether

Tone mode or Pulse mode; 10pps/20pps.

MODE=VDD: Pulse mode, 10pps

MODE=OPEN: Pulse mode, 20pps

MODE=VSS: Tone mode

During pulse mode dialing, switching this pin to the tone mode changes the

subsequent digit entry to tone mode. When the chips are in tone mode, switch-

ing to the pulse mode will also be recognized.

HT9302 Series

Rev. 1.20

3

September 30, 2002

H T 9 3 0 2 A / B / C / D

1

4

7

* / T

2

5

8

0

3

6

9

#

S A

.

P

R

R 4

R 3

R 2

R 1

C 4

C 1

C 2

C 3

H K S

H T 9 3 0 2 G

1

4

7

* / T

2

5

8

0

3

6

9

#

.

P

R

R 4

R 3

R 2

R 1

C 1

C 2

C 3

Pin Name

I/O

Internal

Connection

Description

DTMF

O

CMOS OUT

This pin is active only when the chip transmits tone dialing signals. Otherwise, it

always outputs a low. The pin outputs tone signals to drive the external trans-

mitter amplifier circuit. The load resistor should not be less than 5k

W.

HDI

I

CMOS IN

Pull-high

This pin is a Schmitt trigger input structure. Active low. Applying a negative go-

ing pulse to this pin can toggle the HDO output once.

An external RC network is recommended for input debouncing. The Pull-high

resistance is 200k

W typ.

HDO

O

CMOS OUT

The HDO is a CMOS output structure. Its output is toggle- controlled by a nega-

tive transition on HDI. When HDO is toggled high, PO keeps high to hold the

line. The hold function can be released by setting HFO high or by an on-off hook

operation or by another HDI input. Refer to the functional description for the

hold-line function.

HFI

I

CMOS IN

Pull-low

This pin is a Schmitt trigger input structure. Active high. Applying a positive go-

ing pulse to HFI can toggle the HFO once and hence control the hand-free func-

tion. The Pull-low resistance of HFI is 200k

W typ.

An external RC network is recommended for input debouncing.

HFO

O

CMOS OUT

The HFO is a CMOS output structure. Its output is toggle- controlled by a posi-

tive transition on HFI pin. When HFO is high, the hand-free function is enabled

and PO outputs a high to connect the line.

The hand-free function can be released by setting HDO high or by an on-off-hook

operation or by another HFI input. Refer to the functional description for the

hand-free functional operation.

LOCK

I/O

CMOS IN/OUT

This is a three-state input/output pin, used for controlling long distance call

function with a lock-switch.

LOCK=OPEN: Normal dialing (no lock)

LOCK=VDD:

≤0, 9≤ is inhibited for use as the first key input

LOCK=VSS:

≤0≤ is inhibited for use as the first key input

DOUT

O

NMOS OUT

NMOS open drain output pin. It outputs the BCD code of the dialing digits to the

LCD driver chip (HT16XX series) or MCU for dialing number display. Refer to

the functional description for the detailed timing.

CLOCK

O

NMOS OUT

NMOS open drain output. When dialing, it outputs a series of pulse trains for

DOUT data synchronization. DOUT data is valid at the falling edge of clock.

VDD

æ

æ

Positive power supply, 2.0V~5.5V for normal operation

VSS

æ

æ

Negative power supply, ground

Approximate internal connection circuits

HT9302 Series

Rev. 1.20

4

September 30, 2002

N M O S O U T

V

D D

C M O S I N / O U T

C M O S I N

P u l l - l o w

C M O S I N

P u l l - h i g h

C M O S I N

O S C I L L A T O R

X 1

X 2

1 0 M W

2 0 p .

1 0 p .

C M O S O U T

V

D D

V

D D

Absolute Maximum Ratings

Supply Voltage ...........................................

-0.3V to 6V

Storage Temperature ...........................

-50∞C to 125∞C

Input Voltage .............................. V

SS

-0.3 to V

DD

+0.3V

Operating Temperature ..........................

-20∞C to 75∞C

Note: These are stress ratings only. Stresses exceeding the range specified under

≤Absolute Maximum Ratings≤ may

cause substantial damage to the device. Functional operation of this device at other conditions beyond those

listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliabil-

ity.

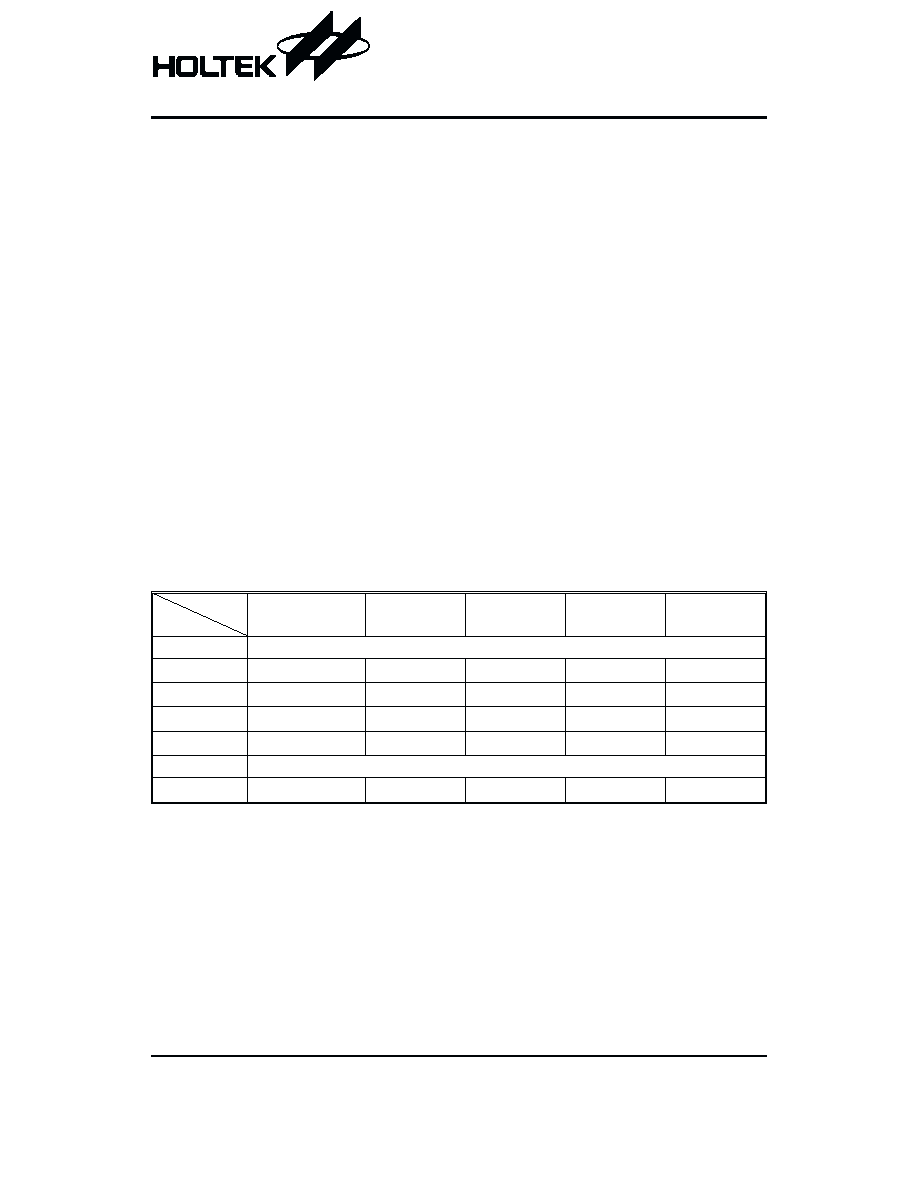

Electrical Characteristics

f

OSC

=3.5795MHz, Ta=25

∞C

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

DD

Conditions

V

DD

Operating Voltage

æ

æ

2

æ

5.5

V

I

DD

Operating Current

2.5V

Pulse

Off-hook

Keypad entry

No load

æ

0.2

1

mA

Tone

æ

0.6

2

mA

I

STB

Standby Current

1V

On-hook, no load

No entry

æ

æ

1

mA

V

R

Memory Retention Voltage

æ

æ

1

æ

5.5

V

I

R

Memory Retention Current

1V

On-hook

æ

0.1

0.2

mA

V

IL

Input Low Voltage

æ

æ

V

SS

æ

0.2V

DD

V

V

IH

Input High Voltage

æ

æ

0.8V

DD

æ

V

DD

V

I

XMO

XMUTE Leakage Current

æ

V

XMUTE

=12V

No entry

æ

æ

1

mA

I

OLXM

XMUTE Sink Current

2.5V V

XMUTE

=0.5V

1

æ

æ

mA

I

HKS

HKS Pin Input Current

2.5V V

HKS

=2.5V

æ

æ

0.1

mA

R

HFI

HFI Pull-low Resistance

2.5V V

HFI

=2.5V

æ

200

æ

k

W

R

HDI

HDI Pull-high Resistance

2.5V V

HDI

=0V

æ

200

æ

k

W

I

OH1

Keypad Pin Source Current

2.5V V

OH

=0V

-4

æ

40

mA

I

OL1

Keypad Pin Sink Current

2.5V V

OL

=2.5V

200

400

æ

mA

I

OH2

HFO Pin Source Current

2.5V V

OH

=2V

-1

æ

æ

mA

I

OL2

HFO Pin Sink Current

2.5V V

OL

=0.5V

1

æ

æ

mA

I

OH3

HDO Pin Source Current

2.5V V

OH

=2V

-1

æ

æ

mA

I

OL3

HDO Pin Sink Current

2.5V V

OL

=0.5V

1

æ

æ

mA

t

FP

Pause Time After Flash

æ

Control key

æ

0.2

æ

s

Digit key

æ

1

æ

t

RP

One-key Redialing Pause Time

æ

One-key redialing

æ

1

æ

s

t

DB

Key-in Debounce Time

æ

æ

æ

20

æ

ms

t

BRK

Break Time for One-key Redialing

æ

One-key redialing

æ

1.2

æ

s

f

OSC

System Frequency

æ

Crystal=3.5795MHz

3.5759

3.5795

3.5831

MHz

HT9302 Series

Rev. 1.20

5

September 30, 2002

Pulse Mode Electrical Characteristics

f

OSC

=3.5795MHz, Ta=25

∞C

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

DD

Conditions

I

POH

PO Output Source Current 2.5V V

OH

=2V

-0.2

æ

æ

mA

I

POL

PO Output Sink Current

2.5V V

OL

=0.5V

0.2

0.6

æ

mA

PR

Pulse Rate

æ

MODE pin is connected to V

DD

æ

10

æ

pps

MODE pin is opened

æ

20

æ

M/B

Make/Break Ratio

æ

A resistor is linked between R2

and C1

æ

33:66

æ

%

No resistor is linked between

R2 and C1

æ

40:60

æ

t

PDP

Pre-digit-pause Time

æ

M/B ratio=40:60

æ

40 (10pps)

20 (20pps)

æ

ms

M/B ratio=33:66

æ

33 (10pps)

17 (20pps)

æ

t

IDP

Inter-digit-pause Time

æ

Pulse rate=10pps

æ

800

æ

ms

Pulse rate=20pps

æ

500

æ

t

M

Pulse Make Duration

æ

A resistor is linked between R2

and C1

æ

33 (10pps)

17 (20pps)

æ

ms

No resistor is linked between

R2 and C1

æ

40 (10pps)

20 (20pps)

æ

t

B

Pulse Break Duration

æ

A resistor is linked between R2

and C1

æ

66 (10pps)

33 (20pps)

æ

ms

No resistor is linked between

R2 and C1

æ

60 (10pps)

30 (20pps)

æ

Tone Mode Electrical Characteristics

f

OSC

=3.5795MHz, Ta=25

∞C

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

DD

Conditions

V

TDC

DTMF Output DC Level

æ

æ

0.45V

DD

æ

0.7V

DD

V

I

TOL

DTMF Sink Current

2.5V V

DTMF

=0.5V

0.1

æ

æ

mA

V

TAC

DTMF Output AC Level

æ Row group, R

L

=5k

W

0.12

0.155

0.18

Vrms

R

L

DTMF Output Load

2.5V THD

£-23dB

5

æ

æ

k

W

A

CR

Column Pre-emphasis

2.5V Row group=0dB

1

2

3

dB

THD

Tone Signal Distortion

2.5V R

L

=5k

W

æ

-30

-23

dB

t

TMIN

Minimum Tone Duration

æ Auto-redial

Others

æ

82.5

æ

ms

9302G

æ

100

æ

t

ITPM

Minimum Inter-tone Pause

æ Auto-redial

Others

æ

85.5

æ

ms

9302G

æ

106

æ

THD (Distortion) (dB) = 20 log

(

)

V1

V2

Vn /

Vi

Vh

2

2

2

2

2

+

+

+

K

Vi, Vh: Row group and column group signals

V1, V2, ... Vn: Harmonic signals (BW=300Hz~3500Hz)

HT9302 Series

Rev. 1.20

6

September 30, 2002

HT9302 Series

Rev. 1.20

7

September 30, 2002

Functional Description

Keyboard matrix

C1~C4 and R1~R4 form a keyboard matrix. Together

with a standard 4

¥4 keyboard, the keyboard matrix is

used for dialing entries. In addition, the keyboard ma-

trix provides resistor option for different dialing specifi-

cation selections. The keyboard arrangement for each of

the HT9302 series are shown in the Keyboard Informa-

tion.

Tone frequency

Tone

Name

Output Frequency (Hz)

% Error

Specified

Actual

R1

697

699

+0.29%

R2

770

766

-0.52%

R3

852

847

-0.59%

R4

941

948

+0.74%

C1

1209

1215

+0.50%

C2

1336

1332

-0.30%

C3

1477

1472

-0.34%

Note: % Error does not contain the crystal frequency

drift

Dialing specification selection

By means of adding resistors on the keyboard matrix

pins, various dialing specifications can be selected. The

allowable option resistor connections are shown.

All the resistors are 330k

W. The resistor option functions

and the default specifications (without option resistors)

are listed below.

Option

Resistor

Option

Function

Default

(No Resistor)

R

K12

Make/Break Ratio

Selection

40:60

R

K13

Flash Function and

Flash Time Selection

Flash=control function

Flash time=600ms

R

K14

R

K21

Pause & P

ÆT

Duration Selection

t

P

=3.6s

t

P

ÆT

=3.6s

R

K31

Pulse Number

Selection

N

R

K41

M/B ratio selection table

R

K12

M/B Ratio (%)

No

40:60

Yes

33.3:66.6

Flash function/time (duration) selection table

R

K13

R

K14

Flash

Function

Flash

Time (t

F

)

No

No

Control

600ms

No

Yes

Digit

600ms

Yes

No

Digit

98ms

Yes

Yes

Digit

300ms

Pause and P

ÆT duration selection table

R

K21

t

P

(sec)

t

P

ÆT

(sec)

No

3.6

3.6

Yes

2

1

Pulse number selection table

∑

This table shows pulse number selections for

HT9302x.

R

K31

R

K41

Pulse Number

No

No

N

No

Yes

N+1

Yes

No

10

-N

Yes

Yes

æ

∑

HT9302G has different selection method listed in the

table below.

R

K31

Pulse Number

No

N

Yes

10-N

C 4

C 3

C 2

C 1

R 4

R 3

R 1

R 2

K 2 1

R

K 3 1

R

K 4 1

R

K 1 2

R

K 1 3

R

K 1 4

R

HT9302 Series

Rev. 1.20

8

September 30, 2002

Pulse number table

Keypad

Output Pulse Number

Digit Key

Normal N

New

Zealand

(10

-N)

Sweden/

Denmark

(N+1)

1

1

9

2

2

2

8

3

3

3

7

4

4

4

6

5

5

5

5

6

6

6

4

7

7

7

3

8

8

8

2

9

9

9

1

10

0

10

10

1

*/T

P

ÆT

P

ÆT

P

ÆT

#

Ignored

Ignored

Ignored

Hand-free function operation

∑

Hand-free function execution

When HFO is low, a rising edge triggers the HFI, en-

abling the Hand-free function (HFO becomes high).

∑

Reset Hand-free function

When HFO is high, the Hand-free function is enabled

and can be reset by:

®

Off-hook

®

Applying a rising edge to HFI

®

Changing the HDO pin from low to high

∑

Hand-free function table

Hold-line function operation

∑

Hold-line function execution

When HDO is low, a falling edge triggers the HDI, en-

abling the Hold-line function (HDO becomes high).

The XMUTE remains low when HDO is high.

∑

Reset Hold-line function

When HDO is high, the Hold-line function is enabled

and can be reset by:

®

Off-hook

®

Applying a falling edge to HDI

®

Changing the HFO pin from low to high

∑

Hold-line function table

DOUT BCD code

When dialing, the corresponding 4-bit BCD codes are

serially presented on DOUT from MSB to LSB. The data

of DOUT is valid at the falling edge of the CLOCK pin.

The following table lists the BCD codes corresponding

to the keyboard input.

Key-In

BCD Code

Key-In

BCD Code

1

0001

8

1000

2

0010

9

1001

3

0011

0

1010

4

0100

*/T

1101

5

0101

#

1100

6

0110

F

1011

7

0111

P

1110

C u r r e n t S t a t e

I n p u t

N e x t S t a t e

H K S

H

H

H

H

L

L

L

L

X

H . O

L

L

H

X

L

L

H

X

X

H D O

X

X

X

L

X

X

L

X

L

H . I

L

L

L

L

L

H K S

A n

A n

A n

L

A n

A n

A n

H

A n

H . O

L

H

L

L

L

H

L

A n

L

H D O

A n

L

A n

L

A n

L

A n

A n

H

H D I

H

H

H

H

H

H

H

H

H :

L :

L o g i c H I G H

L o g i c L O W

X :

A n :

D o n ' t c a r e

U n c h a n g e d

:

:

R i s i n g e d g e

. a l l i n g e d g e

C u r r e n t S t a t e

I n p u t

N e x t S t a t e

H K S

H

H

H

H

L

L

L

L

X

H D O

L

L

H

X

L

L

H

X

X

H . O

X

X

L

X

X

X

L

X

L

H D I

H

H

H

H

H

H K S

A n

A n

A n

L

A n

A n

A n

H

A n

H D O

L

H

L

L

L

H

L

A n

L

H . O

A n

L

A n

L

A n

L

A n

A n

H

H . I

L

L

L

L

L

L

L

L

H :

L :

L o g i c H I G H

L o g i c L O W

X :

A n :

D o n ' t c a r e

U n c h a n g e d

:

:

R i s i n g e d g e

. a l l i n g e d g e

HT9302 Series

Rev. 1.20

9

September 30, 2002

LOCK function

The function aims to detect locked dialing number to

prevent a long distance call. The dialing output of the

chip is disabled if the first input key after on-off-hook is

the locked number when the lock function is enabled.

The lock function selection is listed below.

∑

HT9302x version

LOCK Pin

Function

OPEN

Normal dialing (no lock)

VDD

≤0, 9≤ is inhibited

VSS

≤0≤ is inhibited

Key definition

∑

0,1,2,3,4,5,6,7,8,9 keys

These are dialing number input keys for both the pulse

mode and the tone mode operations.

∑

*/T

This key executes the P

ÆT function and waits a t

P

ÆT

duration in the pulse mode. On the other hand, the

*/T

key executes the

* function in the tone mode.

∑

#

This is a dialing signal key for the tone mode only, no

response in the pulse mode.

∑

SA

Pressing this key can save the preceding dialing tele-

phone numbers. The saved number is redialed if it is

pressed again. SA will also redial the saved number if

it is the first key pressed at the off-hook state. During

the dialing signal transmission, the SA key is inhibited.

∑

F

The flash key can be selected as a digit or a control key

by the option resistors R

K13

& R

K14

. Pressing the flash

key will force the PO pin to be

≤low≤ for the t

F

duration

and is then followed by t

FP

(sec). t

F

can also be selected

by R

K13

, R

K14

.

∑

P

Pause key. The execution of the pause key pauses

the output for the t

P

duration. t

P

can be selected by

R

K21

.

∑

R

Redial key. Executes redialing as well as one-key re-

dial function.

∑

ST

This key can store lock number with personal code in

IDD lock operation.

∑

R/P

Redial and pause function key. If it is pressed as the

first key after off-hook, this key executes the redial

function. Otherwise, it works as the pause key.

Keyboard operation

The following operations are described under an on-off- hook or on-hook condition with the hand-free active condition.

HT9302 Series

Rev. 1.20

10

September 30, 2002

K e y b o a r d i n p u t : D 1 D 2 . . . D n

- P u l s e m o d e

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : D 1 D 2 . . . D n

S A M : U n c h a n g e d

( b ) w i t h * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

P Æ T

D n + 1 . . . D m

R M : D 1 D 2 . . . D n * / T D n + 1 . . . D m

S A M : U n c h a n g e d

T o n e

P u l s e

∑ N o r m a l d i a l i n g

K e y b o a r d i n p u t : D 1 D 2 . . . D n * / T D n + 1 . . .

D m

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : D 1 D 2 . . . D n

S A M : U n c h a n g e d

( b ) w i t h * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n * D n + 1 . . . D m

R M : D 1 D 2 . . . D n * D n + 1 . . . D m

S A M : U n c h a n g e d

- T o n e m o d e

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : U n c h a n g e d

S A M : U n c h a n g e d

R M c o n t e n t : D 1 D 2 . . . D n

( b ) w i t h * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

P Æ T

D n + 1 . . . D m

R M : U n c h a n g e d

S A M : U n c h a n g e d

R M c o n t e n t : D 1 D 2 . . . D n * / T D n + 1 . . . D m

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : U n c h a n g e d

S A M : U n c h a n g e d

R M c o n t e n t : D 1 D 2 . . . D n

( b ) w i t h * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n * D n + 1 . . . D m

R M : U n c h a n g e d

S A M : U n c h a n g e d

R M c o n t e n t : D 1 D 2 . . . D n * / T D n + 1 . . . D m

- P u l s e m o d e

- T o n e m o d e

P u l s e

T o n e

∑ R e d i a l

K e y b o a r d i n p u t : D 1 D 2 . . . D n * / T D n + 1 . . .

D m

( a ) w i t h o u t * / T

K e y b o a r d i n p u t : D 1 D 2 . . . D n

K e y b o a r d i n p u t : [ R o r R / P ]

K e y b o a r d i n p u t : [ R o r R / P ]

K e y b o a r d i n p u t : [ R o r R / P ]

K e y b o a r d i n p u t : [ R o r R / P ]

N o t e : T h e m a x i m u m c a p a c i t y o f t h e R M m e m o r y i s 3 2 d i g i t s . W h e n m o r e t h a n 3 2 d i g i t s a r e e n t e r e d ,

t h e s i g n a l i s t r a n s m i t t e d b u t t h e r e d i a l f u n c t i o n i s i n h i b i t e d .

HT9302 Series

Rev. 1.20

11

September 30, 2002

D m

S A

K e y b o a r d i n p u t : D 1 D 2 . . . D n * / T D n + 1 . . .

D m

R

K e y b o a r d i n p u t : D 1 D 2 . . . D n * / T D n + 1 . . .

K e y b o a r d i n p u t : D 1 D 2 . . . D n R

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

B R K

t

R P

R M : D 1 D 2 . . . D n

S A M : U n c h a n g e d

( b ) w i t h * / T

R M : D 1 D 2 . . . D n * / T D n + 1 . . . D m

S A M : U n c h a n g e d

( a ) w i t h o u t * / T

R M : D 1 D 2 . . . D n

S A M : U n c h a n g e d

( b ) w i t h * / T

- T o n e m o d e

- P u l s e m o d e

P u l s e

t

B R K

t

R P

D 1 D 2 . . . D n t

P Æ T

P u l s e

D i a l i n g o u t p u t : D 1 D 2 . . . D n * D n + 1 . . . D m

R M : D 1 D 2 . . . D n * D n + 1 . . . D m

S A M : U n c h a n g e d

t

B R K

t

R P

D 1 D 2 . . . D n * D n + 1

. . . D m

T o n e

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

P Æ T

D n + 1 . . . D m

T o n e

∑ O n e - k e y r e d i a l

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : D 1 D 2 . . . D n

S A M : D 1 D 2 . . . D n

( b ) w i t h * / T

R M : D 1 D 2 . . . D n * / T D n + 1 . . . D m

S A M : D 1 D 2 . . . D n * / T D n + 1 . . . D m

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : D 1 D 2 . . . D n

S A M : D 1 D 2 . . . D n

( b ) w i t h * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n * D n + 1 . . . D m

R M : D 1 D 2 . . . D n * D n + 1 . . . D m

S A M : D 1 D 2 . . . D n * D n + 1 . . . D m

- P u l s e m o d e

- T o n e m o d e

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

P Æ T

D n + 1 . . . D m

T o n e

P u l s e

∑ S A c o p y

D 1 D 2 . . . D n

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

B R K

t

R P

D 1 D 2

. . . D n

D n + 1 . . . D m

K e y b o a r d i n p u t : D 1 D 2 . . . D n R

D m

R

K e y b o a r d i n p u t : D 1 D 2 . . . D n * / T D n + 1 . . .

K e y b o a r d i n p u t : D 1 D 2 . . . D n S A

K e y b o a r d i n p u t : D 1 D 2 . . . D n S A

D m

S A

K e y b o a r d i n p u t : D 1 D 2 . . . D n * / T D n + 1 . . .

N o t e : T h e m a x i m u m c a p a c i t y o f t h e R M m e m o r y i s 3 2 d i g i t s . W h e n m o r e t h a n 3 2 d i g i t s p l u s t h e " S A " k e y

a r e e n t e r e d , t h e S A V E f u n c t i o n w i l l n o t b e e x e c u t e d , a n d a l l t h e e x i s t i n g d a t a i n t h e s a v e m e m o r y

w i l l n o t b e c h a n g e d .

N o t e : I f t h e d i a l i n g n u m b e r e x c e e d s 3 2 d i g i t s , r e d i a l i n g i s i n h i b i t e d a n d P O = V D D

HT9302 Series

Rev. 1.20

12

September 30, 2002

K e y b o a r d i n p u t : D 1 D 2 . . . D n . D n + 1 . . .

D m

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : U n c h a n g e d

S A M : U n c h a n g e d

( b ) w i t h * / T

R M : U n c h a n g e d

S A M : U n c h a n g e d

( a ) w i t h o u t * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n

R M : U n c h a n g e d

S A M : U n c h a n g e d

( b ) w i t h * / T

D i a l i n g o u t p u t : D 1 D 2 . . . D n * D n + 1 . . . D m

R M : U n c h a n g e d

S A M : U n c h a n g e d

S A M c o n t e n t : D 1 D 2 . . . D n

S A M c o n t e n t : D 1 D 2 . . . D n * / T D n + 1 . . . D m

S A M c o n t e n t : D 1 D 2 . . . D n

S A M c o n t e n t : D 1 D 2 . . . D n * D n + 1 . . . D m

- P u l s e m o d e

- T o n e m o d e

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

P Æ T

D n + 1 . . . D m

T o n e

P u l s e

∑ S A d i a l i n g

K e y b o a r d i n p u t : S A

K e y b o a r d i n p u t : S A

K e y b o a r d i n p u t : S A

K e y b o a r d i n p u t : S A

R M : D 1 D 2 . . . D n

S A M : U n c h a n g e d

- . l a s h a s a d i g i t a l k e y

- . l a s h a s a c o n t r o l k e y

( a ) T h e i n t e r v e n i e n t k e y

R M : U n c h a n g e d

S A M : U n c h a n g e d

D i a l i n g o u t p u t : t

.

t

. P

D 1 D 2 . . . D n

K e y b o a r d i n p u t : . D 1 D 2 . . . D n

( b ) T h e f i r s t k e y

∑ . l a s h

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

.

t

. P

D n + 1 . . .

D m

R M : D n + 1 . . . D m

S A M : U n c h a n g e d

D i a l i n g o u t p u t : D 1 D 2 . . . D n T

.

T

. P

D n + 1 . . .

D m

N o t e : T

.

: b r e a k a f l a s h t i m e

K e y b o a r d i n p u t : D 1 D 2 . . . D n . D n + 1 . . .

D m

D i a l i n g o u t p u t : D 1 D 2 . . . D n t

P

D n + 1 . . . D m

R M : D 1 D 2 . . . D n P D n + 1 . . . D m

S A M : U n c h a n g e d

K e y b o a r d i n p u t : D 1 D 2 . . . D n P D n + 1 . . . D m

∑ P a u s e

∑ N o t e

R M : R e d i a l m e m o r y

S A M : S a v e d i a l i n g m e m o r y

D 1 D 2 . . . D n : 0 ~ 9

D n + 1 . . . D m : 0 ~ 9 , * , #

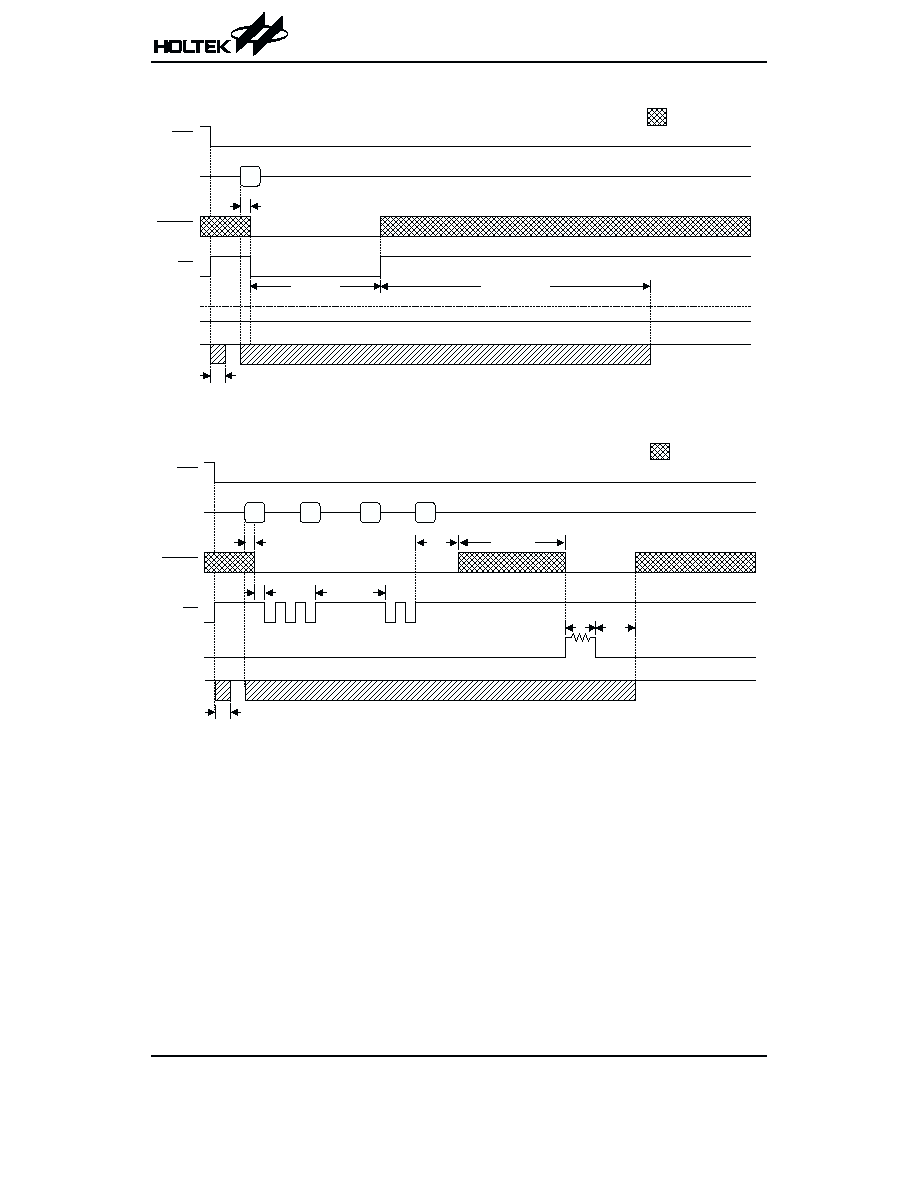

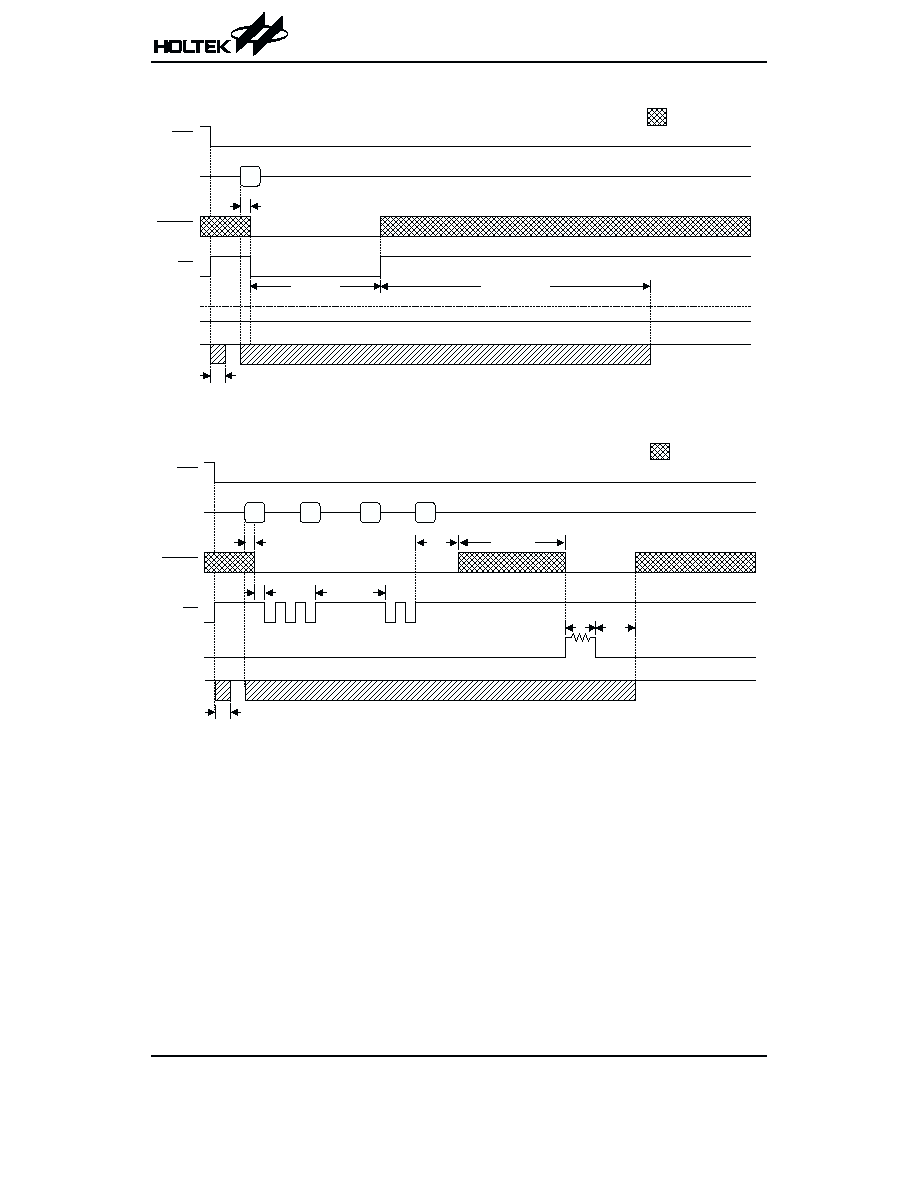

Timing Diagrams

Normal dialing

∑

Pulse mode

∑

Tone mode

HT9302 Series

Rev. 1.20

13

September 30, 2002

H T 9 3 0 2 G

X M U T E

O t h e r s

X M U T E

K E Y I N

P O

t

I D P

- t

M

t

D B

t

D B

t

P D P

t

M

t

M

t

B

t

P D P

t

I D P

H i g h I m p e d a n c e

H K S

t

I D P

- t

M

R

D 2

D 1

t

M

X 2

2 0 m s

t

D B

t

I D P

- t

M

2 0 m s

t

I D P

- t

M

D T M .

X 2

D T M .

H i g h I m p e d a n c e

t

D B

t

I T P M

t

I T P M

t

T M I N

K E Y I N

R

D 1

t

I T P M

t

I T P M

t

D B

t

D B

D 2

P O

H K S

X M U T E

2 0 m s

2 0 m s

Dialing with pause key

∑

Pulse mode

∑

Tone mode

HT9302 Series

Rev. 1.20

14

September 30, 2002

H T 9 3 0 2 G

X M U T E

O t h e r s

X M U T E

K E Y I N

D T M .

P O

t

I D P

t

D B

t

P D P

H i g h I m p e d a n c e

H K S

t

I D P

- t

M

D 3

D 2

D 1

t

M

t

I D P

- t

M

t

M

t

P

+ t

P D P

P

X 2

2 0 m s

X 2

D T M .

H i g h I m p e d a n c e

t

D B

t

I T P M

K E Y I N

D 3

D 2

t

T M I N

t

I T P M

P

t

P

t

I T P M

D 1

P O

H K S

X M U T E

2 0 m s

Flash key operation

Pulse

ÆTone operation

HT9302 Series

Rev. 1.20

15

September 30, 2002

K E Y I N

X 2

t

. P

t

.

H i g h I m p e d a n c e

t

D B

2 0 m s

D T M .

P O

H K S

X M U T E

.

K E Y I N

X 2

D T M .

H i g h I m p e d a n c e

t

P D P

t

I D P

+ t

P D P

t

T M I N

t

D B

t

I T P M

t

I D P

t

P

Æ

T

D 1

2 0 m s

D 2

D 3

* / T

P O

H K S

X M U T E

One key redial operation

CLOCK & DOUT operation

HT9302 Series

Rev. 1.20

16

September 30, 2002

t

R P

( 1 s e c )

t

B R K

( 1 . 2 s e c s )

t

I T P M

t

I T P M

H i g h I m p e d a n c e

t

I T P M

t

I T P M

K E Y I N

X 2

D T M .

D 1

D 2

R

t

D B

P O

H K S

X M U T E

2 0 m s

t

D B

t

D B

N o t e : D 1 = D 3 = 3

D 2 = 2

f

C L O C K

= 2 . 4 k H z

D a t a

t

P D P

t

D B

t

B

t

M

H i g h I m p e d a n c e

X 2

D 1

C L O C K

D O U T

K E Y I N

P O

H K S

X M U T E

2 0 m s

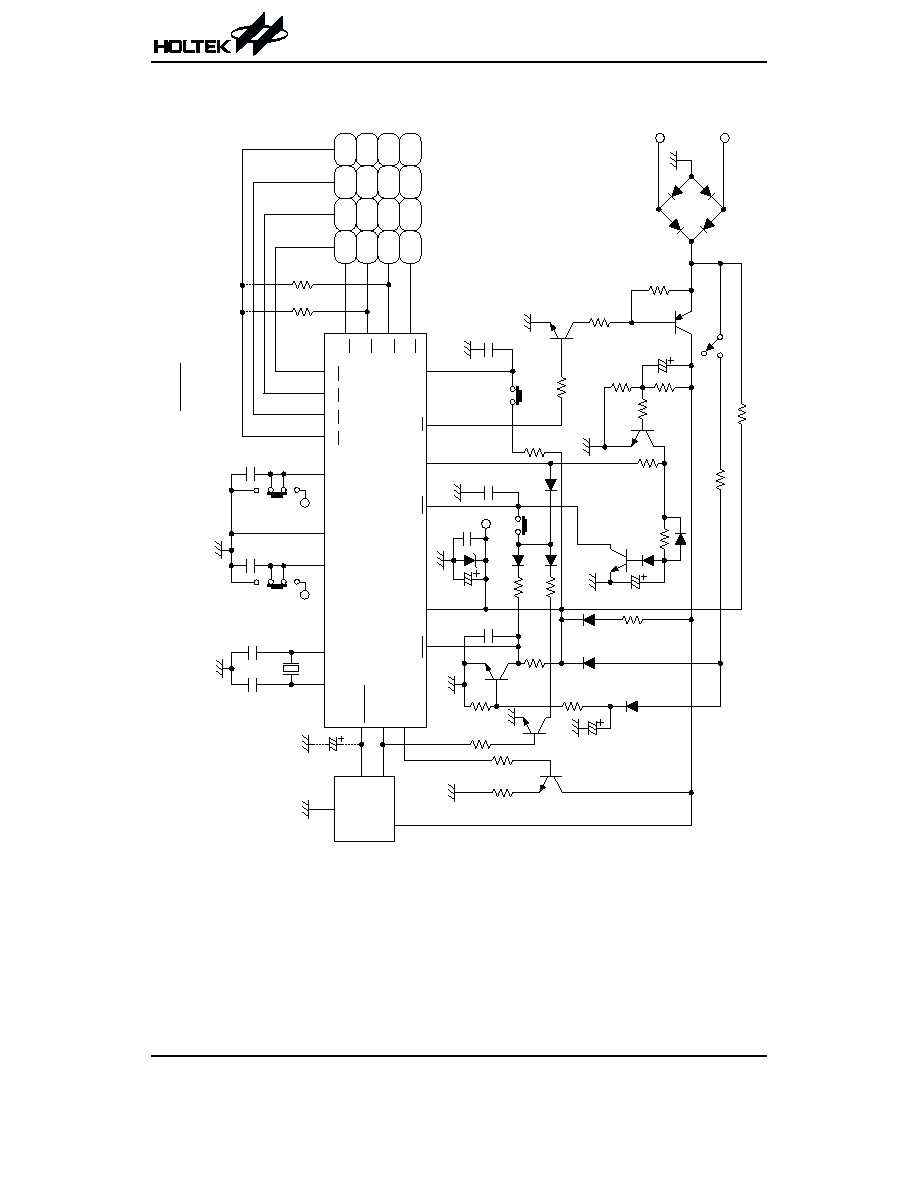

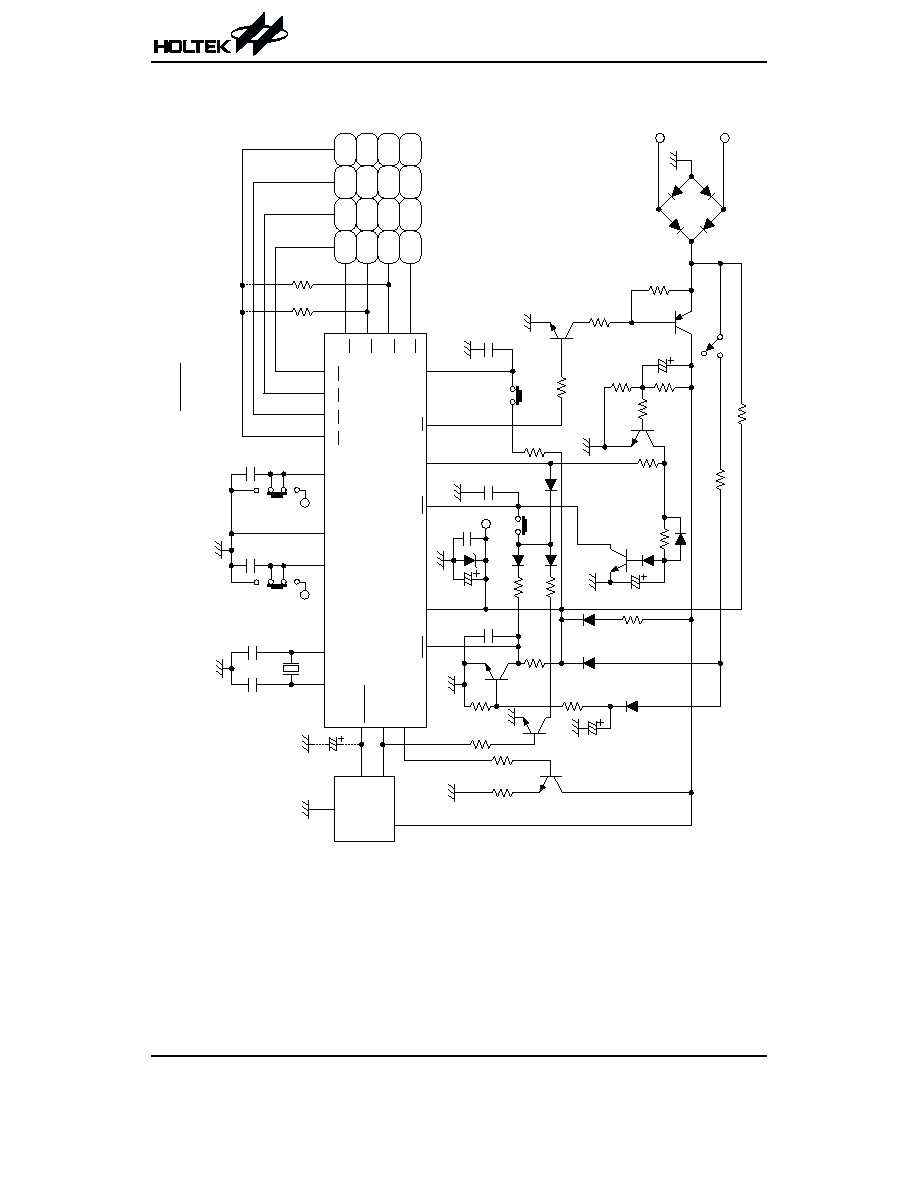

Application Circuits

Application circuit 1

HT9302 Series

Rev. 1.20

17

September 30, 2002

C

4

R

4

P

O

H

K

S

X

M

U

T

E

V

S

S

M

O

D

E

X

1

X

2

V

D

D

1

0

p

p

s

2

0

p

p

s

T

o

n

e

7

8

3

.

5

8

M

H

z

r

e

s

o

n

a

t

o

r

V

D

D

1

5

0

W

1

4

1

3

5

.

1

V

1

N

4

1

4

8

1

N

4

1

4

8

A

4

2

A

9

2

2

2

M

W

T

i

p

R

i

n

g

1

A

b

r

i

d

g

e

1

4

3

2

9

6

D

T

M

.

1

5

1

6

1

7

1

8

R

k

R

k

1

m

.

S

P

E

E

C

H

N

E

T

W

O

R

K

R

2

R

1

R

3

C

1

C

2

C

3

1

1

1

0

1

2

*

R

k

f

o

r

d

i

a

l

i

n

g

s

i

g

n

a

l

o

p

t

i

o

n

(

R

e

f

e

r

t

o

t

h

e

f

u

n

c

t

i

o

n

a

l

d

e

s

c

r

i

p

t

i

o

n

)

*

U

n

s

p

e

c

i

f

i

e

d

t

r

a

n

s

i

s

t

o

r

s

a

r

e

o

f

8

0

5

0

t

y

p

e

*

A

1

m

.

c

a

p

a

c

i

t

o

r

b

e

t

w

e

e

n

X

M

U

T

E

a

n

d

V

S

S

(

G

N

D

)

i

s

r

e

c

o

m

m

e

n

d

e

d

1

4

7

*

/

T

2

5

8

0

3

6

9

#

S

A

.

P

R

V

D

D

L

O

C

K

V

D

D

0

,

9

n

o

l

o

c

k

0

5

1

0

p

.

1

0

p

.

3

9

p

.

3

9

p

.

1

m

.

1

.

5

k

W

2

2

0

k

W

1

0

0

k

W

1

0

0

k

W

2

7

0

k

W

1

0

0

m

.

0

.

1

m

.

2

.

2

k

W

4

7

k

W

3

.

3

k

W

1

0

0

k

W

O

f

f

-

h

o

o

k

O

n

-

h

o

o

k

H

T

9

3

0

2

A

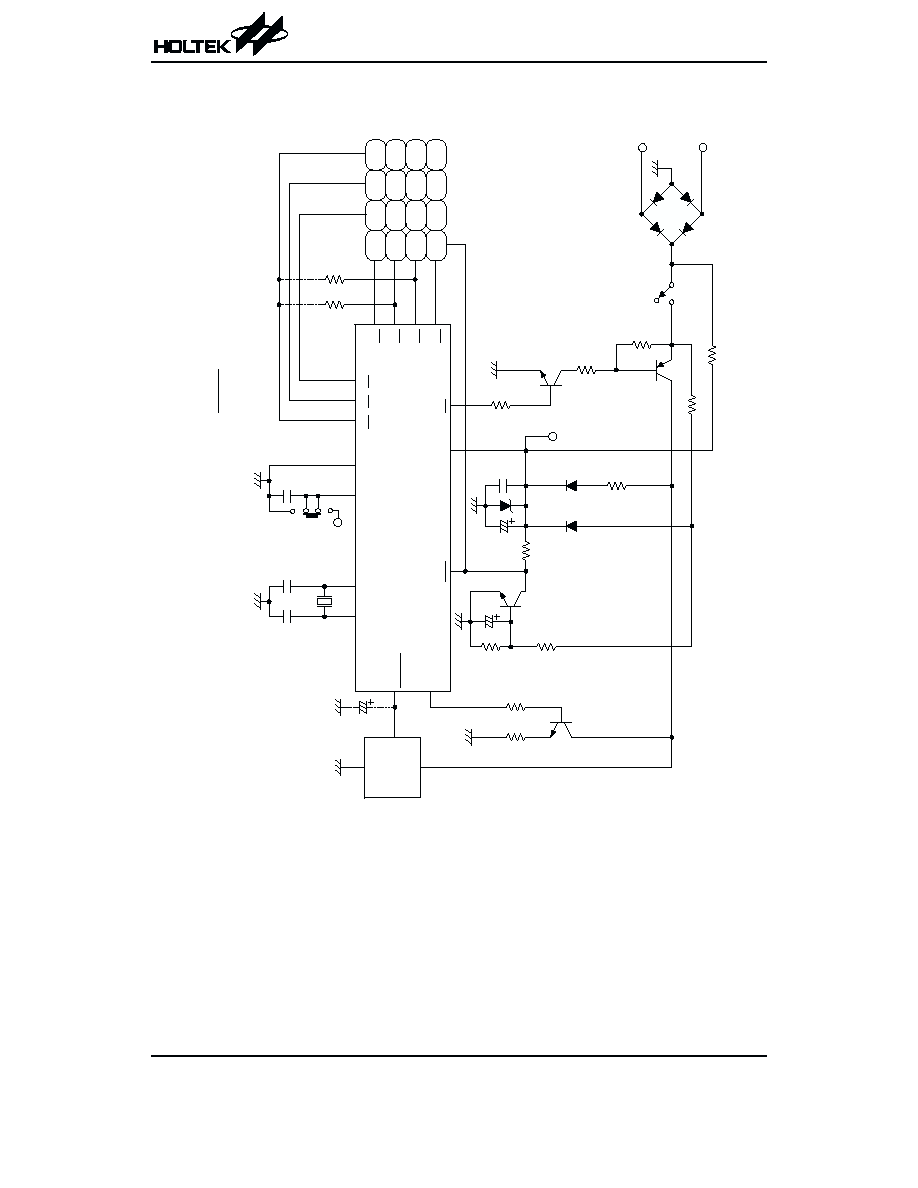

Application circuit 2

HT9302 Series

Rev. 1.20

18

September 30, 2002

H

K

S

1

5

0

W

1

0

0

m

.

5

.

1

V

H

o

l

d

1

N

4

1

4

8

1

N

4

1

4

8

1

N

4

1

4

8

1

N

4

1

4

8

x

4

1

m

.

1

6

V

1

N

4

1

4

8

H

a

n

d

-

f

r

e

e

A

4

2

1

0

m

.

5

0

V

A

9

2

2

2

M

W

T

i

p

R

i

n

g

1

A

b

r

i

d

g

e

C

4

R

4

X

M

U

T

E

V

S

S

M

O

D

E

X

1

X

2

V

D

D

8

H

D

O

1

7

2

5

4

3

1

0

7

D

T

M

.

H

.

O

1

8

1

9

2

0

2

1

R

k

R

k

1

m

.

R

2

R

1

R

3

C

1

C

2

C

3

1

5

H

.

I

1

1

2

2

1

H

D

I

V

D

D

1

3

1

4

S

P

E

E

C

H

N

E

T

W

O

R

K

P

O

1

4

7

*

/

T

2

5

8

0

3

6

9

#

S

A

.

P

R

V

D

D

1

6

1

2

9

1

0

p

p

s

2

0

p

p

s

T

o

n

e

3

.

5

8

M

H

z

r

e

s

o

n

a

t

o

r

L

O

C

K

V

D

D

6

0

,

9

n

o

l

o

c

k

0

1

0

p

.

*

R

k

f

o

r

d

i

a

l

i

n

g

s

i

g

n

a

l

o

p

t

i

o

n

(

R

e

f

e

r

t

o

t

h

e

f

u

n

c

t

i

o

n

a

l

d

e

s

c

r

i

p

t

i

o

n

)

*

U

n

s

p

e

c

i

f

i

e

d

t

r

a

n

s

i

s

t

o

r

s

a

r

e

o

f

8

0

5

0

t

y

p

e

*

A

1

m

.

c

a

p

a

c

i

t

o

r

b

e

t

w

e

e

n

X

M

U

T

E

a

n

d

V

S

S

(

G

N

D

)

i

s

r

e

c

o

m

m

e

n

d

e

d

1

0

p

.

3

9

p

.

3

9

p

.

1

m

.

0

.

1

m

.

1

.

5

k

W

4

7

k

W

1

0

0

k

W

2

7

0

k

W

2

2

0

k

W

2

.

2

k

W

1

0

0

k

W

2

2

0

k

W

2

2

k

W

2

2

k

W

0

.

1

m

.

0

.

1

m

.

3

3

0

k

W

2

2

0

k

W

1

0

0

k

W

1

0

0

k

W

3

3

k

W

3

.

3

k

W

4

7

k

W

0

.

0

2

m

.

1

0

k

W

O

f

f

-

h

o

o

k

O

n

-

h

o

o

k

H

T

9

3

0

2

B

Application circuit 3

HT9302 Series

Rev. 1.20

19

September 30, 2002

C

4

R

4

P

O

H

K

S

X

M

U

T

E

8

3

.

5

8

M

H

z

r

e

s

o

n

a

t

o

r

V

D

D

1

5

0

W

1

5

5

.

1

V

1

N

4

1

4

8

1

N

4

1

4

8

A

4

2

A

9

2

2

2

M

W

T

i

p

R

i

n

g

1

A

b

r

i

d

g

e

1

4

3

2

D

T

M

.

1

7

1

8

1

9

2

0

R

k

R

k

1

m

.

R

2

R

1

R

3

C

1

C

2

C

3

1

3

1

2

1

4

1N

41

48

1

0

D

O

U

T

C

L

O

C

K

1

1

S

P

E

E

C

H

N

E

T

W

O

R

K

H

T

1

6

X

X

L

C

D

D

R

I

V

E

R

(

s

e

e

H

T

1

6

X

X

d

a

t

a

)

2

5

8

0

3

6

9

#

S

A

.

P

R

1

4

7

*

/

T

V

D

D

V

S

S

M

O

D

E

X

1

X

2

V

D

D

1

0

p

p

s

2

0

p

p

s

T

o

n

e

7

1

6

9

6

L

O

C

K

0

,

9

n

o

l

o

c

k

0

5

1

0

p

.

*

R

k

f

o

r

d

i

a

l

i

n

g

s

i

g

n

a

l

o

p

t

i

o

n

(

R

e

f

e

r

t

o

t

h

e

f

u

n

c

t

i

o

n

a

l

d

e

s

c

r

i

p

t

i

o

n

)

*

U

n

s

p

e

c

i

f

i

e

d

t

r

a

n

s

i

s

t

o

r

s

a

r

e

o

f

8

0

5

0

t

y

p

e

*

A

1

m

.

c

a

p

a

c

i

t

o

r

b

e

t

w

e

e

n

X

M

U

T

E

a

n

d

V

S

S

(

G

N

D

)

i

s

r

e

c

o

m

m

e

n

d

e

d

1

0

p

.

3

9

p

.

3

9

p

.

1

m

.

1

.

5

k

W

1

0

0

k

W

2

2

0

k

W

1

0

0

k

W

1

0

0

m

.

2

7

0

k

W

2

.

2

k

W

0

.

1

m

.

3

.

3

k

W

4

7

k

W

1

0

0

k

W

O

f

f

-

h

o

o

k

O

n

-

h

o

o

k

V

D

D

H

T

9

3

0

2

C

Application circuit 4

HT9302 Series

Rev. 1.20

20

September 30, 2002

H

D

I

1

4

7

*

/

T

2

5

8

0

3

6

9

#

S

A

.

P

R

1

5

0

W

5

.

1

V

H

o

l

d

1

N

4

1

4

8

1

N

4

1

4

8

1

N

4

1

4

8

1

N

4

1

4

8

x

4

1

m

.

1

6

V

1

N

4

1

4

8

H

a

n

d

-

f

r

e

e

A

4

2

1

0

m

.

5

0

V

A

9

2

2

2

M

W

T

i

p

R

i

n

g

1

A

b

r

i

d

g

e

C

4

R

4

P

O

X

M

U

T

E

H

D

O

2

5

4

3

2

0

2

1

2

2

2

3

R

k

R

k

1

m

.

R

2

R

1

R

3

C

1

C

2

C

3

1

7

H

.

I

1

1

2

4

1

V

D

D

1

5

1

6

S

P

E

E

C

H

N

E

T

W

O

R

K

D

O

U

T

H

K

S

1

8

1

4

9

1

2

4

7

k

W

1

N

4

1

4

8

D

T

M

.

H

.

O

H

T

1

6

X

X

L

C

D

D

R

I

V

E

R

(

s

e

e

H

T

1

6

X

X

d

a

t

a

)

V

D

D

V

S

S

M

O

D

E

X

1

X

2

V

D

D

1

0

p

p

s

2

0

p

p

s

T

o

n

e

8

3

.

5

8

M

H

z

r

e

s

o

n

a

t

o

r

1

9

1

0

7

C

L

O

C

K

1

3

L

O

C

K

V

D

D

0

,

9

n

o

l

o

c

k

0

6

1

0

p

.

*

R

k

f

o

r

d

i

a

l

i

n

g

s

i

g

n

a

l

o

p

t

i

o

n

(

R

e

f

e

r

t

o

t

h

e

f

u

n

c

t

i

o

n

a

l

d

e

s

c

r

i

p

t

i

o

n

)

*

U

n

s

p

e

c

i

f

i

e

d

t

r

a

n

s

i

s

t

o

r

s

a

r

e

o

f

8

0

5

0

t

y

p

e

*

A

1

m

.

c

a

p

a

c

i

t

o

r

b

e

t

w

e

e

n

X

M

U

T

E

a

n

d

V

S

S

(

G

N

D

)

i

s

r

e

c

o

m

m

e

n

d

e

d

1

0

p

.

3

9

p

.

3

9

p

.

1

m

.

4

7

k

W

1

.

5

k

W

1

0

0

k

W

2

2

0

k

W

2

7

0

k

W

2

.

2

k

W

0

.

1

m

.

1

0

0

m

.

2

2

k

W

2

2

k

W

0

.

1

m

.

0

.

1

m

.

1

0

0

k

W

2

2

0

k

W

2

2

0

k

W

3

3

k

W

1

0

k

W

3

3

0

k

W

1

0

0

k

W

4

7

k

W

3

.

3

k

W

0

.

0

2

m

.

1

0

0

k

W

O

f

f

-

h

o

o

k

O

n

-

h

o

o

k

H

T

9

3

0

2

D

Application circuit 5

HT9302 Series

Rev. 1.20

21

September 30, 2002

R

4

P

O

H

K

S

X

M

U

T

E

V

S

S

M

O

D

E

X

1

X

2

V

D

D

1

0

p

p

s

2

0

p

p

s

T

o

n

e

5

6

3

.

5

8

M

H

z

r

e

s

o

n

a

t

o

r

V

D

D

1

5

0

W

1

2

1

1

5

.

1

V

1

N

4

1

4

8

1

N

4

1

4

8

A

4

2

A

9

2

2

2

M

W

T

i

p

R

i

n

g

1

A

b

r

i

d

g

e

1

3

2

1

0

p

.

7

4

D

T

M

.

1

3

1

4

1

5

1

6

R

k

R

k

1

m

.

R

2

R

1

R

3

C

1

C

2

C

3

9

8

1

0

S

P

E

E

C

H

N

E

T

W

O

R

K

.

P

R

3

6

9

#

2

5

8

0

1

4

7

*

/

T

*

R

k

f

o

r

d

i

a

l

i

n

g

s

i

g

n

a

l

o

p

t

i

o

n

(

R

e

f

e

r

t

o

t

h

e

f

u

n

c

t

i

o

n

a

l

d

e

s

c

r

i

p

t

i

o

n

)

*

U

n

s

p

e

c

i

f

i

e

d

t

r

a

n

s

i

s

t

o

r

s

a

r

e

o

f

8

0

5

0

t

y

p

e

*

A

1

m

.

c

a

p

a

c

i

t

o

r

b

e

t

w

e

e

n

X

M

U

T

E

a

n

d

V

S

S

(

G

N

D

)

i

s

r

e

c

o

m

m

e

n

d

e

d

V

D

D

3

9

p

.

3

9

p

.

1

m

.

1

.

5

k

W

1

0

0

k

W

1

0

0

k

W

2

2

0

k

W

2

7

0

k

W

1

0

0

m

.

2

.

2

k

W

0

.

1

m

.

4

7

k

W

3

.

3

k

W

1

0

0

k

W

O

f

f

-

h

o

o

k

O

n

-

h

o

o

k

H

T

9

3

0

2

G

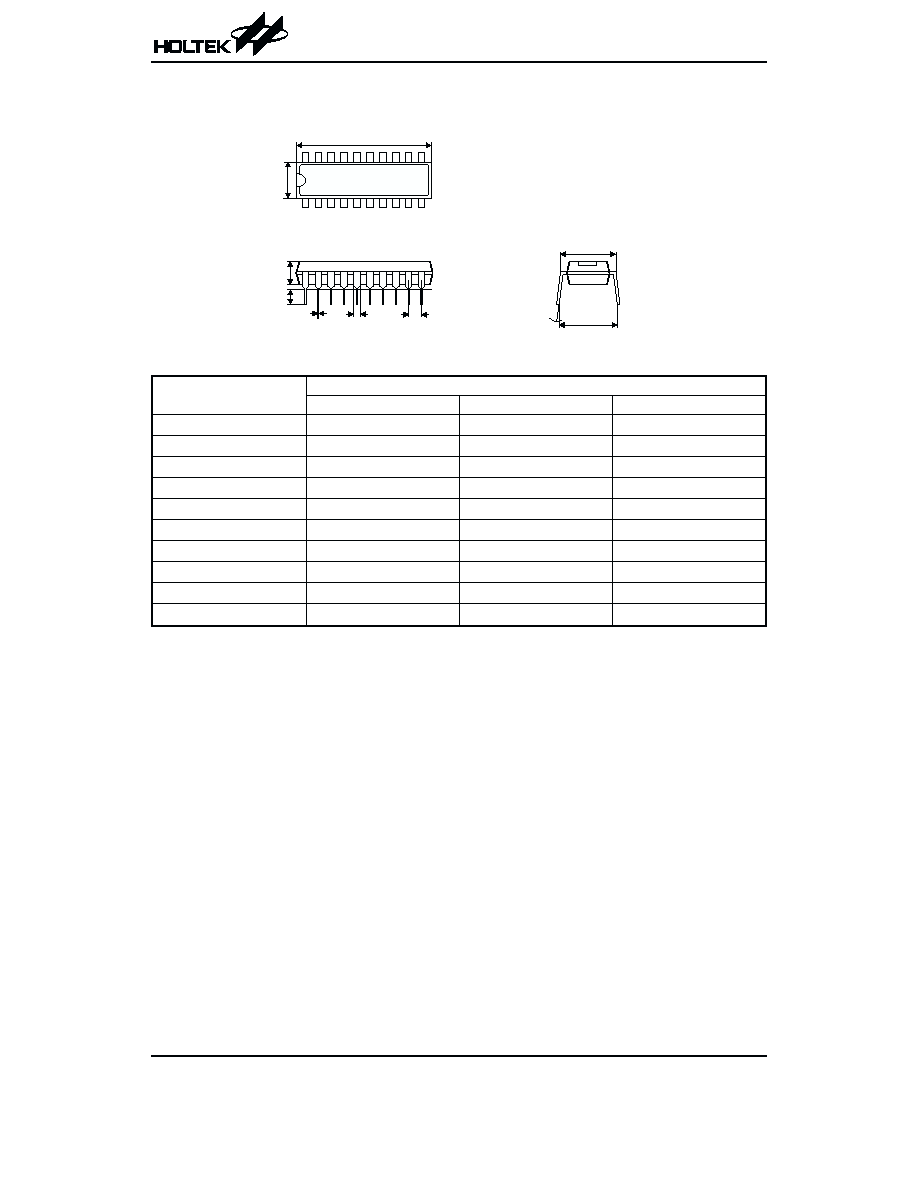

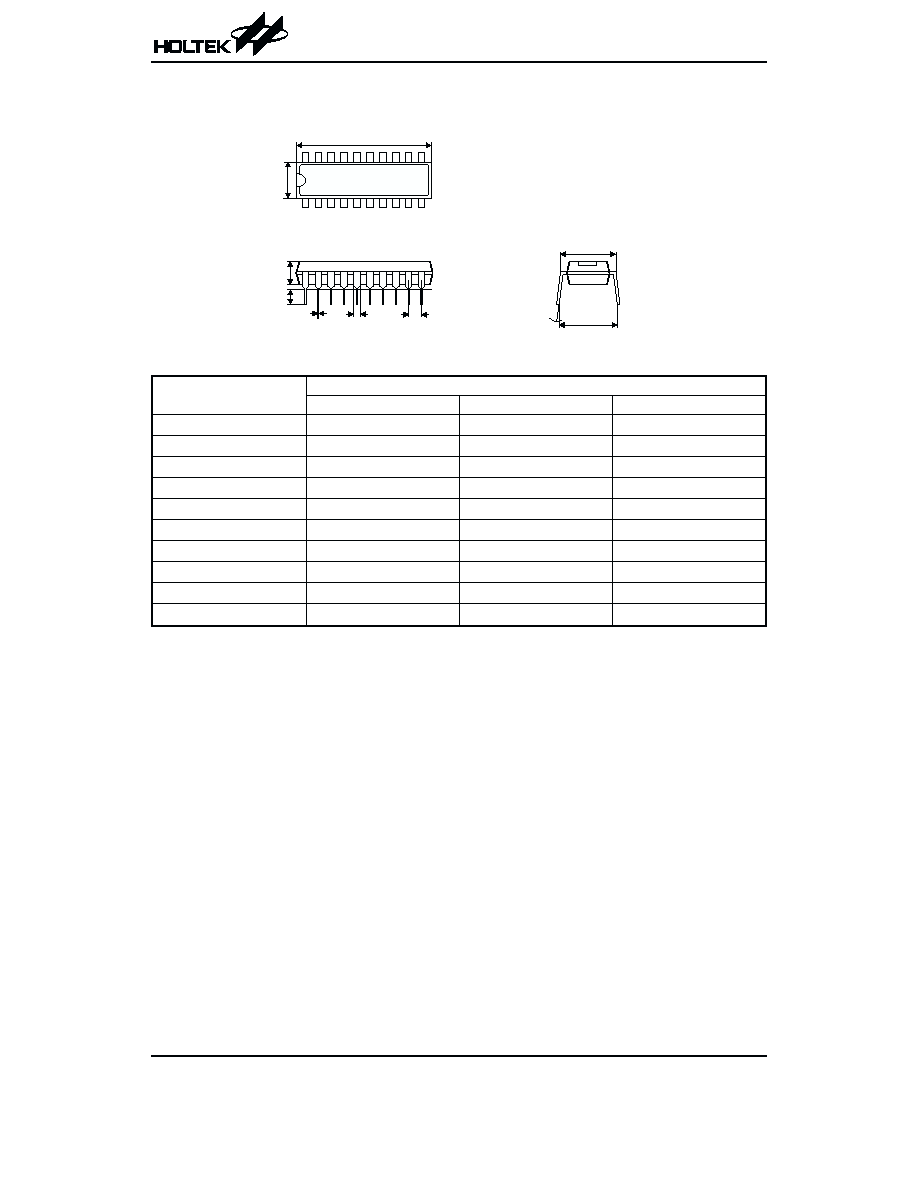

Package Information

16-pin DIP (300mil) outline dimensions

Symbol

Dimensions in mil

Min.

Nom.

Max.

A

745

æ

775

B

240

æ

260

C

125

æ

135

D

125

æ

145

E

16

æ

20

F

50

æ

70

G

æ

100

æ

H

295

æ

315

I

335

æ

375

a

0

∞

æ

15

∞

HT9302 Series

Rev. 1.20

22

September 30, 2002

a

1 6

1

9

8

A

B

C

D

E

.

G

H

I

18-pin DIP (300mil) outline dimensions

Symbol

Dimensions in mil

Min.

Nom.

Max.

A

895

æ

915

B

240

æ

260

C

125

æ

135

D

125

æ

145

E

16

æ

20

F

50

æ

70

G

æ

100

æ

H

295

æ

315

I

335

æ

375

a

0

∞

æ

15

∞

HT9302 Series

Rev. 1.20

23

September 30, 2002

1 8

1

1 0

9

a

A

B

C

D

E

.

G

H

I

20-pin DIP (300mil) outline dimensions

Symbol

Dimensions in mil

Min.

Nom.

Max.

A

1020

æ

1045

B

240

æ

260

C

125

æ

135

D

125

æ

145

E

16

æ

20

F

50

æ

70

G

æ

100

æ

H

295

æ

315

I

335

æ

375

a

0

∞

æ

15

∞

HT9302 Series

Rev. 1.20

24

September 30, 2002

2 0

1

1 1

1 0

a

A

B

C

D

E

.

G

H

I

22-pin SKDIP (300mil) outline dimensions

Symbol

Dimensions in mil

Min.

Nom.

Max.

A

1085

æ

1105

B

253

æ

263

C

125

æ

135

D

125

æ

145

E

16

æ

20

F

50

æ

70

G

æ

100

æ

H

295

æ

315

I

330

æ

375

a

0

∞

æ

15

∞

HT9302 Series

Rev. 1.20

25

September 30, 2002

2 2

1

1 2

1 1

a

A

B

C

D

E

.

G

H

I

24-pin SKDIP (300mil) outline dimensions

Symbol

Dimensions in mil

Min.

Nom.

Max.

A

1235

æ

1265

B

255

æ

265

C

125

æ

135

D

125

æ

145

E

16

æ

20

F

50

æ

70

G

æ

100

æ

H

295

æ

315

I

345

æ

360

a

0

∞

æ

15

∞

HT9302 Series

Rev. 1.20

26

September 30, 2002

2 4

1

1 3

1 2

a

A

B

C

D

E

.

G

H

I

HT9302 Series

Rev. 1.20

27

September 30, 2002

Copyright

” 2002 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek as-

sumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used

solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable

without further modification, nor recommends the use of its products for application that may present a risk to human life

due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most

up-to-date information, please visit our web site at http://www.holtek.com.tw.

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999

Fax: 886-3-563-1189

http://www.holtek.com.tw

Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635

Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560

Fax: 021-6485-0313

http://www.holtek.com.cn

Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288

Fax: 852-2-742-8657

Holmate Semiconductor, Inc.

48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539

Tel: 510-252-9880

Fax: 510-252-9885

http://www.holmate.com