HI-1569

MIL-STD-1553 / 1760

5V Monolithic Dual Transceiver

DESCRIPTION

FEATURES

The HI-1569 is a low power CMOS dual transceiver

designed to meet the requirements of MIL-STD-1553

/1760 specifications.

The transmitter section of each channel takes

complementary CMOS / TTL digital input data and converts

it to bi-phase Manchester encoded 1553 signals suitable

for driving the bus isolation transformer. Separate

transmitter inhibit control signals are provided for each

transmitter.

The receiver section of each channel converts the 1553

bus bi-phase data to complementary CMOS / TTL data

suitable for inputting to a Manchester decoder. Each

receiver has a separate enable input which can be used to

force the output of the receiver to a logic 0.

The transmitter outputs and receiver inputs for each

channel are brought out to separate sets of pins. For typical

MIL-STD-1553 applications the transmitter output and

receiver input will be tied together at the isolation

transformer.

!

!

!

!

!

!

Compliant to MIL-STD-1553A & B,

MIL-STD-1760, ARINC 708A

CMOS technology for low standby power

Single 5V power supply

Less than 1.0W maximum power dissipation

Military processing options

Industry standard 64-pin PQFP package

March 2003

(DS1569 Rev. B)

03/03

HOLT INTEGRATED CIRCUITS

www.holtic.com

PIN CONFIGURATION

(Top View)

64 - Pin Plastic Quad Flat Pack (PQFP)

HI-1569

64

-

63

-

TXA

62

-

TXINHA

61

-

VDD

A

60

-

VDD

A

59

-

N/C

58

-

IN

57

-

BUSA

IN

56

-

N/C

55

-

GND

A

54

-

N/C

53

-

VDD

A

52

-

VDD

A

51

-

N/C

50

-

GND

A

49

-

N/C

TXA

BUSA

48 -

47 - RXENA

46 - RXA

45 - N/C

44 - VDD A

43 - N/C

42 - N/C

41 - N/C

40 - GND A

39 -

OUT

38 -

OUT

37 - VDD B

36 - VDD B

35 - BUSB OUT

34 - BUSB OUT

33 - GND B

RXA

BUSB

BUSB

N/C

-1

7

GND

B

-1

8

N/C

-1

9

VDD

B

-2

0

VDD

B

-2

1

N/C

-2

2

GND

B

-2

3

N/C

-2

4

BUSB

IN

-2

5

IN

-2

6

N/C

-2

7

VDD

B

-2

8

VDD

B

-2

9

TXINHB

-3

0

TXB

-3

1

-3

2

BUSB

TXB

GND A - 1

BUSA OUT - 2

BUSA OUT - 3

VDD A - 4

VDD A - 5

OUT - 6

OUT - 7

GND B - 8

N/C - 9

N/C - 10

N/C - 11

VDD B - 12

N/C - 13

RXB - 14

RXENB - 15

- 16

BUSA

BUSA

RXB

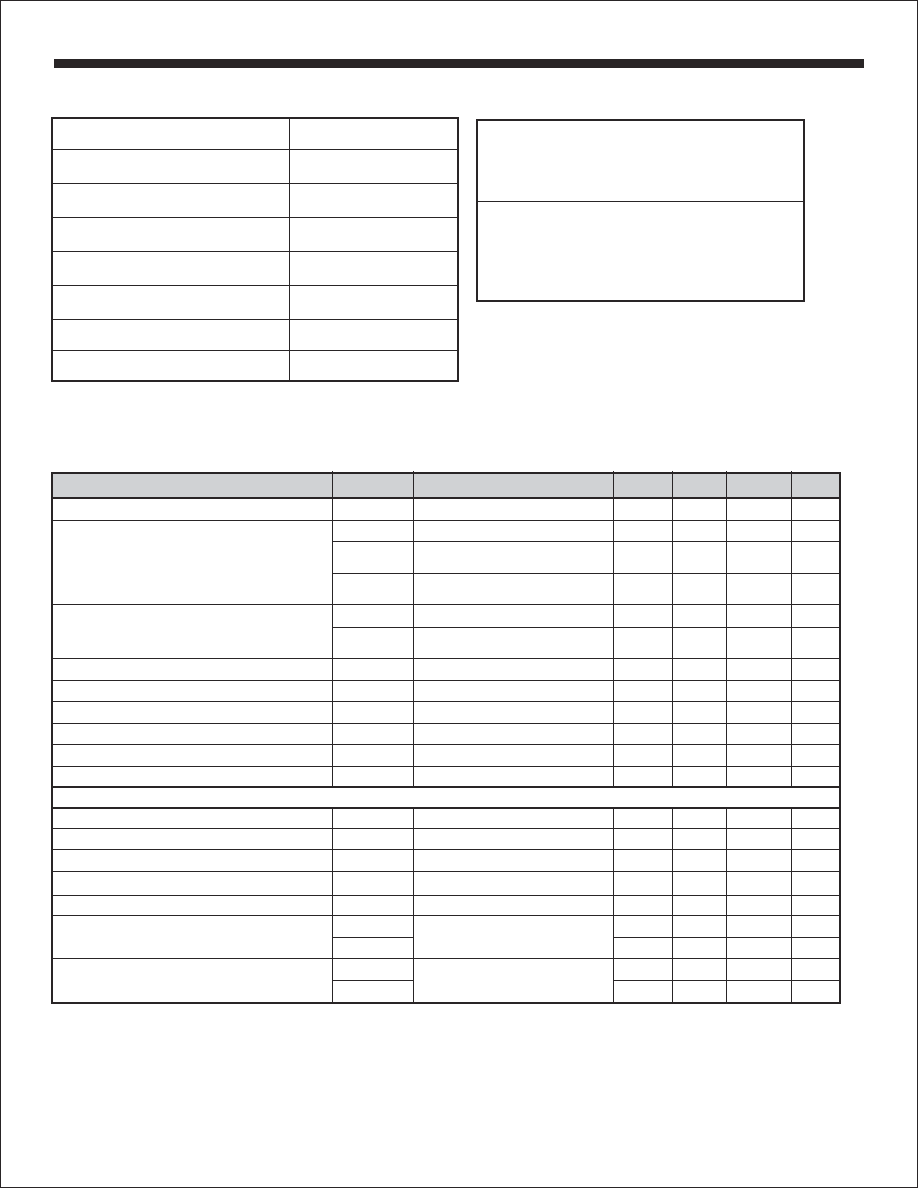

PIN DESCRIPTIONS

PIN

SYMBOL

FUNCTION

DESCRIPTION

1, 40, 50, 55

GNDA

power supply

Ground for channel A (Connect ALL pins)

2, 3

BUSA OUT

analog output

MIL-STD-1533 bus driver A, positive signal

4, 5, 44, 52, 53, 60, 61

VDDA

power supply

+5 volt power for channel A (Connect ALL pins)

6, 7

OUT

analog output

8, 18, 23, 33

GNDB

power supply

Ground for channel B (Connect ALL pins)

12, 20, 21, 28, 29, 36, 37

VDDB

14

16

25

BUSB IN

analog input

26

30

31

32

34, 35

BUSB OUT

38, 39

BUSA

MIL-STD-1533 bus driver A, negative signal

power supply

+5 volt power for channel B (Connect ALL pins)

RXB

digital output

Receiver B output, non-inverted

15

RXENB

digital input

Receiver B enable. If low, forces RXB and

low

digital output

Receiver B output, inverted

MIL-STD-1553 bus receiver B, positive signal

IN

analog input

MIL-STD-1553 bus receiver B, negative signal

TXINHB

digital input

Transmit inhibit, channel B. If high BUSB OUT,

OUT disabled

TXB

digital input

Transmitter B digital data input, non-inverted

digital input

Transmitter B digital data input, inverted

analog output

MIL-STD-1533 bus driver B, positive signal

OUT

analog output

MIL-STD-1533 bus driver B, negative signal

46

RXA

digital output

Receiver A output, non-inverted

47

RXENA

digital input

Receiver B enable. If low, forces RXB and

low

48

digital output

Receiver B output, inverted

57

BUSA IN

analog input

MIL-STD-1553 bus receiver A, positive signal

58

IN

analog input

MIL-STD-1553 bus receiver A, negative signal

62

TXINHA

digital input

Transmit inhibit, channel A. If high BUSA OUT,

OUT disabled

63

TXA

digital input

Transmitter A digital data input, non-inverted

64

digital input

Transmitter A digital data input, inverted

9 -11, 13, 17,19, 22, 24, 27

N/C

-

Not connected. May be left open or connected to power or ground

41 - 43, 45, 49, 51, 54, 56, 59

RXB

RXB

BUSB

BUSB

TXB

BUSB

RXB

RXA

BUSA

BUSA

TXA

HI-1569

HOLT INTEGRATED CIRCUITS

2

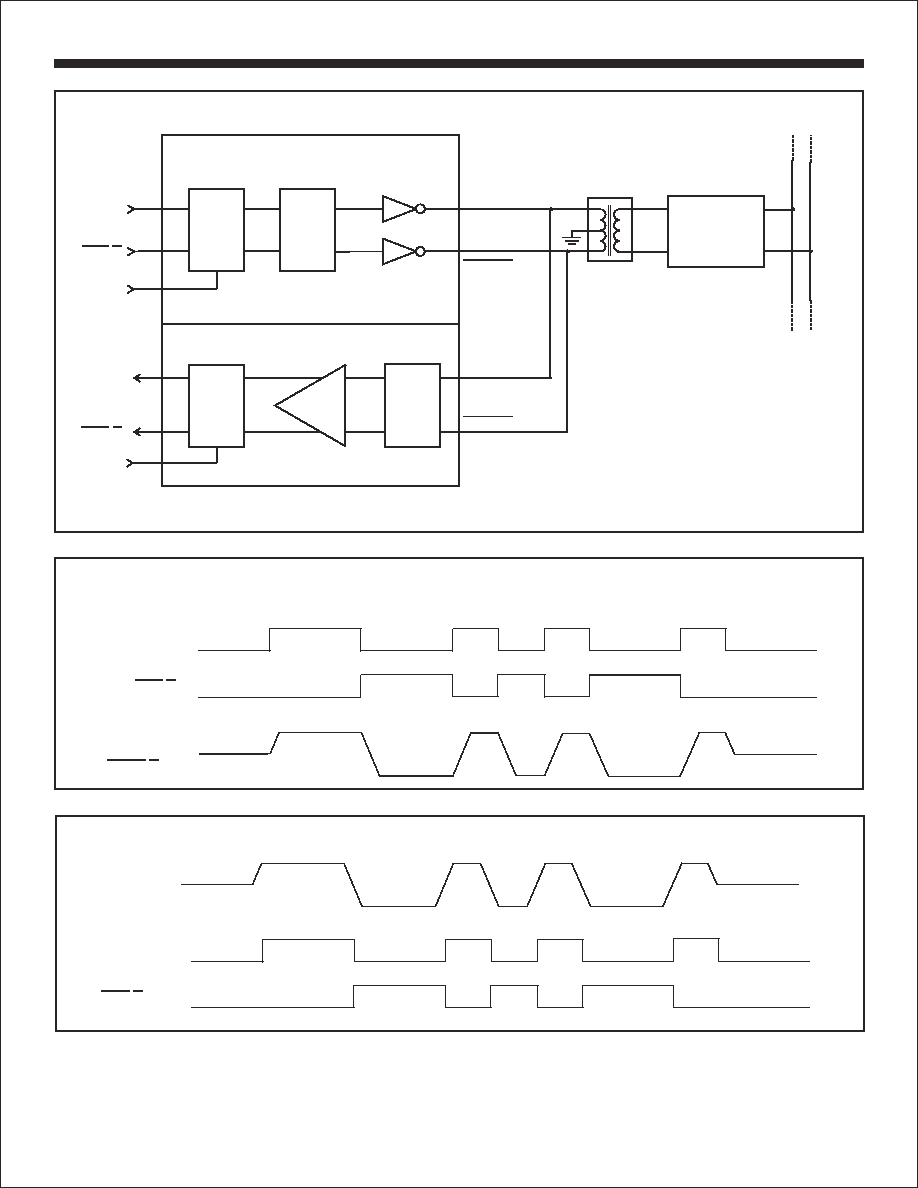

The HI-1569 data bus transceiver contains differential volt-

age source drivers and differential receivers. It is intended

for applications using a MIL-STD-1553 A/B data bus. The

device produces a trapezoidal output waveform during

transmission.

Data input to the device's transmitter section is from the

complementary CMOS /TTL inputs TXA/B and

/ .

The transmitter accepts Manchester II bi-phase data and

converts it to differential voltages on

The transceiver outputs are either direct or

transformer coupled to the MIL-STD-1553 data bus. Both

coupling methods produce a nominal voltage on the bus of

7.5 volts peak to peak.

TRANSMITTER

TXA B

BUSA/B OUT and

/

The transmitter is automatically inhibited and placed in the

high impedance state when both TXA/B and

/ are ei-

ther at a logic "1" or logic "0" simultaneously. A logic "1" ap-

plied to the TXINHA/B input will force the transmitter to the

high impedance state, regardless of the state of TXA/B and

/

BUSA B OUT.

TXA B

TXA B.

RECEIVER

The receiver accepts bi-phase differential data from the MIL-

STD-1553 bus through a direct or transformer coupled inter-

face. The receiver's differential input stage drives a filter and

threshold comparator that produces CMOS/TTL data at the

RXA/B and

/ output pins.

RXA B

Each set of receiver outputs can be independently forced to a

logic "0" by setting RXENA or RXENB low.

A direct coupled interface (see Figure 2) uses a 1:2.5 ratio

isolation transformer and two 55 ohm isolation resistors

between the transformer and the bus.

In a transformer coupled interface (see Figure 3), the

transceiver is connected to a 1:1.79 isolation transformer

which in turn is connected to a 1:1.4 coupling transformer. The

transformer coupled method also requires two coupling

resistors equal to 75% of the bus characteristic impedence

(Zo) between the coupling transformer and the bus.

MIL-STD-1553 BUS INTERFACE

FUNCTIONAL DESCRIPTION

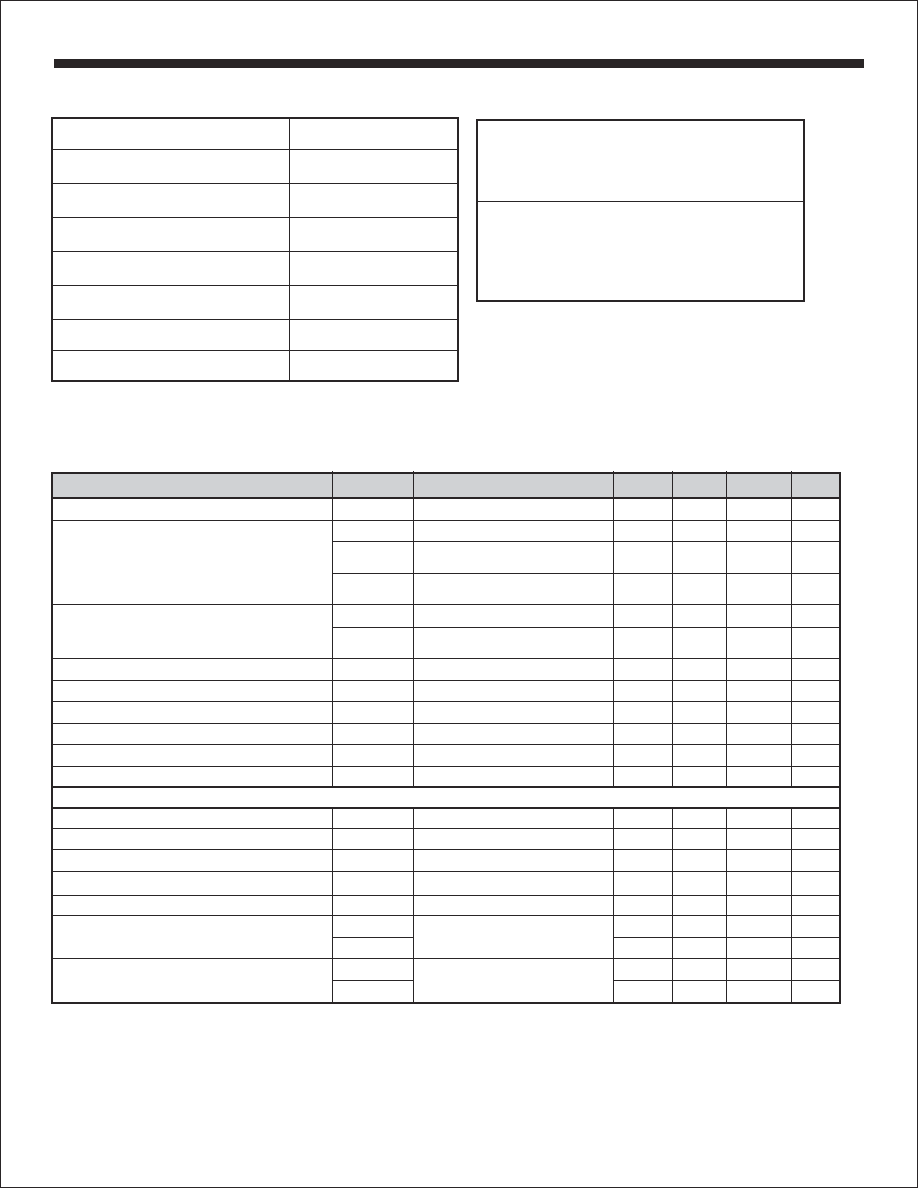

PARAMETER

SYMBOL

CONDITION

MIN

TYP

MAX

UNITS

Operating Voltage

VDD

4.75

5

5.25

V

Total Supply Current

ICC1

Not Transmitting

14

22

mA

ICC2

Transmit one channel @

340

mA

50% duty cycle

ICC3

Transmit one channel @

550

mA

100% duty cycle

Power Dissipation

PD1

Not Transmitting

0.11

W

PD2

Transmit one channel @

0.70

0.95

W

100% duty cycle

Min. Input Voltage

(HI)

V

Digital inputs

2.0

1.4

V

Max. Input Voltage

(LO)

V

Digital inputs

1.4

0.8

V

Min. Input Current

(HI)

I

V

= 4.9V, Digital inputs

20

�A

Max. Input Current

(LO)

I

V

= 0.1V, Digital inputs

-20

�A

Min. Output Voltage

(HI)

V

I

= -4mA, Digital outputs

4.0

V

Max. Output Voltage

(LO)

V

I

= 4.0mA, Digital outputs

0.4

V

Input resistance

R

Differential

20

Kohm

Input capacitance

C

Differential

5

pF

Common mode rejection ratio

CMRR

40

dB

Input Level

V

Differential

9

Vp-p

Input common mode voltage

V

-5.0

5.0

V-pk

Threshold Voltage - Direct-coupled

Detect

1.15

20.0

No Detect

0.28

Theshold Voltage -

Detect

0.86

14.0

No Detect

0.20

200

400

V

1 Mhz Sine Wave

Vp-p

V

(Measured at Point "A " in Figure 2)

Vp-p

Transformer-coupled

V

1 MHz Sine Wave

Vp-p

V

(Measured at Point "A " in Figure 3)

Vp-p

=

IH

IL

IH

IH

IL

IL

OH

OUT

IH

OUT

D

RECEIVER

(Measured at Point "A " in Figure 2 unless otherwise specified)

IN

IN

IN

ICM

THD

THND

THD

THND

D

T

NOTE:

Stresses above absolute maximum

ratings or outside recommended operating

conditions may cause permanent damage to the

device. These are stress ratings only. Operation

at the limits is not recommended.

Supply voltage (

Logic input voltage range

Power dissipation at 25�C

1.0 W

Solder Temperature

275�C for 10 sec.

Junction Temperature

175�C

Storage Temperature

-65�C to +150�C

VDD)

-0.3 V to +7 V

-0.3 V dc to +5.5 V

Receiver differential voltage

10 Vp-p

Driver peak output current

+1.0 A

ABSOLUTE MAXIMUM RATINGS

RECOMMENDED OPERATING CONDITIONS

Supply Voltage

Temperature Range

Industrial Screening.........-40�C to +85�C

Hi-Temp Screening........-55�C to +125�C

Military Screening..........-55�C to +125�C

VDD....................................... 5V... �5%

DC ELECTRICAL CHARACTERISTICS

VDD = 5.0V, GND = 0V, T = Operating Temperature Range (unless otherwise specified).

A

HI-1569

HOLT INTEGRATED CIRCUITS

4

PARAMETER

SYMBOL

CONDITION

MIN

TYP

MAX

UNITS

Output Voltage

Direct coupled

35 ohm load

6.0

9.0

Vp-p

(Measured at Point "A " in Figure 2)

70

20.0

27.0

Vp-p

Output Noise

V

Differential, inhibited

10.0

mVp-p

Output Dynamic Offset Voltage

V

-90

90

mV

-250

250

mV

Output resistance

R

Differential, not transmitting

10

Kohm

Output Capacitance

C

1 MHz sine wave

15

pF

TRANSMITTER

(Measured at Point "A " in Figure 2 unless otherwise specified)

D

D

V

Transformer coupled

V

ohm load

(Measured at Point "A " in Figure 3)

Direct coupled

35 ohm load

(Measured at Point "A " in Figure 2)

Transformer coupled

V

70 ohm load

(Measured at Point "A " in Figure 3)

OUT

OUT

DYN

T

D

T

ON

DYN

OUT

OUT

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Receiver Enable Delay

tREN

From RXENA/B rising or falling edge to

40

ns

RXA/B or

Driver Delay

tDT

TXA/B, TXA/B to BUSA/B OUT,

OUT

150

ns

Rise time

tr

35 ohm load

100

300

ns

Fall Time

tf

35 ohm load

100

300

ns

Inhibit Delay

tDI-H

Inhibited output

100

ns

tDI-L

Active output

150

ns

RECEIVER

TRANSMITTER

(Measured at Point "A " in Figure 2)

(Measured at Point "A " in Figure 2)

D

D

Receiver Delay

tDR

From input zero crossing to RXA/B or

450

ns

RXA/B

RXA/B

BUSA/B

DC ELECTRICAL CHARACTERISTICS (cont.)

VDD = 5.0V, GND = 0V, T = Operating Temperature Range (unless otherwise specified).

A

AC ELECTRICAL CHARACTERISTICS

VDD = 5.0V, GND = 0V, T =Operating Temperature Range (unless otherwise specified).

A

TXA/B

TXA/B

TXINHA/B

TRANSMITTER

RECEIVER

1:2.5

Point "A "

D

55

W

55

W

35

W

2.5:1

55

W

55

W

35

W

RXENA/B

BUSA/B OUT

BUSA/B OUT

RXA/B

RXA/B

Figure 2. Direct Coupled Test Circuits

HI-1569

Isolation

Transformer

Isolation

Transformer

Point "A "

D

HOLT INTEGRATED CIRCUITS

5