| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ICS950812 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Integrated

Circuit

Systems, Inc.

ICS950812

0542G--08/21/03

Block Diagram

Recommended Application:

CK-408 clock with Buffered/Unbuffered mode supporting

Almador, Brookdale, ODEM, and Montara-G chipsets with

PIII/P4 processor. Programmable for group to group skew.

Output Features:

∑

3 Differential CPU Clock Pairs @ 3.3V

∑

7 PCI (3.3V) @ 33.3MHz including 2 early PCI clocks

∑

3 PCI_F (3.3V) @ 33.3MHz

∑

1 USB (3.3V) @ 48MHz, 1 DOT (3.3V) @ 48MHz

∑

1 REF (3.3V) @ 14.318MHz

∑

5 3V66 (3.3V) @ 66.6MHz

∑

1 VCH/3V66 (3.3V) @ 48MHz or 66.6MHz

∑

3 66MHz_OUT/3V66 (3.3V) @ 66.6MHz_IN or 66.6MHz

Features:

∑

Provides standard frequencies and additional 5%

and 10% over-clocked frequencies

∑

Supports spread spectrum modulation:

No spread, Center Spread (±0.35%, ±0.5%,

or ±0.75%), or Down Spread (-0.5%, -1.0%, or -1.5%)

∑

Offers adjustable PCI early clock via latch inputs

∑

Selectable 1X or 2X strength for REF via I

2

C interface

∑

Efficient power management scheme through PD#,

CPU_STOP# and PCI_STOP#.

∑

Uses external 14.318MHz crystal

∑

Stop clocks and functional control available through

I

2

C interface.

Key Specifications:

∑

CPU Output Jitter <150ps

∑

3V66 Output Jitter <250ps

∑

66MHz Output Jitter (Additive) (Buffered Mode) <100ps

∑

CPU Output Skew <100ps

Pin Configuration

Frequency Generator with 200MHz Differential CPU Clocks

Frequency Select

Note:

Almador board level designs MUST use pin 22,

66MHZ_OUT1, as the feedback connection from the

clock buffer path to the Almador (GMCH) chipset.

66MHz_OU

T (2:0)

66MHz_IN

PCICLK_F

3V66 (4:2)

3V66_5

PCICLK

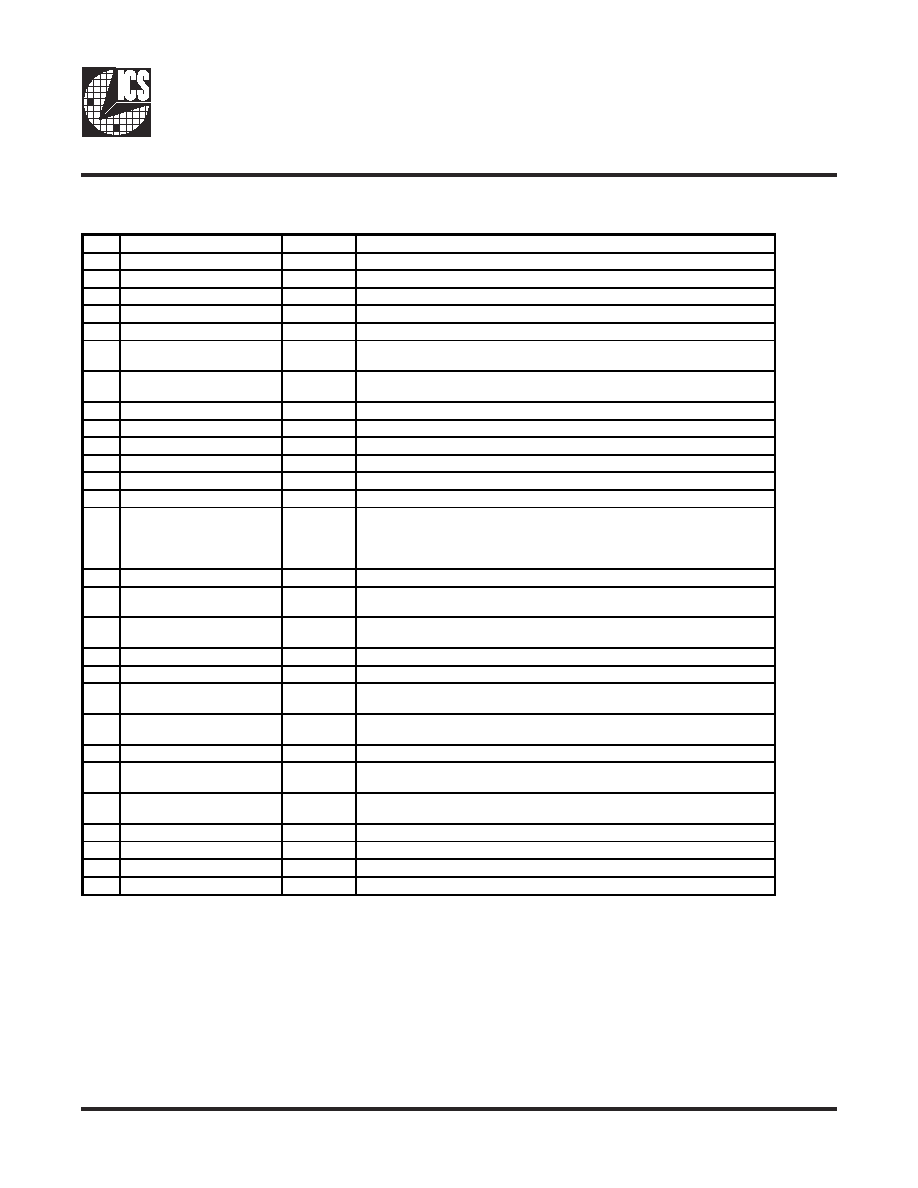

FS2 FS1 FS0

MHz

MHz

MHz

MHz

MHz

0

0

0

66.66

66.66

66.66

66.66

33.33

0

0

1

100.00

66.66

66.66

66.66

33.33

0

1

0

200.00

66.66

66.66

66.66

33.33

0

1

1

133.33

66.66

66.66

66.66

33.33

1

0

0

66.66

66.66

66MHz_IN

Input

66MHz_IN/2

1

0

1

100.00

66.66

66MHz_IN

Input

66MHz_IN/2

1

1

0

200.00

66.66

66MHz_IN

Input

66MHz_IN/2

1

1

1

133.33

66.66

66MHz_IN

Input

66MHz_IN/2

CPUCLK

3V66

Bit

PLL2

PLL1

Spread

Spectrum

3V66_5/66MHz_IN

3V66_3/66MHz_OUT1

3V66_(4,2)/66MHz_OUT(2,0)

48MHz_USB

48MHz_DOT

X1

X2

XTAL

OSC

3V66

DIVDER

PD#

CPU_STOP#

PCI_STOP#

MULTSEL

SDATA

SCLK

FS (5:0)

I REF

Control

Logic

Config.

Reg.

REF

3V66_0

CPU

DIVDER

3

3

CPUCLKT (2:0)

CPUCLKC (2:0)

Stop

3V66_1/VCH_CLK

PCICLK (6:4, 2, 0)

PCI

DIVDER

3

7

PCICLK_F (2:0)

Stop

E_PCICLK(1,3)/PCICLK(1,3)

2

V

TT

_PWRGD#

VDDREF

1

56 REF

X1

2

55 FS1

X2

3

54 FS0

GND

4

53 CPU_STOP#*

PCICLK_F0

5

52 CPUCLKT0

PCICLK_F1

6

51 CPUCLKC0

PCICLK_F2

7

50 VDDCPU

VDDPCI

8

49 CPUCLKT1

GND

9

48 CPUCLKC1

PCICLK0 10

47 GND

**E_PCICLK1/PCICLK1 11

46 VDDCPU

PCICLK2 12

45 CPUCLKT2

**E_PCICLK3/PCICLK3 13

44 CPUCLKC2

VDDPCI 14

43 MULTSEL*

GND 15

42 IREF

PCICLK4 16

41 GND

PCICLK5 17

40 FS2

PCICLK6 18

39 48MHz_USB/FS3

**

VDD3V66 19

38 48MHz_DOT

GND 20

37 VDD48

66MHZ_OUT0/3V66_2 21

36 GND

66MHZ_OUT1/3V66_3 22

35 3V66_1/VCH_CLK/FS4

**

66MHZ_OUT2/3V66_4 23

34 PCI_STOP#*

66MHZ_IN/3V66_5 24

33 3V66_0/FS5

**

*PD# 25

32 VDD3V66

VDDA 26

31 GND

GND 27

30 SCLK

Vtt_PWRGD# 28

29 SDATA

56-Pin 300mil SSOP

6.10 mm. Body, 0.50 mm. pitch TSSOP

*

These inputs have 120K internal pull-up resistors to VDD.

**

Internal pull-down resistors to ground.

I

C

S950812

2

ICS950812

0542G--08/21/03

Pin Configuration

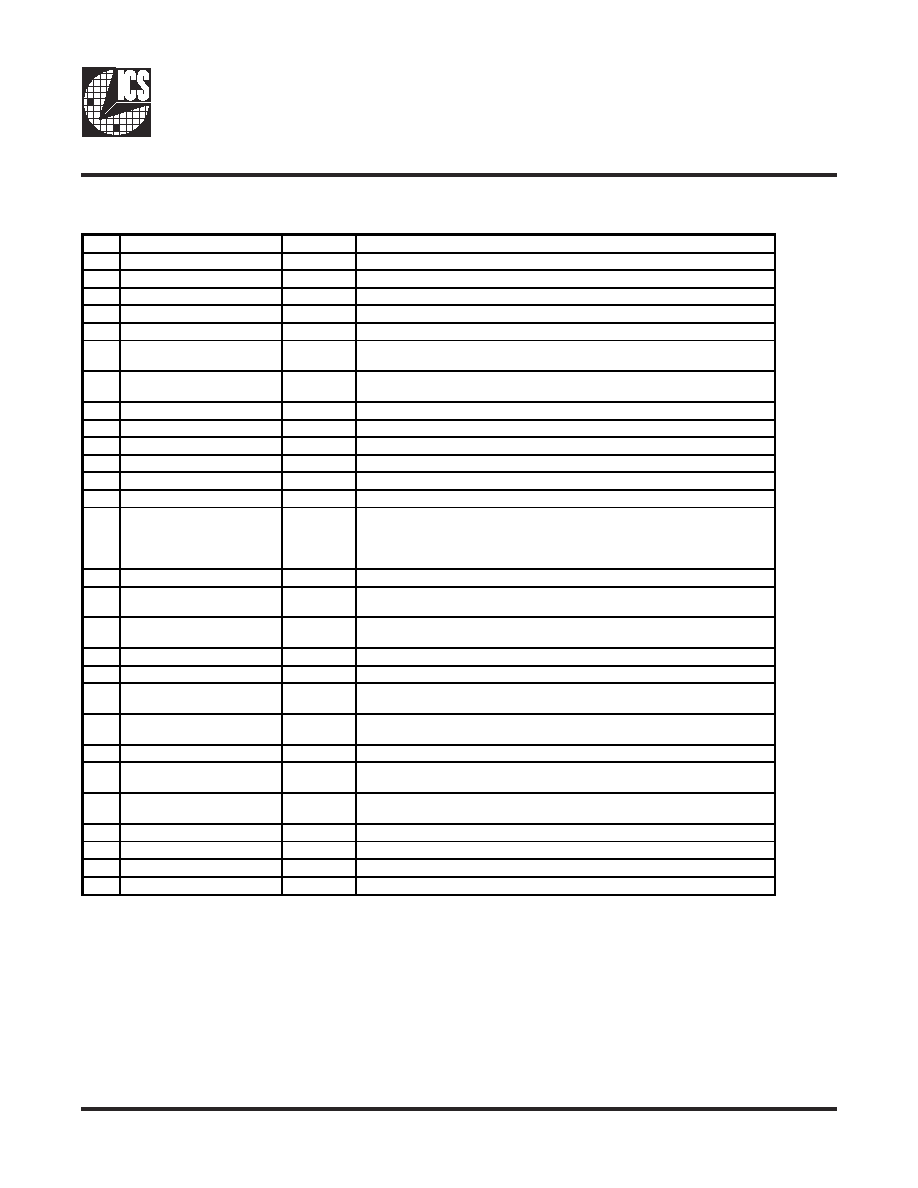

PIN # PIN NAME

PIN TYPE

DESCRIPTION

1

VDDREF

PWR

Ref, XTAL power supply, nominal 3.3V

2

X1

IN

Crystal input, Nominally 14.318MHz.

3

X2

OUT

Crystal output, Nominally 14.318MHz

4

GND

PWR

Ground pin.

5

PCICLK_F0

OUT

Free running PCI clock not affected by PCI_STOP# .

6

PCICLK_F1

OUT

Free running PCI clock not affected by PCI_STOP# .

7

PCICLK_F2

OUT

Free running PCI clock not affected by PCI_STOP# .

8

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

9

GND

PWR

Ground pin.

10

PCICLK0

OUT

PCI clock output.

11

**E_PCICLK1/PCICLK1

I/O

Early/Normal PCI clock output latched at power up.

12

PCICLK2

OUT

PCI clock output.

13

**E_PCICLK3/PCICLK3

I/O

Early/Normal PCI clock output latched at power up.

14

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

15

GND

PWR

Ground pin.

16

PCICLK4

OUT

PCI clock output.

17

PCICLK5

OUT

PCI clock output.

18

PCICLK6

OUT

PCI clock output.

19

VDD3V66

PWR

Power pin for the 3V66 clocks.

20

GND

PWR

Ground pin.

21

66MHZ_OUT0/3V66_2

OUT

3.3V 66.66MHz clock output selected via buffered or internal VCO.

22

66MHZ_OUT1/3V66_3

OUT

3.3V 66.66MHz clock output selected via buffered or internal VCO.

23

66MHZ_OUT2/3V66_4

OUT

3.3V 66.66MHz clock output selected via buffered or internal VCO.

24

66MHZ_IN/3V66_5

I/O

3.3V 66.66MHz clock from internal VCO, 66MHZ input to 66MHz output and

PCI.

25

*PD#

IN

Asynchronous active low input pin used to power down the device into a low

power state. The internal clocks are disabled and the VCO and the crystal

are stopped. The latency of the power down will not be greater than 1.8ms.

26

VDDA

PWR

3.3V power for the PLL core.

27

GND

PWR

Ground pin.

28

Vtt_PWRGD#

IN

This 3.3V LVTTL input is a level sensitive strobe used to determine when

latch inputs are valid and are ready to be sampled. This is an active low

input.

3

ICS950812

0542G--08/21/03

Pin Configuration (Continued)

PIN # PIN NAME

PIN TYPE

DESCRIPTION

29

SDATA

I/O

Data pin for I2C circuitry 5V tolerant

30

SCLK

IN

Clock pin of I2C circuitry 5V tolerant

31

GND

PWR

Ground pin.

32

VDD3V66

PWR

Power pin for the 3V66 clocks.

33

3V66_0/FS5**

I/O

Frequency select latch input pin / 3.3V 66.66MHz clock output.

34

PCI_STOP#*

IN

Stops all PCICLKs besides the PCICLK_F clocks at logic 0 level, when input

low

35

3V66_1/VCH_CLK/FS4**

I/O

Frequency select latch input pin / 3.3V 66.66MHz clock output / 48MHz

VCH clock output.

36

GND

PWR

Ground pin.

37

VDD48

PWR

Power pin for the 48MHz output.3.3V

38

48MHz_DOT

OUT

48MHz clock output.

39

48MHz_USB/FS3**

I/O

Frequency select latch input pin / 3.3V 48MHz clock output.

40

FS2

IN

Frequency select pin.

41

GND

PWR

Ground pin.

42

IREF

OUT

This pin establishes the reference current for the differential current-mode

output pairs. This pin requires a fixed precision resistor tied to ground in

order to establish the appropriate current. 475 ohms is the standard value.

43

MULTSEL*

IN

3.3V LVTTL input for selection the current multiplier for CPU outputs

44

CPUCLKC2

OUT

Complimentary clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

45

CPUCLKT2

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

46

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

47

GND

PWR

Ground pin.

48

CPUCLKC1

OUT

Complimentary clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

49

CPUCLKT1

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

50

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

51

CPUCLKC0

OUT

Complimentary clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

52

CPUCLKT0

OUT

True clock of differential pair CPU outputs. These are current mode

outputs. External resistors are required for voltage bias.

53

CPU_STOP#*

IN

Stops all CPUCLK besides the free running clocks

54

FS0

IN

Frequency select pin.

55

FS1

IN

Frequency select pin.

56

REF

OUT

14.318 MHz reference clock.

4

ICS950812

0542G--08/21/03

Frequency Select Table 2

Frequency Select Table 1

66MHz_OU

T (2:0)

66MHz_IN

FS

2

FS

1

FS

0

3V66 (4:2)

3V66 _5

0

0

0

66.66

66.66

66.66

66.66

33.33

14.318

48.008

0

0

1

100.00

66.66

66.66

66.66

33.33

14.318

48.008

0

1

0

200.00

66.66

66.66

66.66

33.33

14.318

48.008

0

1

1

133.33

66.66

66.66

66.66

33.33

14.318

48.008

1

0

0

66.66

66.66

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

0

1

100.00

66.66

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

1

0

200.00

66.66

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

1

1

133.33

66.66

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

0

0

0

70.00

70.00

70.00

70.00

35.00

14.318

48.008

0

0

1

105.00

70.00

70.00

70.00

35.00

14.318

48.008

0

1

0

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

0

1

1

140.00

70.00

70.00

70.00

35.00

14.318

48.008

1

0

0

70.00

70.00

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

0

1

105.00

70.00

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

1

0

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

1

1

1

140.00

70.00

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

5% Overclocking

0

0

0

73.32

73.32

73.32

73.32

36.66

14.318

48.008

0

0

1

110.00

73.32

73.32

73.32

36.66

14.318

48.008

0

1

0

Test/2

Test/4

Test/4

Test/4

Test/8

Test

Test/2

Test

0

1

1

146.60

73.32

73.32

73.32

36.66

14.318

48.008

1

0

0

73.32

73.32

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

0

1

110.00

73.32

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

1

1

0

Test/2

Test/4

Test/4

Test/4

Test/8

Test

Test/2

Test

1

1

1

146.60

73.32

66MHz_IN

Input

66MHz_IN/2

14.318

48.008

10% Overclocking

10% Overclocking

10% Overclocking

Standard Clocking

Standard Clocking

5% Overclocking

5% Overclocking

110

(See table 2)

111

(See table 2)

REF MHz

USB/DOT

MHz

Clocking Mode

Freq Sel

CPU MHz

3V66 MHz

FS(5:3)

PCI MHz

From

000

to

101

(See table 2)

FS

5

FS

4

FS

3

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

+/-0.35%, Center Spread

0 to -1.5%, Down Spread

+/-0.5%, Center Spread

+/-0.75%, Center Spread

+/-0.35%, Center Spread

10% Overclocking

Clocking Mode

No Spread (default)

or +/-0.4%

0 to -0.5%, Down Spread

0 to -1.0%, Down Spread

Standard Clocking

Standard Clocking

Standard Clocking

Standard Clocking

CPU, 3V66, 66MHz_OUT,

66MHz_IN, PCI

5% Overclocking

Freq Sel

Standard Clocking

Standard Clocking

Note: To enable spread, Byte 0 Bit 7 must be set to 1.

5

ICS950812

0542G--08/21/03

Maximum Allowed Current

Host Swing Select Functions

MULTSEL

0

1

PCI Select Functions

Note:

*

Approximate values

Max 3.3V supply consumption

Max discrete cap loads,

Vdd = 3.465V

All static inputs = Vdd or GND

40mA

280mA

Condition

Powerdown Mode

(PD# = 0)

Active Full

Board Target

Trace/Term Z

Reference R,

Iref = V

DD

/3*Rr

Rr = 221 1%,

Iref = 5.00mA

Rr = 475 1%,

Iref = 2.32mA

50 ohms

50 ohms

Output

Current

Ioh = 4 * I REF

Ioh = 6 * I REF

1.0V @ 50 ohm

0.7V @ 50 ohm

Voh @ Z

E_PCICLK1 (11)

E_PCICLK3 (13)

E_PCICLK(3,1)

*

E_PCICLK1 = 10Kohm resistor.

0

0

0ns

0

1

0.5ns

1.0ns

1

1

1.5ns

E_PCICLK3 = 10Kohm resistor.

0 = No resistor

1 = 10Kohm pull-up to V

DD

.

1

0