| ÐлекÑÑоннÑй компоненÑ: EL5185 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1

®

FN7179

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2003. All Rights Reserved. Elantec is a registered trademark of Elantec Semiconductor, Inc.

All other trademarks mentioned are the property of their respective owners.

EL5185

4ns High-Speed Comparator

The EL5185 comparator is designed

for operation in single supply and dual

supply applications with 5V to 12V

between V

S

+ and V

S

-. For single supplies, the inputs can

operate from 0.1V below ground for use in ground-sensing

applications.

The output side of the comparator can be supplied from a

single supply of 2.7V to 5V. The rail-to-rail output swing

enables direct connection of the comparator to both CMOS

and TTL logic circuits.

The latch input of the EL5185 can be used to hold the

comparator output value by applying a low logic level to the

pin.

The EL5185 is available in the 8-pin SO package and is

specified for operation over the -40°C to +85°C temperature

range. Also available are dual (EL5285), window comparator

(EL5287), and quad (EL5485 and EL5486) versions.

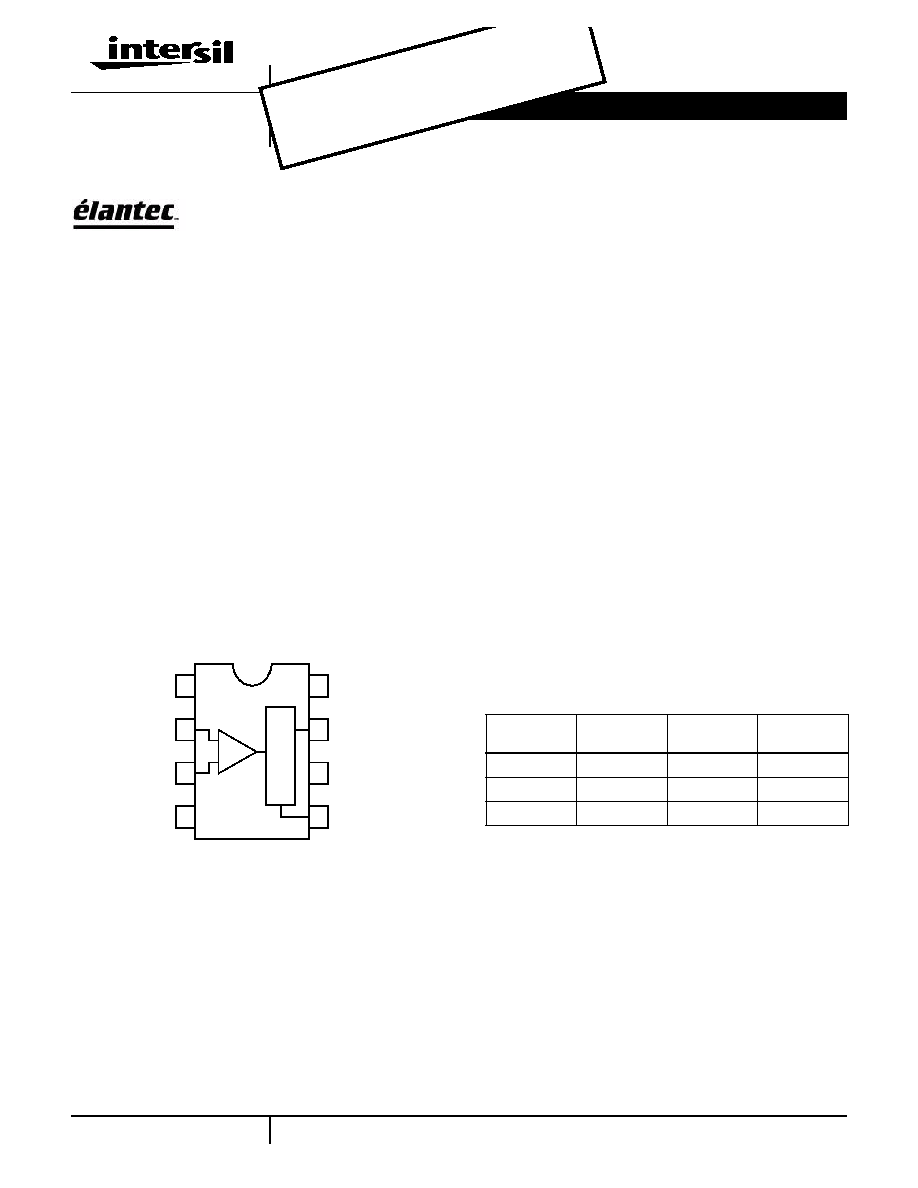

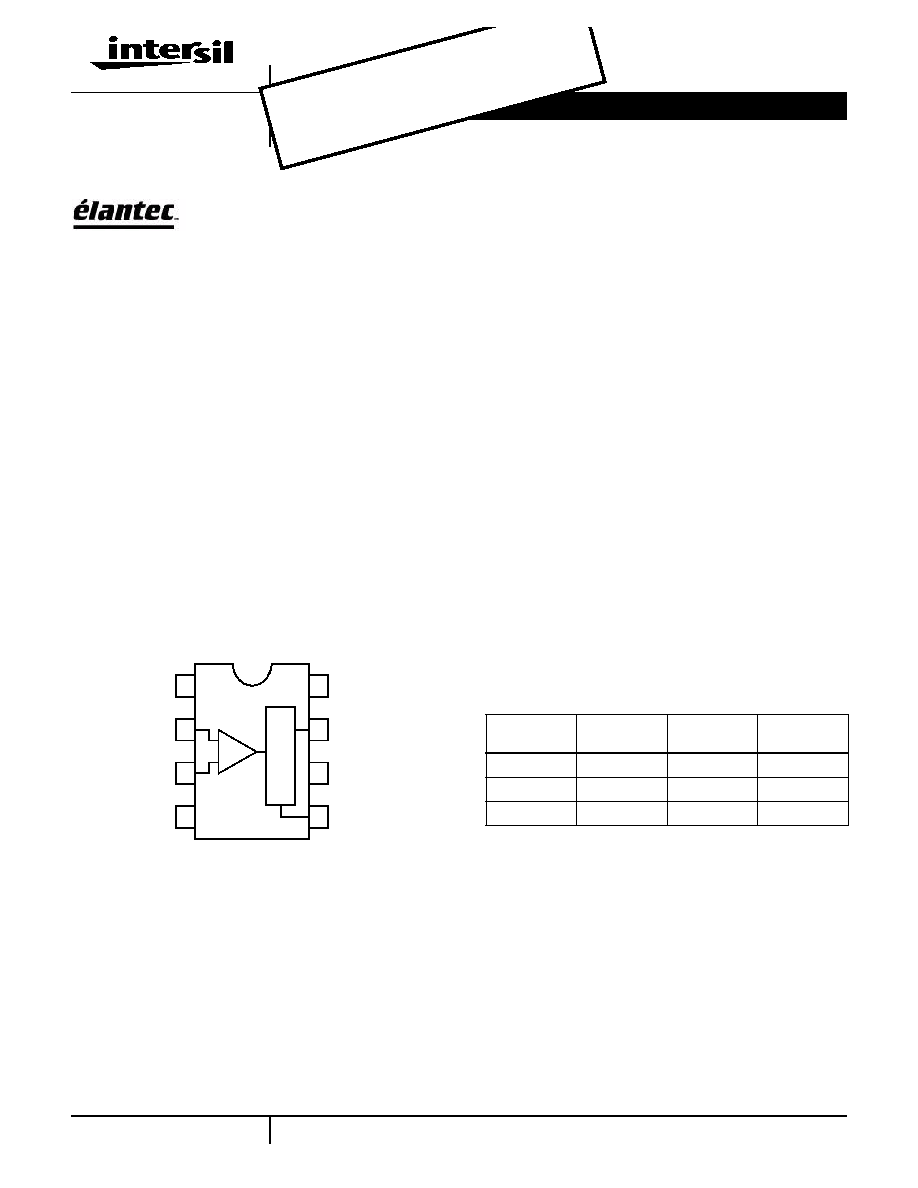

Pinout

Features

· 4ns typ. propagation delay

· 5V to 12V input supply

· +2.7V to +5V output supply

· True-to-ground input

· Rail-to-rail outputs

· Active low latch

· Dual available (EL5285)

· Window comparator (EL5287)

· Quad available (EL5485 & EL5486)

· Pin-compatible 8ns family available (EL5x81, EL5283 &

EL5482)

Applications

· Threshold detection

· High speed sampling circuits

· High speed triggers

· Line receivers

· PWM circuits

· High speed V/F converters

1

2

3

4

8

7

6

5

V

S

+

L

A

T

C

H

V

SD

OUT

GND

LATCH

IN+

IN-

V

S

-

EL5185

(8-PIN SO)

TOP VIEW

-

+

Ordering Information

PART

NUMBER

PACKAGE

TAPE & REEL

PKG. NO.

EL5185CS

8-Pin SO

-

MDP0027

EL5185CS-T7

8-Pin SO

7"

MDP0027

EL5185CS-T13

8-Pin SO

13"

MDP0027

Data Sheet

January 18, 2002

OBSO

LETE

PRO

DUCT

NO R

ECOM

MEND

ED R

EPLA

CEME

NT

conta

ct ou

r Tec

hnica

l Sup

port C

enter

at

1-888

-INTE

RSIL

or w

ww.in

tersil

.com

/tsc

2

Absolute Maximum Ratings

(T

A

= 25°C)

Analog Supply Voltage (V

S

+ to V

S

-) . . . . . . . . . . . . . . . . . . . +12.6V

Digital Supply Voltage (V

SD

to GND) . . . . . . . . . . . . . . . . . . . . .+7V

Differential Input Voltage . . . . . . . . . . .[(V

S

-) -0.2V] to [(V

S

+) +0.2V]

Common-mode Input Voltage . . . . . . .[(V

S

-) -0.2V] to [(V

S

+) +0.2V]

Latch Input Voltage . . . . . . . . . . . . . . . . . . . . -0.2V to [(V

SD

)

+0.2V]

Storage Temperature Range . . . . . . . . . . . . . . . . . . -65°C to +150°C

Ambient Operating Temperature . . . . . . . . . . . . . . . . -40°C to +85°C

Operating Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 125°C

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Curves

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests

are at the specified temperature and are pulsed tests, therefore: T

J

= T

C

= T

A

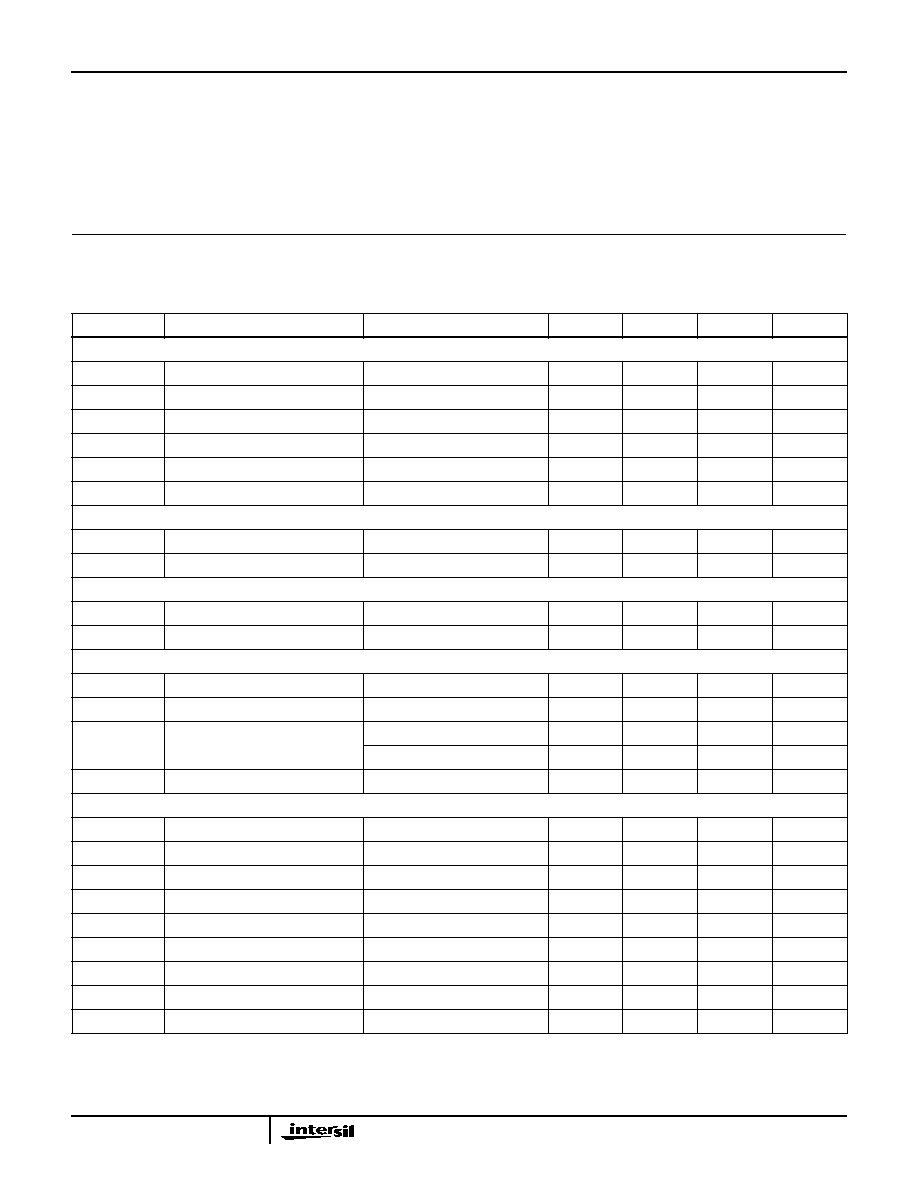

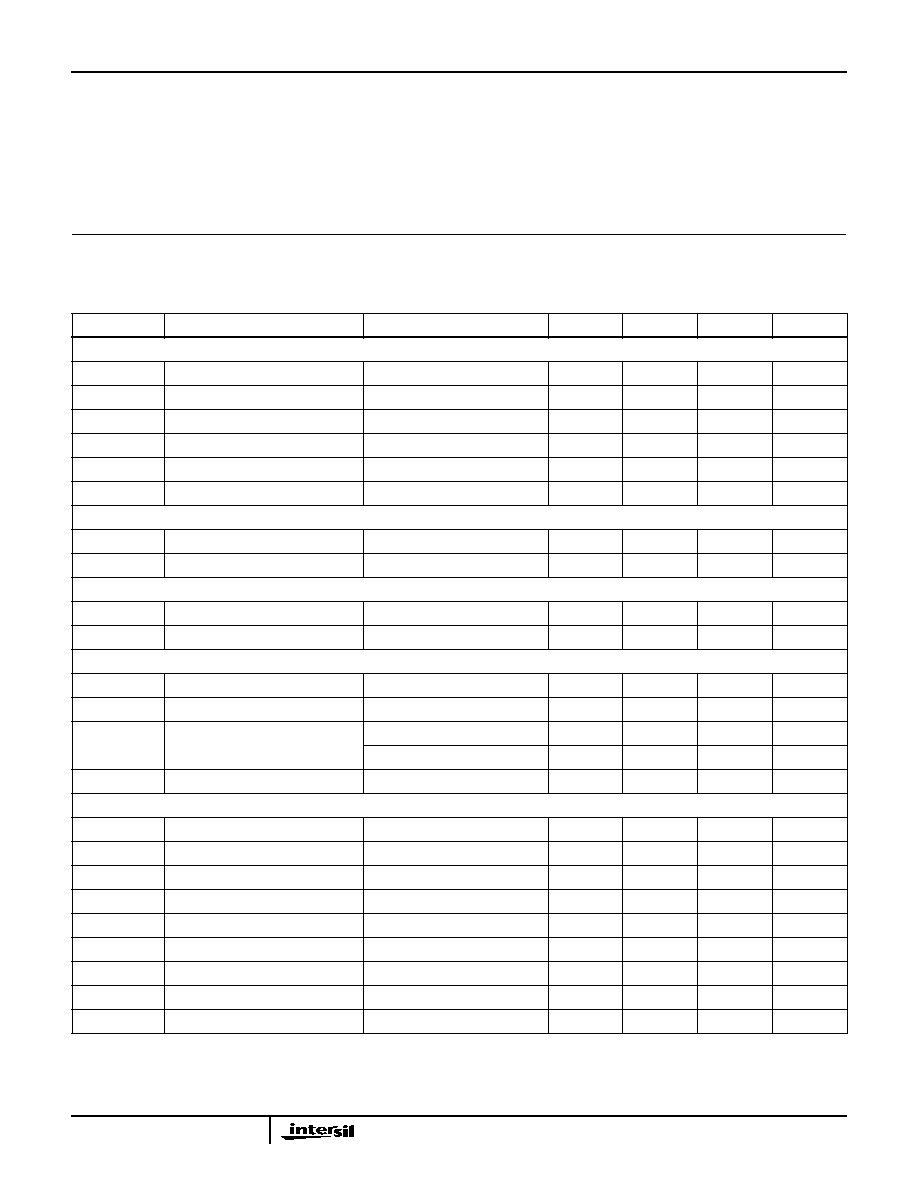

Electrical Specifications

V

S

= ±5V, V

SD

= 5V, R

L

= 2.3k

, T

A

= 25°C, unless otherwise specified.

PARAMETER

DESCRIPTION

CONDITION

MIN

TYP

MAX

UNIT

INPUT

V

OS

Input Offset Voltage

V

CM

= 0V, V

O

= 2.5V

1

4

mV

I

B

Input Bias Current

-10

-5

µA

C

IN

Input Capacitance

5

pF

I

OS

Input Offset Current

V

CM

= 0V, V

O

= 2.5V

-2.5

0.5

2.5

µA

V

CM

Input Voltage Range

(V

S

-) - 0.1

(V

S

+) - 2.25

V

CMRR

Common-mode Rejection Ratio

-5.1V < V

CM

< +2.75V

65

90

dB

OUTPUT

V

OH

Output High Voltage

V

IN

> 250mV

V

SD

- 0.6

V

SD

- 0.4

V

V

OL

Output Low Voltage

V

IN

> 250mV

GND + 0.25

GND + 0.5

V

DYNAMIC PERFORMANCE

t

PD

+

Positive Going Delay Time

V

IN

= 1V

P-P

, V

OD

= 50mV

4

6

ns

t

PD

-

Negative Going Delay Time

V

IN

= 1V

P-P

, V

OD

= 50mV

4

6

ns

SUPPLY

I

S

+

Positive Analog Supply Current

Per comparator

12

13.5

mA

I

S

-

Negative Analog Supply Current

Per comparator

7.5

8.5

mA

I

SD

Digital Supply Current at No Load

Per comparator, output high

5.5

6.5

mA

Per comparator, output low

0.9

1.2

mA

PSRR

Power Supply Rejection Ratio

55

80

dB

LATCH

V

LH

Latch Input Voltage High

2.0

V

V

LL

Latch Input Voltage Low

0.8

V

I

LH

Latch Input Current High

V

LH

= 3.0V

-30

-18

µA

I

LL

Latch Input Current Low

V

LL

= 0.3V

-30

-24

µA

t

D

+

Latch Disable to High Delay

4

ns

t

D

-

Latch Disable to Low Delay

4

ns

t

S

Minimum Setup Time

2

ns

t

H

Minimum Hold Time

1

ns

t

PW

(D)

Minimum Latch Disable Pulse Width

5

ns

EL5185

3

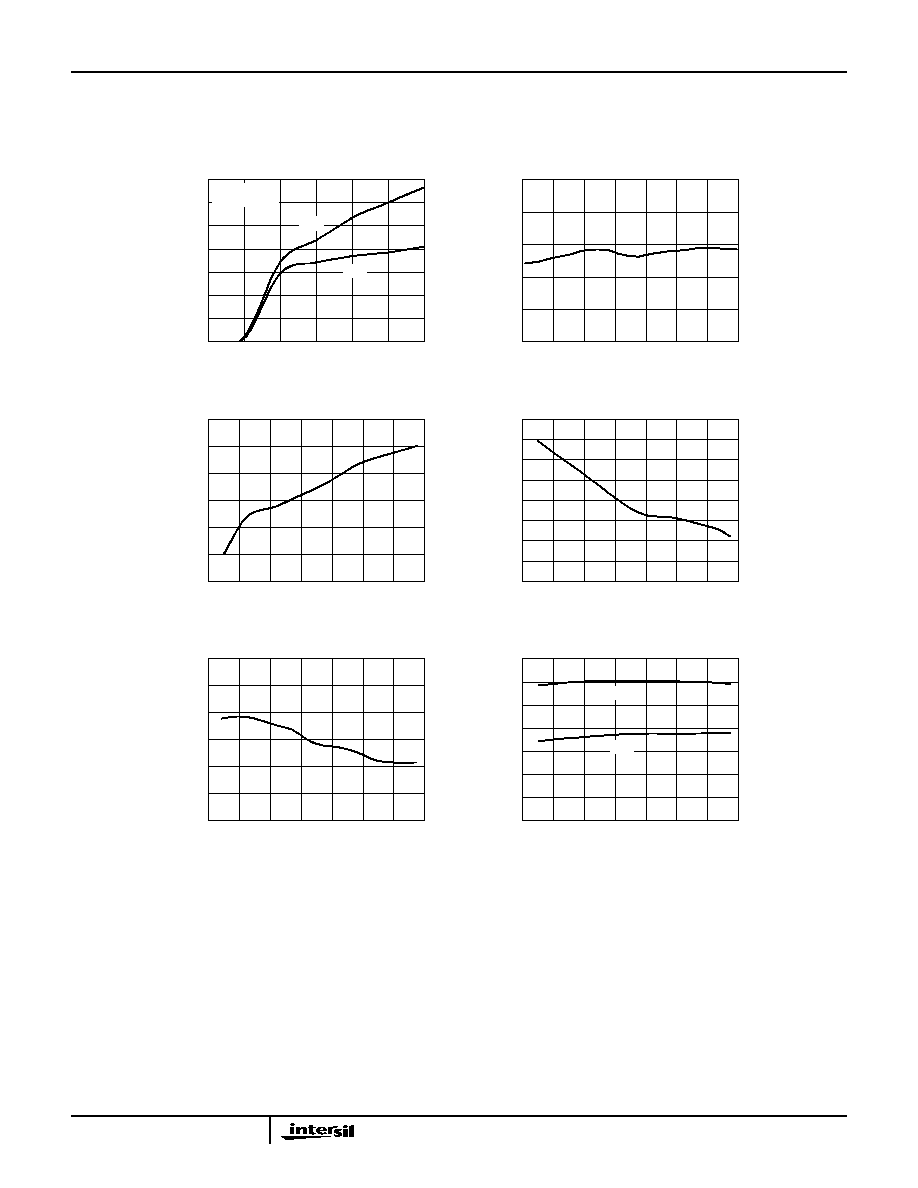

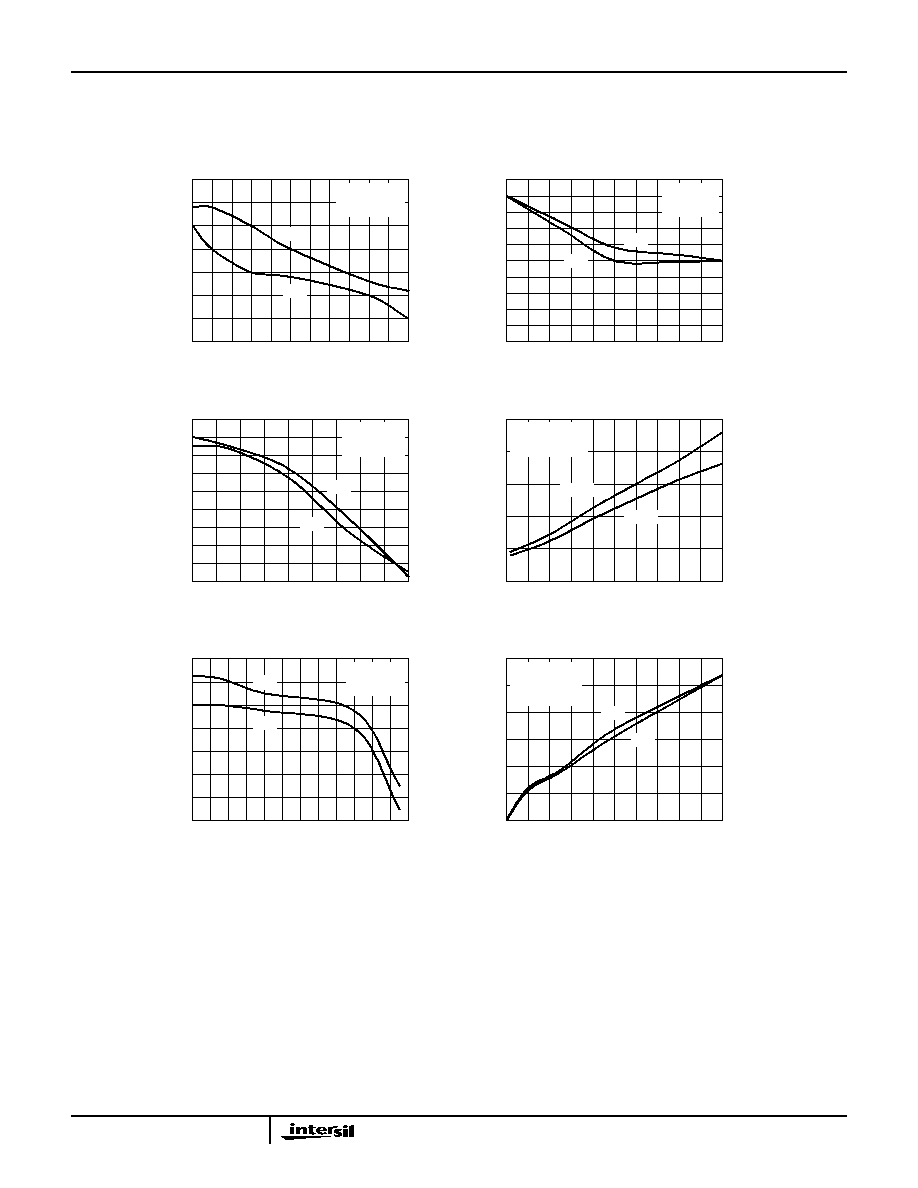

Typical Performance Curves

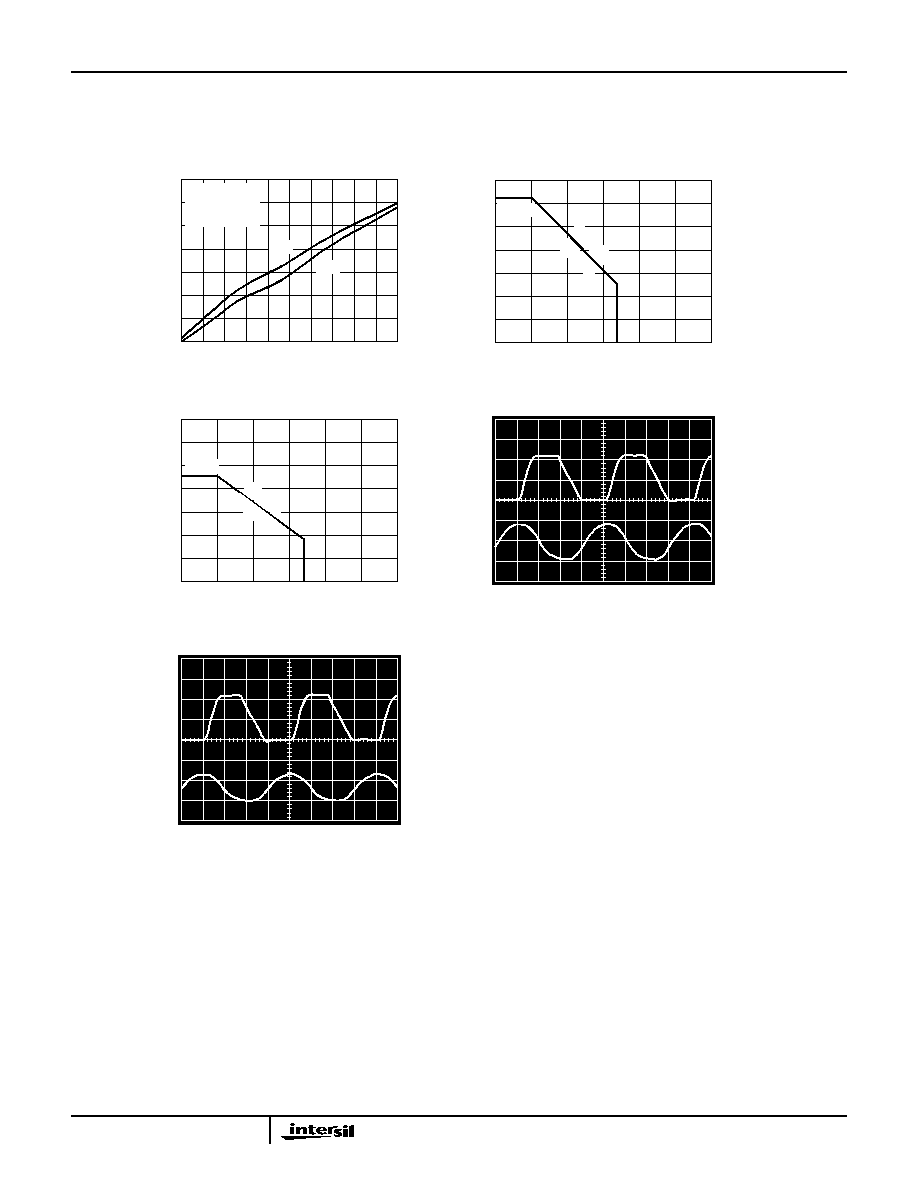

Offset Voltage vs Temperature

-50

-30

10

30

50

70

90

2.5

2

1

0.5

0

-0.5

Temperature (°C)

V

O

S

(

m

V

)

1.5

-10

Output Low Voltage vs Temperature

-50

-30

10

30

50

70

90

Temperature (°C)

V

O

L

(

V

)

-10

Output High Voltage vs Temperature

-50

-30

10

30

50

70

90

Temperature (°C)

V

O

H

(

V

)

-10

Input Bias Current vs Temperature

-50

-30

30

50

90

9

8

4

3

2

1

Temperature (°C)

I

B

(

µ

A

)

6

-10

10

70

7

5

Supply Current vs Supply Voltage

14

12

10

8

6

4

2

0

0

1

2

3

4

5

6

±V

S

(V)

I

S

(

m

A

)

I

S

+

I

S

-

V

IN

=-50mV

R

L

=2.3k

Supply Current vs Temperature (per comparator)

14

12

10

8

6

4

2

0

-50

-30

10

30

50

70

90

Temperature (°C)

S

u

p

p

l

y

C

u

r

r

e

n

t

(

m

A

)

I

S

+

I

S

-

-10

0.4

0.1

0.2

0.3

4.8

4.4

4.2

4

5

4.6

EL5185

4

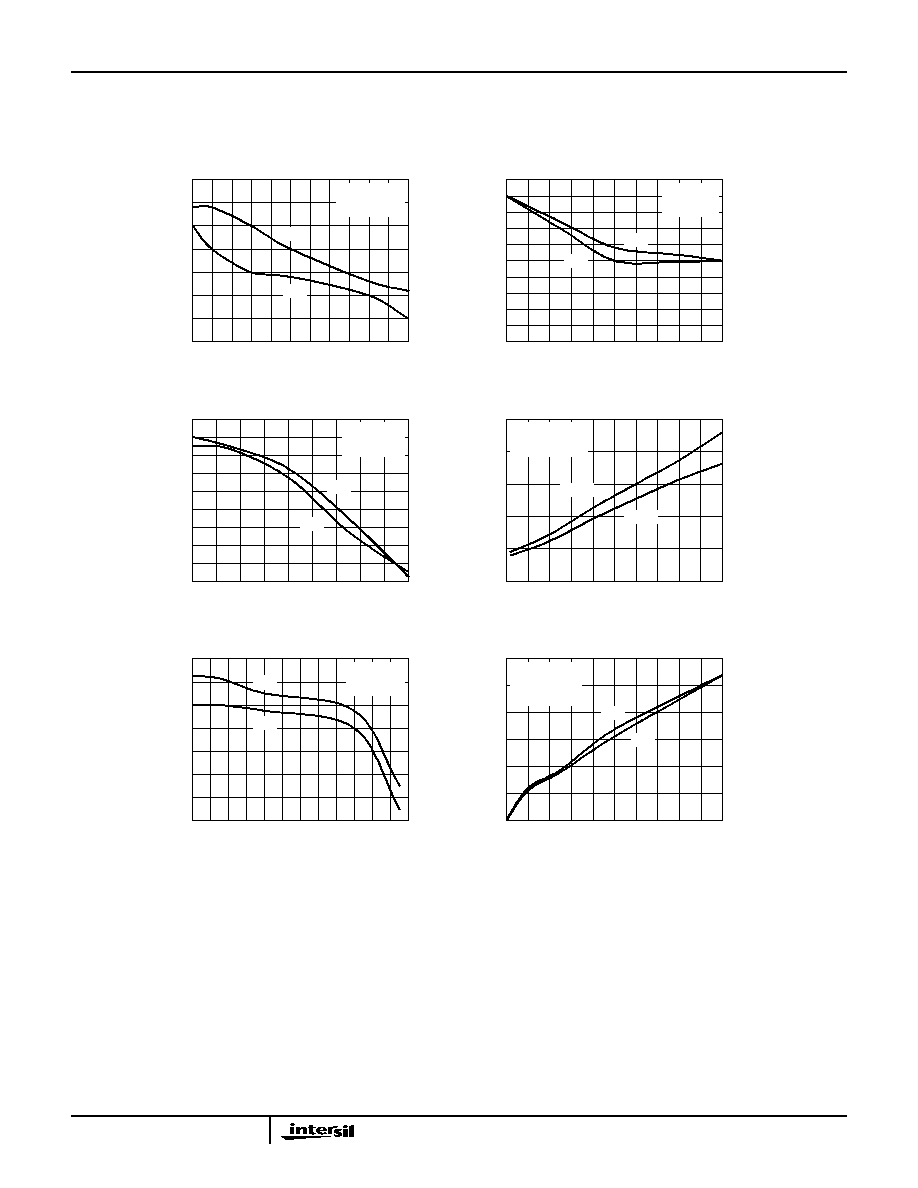

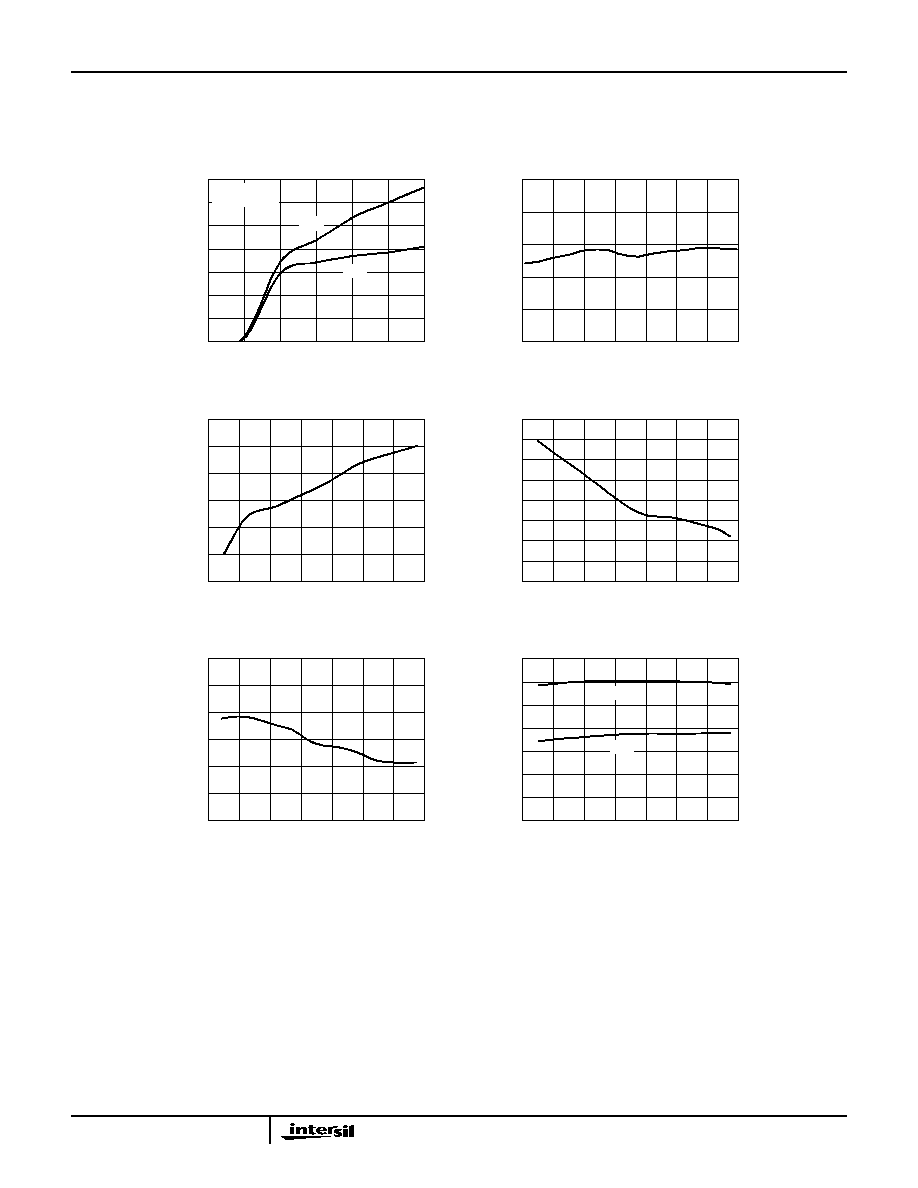

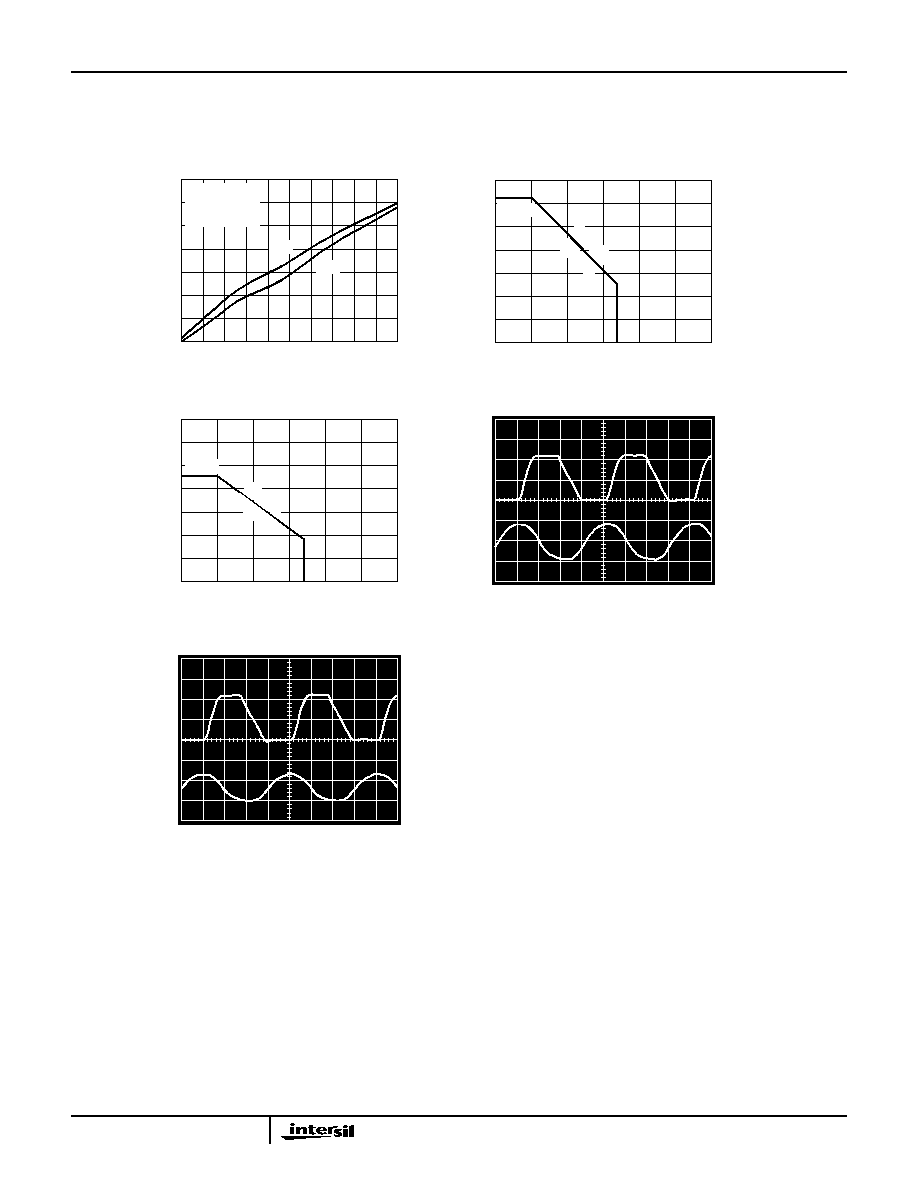

Typical Performance Curves

(Continued)

Digital Supply Current vs Switching Frequency

(per comparator)

0

20

40

50

25

20

10

0

Frequency (MHz)

I

S

D

(

m

A

)

15

10

5

30

V

S

= ±5V

T

A

= 25°C

R

L

= 2.3k

V

SD

=5V

V

SD

=3V

Propagation Delay vs Overdrive

V

IN

= 1V

STEP

4.2

4.1

4

3.9

3.8

3.7

3.6

3.5

50 100

200

300

400

500

600

V

OD

(mV)

D

e

l

a

y

T

i

m

e

(

n

s

)

T

PD

+

T

PD

-

150

250

350

450

550

V

S

= ±5V

V

SD

= 5V

R

L

= 2.3k

Propagation Delay vs Overdrive

V

IN

= 3V

STEP

6.8

6.6

6.4

6.2

6

5.8

5.4

5

0.2

0.4

0.8

1

1.2

1.6

2

V

OD

(V)

D

e

l

a

y

T

i

m

e

(

n

s

)

T

PD

+

T

PD

-

0.6

1.4

1.8

V

S

= ±5V

V

SD

= 5V

R

L

= 2.3k

5.6

5.2

Propagation Delay vs Overdrive

V

IN

= 5V

STEP

7.2

7

6.8

6.6

6.4

6.2

6

5.8

0.2 0.4

1

1.4

1.8

2.2

2.6

V

OD

(V)

D

e

l

a

y

T

i

m

e

(

n

s

)

T

PD

+

T

PD

-

0.6

1.2

1.6

2

2.4

V

S

= ±5V

V

SD

= 5V

R

L

= 2.3k

0.8

Propagation Delay vs Source Resistance

V

IN

= 1V

STEP

16

14

10

6

4

0

0.2

0.8

1.2

1.6 1.8

2

Source Resistance (k

)

D

e

l

a

y

T

i

m

e

(

n

s

)

T

PD

+

T

PD

-

0.4

1

1.4

0.6

12

8

V

S

= ±5V

V

SD

= 5mV

V

OD

= 50mV

R

L

= 2.3k

Propagation Delay vs Supply Voltage

4.5

4.4

4.2

4

3.8

3.7

3.6

3.5

4

4.2

4.8

5.2

5.6 5.8

6

±V

S

(V)

D

e

l

a

y

T

i

m

e

(

n

s

)

T

PD

+

T

PD

-

4.4

5

5.4

V

SD

= V

S

+

V

OD

= 50mV

R

L

= 2.2k

4.6

4.3

4.1

3.9

EL5185

5

Typical Performance Curves

(Continued)

Output with 50MHz Input

V

IN

= 1V

P-P

Output with 50MHz Input

V

IN

= 3V

P-P

Output

(5ns/div,

2V/div)

Input

(5ns/div,

0.5V/div)

Output

(5ns/div,

2V/div)

Input

(5ns/div,

2V/div)

Package Power Dissipation vs Ambient Temp.

JEDEC JESD51-3 Low Effective Thermal Conductivity

Test Board

0.7

0

0.5

0.3

0.2

0.1

P

o

w

e

r

D

i

s

s

i

p

a

t

i

o

n

(

W

)

0.6

0.4

0

125

100

75

50

25

Ambient Temperature (°C)

150

85

625mW

160

°C

/W

SO

8

Package Power Dissipation vs Ambient Temperature

JEDEC JESD51-7 High Effective Thermal Conductivity Test

Board

1.4

1.2

1

0.8

0.6

0.4

0.2

0

150

125

100

75

50

25

0

85

Ambient Temperature (°C)

P

o

w

e

r

D

i

s

s

i

p

a

t

i

o

n

(

W

)

909mW

110

°C/W

SO

8

Propagation Delay vs Load Capacitance

V

IN

=1V

STEP

7.5

7

6

5

4

0

10

40

60

80

90 100

C

LOAD

(pF)

D

e

l

a

y

T

i

m

e

(

n

s

)

T

PD

+

T

PD

-

20

50

70

30

6.5

5.5

V

S

= ±5V

V

SD

= 5V

V

OD

= 50mV

R

L

= 2.3k

4.5

EL5185