1

TM

File Number

3127.4

HI-5042 thru HI-5051

CMOS Analog Switches

This family of CMOS analog switches offers low resistance

switching performance for analog voltages up to the supply

rails and for signal currents up to 80mA. "ON" resistance is

low and stays reasonably constant over the full range of

operating signal voltage and current. r

ON

remains

exceptionally constant for input voltages between +5V and

-5V and currents up to 50mA. Switch impedance also

changes very little over temperature, particularly between

0

o

C and 75

o

C. r

ON

is nominally 25

for HI-5049 and

HI-5051 and 50

for HI-5042 through HI-5047.

All devices provide break-before-make switching and are

TTL and CMOS compatible for maximum application

versatility. Performance is further enhanced by Dielectric

Isolation processing which insures latch-free operation with

very low input and output leakage currents (0.8nA at 25

o

C).

This family of switches also features very low power

operation (1.5mW at 25

o

C).

There are 7 devices in this switch series which are

differentiated by type of switch action and value of r

ON

(see

Functional Description Table). The HI-504X and HI-505X

series switches can directly replace IH-5040 series devices,

and are functionally compatible with the DG180 and DG190

family.

Features

� Wide Analog Signal Range . . . . . . . . . . . . . . . . . . .

�

15V

� Low "ON" Resistance . . . . . . . . . . . . . . . . . . . . . . . . . 25

� High Current Capability . . . . . . . . . . . . . . . . . . . . . . 80mA

� Break-Before-Make Switching

- Turn-On Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370ns

- Turn-Off Time . . . . . . . . . . . . . . . . . . . . . . . . . . . 280ns

� No Latch-Up

� Input MOS Gates are Protected from Electrostatic

Discharge

� DTL, TTL, CMOS, PMOS Compatible

Applications

� High Frequency Switching

� Sample and Hold

� Digital Filters

� Operational Amplifier Gain Switching

Functional Diagram

Ordering Information

PART

NUMBER

TEMP. RANGE

(

o

C)

PACKAGE

PKG. NO.

HI1-5042-2

-55 to 125

16 Ld CERDIP

F16.3

HI1-5043-2

-55 to 125

16 Ld CERDIP

F16.3

HI1-5043-5

0 to 75

16 Ld CERDIP

F16.3

HI3-5043-5

0 to 75

16 Ld PDIP

E16.3

HI9P5043-5

0 to 75

16 Ld SOIC

M16.15

HI1-5047-5

0 to 75

16 Ld CERDIP

F16.3

HI1-5049-5

0 to 75

16 Ld CERDIP

F16.3

HI1-5051-2

-55 to 125

16 Ld CERDIP

F16.3

HI1-5051-5

0 to 75

16 Ld CERDIP

F16.3

HI3-5051-5

0 to 75

16 Ld PDIP

E16.3

HI9P5051-9

-40 to 85

16 Ld SOIC

M16.15

Functional Description

PART NUMBER

TYPE

r

ON

HI-5042

SPDT

50

HI-5043

Dual SPDT

50

HI-5047

4PST

50

HI-5049

Dual DPST

25

HI-5051

Dual SPDT

25

S

N

A

P

D

Data Sheet

April 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Intersil and Design is a trademark of Intersil Corporation.

|

Copyright

�

Intersil Corporation 2000

2

Pinouts

(SWITCHES SHOWN FOR LOGIC "0" INPUT)

Single Control

SPDT

HI-5042 (50

)

4PST

HI-5047 (50

)

NOTE:

Unused pins may be internally connected. Ground all

unused pins.

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

V-

V+

D

1

D

2

S

2

S

1

A

V

L

V

R

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

V-

V+

D

2

D

1

S

1

S

2

S

4

D

4

D

3

V

L

V

R

A

S

3

Pinouts

(SWITCHES SHOWN FOR LOGIC "0" INPUT)

Dual Control

DUAL SPDT

HI-5043 (50

), HI-5051 (25

)

DUAL DPST

HI-5049 (25

)

NOTE:

Unused pins may be internally connected. Ground all

unused pins.

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

D

3

S

3

S

4

D

4

V-

V+

S

1

S

2

A

2

V

L

V

R

A

1

D

1

D

2

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

V-

V+

S

1

S

2

A

2

V

L

V

R

A

1

D

3

S

3

S

4

D

4

D

1

D

2

Switch Functions

(SWITCHES SHOWN FOR LOGIC "1" INPUT)

SPDT

HI-5042 (50

)

DUAL SPDT

HI-5043 (50

)

4PST

HI-5047 (50

)

DUAL DPST

HI-5049 (25

)

DUAL SPDT

HI-5051 (25

)

12

11

13

14

15

A

1

16

3

4

V+

V

L

S

1

S

2

V-

V

R

D

1

D

2

1

3

8

6

5

9

10

12

15

4

16

11

13

14

V+

V

L

S

1

A

1

A

2

S

4

S

3

S

2

V-

V

R

D

1

D

2

D

4

D

3

12

11

13

14

15

3

4

1

16

8

9

6

5

D

1

D

2

D

4

D

3

S

1

S

3

S

4

S

2

A

V-

V

R

V+

V

L

1

3

8

6

5

9

10

12

15

4

16

11

13

14

V+

V

L

S

1

A

1

A

2

S

4

S

3

S

2

V-

V

R

D

1

D

2

D

4

D

3

1

3

8

6

5

9

10

12

15

4

16

11

13

14

D

1

D

2

D

4

D

3

S

1

A

1

A

2

S

4

S

3

S

2

V-

V

R

V+

V

L

HI-5042 thru HI-5051

3

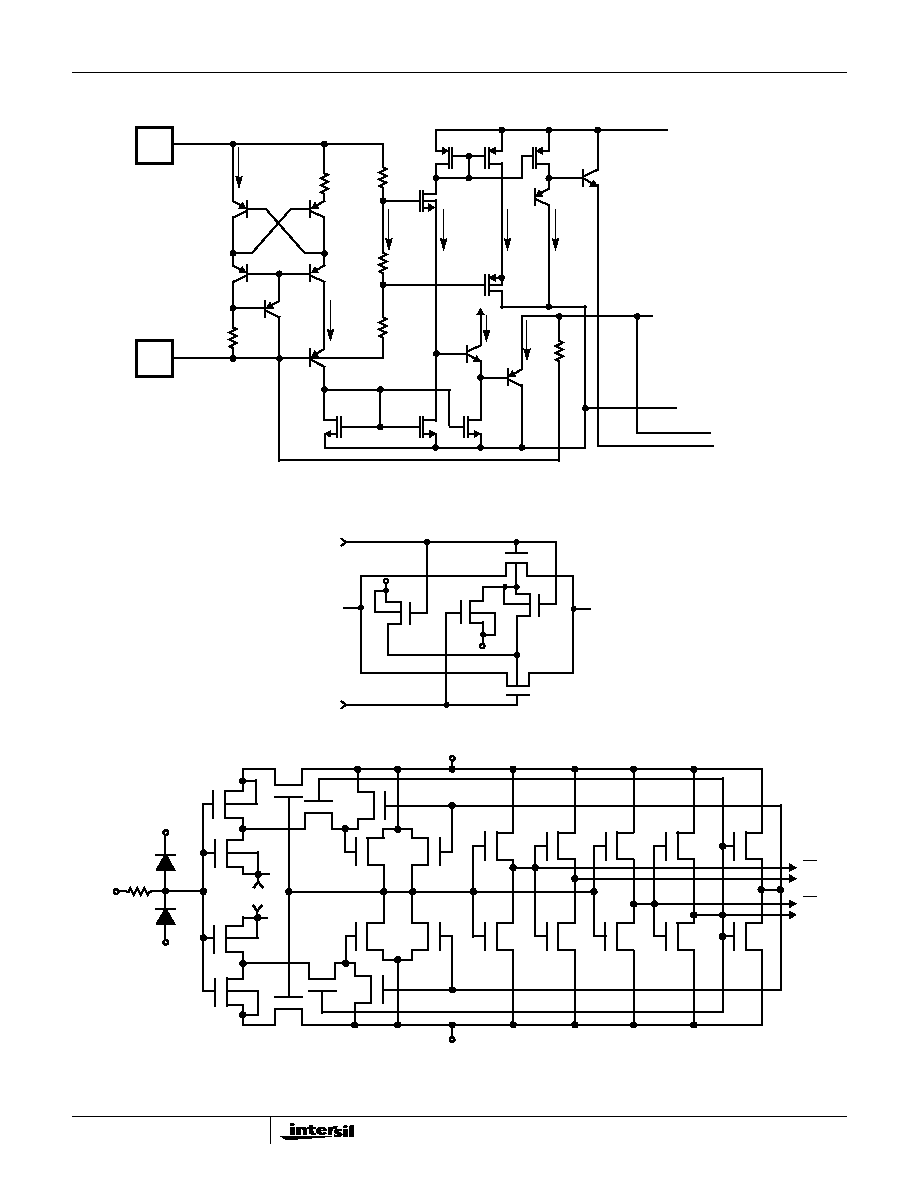

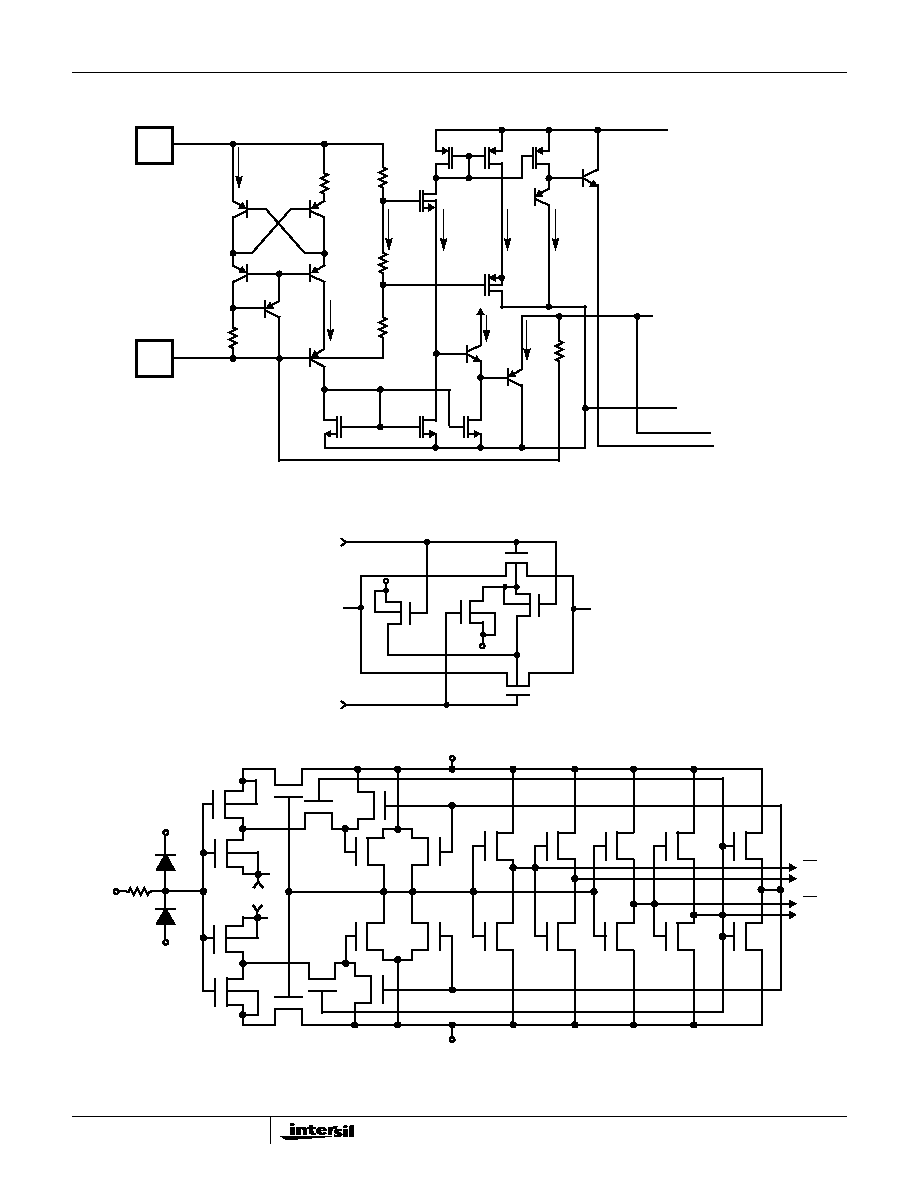

Schematic Diagrams

NOTE: Connect V+ to V

L

for minimizing power consumption when driving from CMOS circuits.

TTL/CMOS REFERENCE CIRCUIT (NOTE)

SWITCH CELL

NOTE: All N-Channel bodies to V-, all P-Channel bodies to V+ except as shown.

DIGITAL INPUT BUFFER AND LEVEL SHIFTER

P14

P15

P16

QN1

QP1

25

�

A

P13

V+

QN2

N14

N15

N16

QP2

R7

QP3

QP4

QP5

QP6

QP8

R2

QP7

R4

R5

R6

R3

TO V

R

'

to V

L

'

V-

V+

25

�

A

25

�

A

25

�

A

100

�

A

16

�

A

25

�

A

V

L

V

R

35

�

A

N13

P2

N2

N1

N3

V-

P1

IN

OUT

V+

A

1

(A

2

)

A

1

(A

2

)

N1

N2

P2

P1

P3

P5

P4

P6

P7

P8

P9

P10

P11

P12

A1

A2

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

V-

V

L

'

V

R

'

V+

V+

D2

D1

V-

A

R4

200

A1

A2

HI-5042 thru HI-5051

4

Absolute Maximum Ratings

Thermal Information

Supply Voltage (V+ to V-). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36V

V

R

to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V+, V-

Digital and Analog Input Voltage . . . . . . . . . . . . (V+) +4V to (V-) -4V

Analog Current (S to D) Continuous . . . . . . . . . . . . . . . . . . . . 30mA

Analog Current (S to D) Peak . . . . . . . . . . . . . . . . . . . . . . . . . 80mA

Operating Conditions

Temperature Range

HI-50XX-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

HI-50XX-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

o

C to 75

o

C

HI-50XX-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40

o

C to 85

o

C

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

JC

(

o

C/W)

CERDIP Package . . . . . . . . . . . . . . . . .

75

22

SOIC Package . . . . . . . . . . . . . . . . . . .

110

N/A

PDIP Package . . . . . . . . . . . . . . . . . . .

90

N/A

Maximum Junction Temperature

Plastic Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

o

C

Ceramic Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

o

C

Maximum Storage Temperature. . . . . . . . . . . . . . . . -65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300

o

C

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

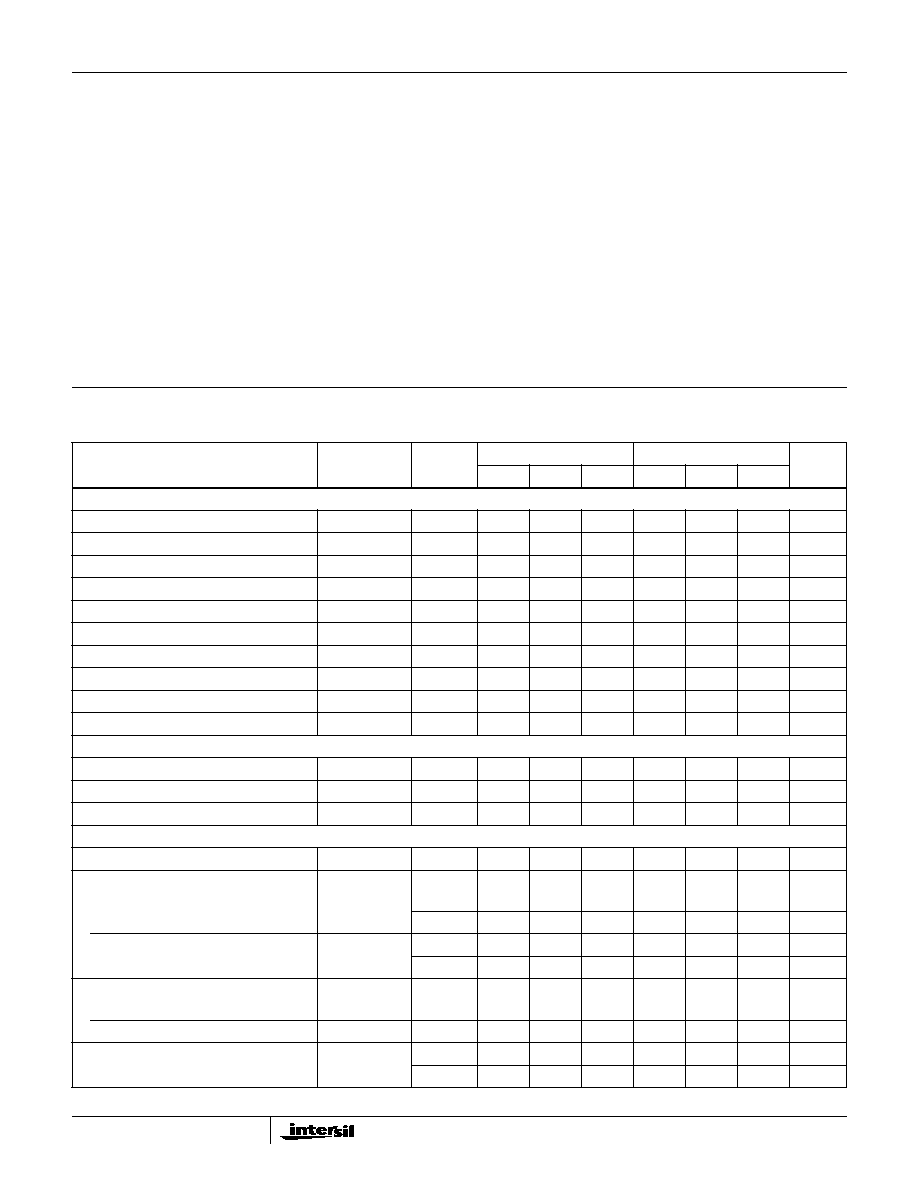

Electrical Specifications

Supplies = +15V, -15V; V

R

= 0V; V

AH

(Logic Level High) = 2.4V, V

AL

(Logic Level Low) = 0.8V, V

L

= 5V,

Unless Otherwise Specified. For Test Conditions, Consult Performance Characteristics,

Unused Pins are Grounded

PARAMETER

TEST

CONDITIONS

TEMP

(

o

C)

-2

-5, -9

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

DYNAMIC CHARACTERISTICS

Switch ON Time, t

ON

(Note 5)

25

-

370

500

-

370

500

ns

Switch OFF Time, t

OFF

(Note 5)

25

-

280

500

-

280

500

ns

Charge Injection, Q

(Note 3)

25

-

5

20

-

5

-

mV

OFF Isolation

(Note 4)

25

75

80

-

-

80

-

dB

Crosstalk

(Note 4)

25

80

88

-

-

88

-

dB

Input Switch Capacitance, C

S(OFF)

25

-

11

-

-

11

-

pF

Output Switch Capacitance, C

D(OFF)

25

-

11

-

-

11

-

pF

Output Switch Capacitance, C

D(ON)

25

-

22

-

-

22

-

pF

Digital Input Capacitance, C

A

25

-

5

-

-

5

-

pF

Drain To Source Capacitance, C

DS(OFF)

25

-

0.5

-

-

0.5

-

pF

DIGITAL INPUT CHARACTERISTICS

Input Low Threshold, V

AL

Full

-

-

0.8

-

-

0.8

V

Input High Threshold, V

AH

Full

2.4

-

-

2.4

-

-

V

Input Leakage Current (High or Low), I

A

Full

-

0.01

1.0

-

0.01

1.0

�

A

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range

Full

-15

-

+15

-15

-

+15

V

ON Resistance, r

ON

HI-5042 to HI-5047

(Note 2)

25

-

50

75

-

50

75

Full

-

-

150

-

-

150

HI-5049, HI-5051

(Note 2)

25

-

25

45

-

25

45

Full

-

-

50

-

-

50

Channel-to-Channel Match,

r

ON

HI-5042 to HI-5047

25

-

2

10

-

2

10

HI-5049, HI-5051

25

-

1

5

-

1

5

OFF Input or Output Leakage Current,

I

S(OFF)

= I

D(OFF)

25

-

0.8

2

-

0.8

2

nA

Full

-

100

200

-

100

200

nA

HI-5042 thru HI-5051

5

ON Leakage Current, I

D(ON)

25

-

0.01

2

-

0.01

2

nA

Full

-

2

200

-

2

200

nA

POWER REQUIREMENTS

Quiescent Power Dissipation, P

D

25

-

1.5

-

-

1.5

-

mW

I+, I-, I

L

, I

R

25

-

-

0.2

-

-

0.3

mA

I+, +15V Quiescent Current

(Note 5)

Full

-

-

0.3

-

-

0.5

mA

I-, -15V Quiescent Current

(Note 5)

Full

-

-

0.3

-

-

0.5

mA

I

L

, +5V Quiescent Current

(Note 5)

Full

-

-

0.3

-

-

0.5

mA

I

R

, Ground Quiescent Current

(Note 5)

Full

-

-

0.3

-

-

0.5

mA

NOTES:

2. V

OUT

=

�

10V, I

OUT

=

1mA.

3. V

IN

= 0V, C

L

= 10nF.

4. R

L

= 100

, f = 100kHz, V

IN

= 2.0V

P-P

, C

L

= 5pF.

5. V

AL

= 0V, V

AH

= 5V.

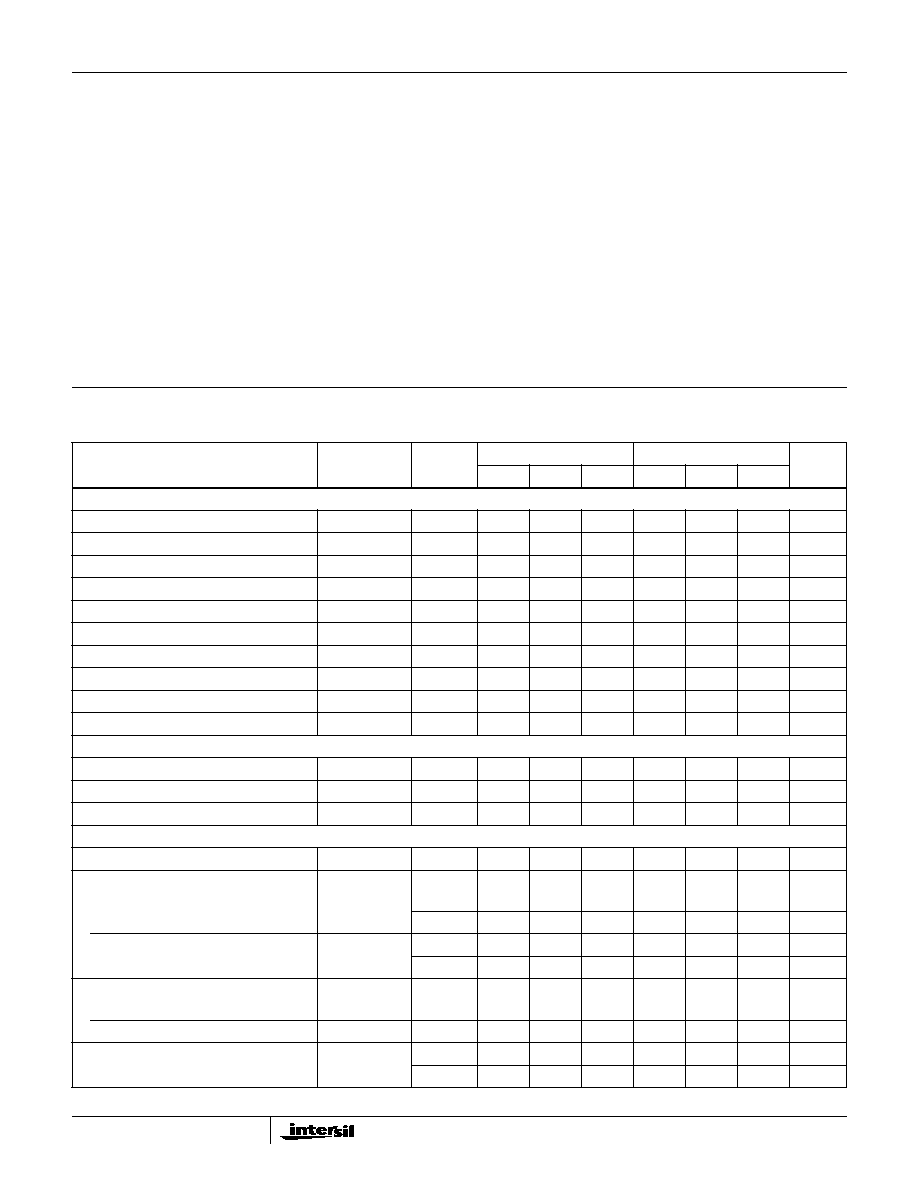

Electrical Specifications

Supplies = +15V, -15V; V

R

= 0V; V

AH

(Logic Level High) = 2.4V, V

AL

(Logic Level Low) = 0.8V, V

L

= 5V,

Unless Otherwise Specified. For Test Conditions, Consult Performance Characteristics,

Unused Pins are Grounded (Continued)

PARAMETER

TEST

CONDITIONS

TEMP

(

o

C)

-2

-5, -9

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

Test Circuits and Waveforms

T

A

= 25

o

C, V+ = +15V, V- = -15V, V

L

= +5V, V

R

= 0V, V

AH

= 3V and V

AL

= 0.8V

Unless Otherwise Specified

FIGURE 1A. TEST CIRCUIT

FIGURE 1B. ON RESISTANCE vs ANALOG SIGNAL LEVEL

FIGURE 1C. NORMALIZED ON RESISTANCE vs TEMPERATURE

FIGURE 1. ON RESISTANCE

IN

OUT

1mA

V

2

r

ON

=

1mA

V

2

�

V

IN

ANALOG SIGNAL LEVEL (V)

ON RESIST

ANCE (

)

80

60

40

20

0

-15

-10

-5

0

5

10

15

V+ = +10V

V- = -10V

V+ = +12V

V- = -12V

V+ = +15V

V- = -15V

TEMPERATURE (

o

C)

-50

-25

0

75

100

125

50

25

0.6

1.2

1.1

1.0

0.9

0.8

0.7

NORMALIZED ON RESIST

ANCE

(REFERRED T

O

25

o

C)

V

IN

= 0V

HI-5042 thru HI-5051