1

File Number

3121.4

HI-200, HI-201

Dual/Quad SPST, CMOS Analog Switches

HI-200/HI-201 (dual/quad) are monolithic devices comprising

independently selectable SPST switches which feature fast

switching speeds (HI-200 240ns, and HI-201 185ns)

combined with low power dissipation (15mW at 25

o

C). Each

switch provides low "ON" resistance operation for input signal

voltage up to the supply rails and for signal current up to

80mA. Rugged DI construction eliminates latch-up and

substrate SCR failure modes.

All devices provide break-before-make switching and are

TTL and CMOS compatible for maximum application

versatility. HI-200/HI-201 are ideal components for use in

high frequency analog switching. Typical applications include

signal path switching, sample and hold circuit, digital filters,

and operational amplifier gain switching networks.

Features

∑ Analog Voltage Range . . . . . . . . . . . . . . . . . . . . . . .

±

15V

∑ Analog Current Range . . . . . . . . . . . . . . . . . . . . . . . 80mA

∑ Turn-On Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240ns

∑ Low r

ON

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

∑ Low Power Dissipation . . . . . . . . . . . . . . . . . . . . . . .15mW

∑ TTL/CMOS Compatible

Applications

∑ High Frequency Analog Switching

∑ Sample and Hold Circuits

∑ Digital Filters

∑ Operational Amplifier Gain Switching Networks

Functional Diagram

Ordering Information

PART

NUMBER

TEMPERATURE

RANGE (

o

C)

PACKAGE

PKG. NO.

HI1-0200-5

0 to 75

14 Ld CERDIP

F14.3

HI2-0200-5

0 to 75

10 Pin Metal Can

T10.B

HI3-0200-5

0 to 75

14 Ld PDIP

E14.3

HI1-0201-2

-55 to 125

16 Ld CERDIP

F16.3

HI1-0201-4

-25 to 85

16 Ld CERDIP

F16.3

HI1-0201-5

0 to 75

16 Ld CERDIP

F16.3

HI3-0201-5

0 to 75

16 Ld PDIP

E16.3

HI4P0201-5

0 to 75

20 Ld PLCC

N20.35

HI9P0201-5

0 to 75

16 Ld SOIC

M16.15

HI9P0201-9

-40 to 85

16 Ld SOIC

M16.15

TRUTH TABLE

LOGIC

HI-200

HI-201

0

ON

ON

1

OFF

OFF

REFERENCE,

LEVEL SHIFTER,

AND DRIVER

GATE

SWITCH

CELL

SOURCE

DRAIN

OUTPUT

LOGIC

INPUT

V+

V

REF

V-

INPUT

GATE

Data Sheet

October 1999

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 407-727-9207

|

Copyright

©

Intersil Corporation 1999

4

Absolute Maximum Ratings

Thermal Information

Supply Voltage (V+ to V-). . . . . . . . . . . . . . . . . . . . . . . . . 44V (

±

22)

V

REF

to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20V, -5V

Digital Input Voltage . . . . . . . . . . . . . . . . . . . . . . (V+) +4V to (V-) -4V

Analog Input Voltage (One Switch) . . . . . . . . . . (V+) +2V to (V-) -2V

Operating Conditions

Temperature Ranges

HI-201-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

HI-201-4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -25

o

C to 85

o

C

HI-200-5, HI-201-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

o

C to 75

o

C

HI-201-9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40

o

C to 85

o

C

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

JC

(

o

C/W)

14 Ld CERDIP Package . . . . . . . . . . . .

80

24

16 Ld CERDIP Package . . . . . . . . . . . .

75

20

PLCC Package . . . . . . . . . . . . . . . . . . .

80

N/A

PDIP Package . . . . . . . . . . . . . . . . . . .

95

N/A

16 Ld SOIC Package . . . . . . . . . . . . . .

110

N/A

10 Pin Metal Can Package . . . . . . . . . .

160

75

Maximum Storage Temperature. . . . . . . . . . . . . . . . -65

o

C to 150

o

C

Maximum Junction Temperature (Hermetic Packages) . . . . . 175

o

C

Maximum Junction Temperature (Plastic Packages) . . . . . . . 150

o

C

Maximum Lead Temperature (Soldering, 10s). . . . . . . . . . . . 300

o

C

(PLCC and SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

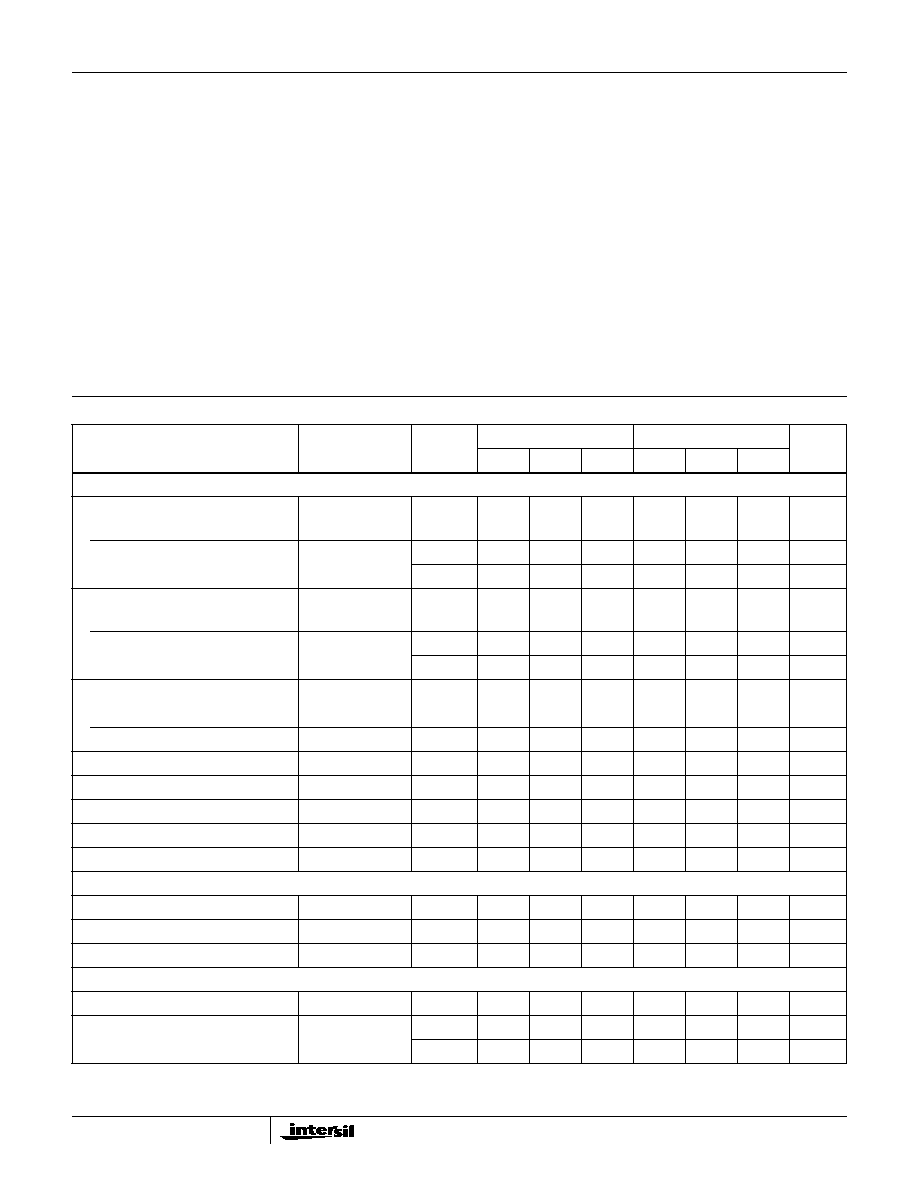

Electrical Specifications

Supplies = +15V, -15V; V

REF

= Open; V

AH

(Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.8V

PARAMETER

TEST

CONDITIONS

TEMP

(

o

C)

-2

-4, -5, -9

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

DYNAMIC CHARACTERISTICS

Switch ON Time, t

ON

HI-200

25

-

240

500

-

240

-

ns

HI-201

25

-

185

500

-

185

-

ns

Full

-

1000

-

-

1000

-

ns

Switch OFF Time, t

OFF

HI-200

25

-

330

500

-

500

-

ns

HI-201

25

-

220

500

-

220

-

ns

Full

-

1000

-

-

1000

-

ns

Off Isolation

(Note 4)

HI-200

25

-

70

-

-

70

-

dB

HI-201

25

-

80

-

-

80

-

dB

Input Switch Capacitance, C

S(OFF)

25

-

5.5

-

-

5.5

-

pF

Output Switch Capacitance, C

D(OFF)

25

-

5.5

-

-

5.5

-

pF

Output Switch Capacitance, C

D(ON)

25

-

11

-

-

11

-

pF

Digital Input Capacitance, C

A

25

-

5

-

-

5

-

pF

Drain-to-Source Capacitance, C

DS(OFF)

25

-

0.5

-

-

0.5

-

pF

DIGITAL INPUT CHARACTERISTICS

Input Low Threshold, V

AL

Full

-

-

0.8

-

-

0.8

V

Input High Threshold, V

AH

Full

2.4

-

-

2.4

-

-

V

Input Leakage Current (High or Low), I

A

(Note 3)

Full

-

-

1.0

-

-

1.0

µ

A

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

S

Full

-15

-

+15

-15

-

+15

V

ON Resistance, r

ON

(Note 2)

25

-

55

70

-

55

80

Full

-

80

100

-

72

100

HI-200, HI-201

5

OFF Input Leakage Current, I

S(OFF)

(Note 6)

25

-

1

5

-

1

50

nA

HI-200

Full

-

100

500

-

10

500

nA

HI-201

25

-

2

5

-

2

50

nA

Full

-

-

500

-

-

250

nA

OFF Output Leakage Current, I

D(OFF)

(Note 6)

25

-

1

5

-

1

50

nA

HI-200

Full

-

100

500

-

10

500

nA

HI-201

25

-

2

5

-

2

50

nA

Full

-

35

500

-

35

250

nA

ON Leakage Current, I

D(ON)

(Note 6)

25

-

1

5

-

1

50

nA

HI-200

Full

-

100

500

-

10

500

nA

HI-201

25

-

2

5

-

2

50

nA

Full

-

-

500

-

-

250

nA

POWER SUPPLY CHARACTERISTICS (Note 5)

Power Dissipation, P

D

25

-

15

-

-

15

-

mW

Full

-

-

60

-

-

60

mW

Current, I+

25

-

0.5

-

-

0.5

-

mA

Full

-

-

2.0

-

-

2.0

mA

Current, I-

25

-

0.5

-

-

0.5

-

mA

Full

-

-

2.0

-

-

2.0

mA

NOTES:

2. V

OUT

=

±

10V, I

OUT

= 1mA.

3. Digital Inputs are MOS gates: typical leakage is < 1nA.

4. V

A

= 5V, R

L

= 1k

, C

L

= 10pF, V

S

= 3V

RMS

, f = 100kHz.

5. V

A

= +3V or V

A

= 0V for Both Switches.

6. Refer to Leakage Current Measurements (Figure 2).

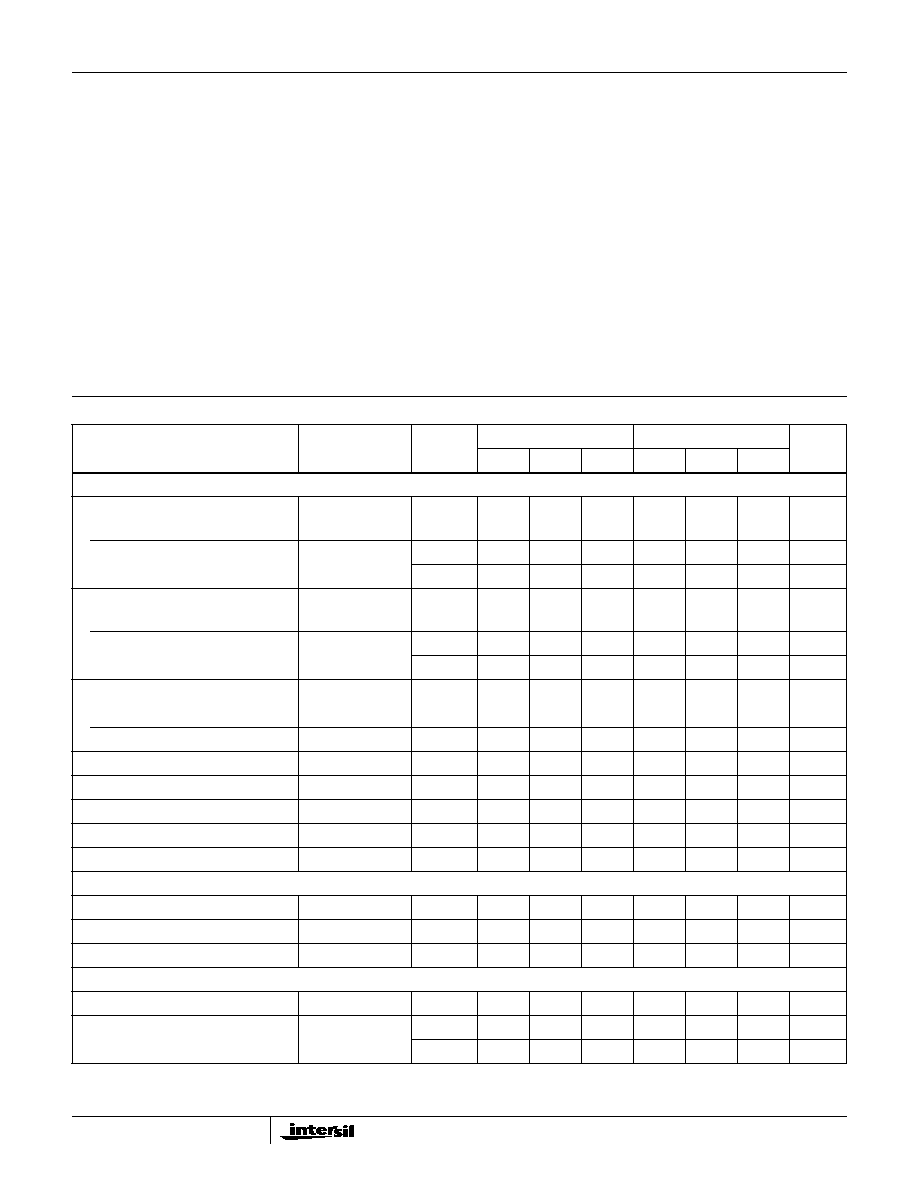

Electrical Specifications

Supplies = +15V, -15V; V

REF

= Open; V

AH

(Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.8V (Continued)

PARAMETER

TEST

CONDITIONS

TEMP

(

o

C)

-2

-4, -5, -9

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

Test Circuits and Waveforms

T

A

= 25

o

C, V

SUPPLY

=

±

15V, V

AH

= 2.4V, V

AL

= 0.8V and V

REF

= Open

FIGURE 1A. ON RESISTANCE TEST CIRCUIT

V

2

1mA

IN

OUT

±

V

IN

r

ON

2

V

1mA

-------------

=

HI-200, HI-201