1

TM

File Number

3131.3

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation

Copyright © Intersil Corporation 2000

IH5053

Quad CMOS Analog Switch

The IH5053 analog switch uses an improved, high voltage

CMOS technology, which provides performance advantages

not previously available from solid state switches. Key

performance advantages are TTL compatibility and ultra low-

power operation. The quiescent current requirement is less

than 10

µ

A.

The IH5053 also guarantees Break-Before-Make switching.

This is accomplished by extending the t

ON

time (1000ns)

such that it exceeds the t

OFF

time (500ns). This insures that

an ON channel will be turned OFF before an OFF channel

can turn ON, and eliminates the need for external logic

required to avoid channel to channel shorting during

switching.

Pinout

IH5053 (SBDIP)

TOP VIEW

SWITCH STATES SHOWN FOR LOGIC "1" INPUT

Features

∑ Switches Greater Than 20V

P-P

Signals with

±

15V

Supplies

∑ Quiescent Current . . . . . . . . . . . . . . . . . . . . . . . . . <10

µ

A

∑ Break-Before-Make Switching

- t

OFF

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns

- t

ON

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns

∑ TTL, CMOS Compatible

∑ 4 Normally Open Switches

∑ Low r

DS(ON)

(Typ) . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

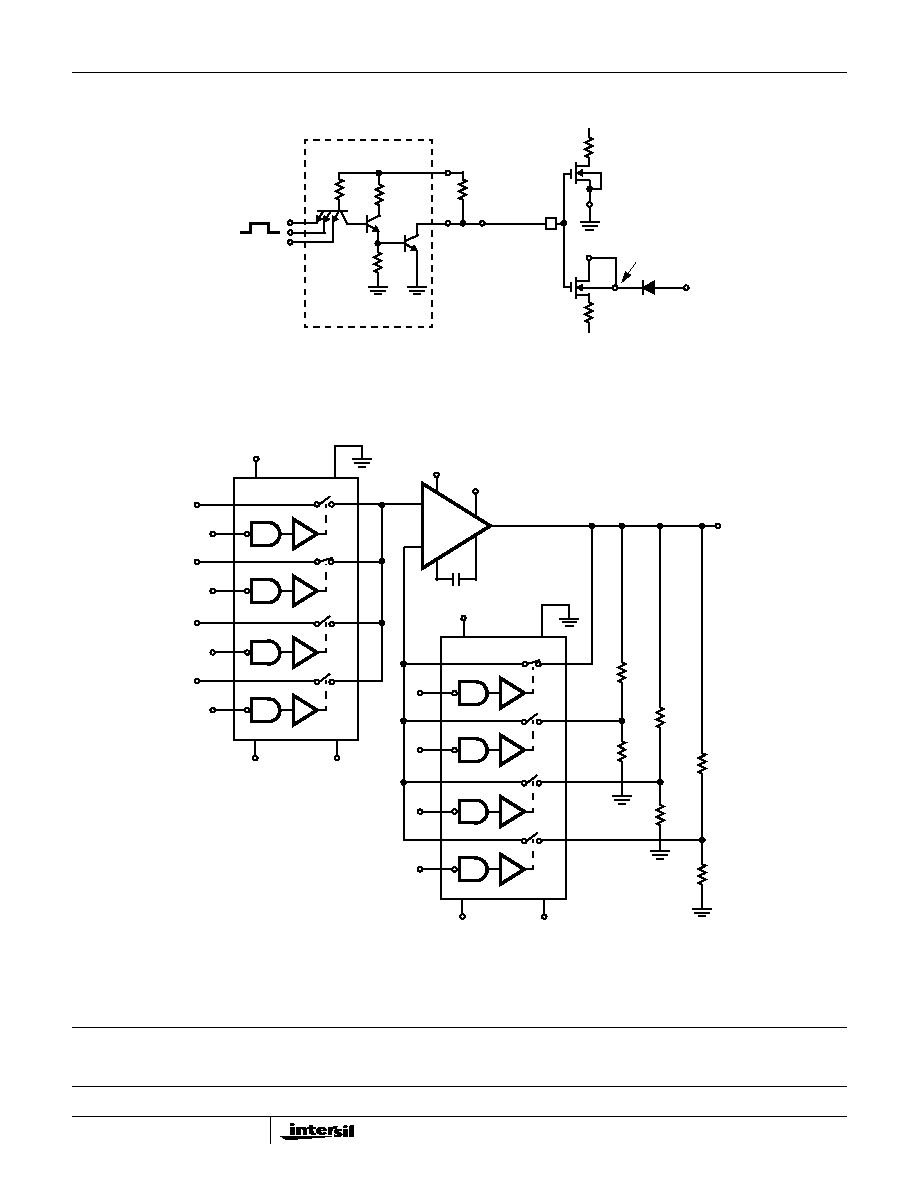

Schematic Diagram

(

1

/

4

AS SHOWN)

TRUTH TABLE

LOGIC

SWITCHES

0

Off

1

On

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

IN

1

D

1

S

1

V-

GND

S

2

IN

2

D

2

IN

4

S

4

V+

V

L

S

3

D

3

IN

3

D

4

Part Number Information

PART NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG.

NO.

IH5053CDE

0 to 70

16 Ld SBDIP

D16.3

V+

IN

Q3

5K

Q1

GND

V

L

Q2

10K

Q5

V-

Q6

1K

2K

Q4

Q7

Q8

400

Q11

FLOATS

Q12

400

Data Sheet

March 2000

[ /Title

(IH505

3)

/Sub-

ject

(Quad

CMOS

Ana-

log

Switch

es)

/Autho

r ()

/Key-

words

(Inter-

sil

Corpo-

ration,

semi-

con-

ductor,

Quad

CMOS

Ana-

log

Switch

es)

/Cre-

ator ()

/DOCI

NFO

pdf-

mark

[

/Page-

Mode

OBSOLETE PR

ODUCT

POSSIBLE SUBSTITUTE PR

ODUCT

DG445, DG442

2

Absolute Maximum Ratings

Thermal Information

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <36V

V+ to V

D

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <30V

V

D

to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <30V

V

D

to V

S

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <

±

22V

V

L

to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <33V

V

L

to V

IN

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <30V

V

L

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <20V

V

IN

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <20V

Continuous Current (S-D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30mA

Peak Current IN or OUT (Pulsed 1ms, 10% Duty Cycle, Max) . . . 70mA

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

o

C to 70

o

C

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . .175

o

C

Maximum Storage Temperature Range . . . . . . . . . . -65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Electrical Specifications

V+ = +15V, V- = -15V, V

L

= +5V

PER CHANNEL PARAMETER

TEST CONDITIONS

(NOTES 1, 2)

UNITS

0

o

C

25

o

C

70

o

C

DYNAMIC CHARACTERISTICS

Turn ON Time, t

ON

R

L

= 1k

, V

ANALOG

= -10V to +10V (Figure 6)

-

1000

-

ns

Turn OFF Time, t

OFF

-

500

-

ns

Charge Injection, Q

Figure 7

-

20 (Typ)

-

mV

OFF Isolation, OIRR

f = 1MHz, R

L

= 100

, C

L

5pF (Figure 4)

-

50 (Typ)

-

dB

Crosstalk, CCRR

One Channel Off (Figure 3)

-

50 (Typ)

-

dB

DIGITAL INPUT CHARACTERISTICS

Input Logic Current, I

IN(ON)

V

lN

= 2.4V

-

±

10

-

µ

A

Input Logic Current, I

IN(OFF)

V

lN

= 0.8V

-

±

10

-

µ

A

ANALOG SWITCH CHARACTERISTICS

Drain-Source ON Resistance, r

DS(ON)

I

S

= 10mA, V

ANALOG

= -10V to +10V

80

80

100

Channel-to-Channel, r

DS(ON)

Match

-

30 (Typ)

-

Minimum Analog Signal Handling Capability,

V

ANALOG

-

±

10 (Typ)

-

V

Switch OFF Leakage Current, I

D(OFF)

, I

S(OFF)

V

ANALOG

= -10V to +10V

-

±

5

100

nA

Switch ON Leakage Current, I

D(ON)

+ I

S(ON)

V

D

= V

S

= -10V to +10V

-

±

10

100

nA

POWER SUPPLY CHARACTERISTICS

+ Power Supply Quiescent Current, I+

10

10

100

µ

A

- Power Supply Quiescent Current, I-

10

10

100

µ

A

+5V Supply Quiescent Current, I

L

10

10

100

µ

A

NOTES:

1. Typical values are for Design Aid only, not guaranteed nor production tested.

2. Min or Max value unless otherwise specified.

IH5053

5

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time with-

out notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

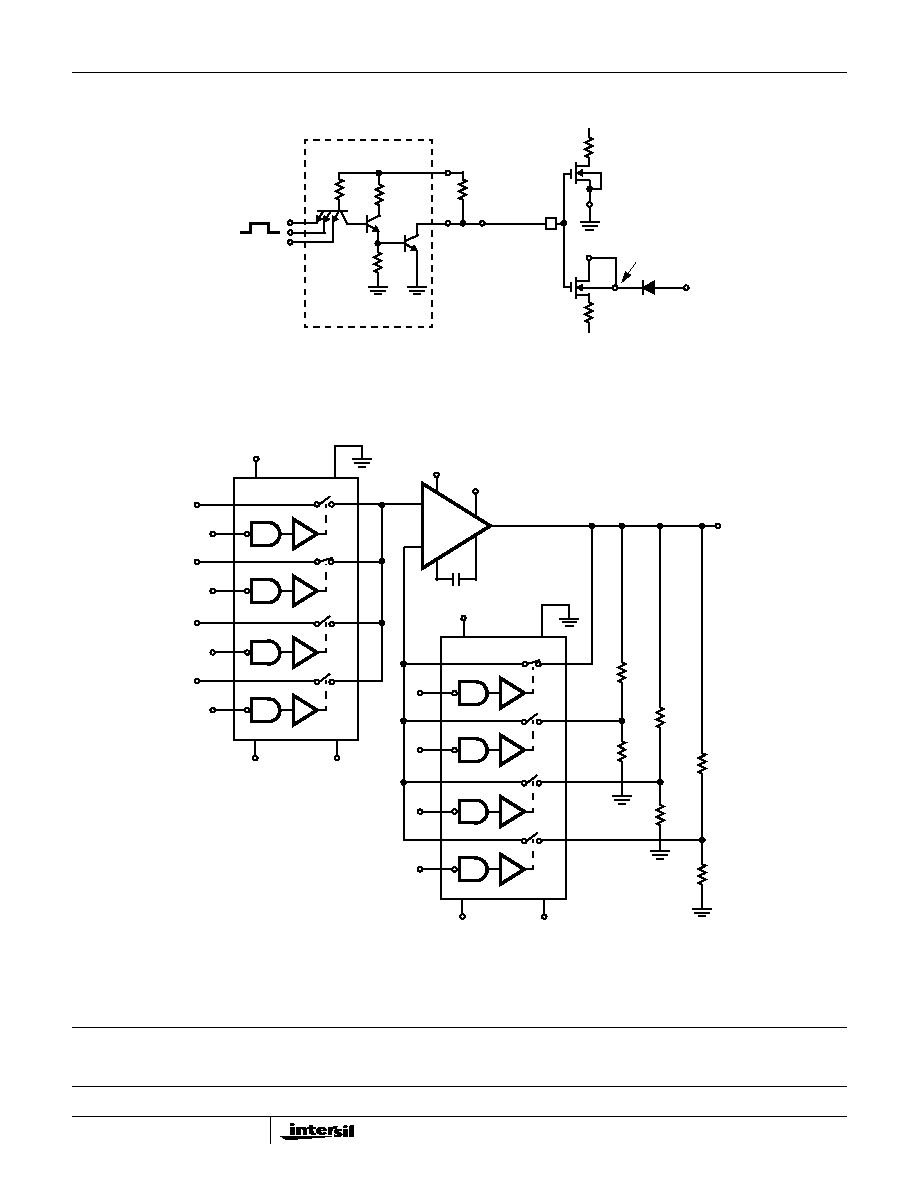

Typical Applications

FIGURE 8. +15V OPEN COLLECTOR TTL INTERFACE

FIGURE 9. ACTIVE LOW PASS FILTER WITH DIGITALLY SELECTED BREAK FREQUENCY

TTL

LOGIC

INPUT

15V

10k

LOGIC

INPUT

15V TTL GATE

R

EXT

(1k

TO 20k

)

IN

GND

V

L

V+

20k

+15V

GAIN

1

LM101A

1X

18k

100

9.9k

100

100k

2k

10X

100X

1000X

3

14

11

6

12

4

+5V

-15V

2

1

5

13

+15V

30pF

+15V

-15V

4

6

7

1

2

3

+

-

V

OUT

GAIN

2

15

16

GAIN

3

10

9

GAIN

4

7

8

+15V

13

5

IH5053

IH5053

2

15

10

7

12

4

-15V

+5V

8

6

9

11

16

14

1

3

V

IN1

CH

1

V

IN2

CH

2

V

IN3

CH

3

V

IN4

CH

4

IH5053