| ÐлекÑÑоннÑй компоненÑ: IRF1405 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

Parameter

Max.

Units

I

D

@ T

C

= 25°C

Continuous Drain Current, V

GS

@ 10V

169

I

D

@ T

C

= 100°C

Continuous Drain Current, V

GS

@ 10V

118

A

I

DM

Pulsed Drain Current

680

P

D

@T

C

= 25°C

Power Dissipation

330

W

Linear Derating Factor

2.2

W/°C

V

GS

Gate-to-Source Voltage

± 20

V

E

AS

Single Pulse Avalanche Energy

560

mJ

I

AR

Avalanche Current

See Fig.12a, 12b, 15, 16

A

E

AR

Repetitive Avalanche Energy

mJ

dv/dt

Peak Diode Recovery dv/dt

5.0

V/ns

T

J

Operating Junction and

-55 to + 175

T

STG

Storage Temperature Range

Soldering Temperature, for 10 seconds

300 (1.6mm from case )

°C

Mounting Torque, 6-32 or M3 screw

10 lbf·in (1.1N·m)

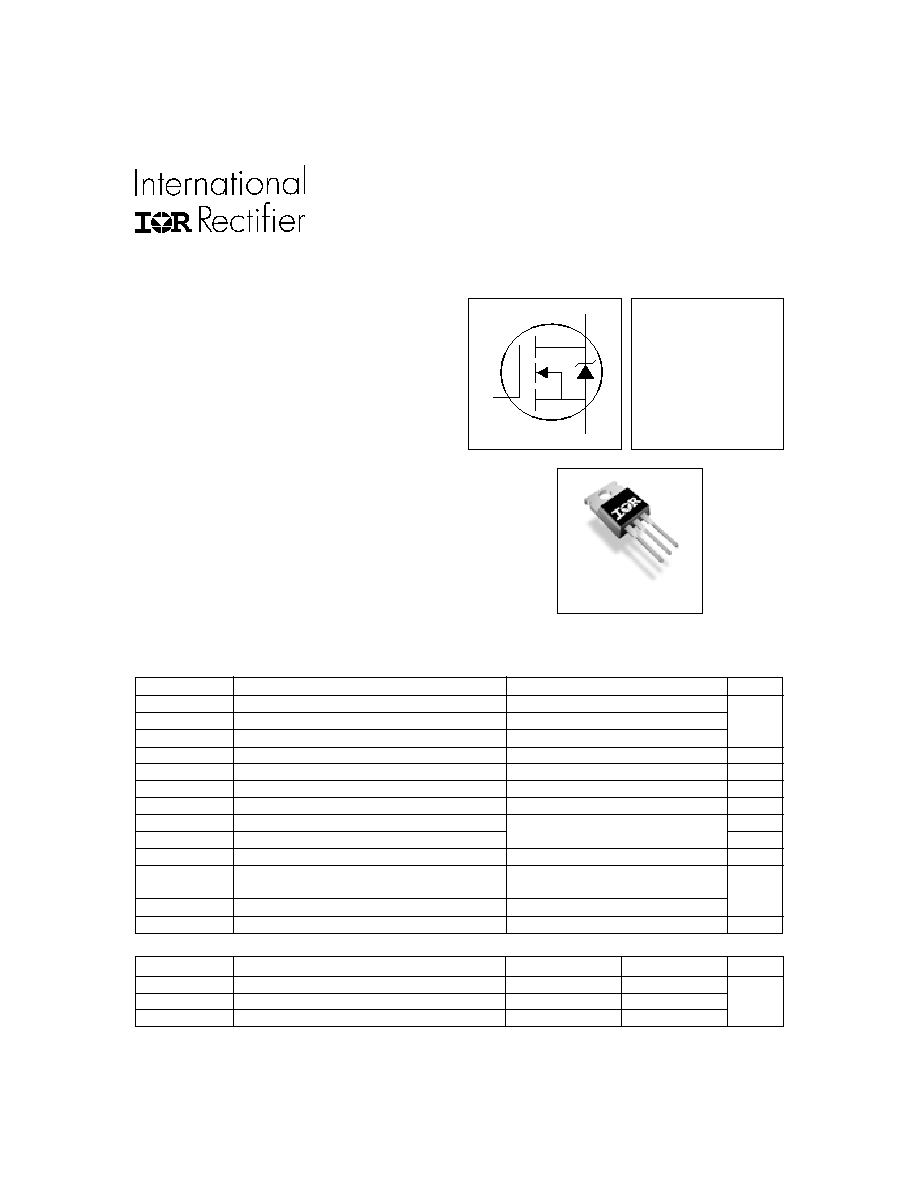

HEXFET

®

Power MOSFET

Specifically designed for Automotive applications, this

Stripe Planar design of HEXFET

®

Power MOSFETs

utilizes the lastest processing techniques to achieve

extremely low on-resistance per silicon area. Additional

features of this HEXFET power MOSFET are a 175°C

junction operating temperature, fast switching speed

and improved repetitive avalanche rating. These benefits

combine to make this design an extremely efficient and

reliable device for use in Automotive applications and a

wide variety of other applications.

S

D

G

Absolute Maximum Ratings

V

DSS

= 55V

R

DS(on)

= 5.3m

I

D

= 169A

Description

3/25/01

www.irf.com

1

q

Advanced Process Technology

q

Ultra Low On-Resistance

q

Dynamic dv/dt Rating

q

175°C Operating Temperature

q

Fast Switching

q

Repetitive Avalanche Allowed up to Tjmax

Benefits

AUTOMOTIVE MOSFET

Thermal Resistance

Parameter

Typ.

Max.

Units

R

JC

Junction-to-Case

0.45

°C/W

R

CS

Case-to-Sink, Flat, Greased Surface

0.50

R

JA

Junction-to-Ambient

62

TO-220AB

PD -93991A

IRF1405

Typical Applications

q

Electric Power Steering (EPS)

q

Anti-lock Braking System (ABS)

q

Wiper Control

q

Climate Control

q

Power Door

IRF1405

2

www.irf.com

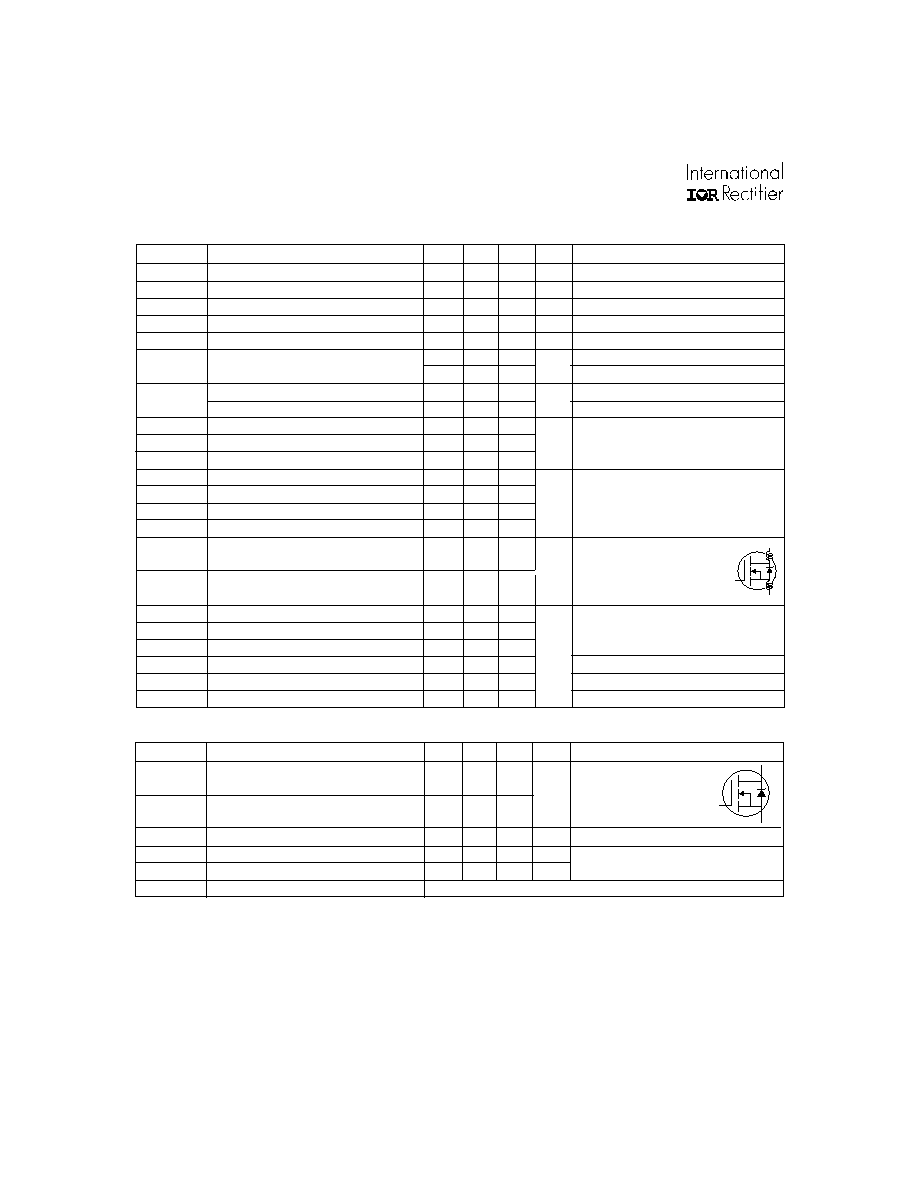

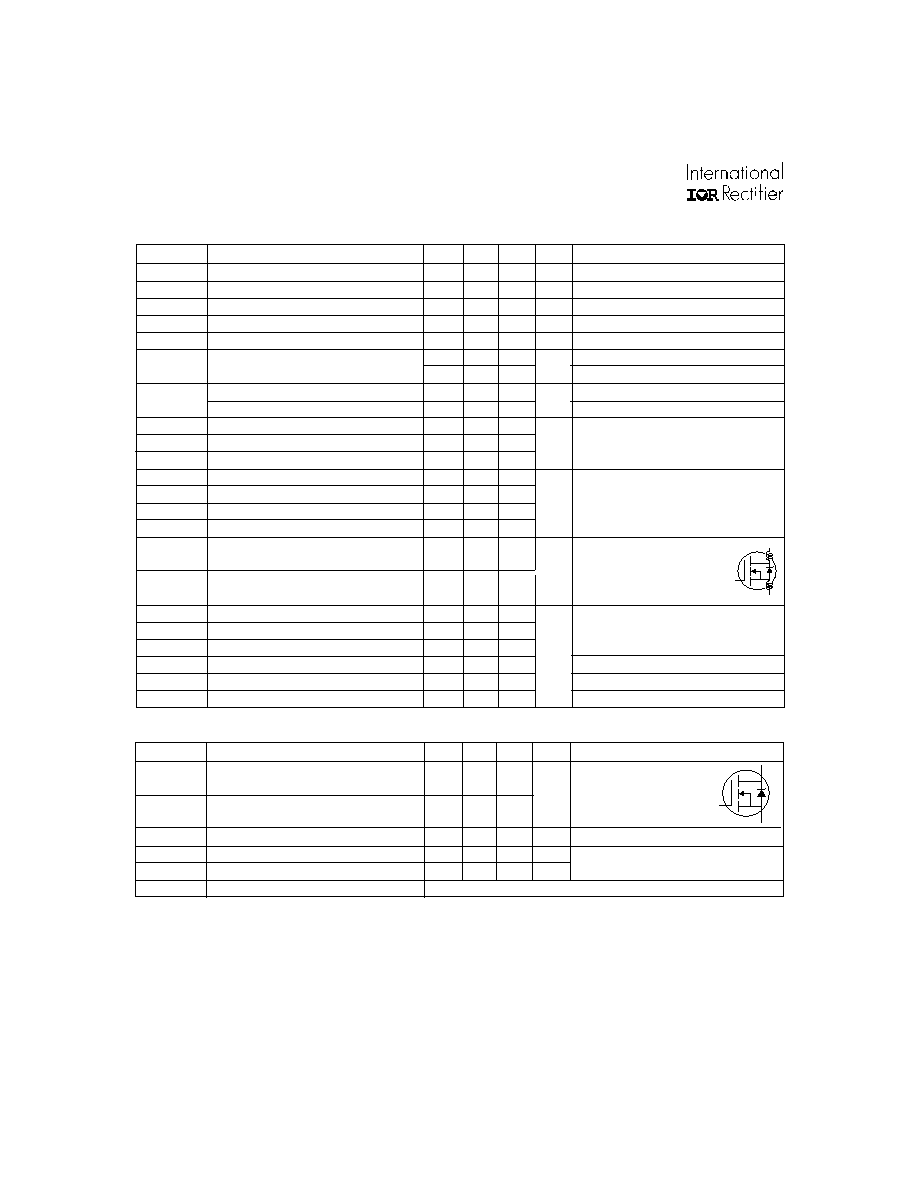

Parameter

Min. Typ. Max. Units

Conditions

V

(BR)DSS

Drain-to-Source Breakdown Voltage

55

V

V

GS

= 0V, I

D

= 250µA

V

(BR)DSS

/

T

J

Breakdown Voltage Temp. Coefficient

0.057

V/°C

Reference to 25°C, I

D

= 1mA

R

DS(on)

Static Drain-to-Source On-Resistance

4.6

5.3

m

V

GS

= 10V, I

D

= 101A

V

GS(th)

Gate Threshold Voltage

2.0

4.0

V

V

DS

= 10V, I

D

= 250µA

g

fs

Forward Transconductance

69

S

V

DS

= 25V, I

D

= 110A

20

µA

V

DS

= 55V, V

GS

= 0V

250

V

DS

= 44V, V

GS

= 0V, T

J

= 150°C

Gate-to-Source Forward Leakage

200

V

GS

= 20V

Gate-to-Source Reverse Leakage

-200

nA

V

GS

= -20V

Q

g

Total Gate Charge

170

260

I

D

= 101A

Q

gs

Gate-to-Source Charge

44

66

nC

V

DS

= 44V

Q

gd

Gate-to-Drain ("Miller") Charge

62

93

V

GS

= 10V

t

d(on)

Turn-On Delay Time

13

V

DD

= 38V

t

r

Rise Time

190

I

D

= 110A

t

d(off)

Turn-Off Delay Time

130

R

G

= 1.1

t

f

Fall Time

110

V

GS

= 10V

Between lead,

6mm (0.25in.)

from package

and center of die contact

C

iss

Input Capacitance

5480

V

GS

= 0V

C

oss

Output Capacitance

1210

pF

V

DS

= 25V

C

rss

Reverse Transfer Capacitance

280

= 1.0MHz, See Fig. 5

C

oss

Output Capacitance

5210

V

GS

= 0V, V

DS

= 1.0V, = 1.0MHz

C

oss

Output Capacitance

900

V

GS

= 0V, V

DS

= 44V, = 1.0MHz

C

oss

eff.

Effective Output Capacitance

1500

V

GS

= 0V, V

DS

= 0V to 44V

nH

Electrical Characteristics @ T

J

= 25°C (unless otherwise specified)

L

D

Internal Drain Inductance

L

S

Internal Source Inductance

S

D

G

I

GSS

ns

4.5

7.5

I

DSS

Drain-to-Source Leakage Current

S

D

G

Parameter

Min. Typ. Max. Units

Conditions

I

S

Continuous Source Current

MOSFET symbol

(Body Diode)

showing the

I

SM

Pulsed Source Current

integral reverse

(Body Diode)

p-n junction diode.

V

SD

Diode Forward Voltage

1.3

V

T

J

= 25°C, I

S

= 101A, V

GS

= 0V

t

rr

Reverse Recovery Time

88

130

ns

T

J

= 25°C, I

F

= 101A

Q

rr

Reverse RecoveryCharge

250

380

nC

di/dt = 100A/µs

t

on

Forward Turn-On Time

Intrinsic turn-on time is negligible (turn-on is dominated by L

S

+L

D

)

Source-Drain Ratings and Characteristics

169

680

A

Repetitive rating; pulse width limited by

max. junction temperature. (See fig. 11).

Starting T

J

= 25°C, L = 0.11mH

R

G

= 25

, I

AS

= 101A. (See Figure 12).

I

SD

101A, di/dt

210A/µs, V

DD

V

(BR)DSS

,

T

J

175°C

Pulse width

400µs; duty cycle

2%.

Notes:

C

oss

eff. is a fixed capacitance that gives the same charging time

as C

oss

while V

DS

is rising from 0 to 80% V

DSS

.

Calculated continuous current based on maximum allowable

junction temperature. Package limitation current is 75A.

Limited by T

Jmax

, see Fig.12a, 12b, 15, 16 for typical repetitive

avalanche performance.

IRF1405

www.irf.com

3

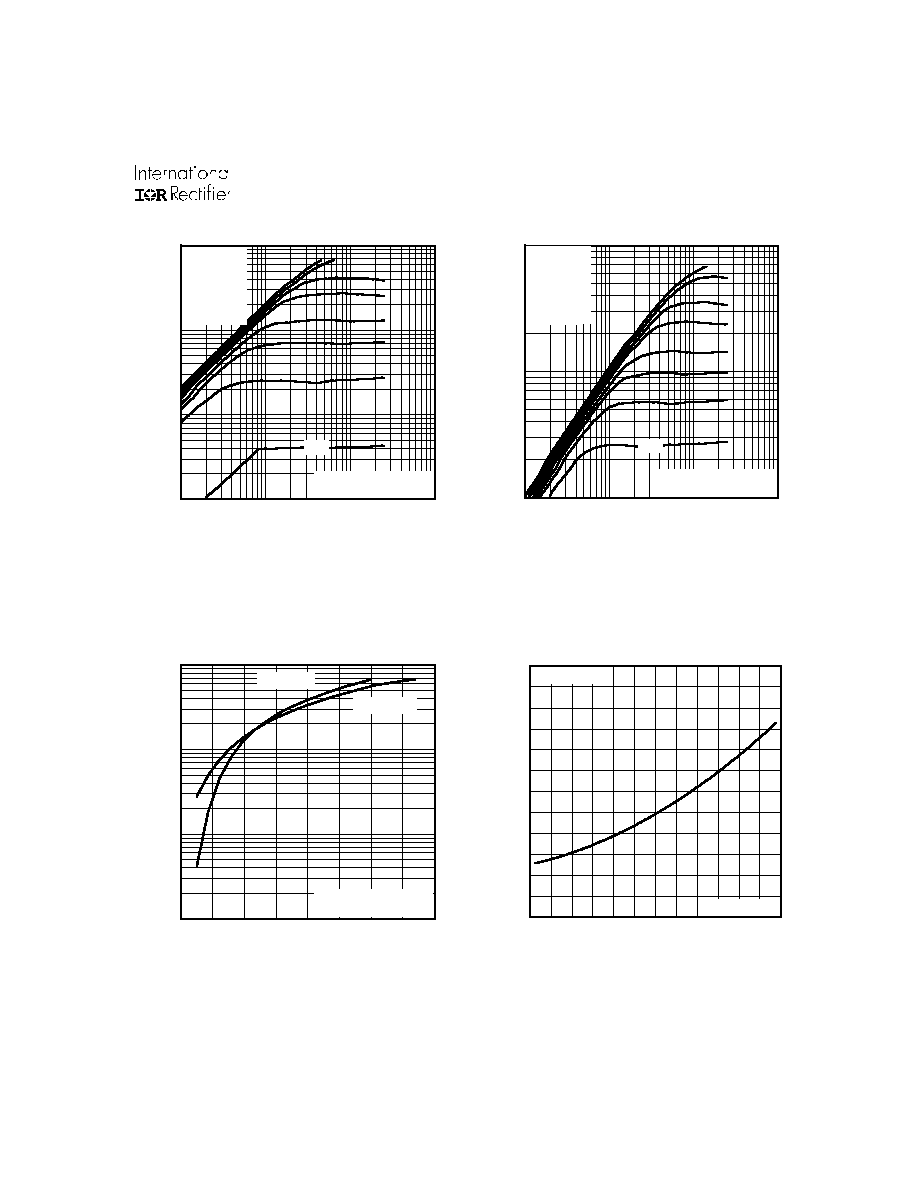

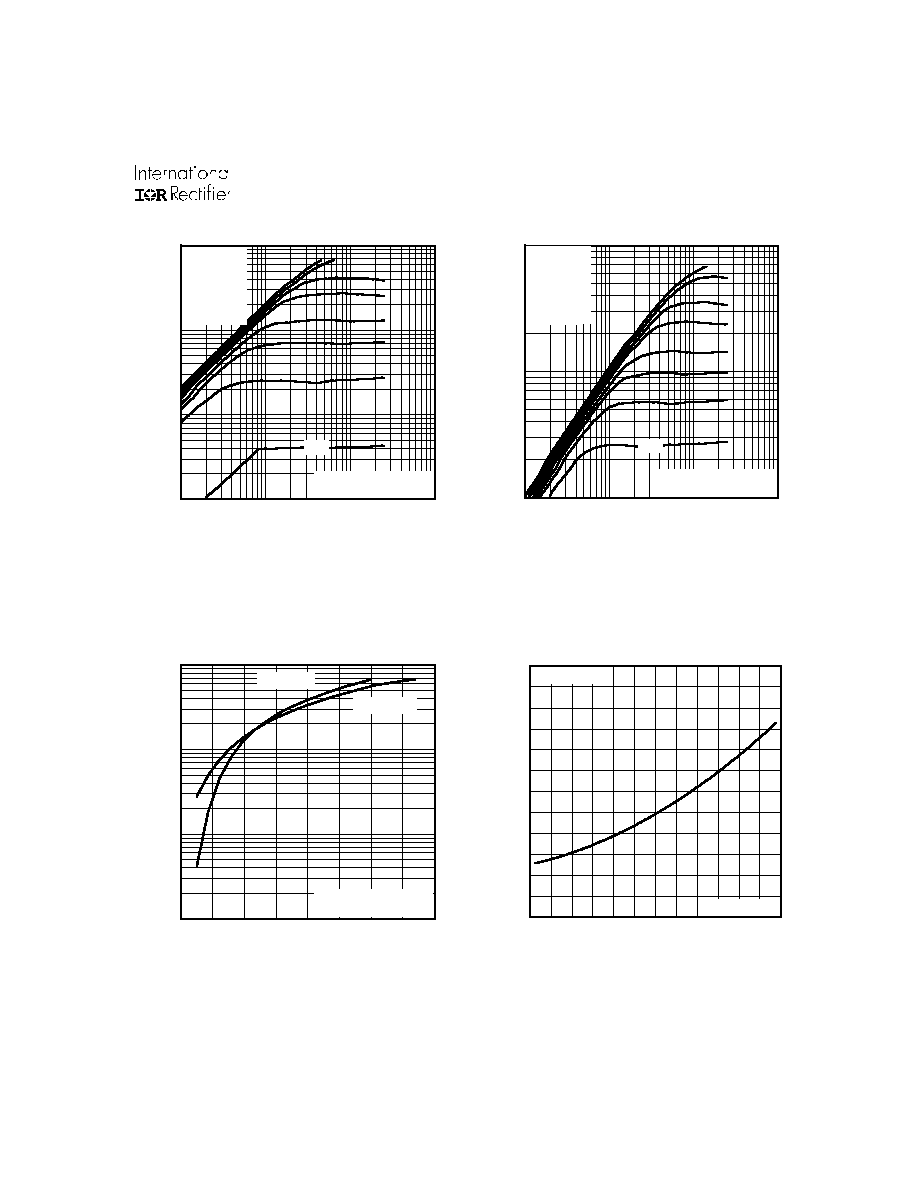

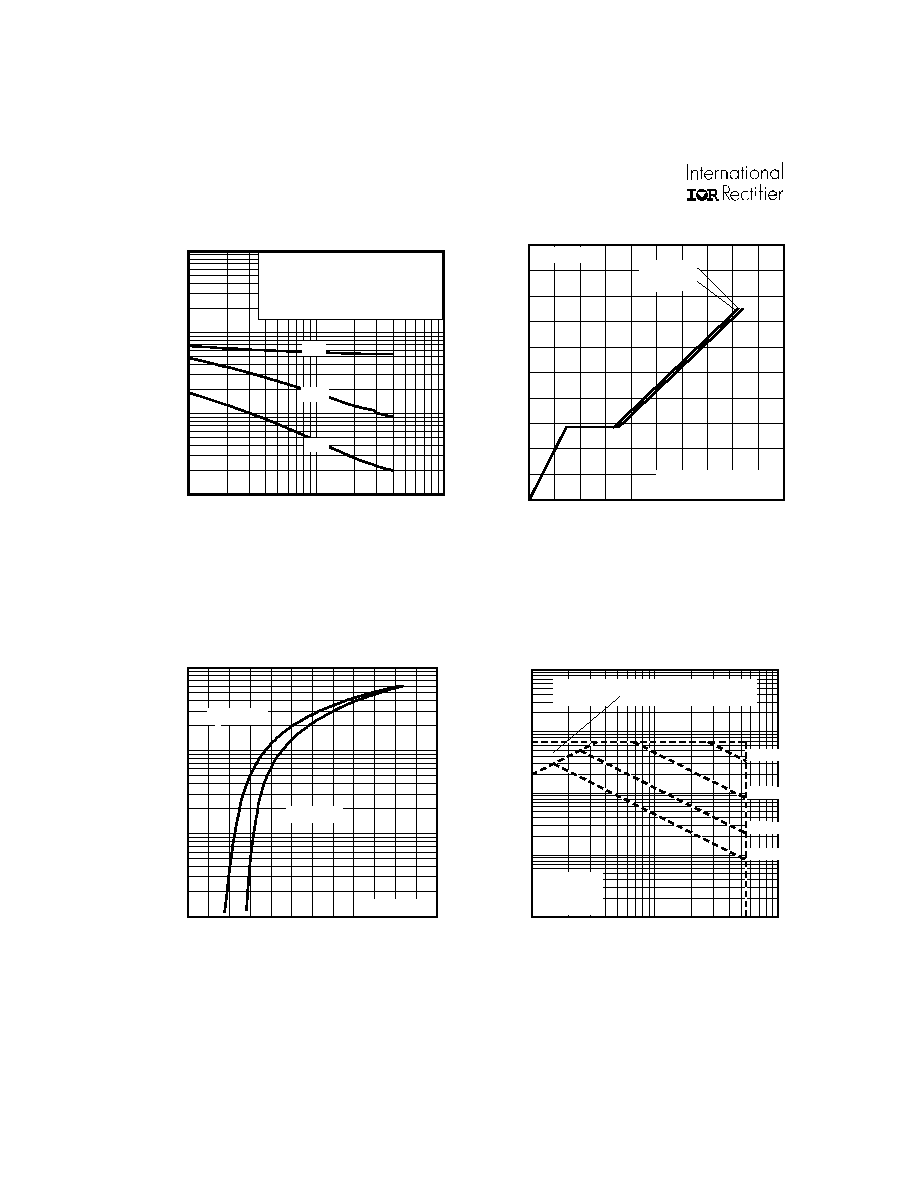

Fig 4. Normalized On-Resistance

Vs. Temperature

Fig 2. Typical Output Characteristics

Fig 1. Typical Output Characteristics

Fig 3. Typical Transfer Characteristics

1

10

100

1000

0.1

1

10

100

20µs PULSE WIDTH

T = 25 C

J

°

TOP

BOTTOM

VGS

15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

4.5V

V , Drain-to-Source Voltage (V)

I , Drain-to-Source Current (A)

DS

D

4.5V

10

100

1000

0.1

1

10

100

20µs PULSE WIDTH

T = 175 C

J

°

TOP

BOTTOM

VGS

15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

4.5V

V , Drain-to-Source Voltage (V)

I , Drain-to-Source Current (A)

DS

D

4.5V

1

10

100

1000

4

6

8

10

12

V = 25V

20µs PULSE WIDTH

DS

V , Gate-to-Source Voltage (V)

I , Drain-to-Source Current (A)

GS

D

T = 25 C

J

°

T = 175 C

J

°

-60 -40 -20

0

20 40 60 80 100 120 140 160 180

0.0

0.5

1.0

1.5

2.0

2.5

3.0

T , Junction Temperature ( C)

R , Drain-to-Source On Resistance

(Normalized)

J

DS(on)

°

V

=

I =

GS

D

10V

169A

IRF1405

4

www.irf.com

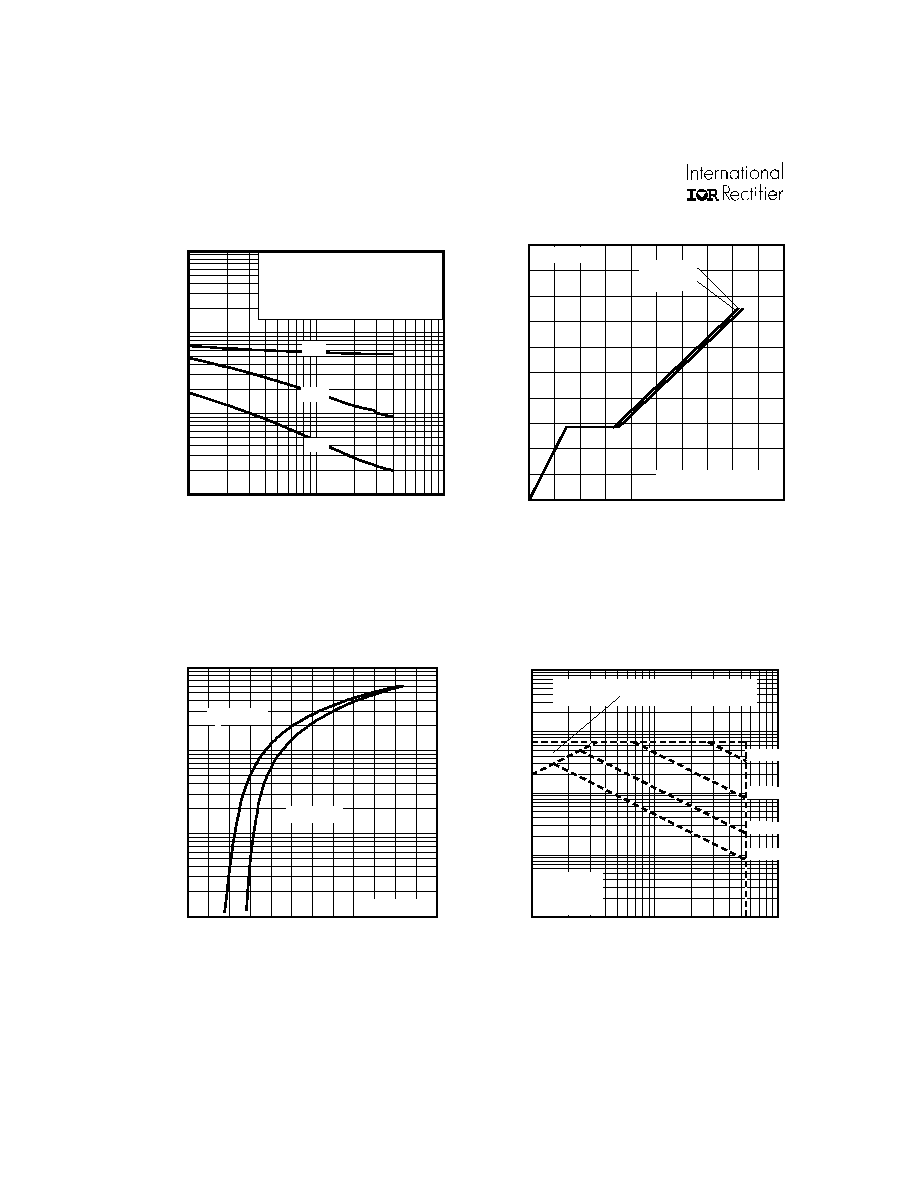

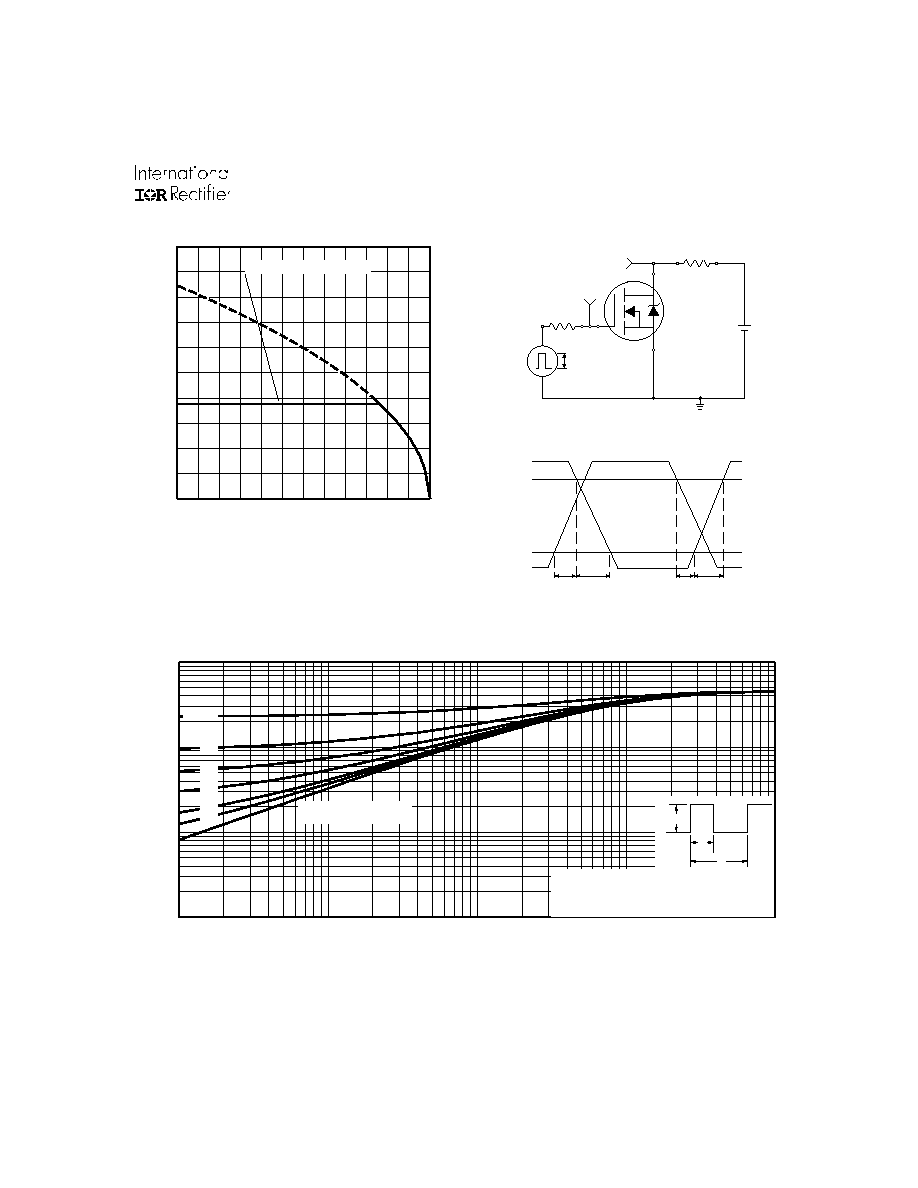

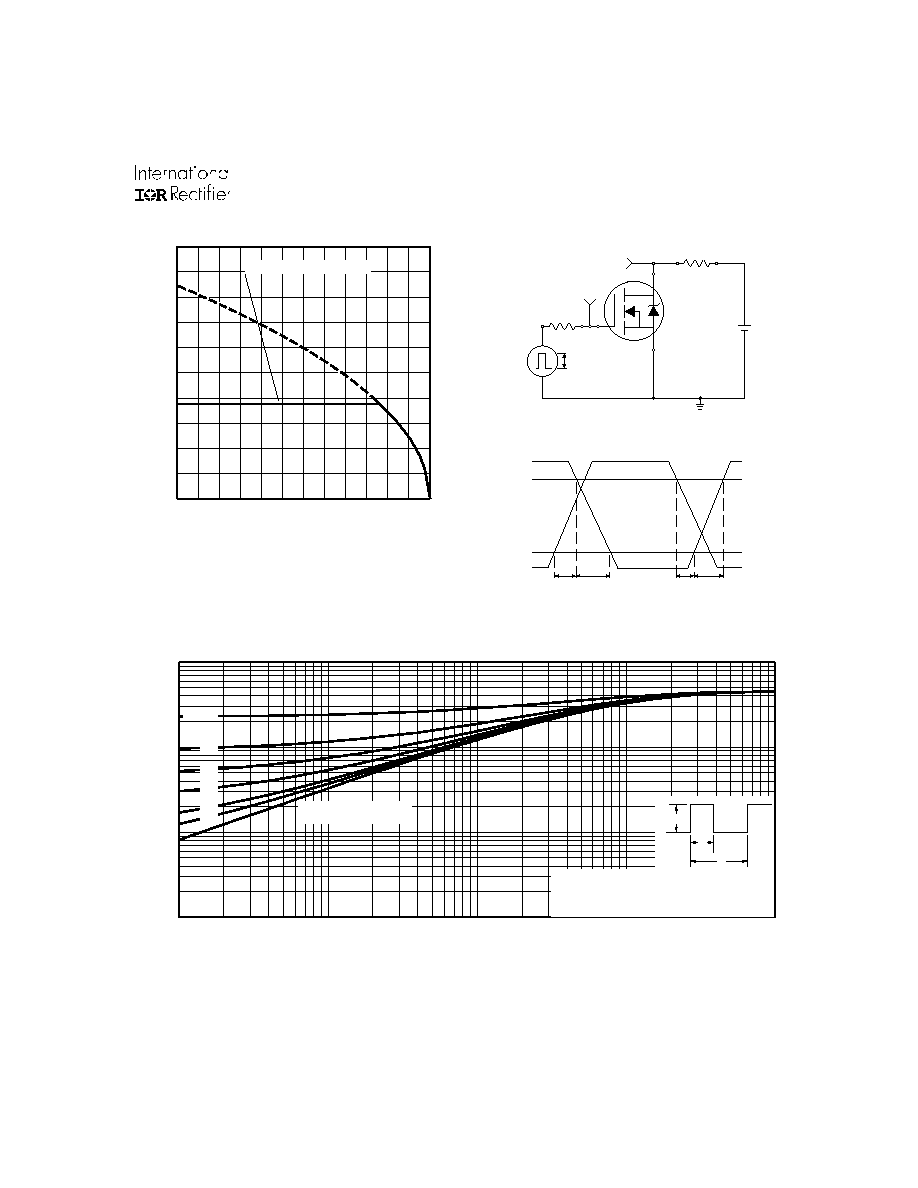

Fig 8. Maximum Safe Operating Area

Fig 6. Typical Gate Charge Vs.

Gate-to-Source Voltage

Fig 5. Typical Capacitance Vs.

Drain-to-Source Voltage

Fig 7. Typical Source-Drain Diode

Forward Voltage

0

60

120

180

240

300

0

4

8

12

16

20

Q , Total Gate Charge (nC)

V , Gate-to-Source Voltage (V)

G

GS

FOR TEST CIRCUIT

SEE FIGURE

I =

D

13

101A

V

= 27V

DS

V

= 44V

DS

1

10

100

1000

0.0

0.5

1.0

1.5

2.0

2.5

3.0

V ,Source-to-Drain Voltage (V)

I , Reverse Drain Current (A)

SD

SD

V = 0 V

GS

T = 25 C

J

°

T = 175 C

J

°

1

10

100

1000

10000

1

10

100

OPERATION IN THIS AREA LIMITED

BY R

DS(on)

Single Pulse

T

T

= 175 C

= 25 C

°

°

J

C

V , Drain-to-Source Voltage (V)

I , Drain Current (A)

I , Drain Current (A)

DS

D

10us

100us

1ms

10ms

1

10

100

VDS, Drain-to-Source Voltage (V)

100

1000

10000

100000

C, Capacitance(pF)

Coss

Crss

Ciss

VGS = 0V, f = 1 MHZ

Ciss = Cgs + Cgd, Cds SHORTED

Crss = Cgd

Coss = Cds + Cgd

IRF1405

www.irf.com

5

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Fig 9. Maximum Drain Current Vs.

Case Temperature

V

DS

90%

10%

V

GS

t

d(on)

t

r

t

d(off)

t

f

V

DS

Pulse Width

1

µs

Duty Factor

0.1 %

R

D

V

GS

R

G

D.U.T.

10V

+

-

V

DD

Fig 10a. Switching Time Test Circuit

Fig 10b. Switching Time Waveforms

0.001

0.01

0.1

1

0.00001

0.0001

0.001

0.01

0.1

Notes:

1. Duty factor D =

t / t

2. Peak T = P

x Z

+ T

1

2

J

DM

thJC

C

P

t

t

DM

1

2

t , Rectangular Pulse Duration (sec)

Thermal Response

(Z )

1

thJC

0.01

0.02

0.05

0.10

0.20

D = 0.50

SINGLE PULSE

(THERMAL RESPONSE)

25

50

75

100

125

150

175

0

40

80

120

160

200

T , Case Temperature ( C)

I , Drain Current (A)

°

C

D

LIMITED BY PACKAGE