| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LT1124AC | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

LT1124/LT1125

s

100% Tested Low Voltage Noise: 2.7nV/

Hz Typ

4.2nV/

Hz Max

s

Slew Rate: 4.5V/

µ

s Typ

s

Gain Bandwidth Product: 12.5MHz Typ

s

Offset Voltage, Prime Grade: 70

µ

V Max

Low Grade: 100

µ

V Max

s

High Voltage Gain: 5 Million Min

s

Supply Current Per Amplifier: 2.75mA Max

s

Common Mode Rejection: 112dB Min

s

Power Supply Rejection: 116dB Min

s

Available in 8-Pin SO Package

Dual/Quad Low Noise,

High Speed Precision Op Amps

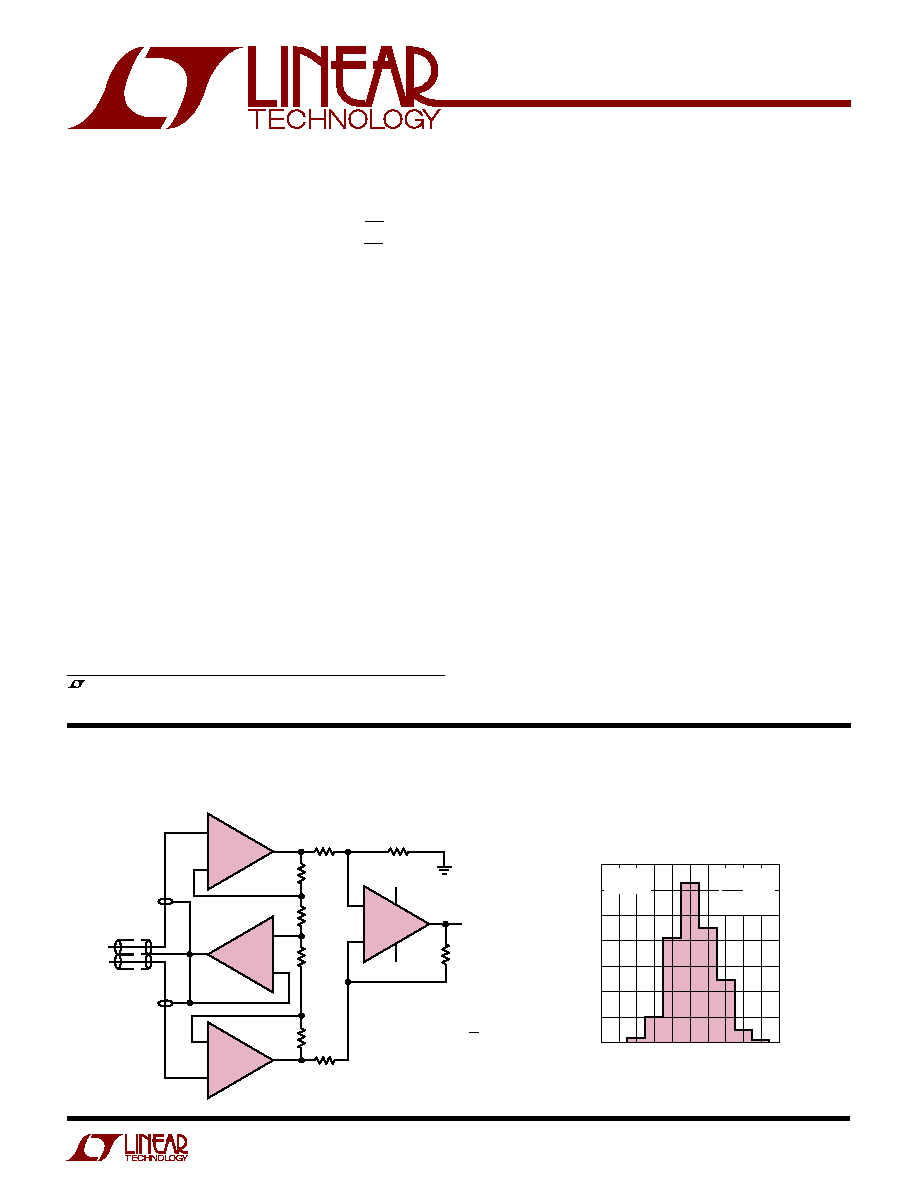

Instrumentation Amplifier with Shield Driver

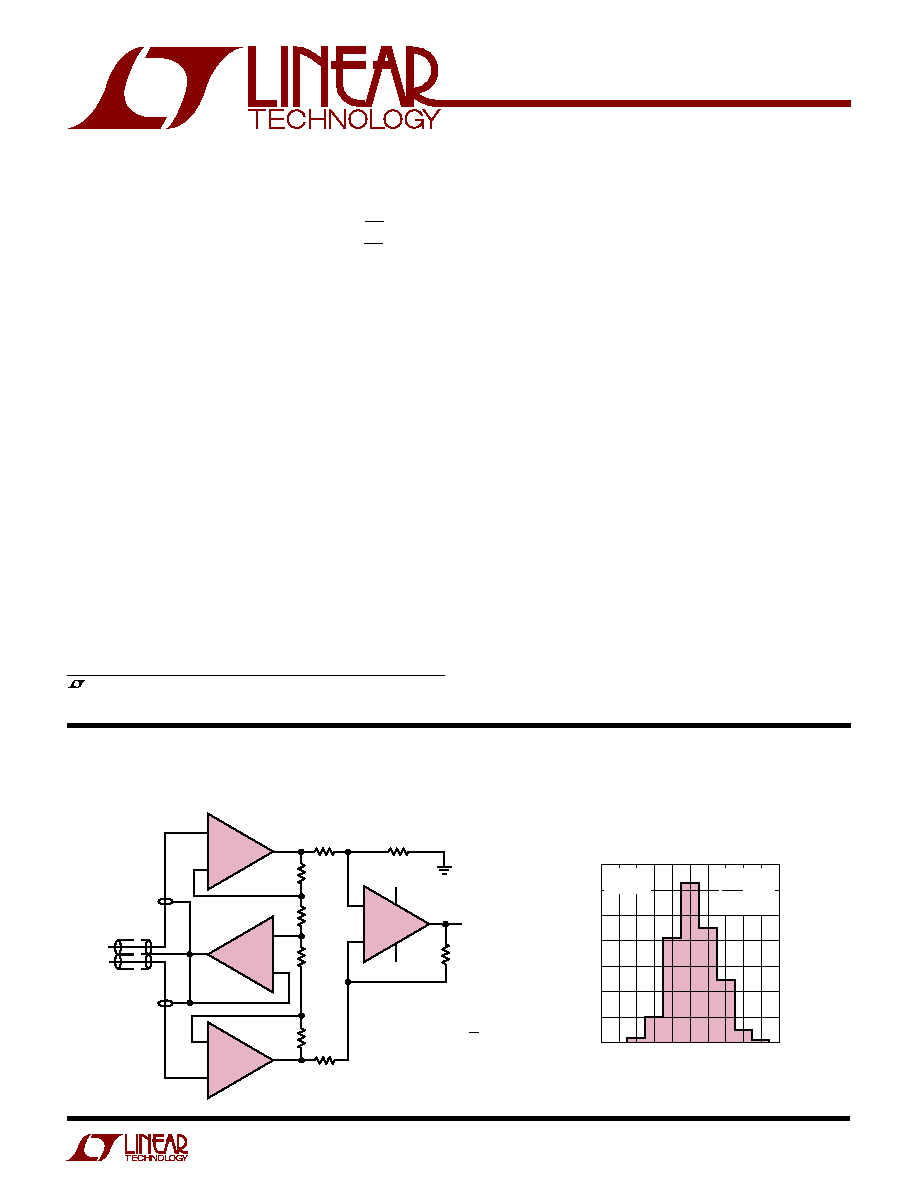

Input Offset Voltage Distribution

(All Packages, LT1124 and LT1125)

The LT

Æ

1124 dual and LT1125 quad are high performance

op amps that offer higher gain, slew rate and bandwidth

than the industry standard OP-27 and competing OP-270/

OP-470 op amps. In addition, the LT1124/LT1125 have

lower I

B

and I

OS

than the OP-27; lower V

OS

and noise

than the OP-270/OP-470.

In the design, processing and testing of the device, par-

ticular attention has been paid to the optimization of the

entire distribution of several key parameters. Slew rate,

gain bandwidth and 1kHz noise are 100% tested for each

individual amplifier. Consequently, the specifications of

even the lowest cost grades (the LT1124C and the

LT1125C) have been spectacularly improved compared

to equivalent grades of competing amplifiers.

Power consumption of the LT1124 is one half of two

OP-27s. Low power and high performance in an 8-pin SO

package make the LT1124 a first choice for surface mounted

systems and where board space is restricted.

For a decompensated version of these devices, with three

times higher slew rate and bandwidth, please see the

LT1126/LT1127 data sheet.

s

Two and Three Op Amp Instrumentation Amplifiers

s

Low Noise Signal Processing

s

Active Filters

s

Microvolt Accuracy Threshold Detection

s

Strain Gauge Amplifiers

s

Direct Coupled Audio Gain Stages

s

Tape Head Preamplifiers

s

Infrared Detectors

FEATURES

DESCRIPTIO

U

APPLICATIO S

U

Protected by U.S. patents 4,775,884 and 4,837,496.

, LTC and LT are registered trademarks of Linear Technology Corporation.

TYPICAL APPLICATIO

U

+

≠

1/4

LT1125

1124/25 TA01

+

≠

≠

+

1/4

LT1125

1/4

LT1125

≠15V

15V

OUTPUT

1/4

LT1125

30k

1k

R

F

3.4k

R

G

100

R

F

3.4k

30k

1k

5

4

6

11

7

1

3

2

10

9

8

14

13

12

+

≠

INPUT

GUARD

GUARD

= 30 (1 + R

F

/R

G

)

1000

= 170kHz

= 400kHz

= 3.8

µ

V/ Hz AT OUTPUT

= 35

µ

V

GAIN

POWER BW

SMALL-SIGNAL BW

NOISE

V

OS

R

G

100

+

≠

INPUT OFFSET VOLTAGE (

µ

V)

≠100

PERCENT OF UNITS

10

20

30

60

1124/25 TA02

≠ 60

≠ 20

V

S

=

±

15V

T

A

= 25

∞

C

DUALS

QUADS

2316 UNITS

TESTED

758

200

100

20

0

2

LT1124/LT1125

LT1124AC/AI/AM

LT1124/C/I/M

LT1125AC/AM

LT1125/C/M

SYMBOL

PARAMETER

CONDITIONS (Note 2)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

V

OS

Input Offset Voltage

LT1124

20

70

25

100

µ

V

LT1125

25

90

30

140

µ

V

V

OS

Long Term Input Offset

0.3

0.3

µ

V/Mo

Time

Voltage Stability

I

OS

Input Offset Current

LT1124

5

15

6

20

nA

LT1125

6

20

7

30

nA

LT1125CJ

LT1125ACN

LT1125CN

LT1125AMJ

LT1125MJ

Operating Temperature Range

LT1124AC/LT1124C

LT1125AC/LT1125C (Note 10) .......... ≠ 40

∞

C to 85

∞

C

LT1124AI/LT1124I ............................ ≠ 40

∞

C to 85

∞

C

LT1124AM/LT1124M

LT1125AM/LT1125M ...................... ≠ 55

∞

C to 125

∞

C

Supply Voltage .....................................................

±

22V

Input Voltages ......................... Equal to Supply Voltage

Output Short-Circuit Duration ......................... Indefinite

Differential Input Current (Note 6) .....................

±

25mA

Lead Temperature (Soldering, 10 sec)................. 300

∞

C

Storage Temperature Range ................ ≠ 65

∞

C to 150

∞

C

A

U

G

W

A

W

U

W

A

R

BSOLUTE

XI

TI

S

LT1124CJ8

LT1124ACN8

LT1124CN8

LT1124AMJ8

LT1124MJ8

W

U

U

PACKAGE/ORDER I FOR ATIO

ORDER PART

NUMBER

LT1125CS

ELECTRICAL C

C

HARA TERISTICS

ORDER PART

NUMBER

S8 PART MARKING

LT1124CS8

LT1124AIS8

LT1124IS8

1124

1124AI

1124I

(Note 1)

1

2

3

4

8

7

6

5

TOP VIEW

≠IN A

OUT A

V

+

OUT B

+IN A

V

≠

+IN B

≠IN B

S8 PACKAGE

8-LEAD PLASTIC SO

A

B

T

JMAX

= 140

∞

C,

JA

= 190

∞

C

NOTE: THIS PIN CONFIGURATION DIFFERS FROM THE

8-PIN PDIP CONFIGURATION. INSTEAD, IT FOLLOWS

THE INDUSTRY STANDARD LT1013DS8 SO PACKAGE

PIN LOCATIONS

T

JMAX

= 140

∞

C,

JA

= 130

∞

C

1

2

3

4

5

6

7

8

TOP VIEW

SW PACKAGE

16-LEAD PLASTIC (WIDE) SO

16

15

14

13

12

11

10

9

OUT A

≠IN A

+IN A

V

+

+IN B

≠IN B

OUT B

NC

OUT D

≠IN D

+IN D

V

≠

+IN C

≠IN C

OUT C

NC

B

A

C

D

1

2

3

4

8

7

6

5

TOP VIEW

OUT A

≠IN A

+IN A

V

≠

V

+

OUT B

≠IN B

+IN B

N8 PACKAGE

8-LEAD PDIP

J8 PACKAGE

8-LEAD CERDIP

A

B

T

JMAX

= 160

∞

C,

JA

= 100

∞

C (J8)

T

JMAX

= 140

∞

C,

JA

= 130

∞

C (N8)

1

2

3

4

5

6

7

TOP VIEW

N PACKAGE

14-LEAD PDIP

J PACKAGE

14-LEAD CERDIP

14

13

12

11

10

9

8

OUT A

≠IN A

+IN A

V

+

+IN B

≠IN B

OUT B

OUT D

≠IN D

+IN D

V

≠

+IN C

≠IN C

OUT C

B

A

C

D

T

JMAX

= 160

∞

C,

JA

= 80

∞

C (J)

T

JMAX

= 140

∞

C,

JA

= 110

∞

C (N)

T

A

= 25

∞

C, V

S

=

±

15V, unless otherwise noted.

3

LT1124/LT1125

The

q

denotes the specifications which apply over the ≠55

∞

C

T

A

125

∞

C temperature range, V

S

=

±

15V, unless otherwise noted.

LT1124AC/AI/AM

LT1124C/I/M

LT1125AC/AM

LT1125C/M

SYMBOL

PARAMETER

CONDITIONS (Note 2)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

I

B

Input Bias Current

±

7

±

20

±

8

±

30

nA

e

n

Input Noise Voltage

0.1Hz to 10Hz (Notes 8, 9)

70

200

70

nV

P-P

Input Noise Voltage Density

f

O

= 10Hz (Note 4)

3.0

5.5

3.0

5.5

nV/

Hz

f

O

= 1000Hz (Note 3)

2.7

4.2

2.7

4.2

nV/

Hz

i

n

Input Noise Current Density

f

O

= 10Hz

1.3

1.3

pA/

Hz

f

O

= 1000Hz

0.3

0.3

pA/

Hz

V

CM

Input Voltage Range

±

12

±

12.8

±

12

±

12.8

V

CMRR

Common Mode Rejection Ratio

V

CM

=

±

12V

112

126

106

124

dB

PSRR

Power Supply Rejection Ratio

V

S

=

±

4V to

±

18V

116

126

110

124

dB

A

VOL

Large-Signal Voltage Gain

R

L

10k, V

OUT

=

±

10V

5

17

3.0

15

V/

µ

V

R

L

2k, V

OUT

=

±

10V

2

4

1.5

3

V/

µ

V

V

OUT

Maximum Output Voltage Swing

R

L

2k

±

13

±

13.8

±

12.5

±

13.8

V

SR

Slew Rate

R

L

2k (Notes 3, 7)

3

4.5

2.7

4.5

V/

µ

s

GBW

Gain Bandwidth Product

f

O

= 100kHz (Note 3)

9

12.5

8

12.5

MHz

Z

O

Open-Loop Output Resistance

V

OUT

= 0, I

OUT

= 0

75

75

I

S

Supply Current per Amplifier

2.3

2.75

2.3

2.75

mA

Channel Separation

f

10Hz (Note 9)

134

150

130

150

dB

V

OUT

=

±

10V, R

L

= 2k

ELECTRICAL C

C

HARA TERISTICS

T

A

= 25

∞

C, V

S

=

±

15V, unless otherwise noted.

LT1124AM

LT1124M

LT1125AM

LT1125M

SYMBOL

PARAMETER

CONDITIONS (Note 2)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

V

OS

Input Offset Voltage

LT1124

q

50

170

60

250

µ

V

LT1125

q

55

190

70

290

µ

V

V

OS

Average Input Offset

(Note 5)

q

0.3

1.0

0.4

1.5

µ

V/

∞

C

Temp

Voltage Drift

I

OS

Input Offset Current

LT1124

q

18

45

20

60

nA

LT1125

q

18

55

20

70

nA

I

B

Input Bias Current

q

±

18

±

55

±

20

±

70

nA

V

CM

Input Voltage Range

q

±

11.3

±

12

±

11.3

±

12

V

CMRR

Common Mode Rejection Ratio

V

CM

=

±

11.3V

q

106

122

100

120

dB

PSRR

Power Supply Rejection Ratio

V

S

=

±

4V to

±

18V

q

110

122

104

120

dB

A

VOL

Large-Signal Voltage Gain

R

L

10k, V

OUT

=

±

10V

q

3

10

2.0

10

V/

µ

V

R

L

2k, V

OUT

=

±

10V

q

1

3

0.7

2

V/

µ

V

V

OUT

Maximum Output Voltage Swing

R

L

2k

q

±

12.5

±

13.6

±

12

±

13.6

V

SR

Slew Rate

R

L

2k (Notes 3, 7)

q

2.3

3.8

2

3.8

V/

µ

s

I

S

Supply Current per Amplifier

q

2.5

3.25

2.5

3.25

mA

4

LT1124/LT1125

Note 7: Slew rate is measured in A

V

= ≠1; input signal is

±

7.5V, output

measured at

±

2.5V.

Note 8: 0.1Hz to 10Hz noise can be inferred from the 10Hz noise voltage

density test. See the test circuit and frequency response curve for 0.1Hz to

10Hz tester in the Applications Information section of the LT1007 or

LT1028 data sheets.

Note 9: This parameter is guaranteed but not tested.

Note 10: The LT1124C/LT1125C and LT1124AC/LT1125AC are guaranteed

to meet specified performance from 0

∞

C to 70

∞

C and are designed,

characterized and expected to meet these extended temperature limits, but

are not tested at ≠40

∞

C and 85

∞

C. The LT1124AI and LT1124I are

guaranteed to meet the extended temperature limits.

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: Typical parameters are defined as the 60% yield of parameter

distributions of individual amplifiers; i.e., out of 100 LT1125s (or 100

LT1124s) typically 240 op amps (or 120) will be better than the indicated

specification.

Note 3: This parameter is 100% tested for each individual amplifier.

Note 4: This parameter is sample tested only.

Note 5: This parameter is not 100% tested.

Note 6: The inputs are protected by back-to-back diodes. Current limiting

resistors are not used in order to achieve low noise. If differential input

voltage exceeds

±

1.4V, the input current should be limited to 25mA.

ELECTRICAL C

C

HARA TERISTICS

The

q

denotes the specifications which apply over the 0

∞

C

T

A

70

∞

C

temperature range, V

S

=

±

15V, unless otherwise noted.

LT1124AC

LT1124C

LT1125AC

LT1125C

SYMBOL

PARAMETER

CONDITIONS (Note 2)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

V

OS

Input Offset Voltage

LT1124

q

35

120

45

170

µ

V

LT1125

q

40

140

50

210

µ

V

V

OS

Average Input Offset

(Note 5)

q

0.3

1

0.4

1.5

µ

V/

∞

C

Temp

Voltage Drift

I

OS

Input Offset Current

LT1124

q

6

25

7

35

nA

LT1125

q

7

35

8

45

nA

I

B

Input Bias Current

q

±

8

±

35

±

9

±

45

nA

V

CM

Input Voltage Range

q

±

11.5

±

12.4

±

11.5

±

12.4

V

CMRR

Common Mode Rejection Ratio

V

CM

=

±

11.5V

q

109

125

102

122

dB

PSRR

Power Supply Rejection Ratio

V

S

=

±

4V to

±

18V

q

112

125

107

122

dB

A

VOL

Large-Signal Voltage Gain

R

L

10k, V

OUT

=

±

10V

q

4.0

15

2.5

14

V/

µ

V

R

L

2k, V

OUT

=

±

10V

q

1.5

3.5

1.0

2.5

V/

µ

V

V

OUT

Maximum Output Voltage Swing

R

L

2k

q

±

12.5

±

13.7

±

12

±

13.7

V

SR

Slew Rate

R

L

2k (Notes 3, 7)

q

2.6

4

2.4

4

V/

µ

s

I

S

Supply Current per Amplifier

q

2.4

3

2.4

3

mA

The

q

denotes the specifications which apply over the ≠40

∞

C

T

A

85

∞

C temperature range, V

S

=

±

15V,

unless otherwise noted. (Note 10)

LT1124AC/AI

LT1124C/I

LT1125AC

LT1125C

SYMBOL

PARAMETER

CONDITIONS (Note 2)

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

V

OS

Input Offset Voltage

LT1124

q

40

140

50

200

µ

V

LT1125

q

45

160

55

240

µ

V

V

OS

Average Input Offset

(Note 5)

q

0.3

1

0.4

1.5

µ

V/

∞

C

Temp

Voltage Drift

I

OS

Input Offset Current

LT1124

q

15

40

17

55

nA

LT1125

q

15

50

17

65

nA

I

B

Input Bias Current

q

±

15

±

50

±

17

±

65

nA

V

CM

Input Voltage Range

q

±

11.4

±

12.2

±

11.4

±

12.2

V

CMRR

Common Mode Rejection Ratio

V

CM

=

±

11.4V

q

107

124

101

121

dB

PSRR

Power Supply Rejection Ratio

V

S

=

±

4V to

±

18V

q

111

124

106

121

dB

A

VOL

Large-Signal Voltage Gain

R

L

10k, V

OUT

=

±

10V

q

3.5

12

2.2

12

V/

µ

V

R

L

2k, V

OUT

=

±

10V

q

1.2

3.2

0.8

2.3

V/

µ

V

V

OUT

Maximum Output Voltage Swing

R

L

2k

q

±

12.5

±

13.6

±

12

±

13.6

V

SR

Slew Rate

R

L

2k (Notes 3, 7)

q

2.4

3.9

2.1

3.9

V/

µ

s

I

S

Supply Current per Amplifier

q

2.4

3.25

2.4

3.25

mA

5

LT1124/LT1125

C

C

HARA TERISTICS

U

W

A

TYPICAL PERFOR

CE

0.1Hz to 10Hz Voltage Noise

0.01Hz to 1Hz Voltage Noise

Voltage Noise vs Frequency

Input Bias or Offset Current

Output Short-Circuit Current

Current Noise vs Frequency

vs Temperature

vs Time

Input Bias Current Over the

Common Mode Rejection Ratio

Power Supply Rejection Ratio

Common Mode Range

vs Frequency

vs Frequency

TIME (SECONDS)

0

VOLTAGE NOISE (40nV/DIV)

2

6

8

10

1124/25 G01

4

TIME (SECONDS)

0

VOLTAGE NOISE (40nV/DIV)

20

60

80

100

1124/25 G02

40

FREQUENCY (Hz)

3

RMS VOL

T

AGE NOISE DENSITY (nV/ Hz)

10

30

100

0.1

10

100

1000

1124/25 G03

1

1.0

MAXIMUM

TYPICAL

V

S

=

±

15V

T

A

= 25

∞

C

1/f CORNER

2.3Hz

FREQUENCY (Hz)

0.3

RMS CURRENT NOISE DENSITY (pA/ Hz)

1.0

3.0

10.0

10

1k

10k

1124 G04

0.1

100

V

S

=

±

15V

T

A

= 25

∞

C

TYPICAL

MAXIMUM

1/f CORNER

100Hz

TEMPERATURE (

∞

C)

≠75

0

INPUT BIAS OR OFFSET CURRENT (nA)

10

20

30

≠50

25

75

125

1124/25 G05

≠25

0

50

100

LT1124M/LT1125M

LT1124AM/LT1125AM

V

S

=

±

15V

TIME FROM OUTPUT SHORT TO GND (MINUTES)

0

0

20

40

50

2

3

4

LT1124 G06

1

V

S

=

±

15V

10

30

≠10

≠20

≠30

≠40

≠50

125

∞

C

25

∞

C

125

∞

C

SHOR

T

-CIRCUIT CURRENT (mA)

SINKING

SOURCING

≠ 55

∞

C

25

∞

C

≠55

∞

C

COMMON MODE INPUT VOLTAGE (V)

≠15

≠20

INPUT BIAS CURRENT (nA) ≠ 10

5

20

≠10

5

15

1124/25 G07

≠5

10

≠15

0

10

≠ 5

15

0

DEVICE WITH POSITIVE

INPUT CURRENT

DEVICE WITH NEGATIVE

INPUT CURRENT

V

S

=

±

15V

T

A

= 25

∞

C

FREQUENCY (Hz)

80

COMMON MODE REJECTION RATIO (dB)

100

120

140

160

1k

100k

1M

10M

1124/25 G08

10k

60

40

20

0

T

A

= 25

∞

C

V

S

=

±

15V

V

CM

=

±

10V

FREQUENCY (Hz)

1

0

POWER SUPPL

Y REJECTION RA

TIO (dB)

20

40

120

140

160

10

2

10

8

1124/25 G09

10

10

3

10

4

10

5

10

6

10

7

60

100

80

≠ PSRR

+PSRR

T

A

= 25

∞

C