| ÐлекÑÑоннÑй компоненÑ: DS26102 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

FEATURES

1 of 64

REV: 021403

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here:

www.maxim-ic.com/errata

.

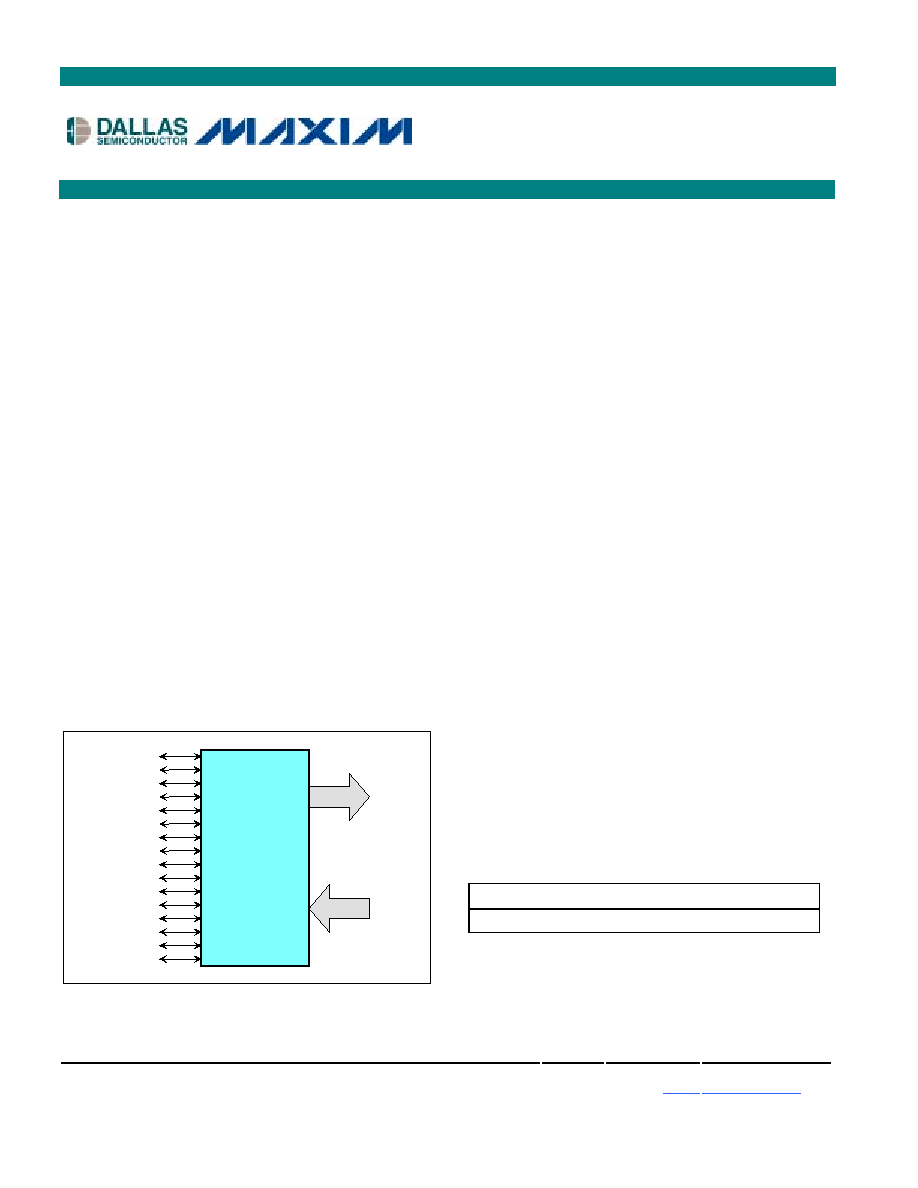

GENERAL DESCRIPTION

On the transmit side, the DS26102 receives ATM cells

from an ATM device through a UTOPIA II interface,

provides cell buffering (up to 4 cells), HEC generation

and insertion, cell scrambling, and converts the data

to a serial stream appropriate for interfacing to a

T1/E1 framer or transceiver. On the receive side, the

DS26102 receives a TDM stream from a T1/E1 framer

or transceiver; searches for the cell alignment; verifies

the HEC; provides cell filtering, descrambling, and cell

buffering; and passes the cells to an ATM device

through the UTOPIA II interface. Other low-level traffic

management functions are selectable for the transmit

and receive paths. The DS26102 can also be used in

fractional T1/E1 applications.

The DS26102 maps ATM cells to T1/E1 TDM frames

as per the ATM Forum Specifications af-phy-0016.000

and af-phy-0064.000. In the receive direction, the cell

delineation mechanism used for finding ATM cell

boundary within T1/E1 frame is performed as per ITU

I.432. The DS26102 provides a mapping solution for

up to 16 T1/E1 TDM ports. The terms physical layer

(PHY) and line side are used synonymously in this

document and refer to the device interfacing with the

line side of the DS26102. The terms ATM layer and

system side are used synonymously and refer to the

DS26102's UTOPIA II interface.

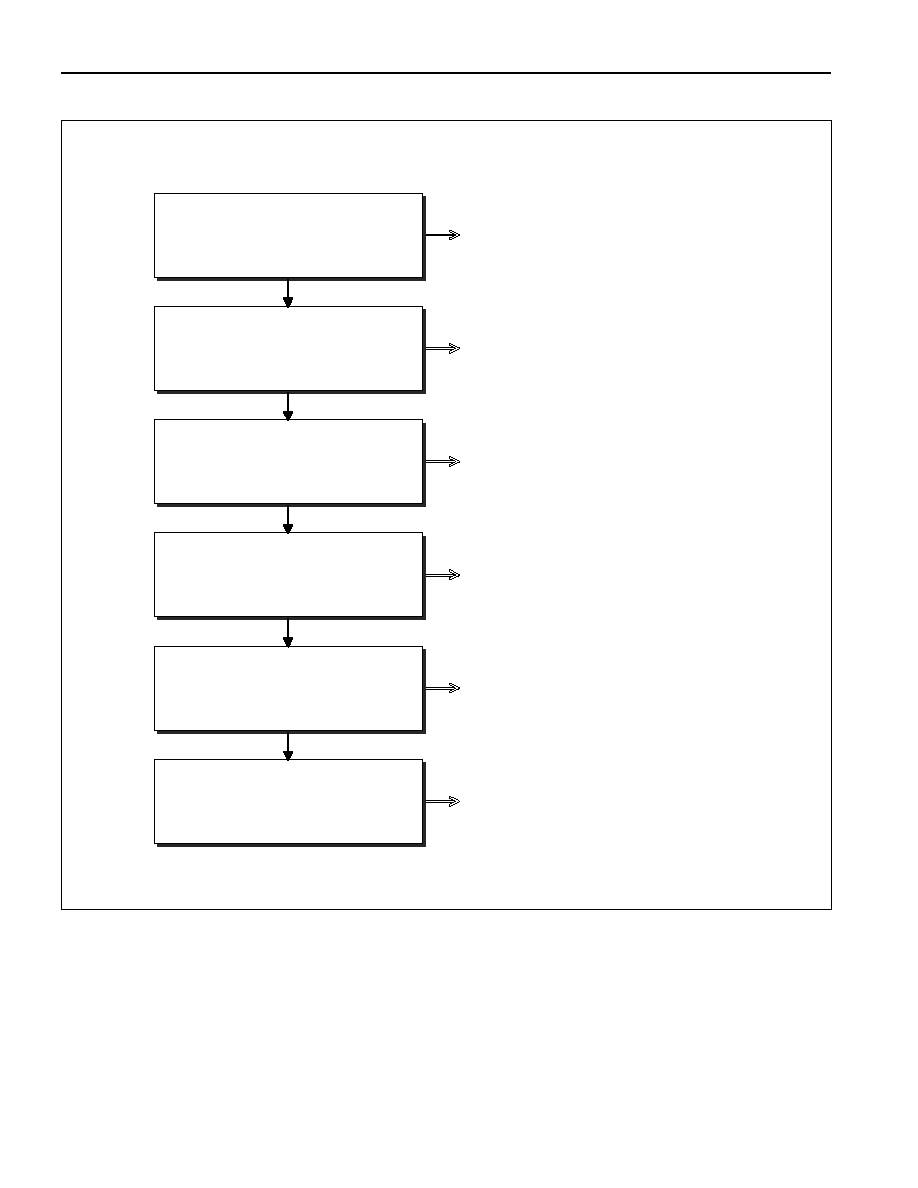

FUNCTIONAL DIAGRAM

FEATURES

§ Supports 16 T1/E1 TDM Ports

§ Supports Fractional T1/E1

§ Compliant to ATM Forum Specifications for ATM

Over T1 and E1

§ Standard UTOPIA II Interface to the ATM Layer

§ Configurable UTOPIA Address Range

§ Configurable Tx FIFO Depth to 2, 3, or 4 Cells

§ Optional Payload Scrambling in Transmit

Direction and Descrambling in Receive Direction

per ITU I.432

§ Optional HEC Insertion in Transmit Direction with

Programmable COSET Polynomial Addition

§ HEC-Based Cell Delineation

§ Single-Bit HEC Error Correction in the Receive

Direction

§ Receive HEC-Errored Cell Filtering

§ Receive Idle/Unassigned Cell Filtering

§ User-Definable Cell Filtering

§ 8-Bit Mux/Nonmux, Motorola/Intel Microprocessor

Interface

§ Internal Clock Generator Eliminates External

High-Speed Clocks

§ Internal One-Second Timer

§ Detects/Reports Up to Eight External Status

Signals with Interrupt Support

§ IEEE 1149.1 JTAG Boundary Scan Support

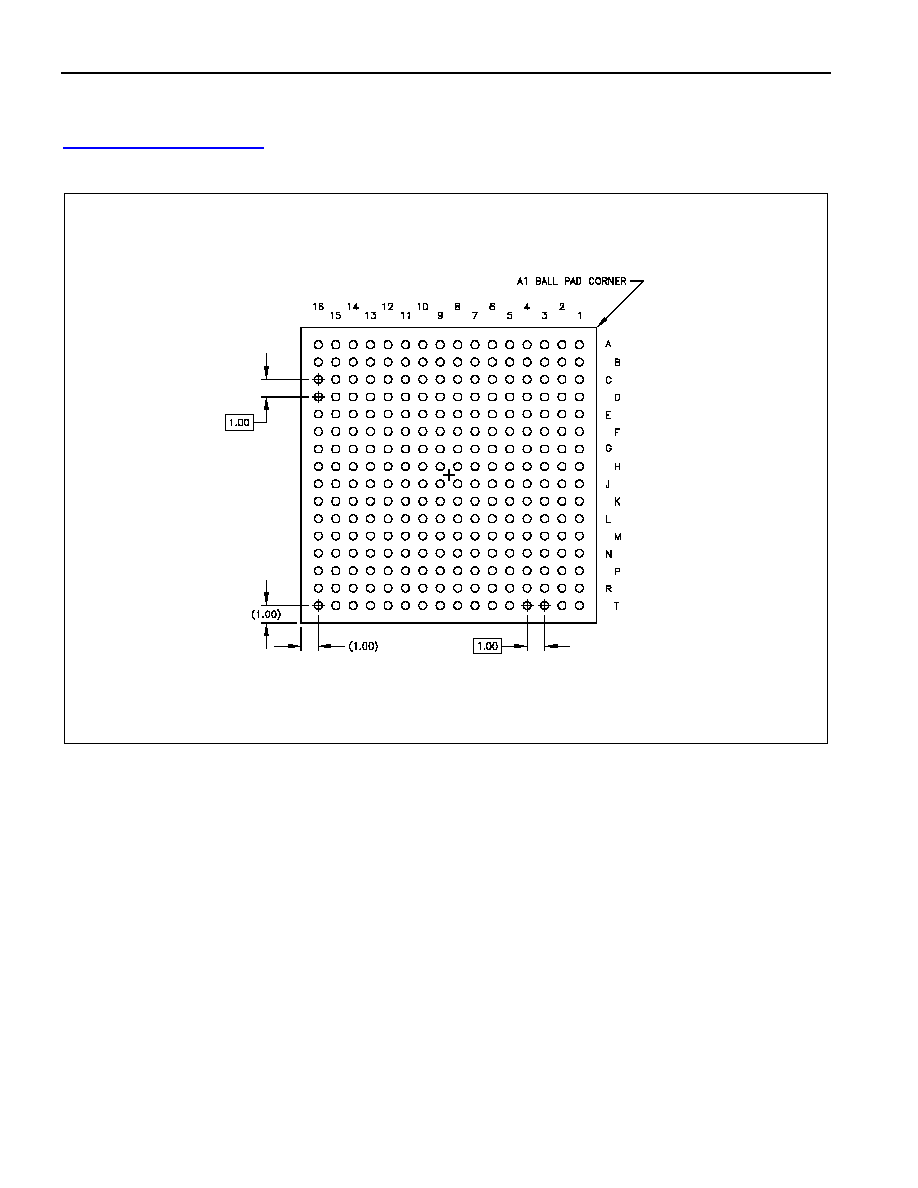

§

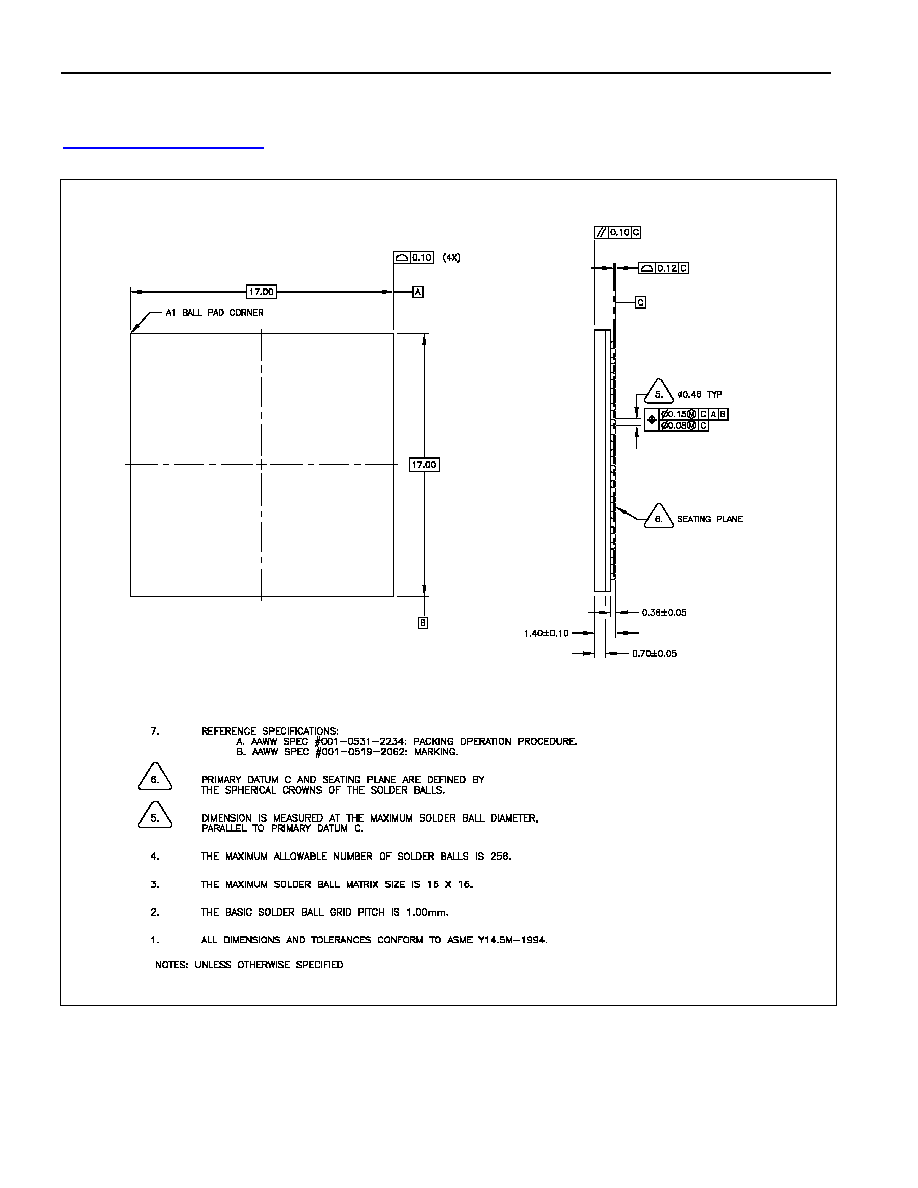

17mm x 17mm, 256-Pin CSBGA

Features continued on page 5.

APPLICATIONS

DSLAMS

ATM Over T1/E1

Routers

IMA

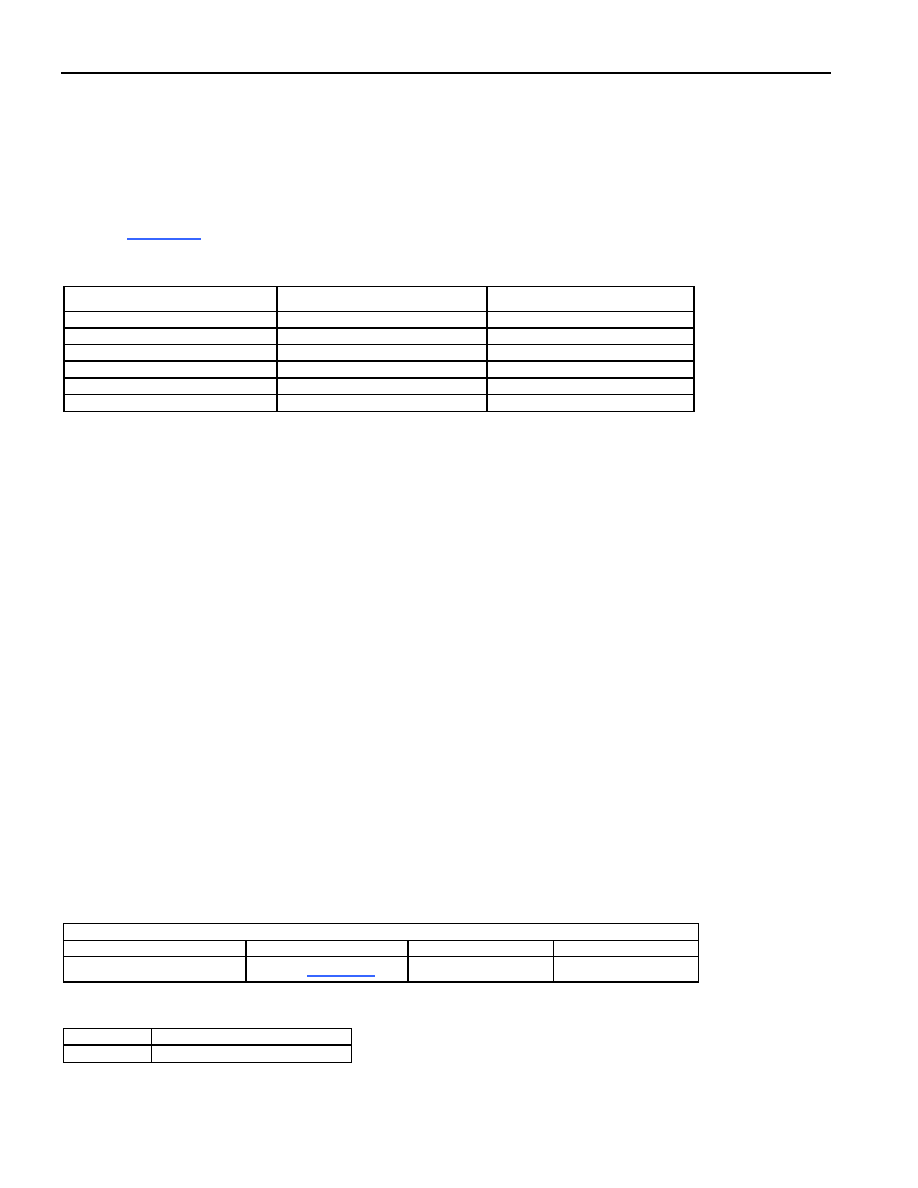

ORDERING INFORMATION

PART TEMP

RANGE

PIN-PACKAGE

DS26102

-40°C to +85°C

256 CSBGA

www.maxim-ic.com

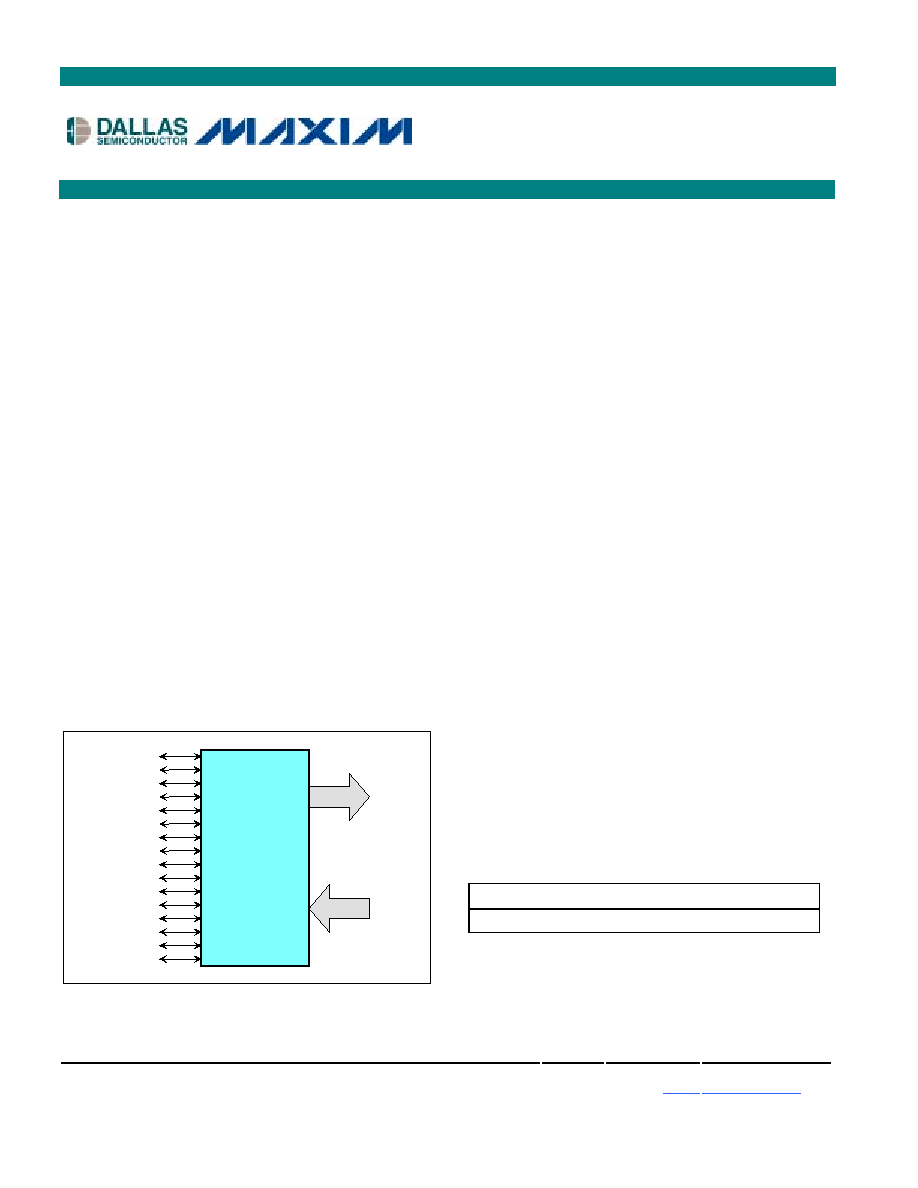

DS26102

16-Port TDM-to-ATM PHY

UTOPIA II

16 TDM

PORTS

DS26102

DS26102 16-Port TDM-to-ATM PHY

2 of 64

TABLE OF CONTENTS

1.

FEATURES ......................................................................................................................................5

2.

APPLICABLE STANDARDS............................................................................................................5

3.

ACRONYMS AND DEFINITIONS.....................................................................................................6

4.

BLOCK DIAGRAM ...........................................................................................................................7

5.

PIN DESCRIPTION ..........................................................................................................................8

6.

SIGNAL DEFINITIONS...................................................................................................................12

6.1

TDM S

IGNALS

..........................................................................................................................12

6.2

UTOPIA-S

IDE

S

IGNALS

............................................................................................................12

6.3

M

ICROPROCESSOR AND

S

YSTEM

I

NTERFACE

S

IGNALS

................................................................14

6.4

T

EST AND

JTAG S

IGNALS

.........................................................................................................16

7.

TRANSMIT OPERATION ...............................................................................................................17

7.1

UTOPIA-S

IDE

T

RANSMIT

--M

UXED

M

ODE WITH

1 TXCLAV ........................................................17

7.2

UTOPIA-S

IDE

T

RANSMIT

--D

IRECT

S

TATUS

M

ODE

(MULTITXCLAV) .........................................19

7.3

T

RANSMIT

P

ROCESSING

............................................................................................................20

7.4

P

HYSICAL

-S

IDE

T

RANSMIT

.........................................................................................................21

8.

RECEIVE OPERATION..................................................................................................................23

8.1

P

HYSICAL

-S

IDE

R

ECEIVE

...........................................................................................................23

8.2

R

ECEIVE

P

ROCESSING

..............................................................................................................25

8.3

UTOPIA-S

IDE

R

ECEIVE

--M

UXED

M

ODE WITH

1 RXCLAV..........................................................27

8.4

UTOPIA-S

IDE

R

ECEIVE

--D

IRECT

S

TATUS

M

ODE

(MULTIRXCLAV) ...........................................28

9.

REGISTER MAPPING....................................................................................................................30

10.

REGISTER DEFINITIONS..............................................................................................................31

10.1

T

RANSMIT

R

EGISTERS

..............................................................................................................31

10.2

S

TATUS

R

EGISTERS

..................................................................................................................35

10.3

R

ECEIVE

R

EGISTERS

................................................................................................................36

11.

JTAG BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT....................................45

11.1

I

NSTRUCTION

R

EGISTER

............................................................................................................48

11.2

T

EST

R

EGISTERS

......................................................................................................................49

12.

OPERATING PARAMETERS.........................................................................................................52

13.

CRITICAL TIMING INFORMATION................................................................................................53

14.

THERMAL INFORMATION ............................................................................................................59

15.

APPLICATIONS INFORMATION ...................................................................................................60

15.1

A

PPLICATION IN

ATM U

SER

-N

ETWORK

I

NTERFACES

...................................................................60

15.2

I

NTERFACING WITH

F

RAMERS

....................................................................................................60

15.3

F

RACTIONAL

T1/E1 S

UPPORT

...................................................................................................61

16.

PACKAGE INFORMATION............................................................................................................62

17.

REVISION HISTORY......................................................................................................................64

DS26102 16-Port TDM-to-ATM PHY

3 of 64

TABLE OF FIGURES

Figure 4-1. Block Diagram ....................................................................................................................... 7

Figure 7-1. Polling Phase and Selection Phase at Transmit Interface.....................................................18

Figure 7-2. End and Restart of Cell at Transmit Interface .......................................................................18

Figure 7-3. Transmission to PHY Paused for Three Cycles ....................................................................19

Figure 7-4. Example of Direct Status Indication, Transmit Direction .......................................................20

Figure 7-5. Transmit Cell Flow and Processing ......................................................................................21

Figure 7-6. Transmit Framer Interface in TFP Mode for T1.....................................................................22

Figure 7-7. Transmit Framer Interface in Gapped-Clock Mode for T1.....................................................22

Figure 7-8. Transmit Framer Interface in TFP Mode for E1.....................................................................22

Figure 7-9. Transmit Framer Interface in Gapped-Clock Mode for E1.....................................................23

Figure 8-1. Receive Framer Interface in RFP Mode for T1 .....................................................................24

Figure 8-2. Receive Framer Interface in Gapped-Clock Mode for T1......................................................24

Figure 8-3. Receive Framer Interface in RFP Mode for E1 .....................................................................25

Figure 8-4. Receive Framer Interface in Gapped-Clock Mode for E1......................................................25

Figure 8-5. Cell Delineation State Diagram.............................................................................................26

Figure 8-6. Header Correction State Machine.........................................................................................26

Figure 8-7. Polling Phase and Selection at Receive Interface.................................................................27

Figure 8-8. End and Restart of Cell Transmission at Receive Interface ..................................................28

Figure 8-9. Example Direct Status Indication, Receive Direction ............................................................29

Figure 10-1. Accessing Tx PMON Counter.............................................................................................34

Figure 10-2. Accessing Rx PMON Counters...........................................................................................40

Figure 11-1. JTAG Functional Block Diagram.........................................................................................45

Figure 11-2. TAP Controller State Diagram ............................................................................................47

Figure 13-1. Intel Bus Read Timing (BTS = 0/MUX = 1) .........................................................................53

Figure 13-2. Intel Bus Write Timing (BTS = 0/MUX = 1) .........................................................................54

Figure 13-3. Motorola Bus Timing (BTS = 1/MUX = 1)............................................................................54

Figure 13-4. Intel Bus Read Timing (BTS = 0/MUX = 0) .........................................................................55

Figure 13-5. Intel Bus Write Timing (BTS = 0/MUX = 0) .........................................................................56

Figure 13-6. Motorola Bus Read Timing (BTS = 1/MUX = 0) ..................................................................56

Figure 13-7. Motorola Bus Write Timing (BTS = 1/MUX = 0) ..................................................................56

Figure 13-8. Setup/Hold Time Definition .................................................................................................58

Figure 13-9. Delay Time Definition .........................................................................................................58

Figure 13-10. JTAG Interface Timing Diagram .......................................................................................58

Figure 15-1. User-Network Interface Application ....................................................................................60

Figure 15-2. DS26102 Interfacing with Dallas Framer in Framing-Pulse Mode .......................................61

DS26102 16-Port TDM-to-ATM PHY

4 of 64

LIST OF TABLES

Table 5-A. Pin Description List ................................................................................................................ 8

Table 9-A. Register Map.........................................................................................................................30

Table 11-A. Instruction Codes for IEEE 1149.1 Architecture...................................................................48

Table 11-B. ID Code Structure ...............................................................................................................48

Table 11-C. Device ID Codes .................................................................................................................48

Table 11-D. Boundary Scan Control Bits ................................................................................................49

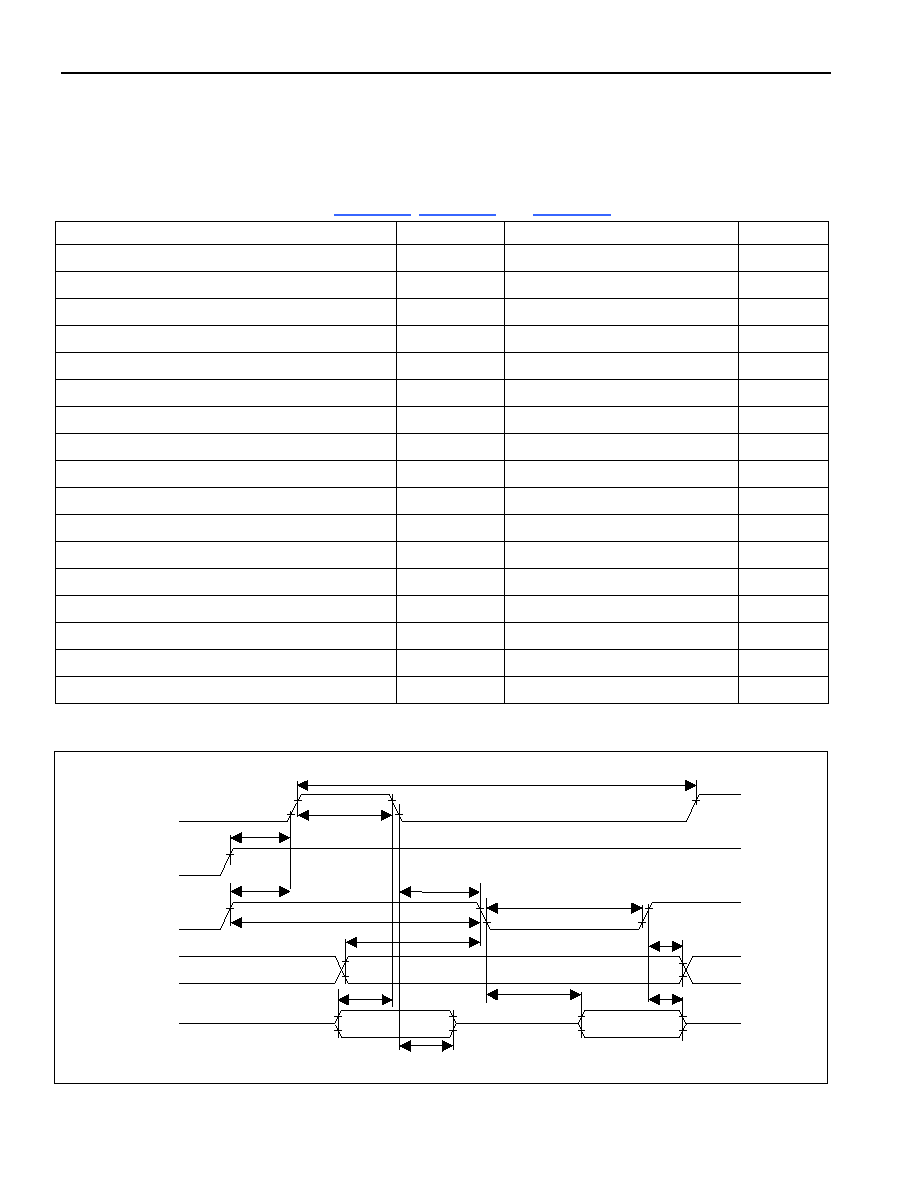

Table 13-A. AC Characteristics--Multiplexed Parallel Port (MUX = 1)....................................................53

Table 13-B. AC Characteristics--Nonmultiplexed Parallel Port (MUX = 1) .............................................55

Table 13-C. Framer Interface AC Characteristics ...................................................................................57

Table 13-D. UTOPIA Transmit AC Characteristics .................................................................................57

Table 13-E. UTOPIA Receive AC Characteristics...................................................................................57

Table 13-F. JTAG Interface Timing.........................................................................................................58

Table 13-G. System Clock AC Characteristics........................................................................................59

Table 14-A. Thermal Properties, Natural Convection..............................................................................59

Table 14-B. Theta-JA (

q

JA

) vs. Airflow.....................................................................................................59

Table 15-A. Suggested Clock Edge Configurations ................................................................................61

Table 15-B. Fractional T1/E1 Register Settings ......................................................................................61

DS26102 16-Port TDM-to-ATM PHY

5 of 64

1. FEATURES

§

Supports 16 T1/E1 Ports

§

Supports Fractional T1/E1 and Arbitrary Bit

Rates in Multiples of 64kbps (DS0/TS) Up to

2.048Mbps

§

Supports Clear E1

§

Compliant to the ATM Forum Specifications for

ATM Over T1 and E1

§

Standard UTOPIA II Interface to the ATM Layer

§

Configurable UTOPIA Address Range

§

Generic 8-Bit Asynchronous Microprocessor

Interface for Configuration and Status Indications

Including Interrupt Capability

§

Physical Layer Interface Can Accept T1/E1 TDM

Stream in the Form of Either (1) Clock, Data, and

Frame-Overhead Indication or (2) Gapped Clock

(Gapped at Overhead Positions in the Frame)

and Data

§

Selectable Active Clock Edge for Interface with

the T1/E1 Framer

§

Supports Diagnostic Loopback

§

Optional Payload Scrambling in Transmit

Direction and Descrambling in Receive Direction

as per the ITU I.432 for the Cell-Based Physical

Layer

§

Optional HEC Insertion in Transmit Direction with

Programmable COSET Polynomial Addition

§

Option of Using Either Idle or Unassigned Cells

for Cell-Rate Decoupling in Transmit Direction

§

1-Byte Programmable Pattern for Payload of

Cells Used for Cell-Rate Decoupling

§

Tx FIFO Depth Configurable to Either 2, 3, or 4

Cells

§

Transmit FIFO Depth Indication for 2-Cell Space

Through External Pins

§

Optional Single-Bit HEC Error Insertion

§

HEC-Based Cell Delineation as per I.432

§

Optional Single-Bit HEC Error Correction in the

Receive Direction

§

Optional Filtering of HEC-Errored Cells Received

§

Optional Receive Idle/Unassigned Cell Filtering

§

Optional User-Defined Cell Filtering Based on

Programmable Header Bits

§

Programmable Loss-Of-Cell Delineation (LCD)

Integration and Interrupt

§

Interrupt for FIFO Overrun in Receive Direction

§

Saturating Counts for (1) Number of Error-Free

Assigned Cells Received and Transmitted and

(2) Number of Correctable and Uncorrectable

HEC-Errored Cells Received

§

Selectable Internally Generated Clock (System

Clock Divided by 8) in Diagnostic Loopback

Mode

§

Integrated PLL Generates High-Frequency

Clocks

§

IEEE 1149.1 JTAG Boundary Scan Support

2. APPLICABLE STANDARDS

[1] ATM Forum "DS1 Physical Layer Specification," af-phy-0016.000, September 1994

[2] ATM Forum "E1 Physical Layer Specification," af-phy-0064.000, September 1996

[3] ATM Forum "UTOPIA Level 2 Specification," Version 1.0, af-phy-0039.000, June 1995

[4] B-ISDN User-Network Interface--Physical Layer Specification--ITU-T Recommendation I.432--3/93

DS26102 16-Port TDM-to-ATM PHY

6 of 64

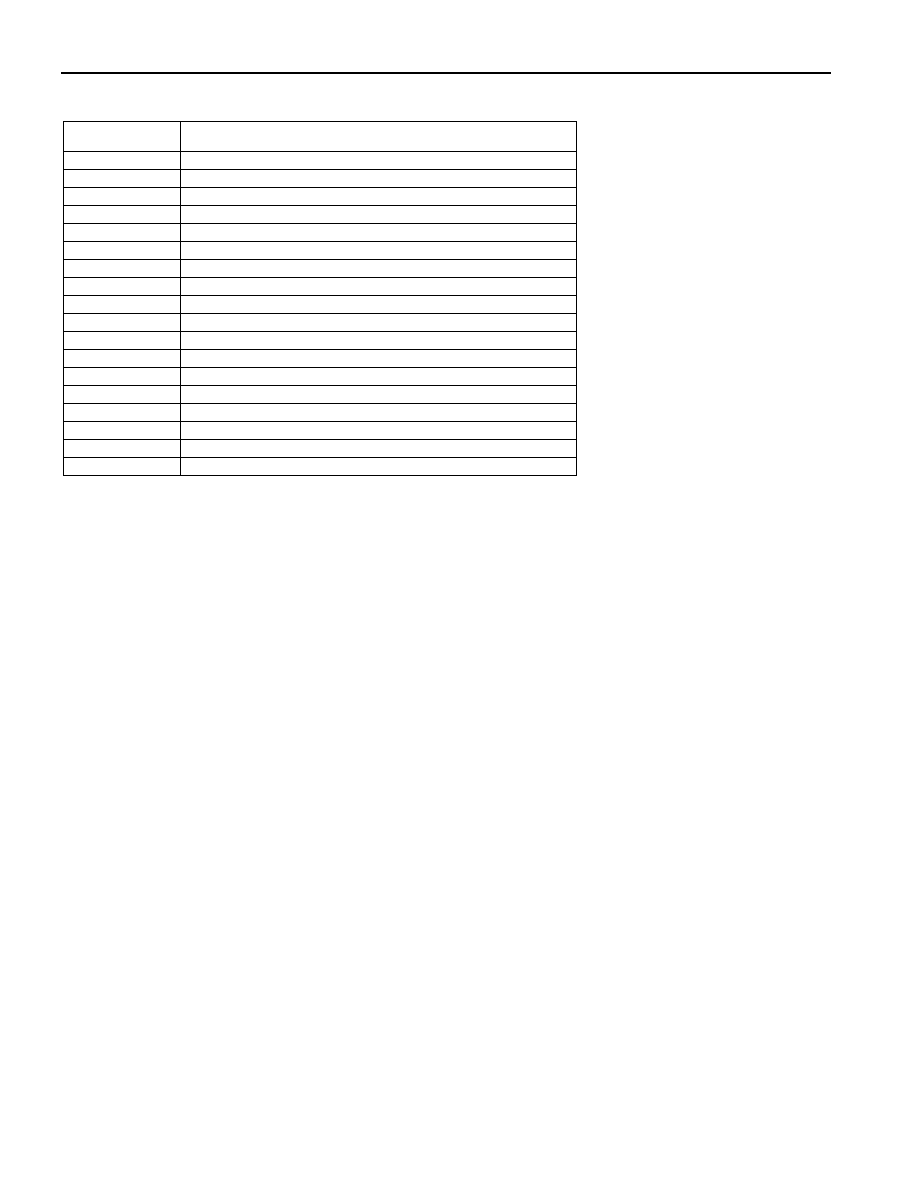

3. ACRONYMS AND DEFINITIONS

ACRONYM DESCRIPTION

ATM

Asynchronous Transfer Mode

CRC Cyclic

Redundancy

Check

DPRAM

Dual Port Random Access Memory

FIFO

First In, First Out (Memory)

HEC

Header Error Check

IMA

Inverse Multiplexing for ATM

µP Microprocessor

µs Microsecond

LCD Loss-of-Cell

Delineation

ms Millisecond

OAM

Operations Administration and Maintenance

OCD Out-of-Loss

Delineation

PMON Performance

Monitoring

Rx Receive

DS0

Each 64kbps Channel in DS1 Frame

TS

Each 64kbps Channel in E1 Frame (Time Slot)

Tx Transmit

UTOPIA

Universal Test and Operations PHY Interface for ATM

DS26102 16-Port TDM-to-ATM PHY

7 of 64

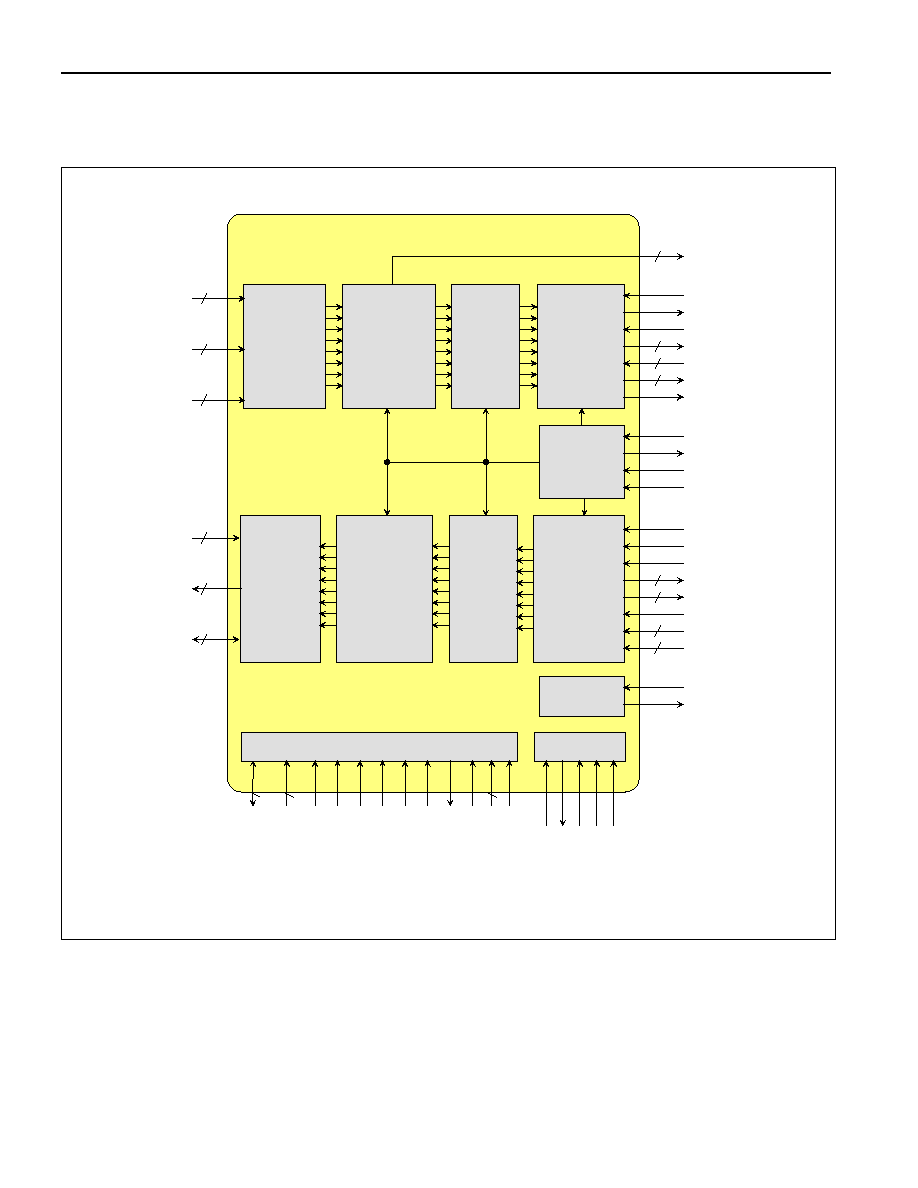

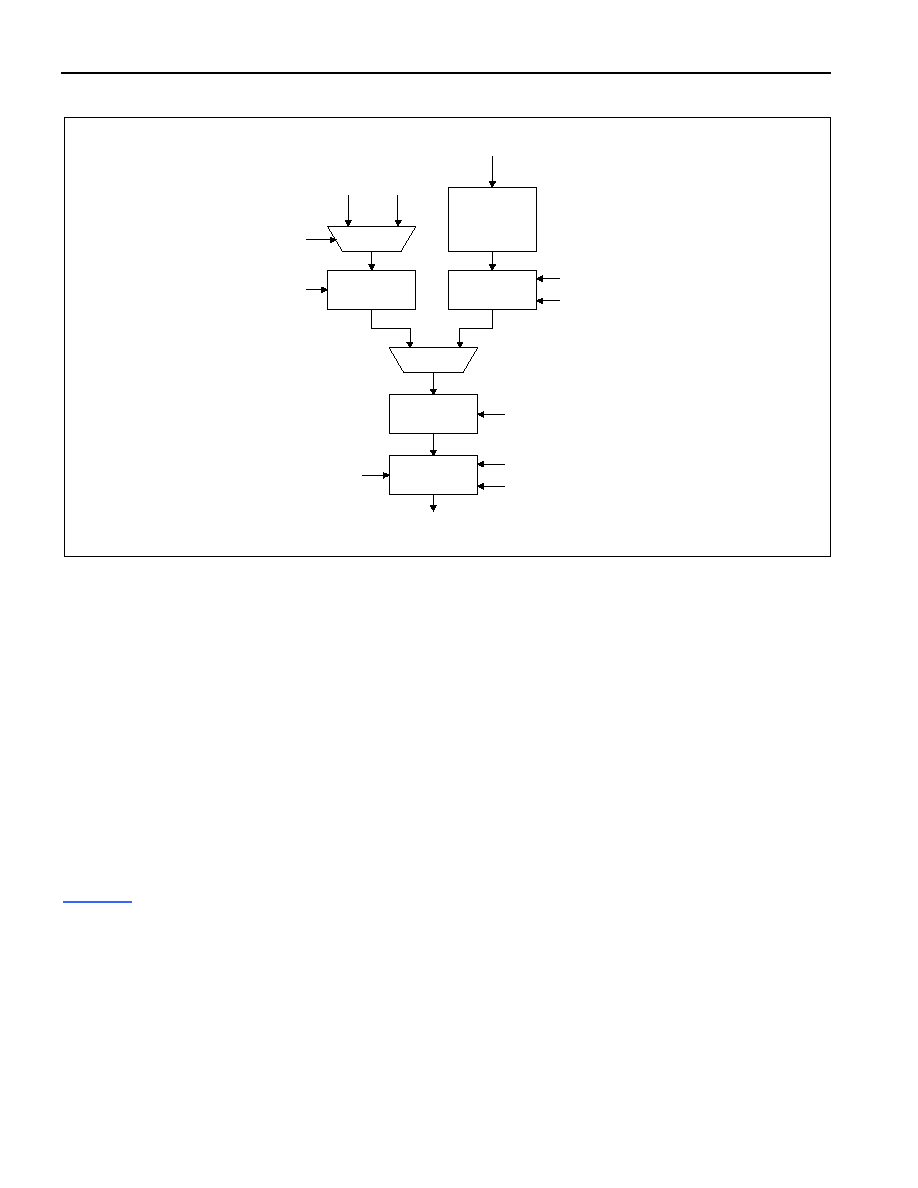

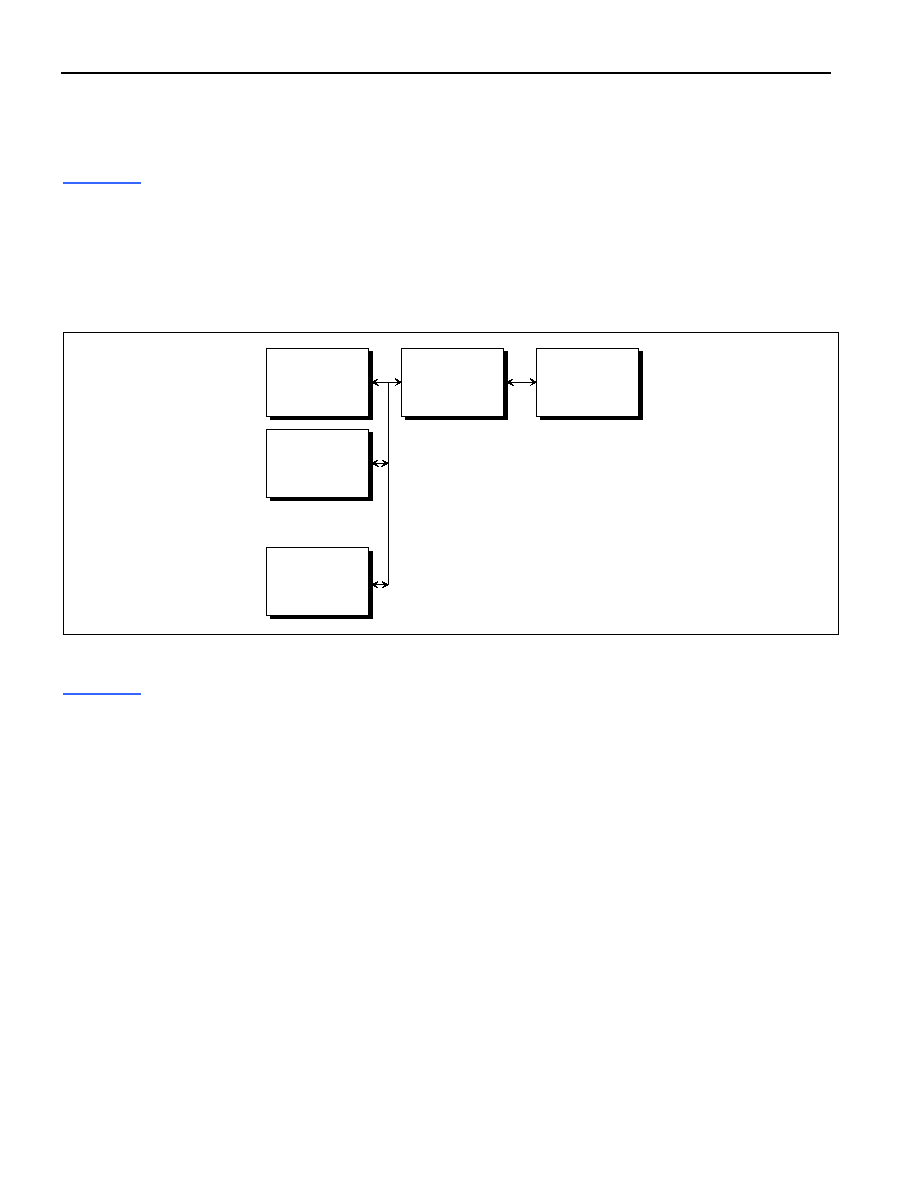

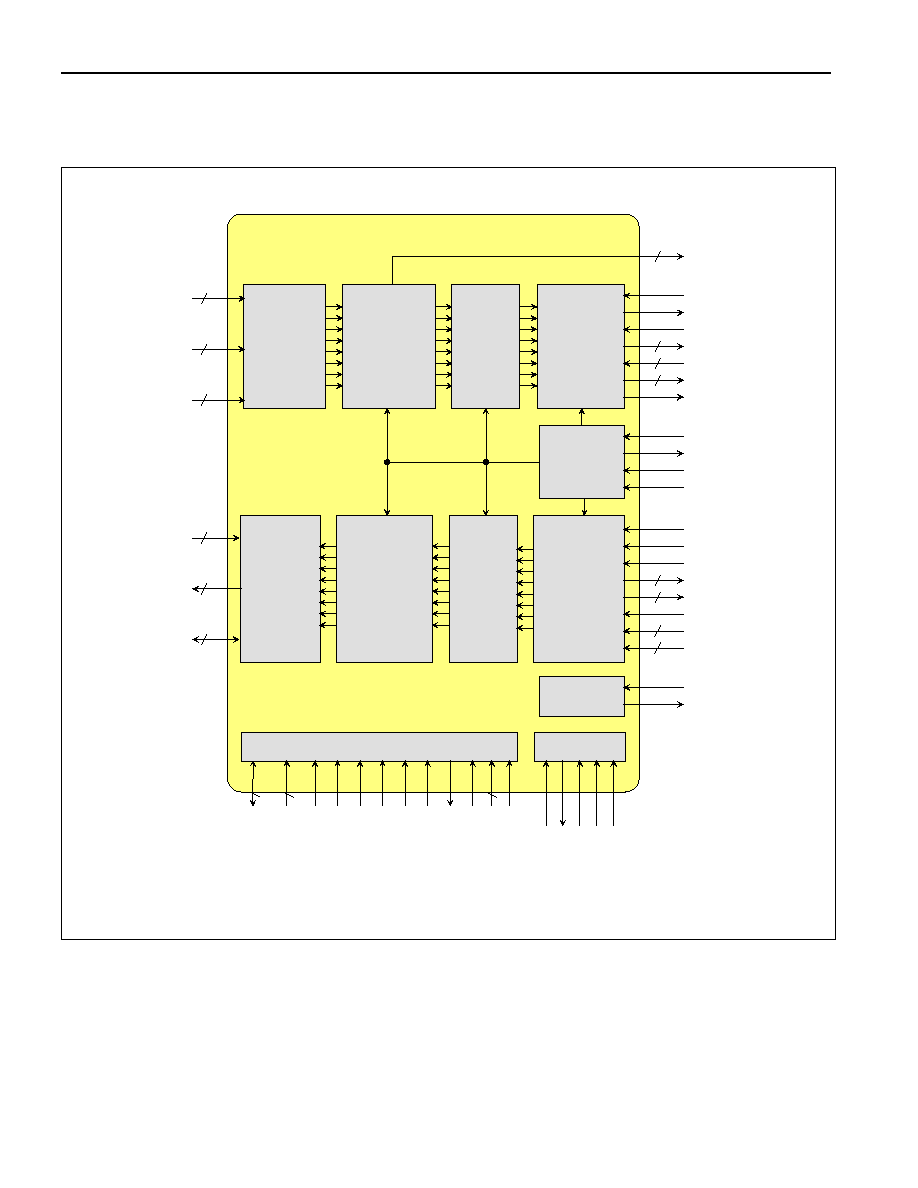

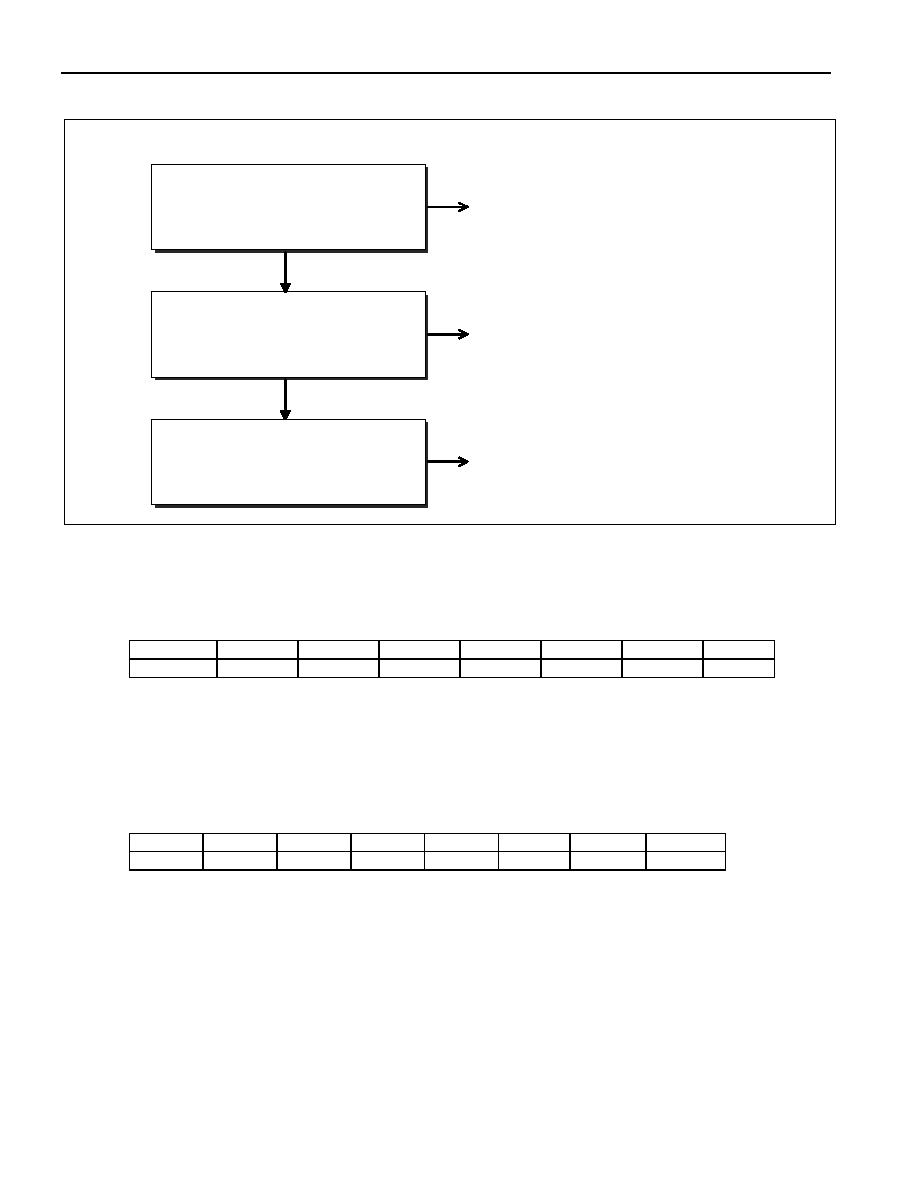

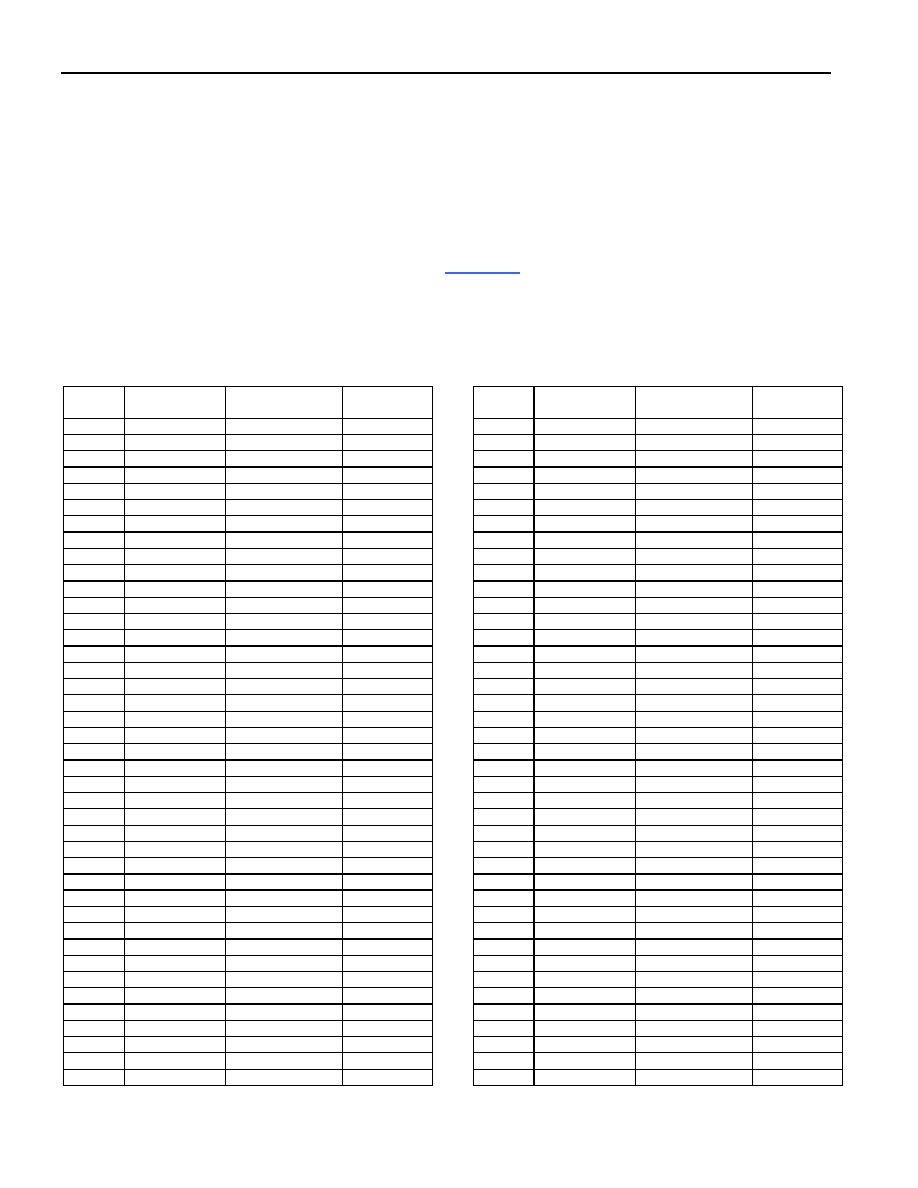

4. BLOCK DIAGRAM

Figure 4-1. Block Diagram

TRANSMIT

TDM

INTERFACE

CONTROL

SCRAMBLING

AND RATE

DECOUPLING

CELL

STORAGE

FIFO

TRANSMIT

UTOPIA BUS

INTERFACE

RECEIVE

TDM

INTERFACE

CONTROL

SCRAMBLING

AND RATE

DECOUPLING

CELL

STORAGE

FIFO

RECEIVE

UTOPIA BUS

INTERFACE

RCLK015

RDATA015

RFP015

TCLK015

TDATA015

TFP015

16

16

16

16

16

16

DS26102

CONTROLLER INTERFACE

JTAG

A

0A

6

A

D0A

D7

JT

C

L

K

JT

D

O

JT

D

I

JT

M

S

JT

R

S

T

8

7

A

7

/

AL

E (

A

S)

C

S

R

D

(

DS

)

W

R

(

R/

W

)

BTS

MU

X

I

NT

R

ESET

RLCD0-15

16

UR-SOC

UR-CLK

UR-ADDR04

UR-DATA07

UR-CLAV03

5

8

UR-PAR

4

UR-ENB

UT-SOC

UT-CLK

UT-ADDR04

UT-DATA07

UT-CLAV0 3

5

8

UT-2CLAV0 3

UT_PAR

4

4

UT-ENB

REFCLKIN

GCLKOUT

GCLKIN

TEST

CLOCK

PLL

EX

STA

T

0

-

7

8

8KHZIN

1SECOUT

1-SECOND

TIMER

BL

S0

DS26102 16-Port TDM-to-ATM PHY

8 of 64

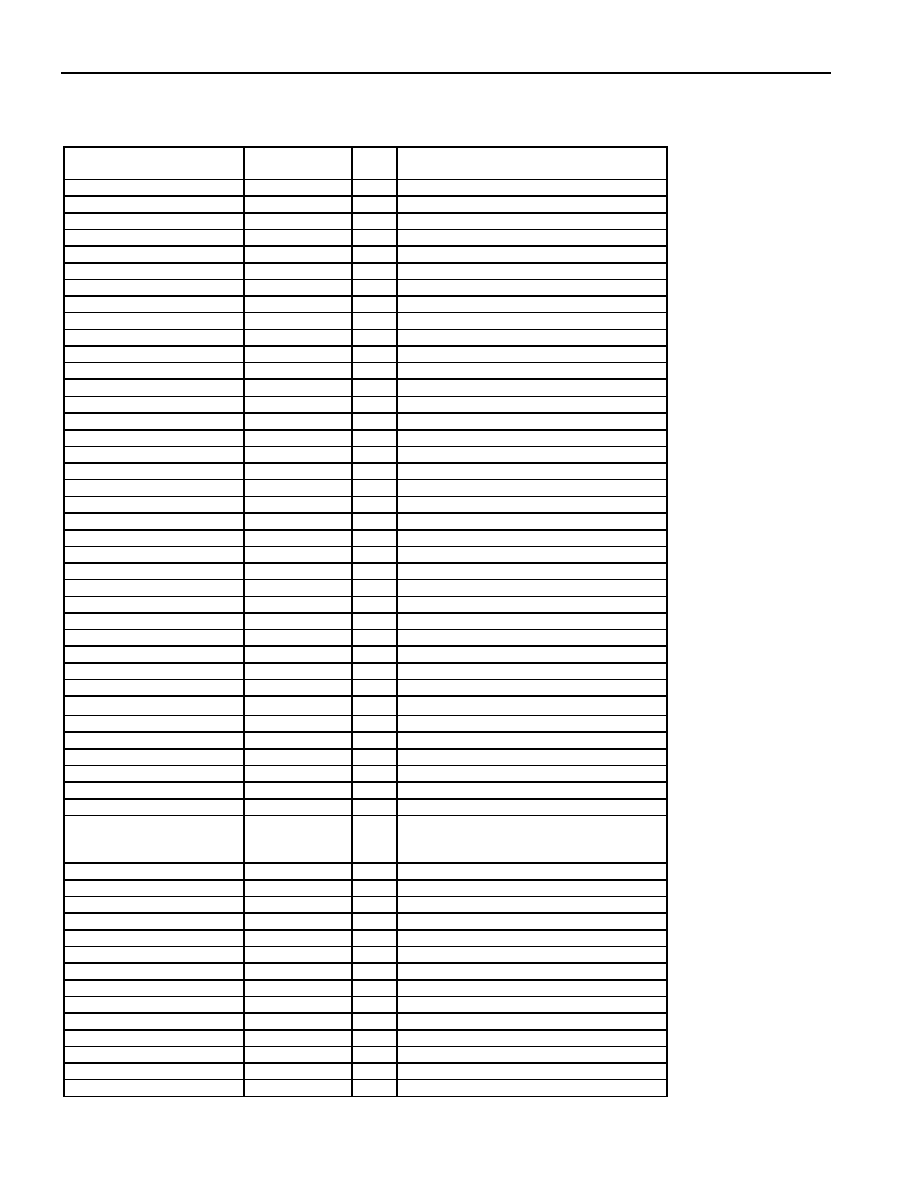

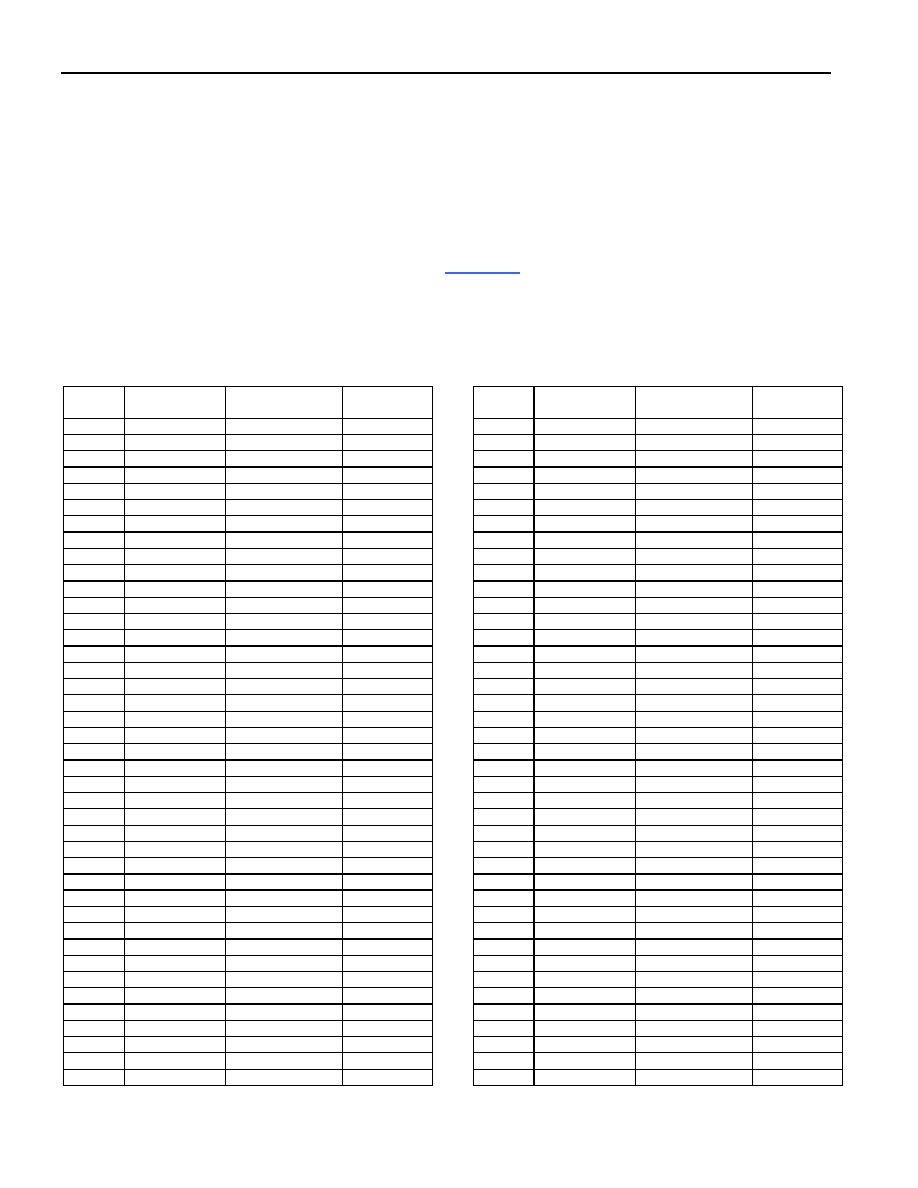

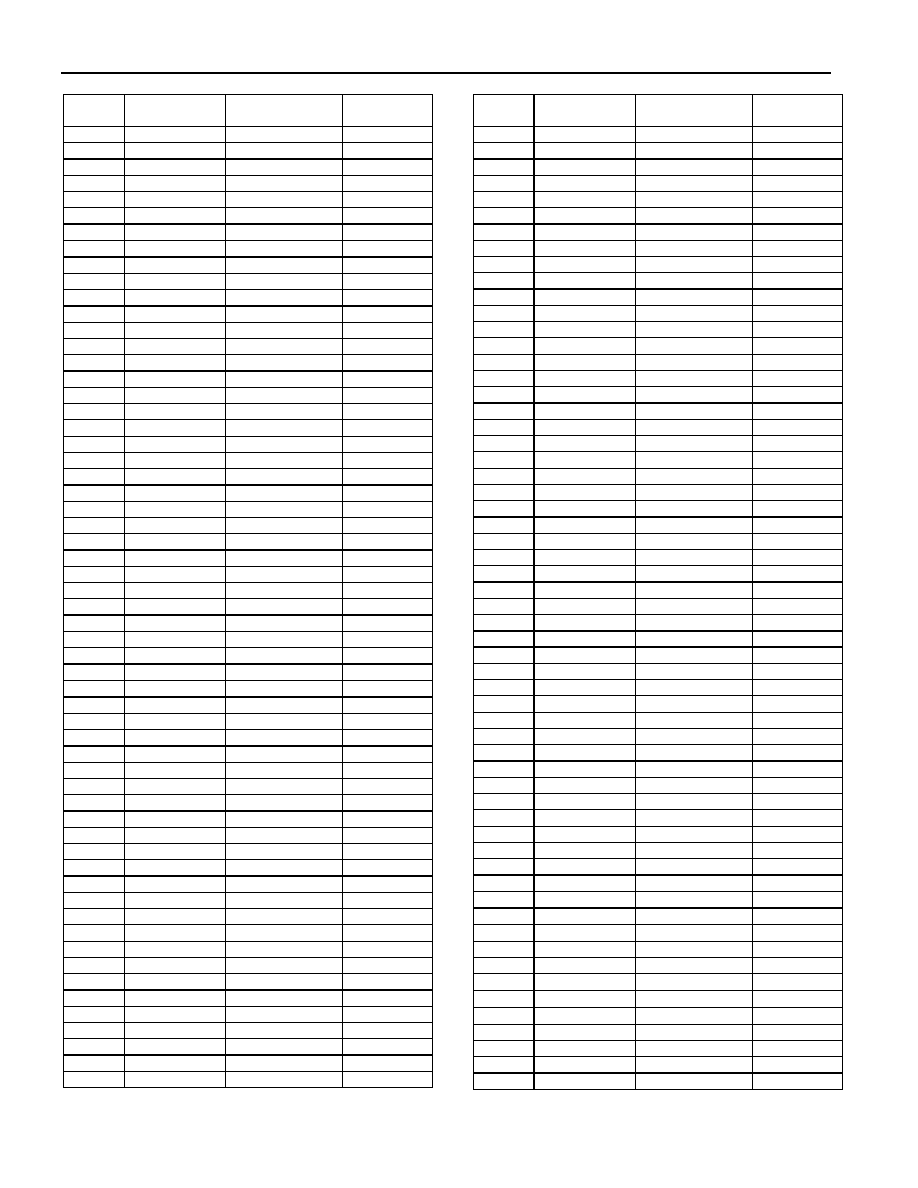

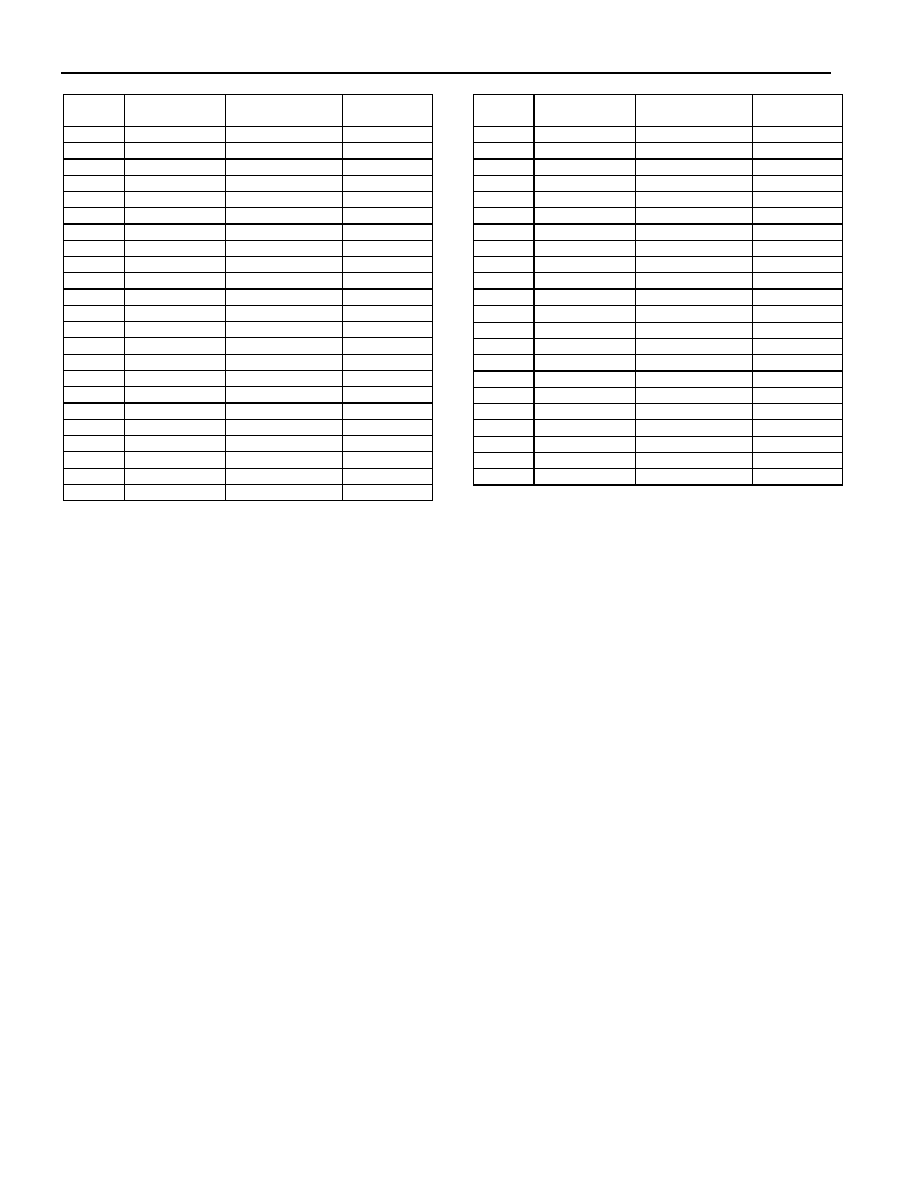

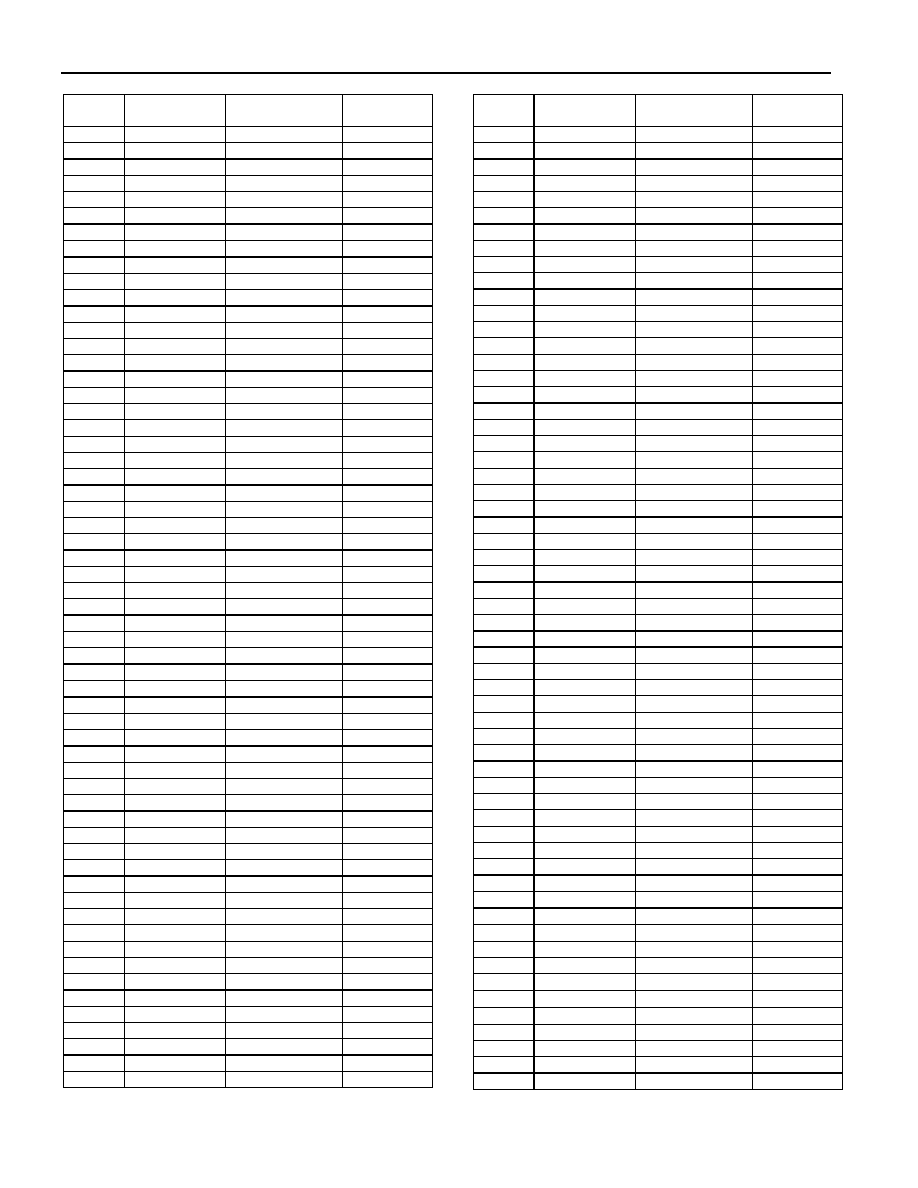

5. PIN DESCRIPTION

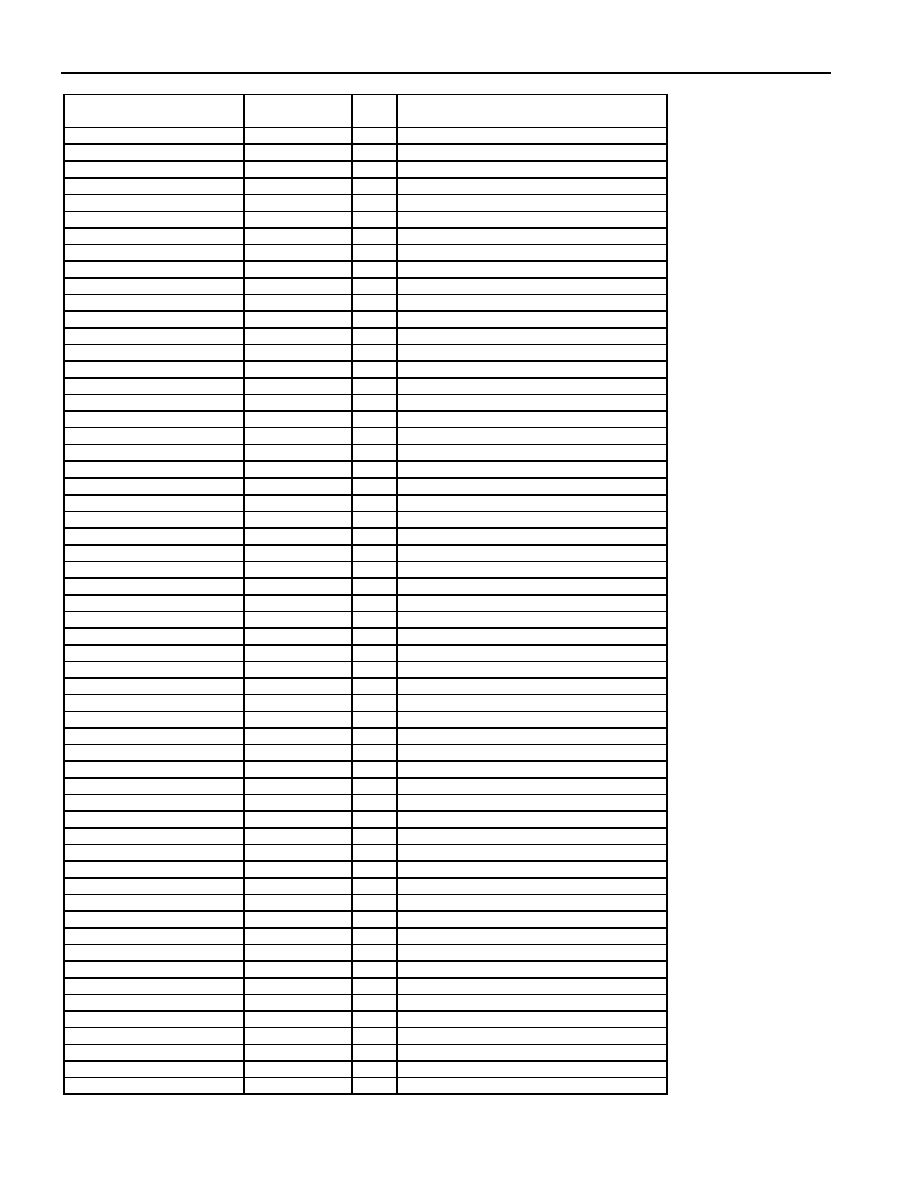

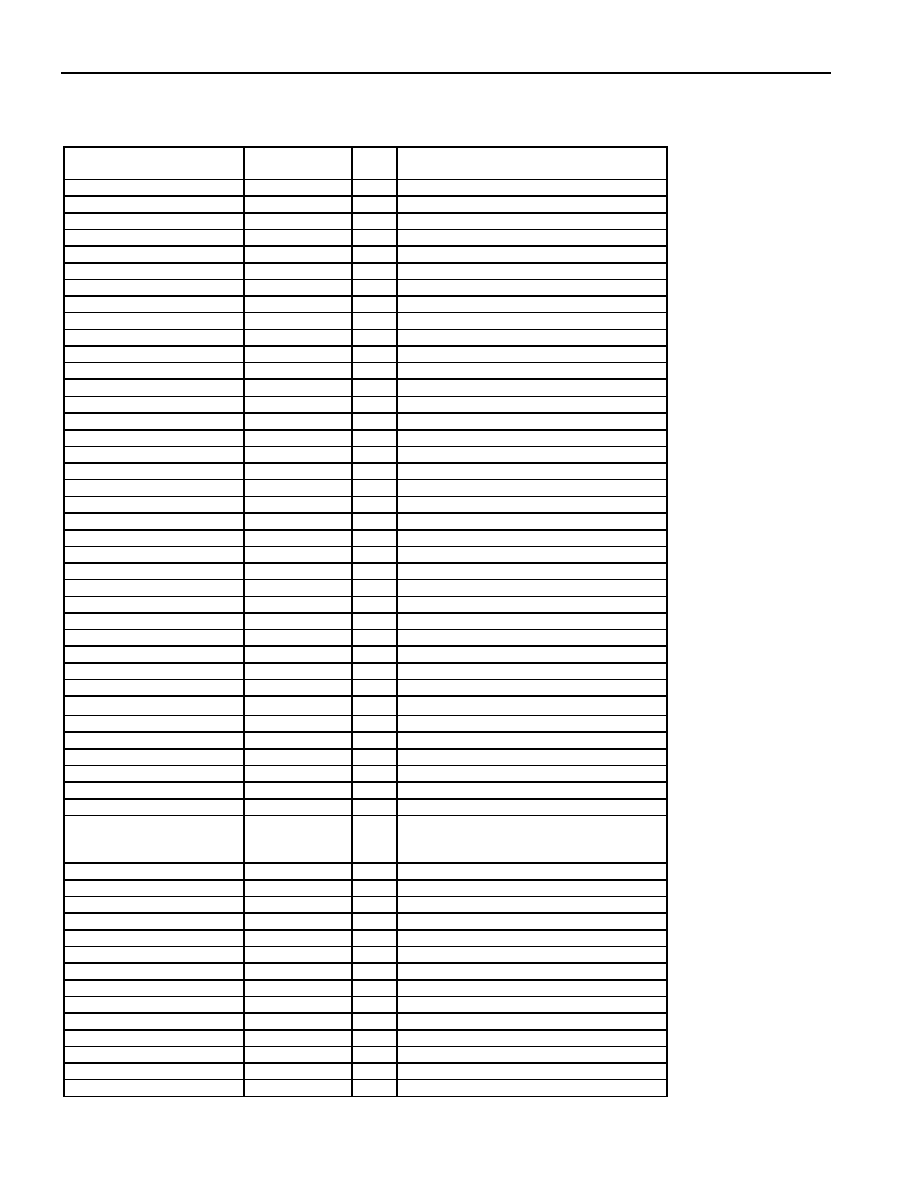

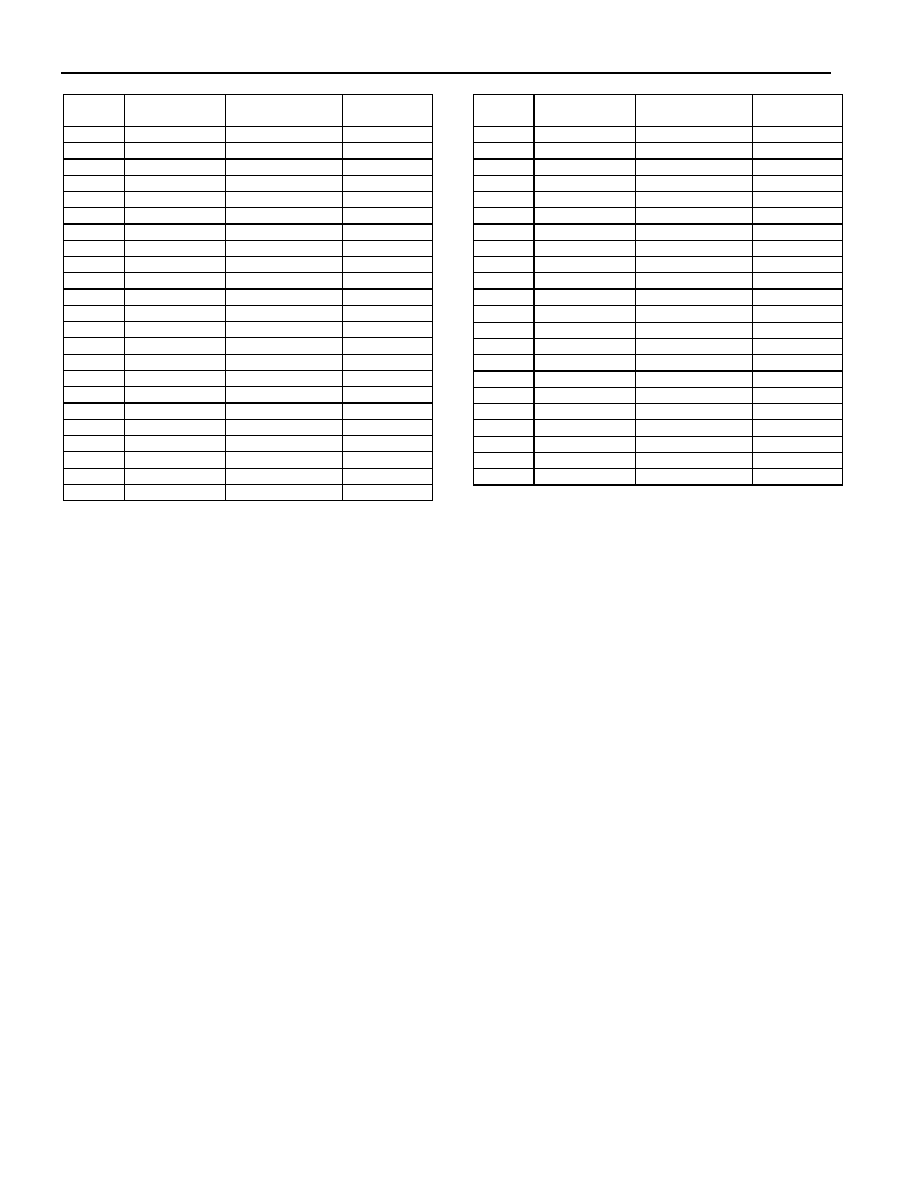

Table 5-A. Pin Description List

PIN NAME

I/O FUNCTION

J13 1SECOUT

O

One-Second

Reference

J12

8KHZIN

I

8kHz Clock for One-Second Timer

F16

A0

I

µP Address Bus Bit 0

F13

A1

I

µP Address Bus Bit 1

F12

A2

I

µP Address Bus Bit 2

G15

A3

I

µP Address Bus Bit 3

G14

A4

I

µP Address Bus Bit 4

G16

A5

I

µP Address Bus Bit 5

G13

A6

I

µP Address Bus Bit 6

G12

A7/ALE (AS)

I

µP Address Bus Bit 7 (Note 1)

C14 BLS0

I

Block

Select

0

C16

BTS

I

Bus Type Select (0 = Intel)

D14

CS

I

Chip Select (Active Low)

D16

D0/AD0

I/O

µP Data 0/Address/Data 0

E15

D1/AD1

I/O

µP Data 1/Address/Data 1

E14

D2/AD2

I/O

µP Data 2/Address/Data 2

E16

D3/AD3

I/O

µP Data 3/Address/Data 3

E13

D4/AD4

I/O

µP Data 4/Address/Data 4

E12

D5/AD5

I/O

µP Data 5/Address/Data 5

F15

D6/AD6

I/O

µP Data 6/Address/Data 6

F14

D7/AD7

I/O

µP Data 7/Address/Data 7

J16

EXSTAT0

I

External Status Input

J14

EXSTAT1

I

External Status Input

J15

EXSTAT2

I

External Status Input

H12

EXSTAT3

I

External Status Input

H13

EXSTAT4

I

External Status Input

H16

EXSTAT5

I

External Status Input

H14

EXSTAT6

I

External Status Input

H15

EXSTAT7

I

External Status Input

K13

GCLKIN

I

High-Frequency Clock Input

K12

GCLKOUT

O

High-Frequency Clock Output

B16

INT

O

Interrupt Signal (Active Low) (Note 2)

P16

JTCLK

I

IEEE 1149.1 Test Clock

N16

JTDI

I

IEEE 1149.1 Test Data Input

N15

JTDO

O

IEEE 1149.1 Test Data Output

P15

JTMS

I

IEEE 1149.1 Test Mode Select

N14

JTRST

I

IEEE 1149.1 Reset

C15

MUX

I

Bus Mode Select (0 = Nonmuxed)

A1, A15, A16, B1, B2, B15,

C1, C2, L16, P3, R1, R2,

R15, R16, T1, T2, T16

N.C. --

No

Connect

A14

RCLK0

I

Rx Line Clock for Port 0

B13

RCLK1

I

Rx Line Clock for Port 1

N8

RCLK11

I

Rx Line Clock for Port 11

P7

RCLK10

I

Rx Line Clock for Port 10

R8

RCLK12

I

Rx Line Clock for Port 12

T9

RCLK13

I

Rx Line Clock for Port 13

M10

RCLK14

I

Rx Line Clock for Port 14

P10

RCLK15

I

Rx Line Clock for Port 15

C12

RCLK2

I

Rx Line Clock for Port 2

D11

RCLK3

I

Rx Line Clock for Port 3

B11

RCLK4

I

Rx Line Clock for Port 4

A10

RCLK5

I

Rx Line Clock for Port 5

E9

RCLK6

I

Rx Line Clock for Port 6

C9

RCLK7

I

Rx Line Clock for Port 7

DS26102 16-Port TDM-to-ATM PHY

9 of 64

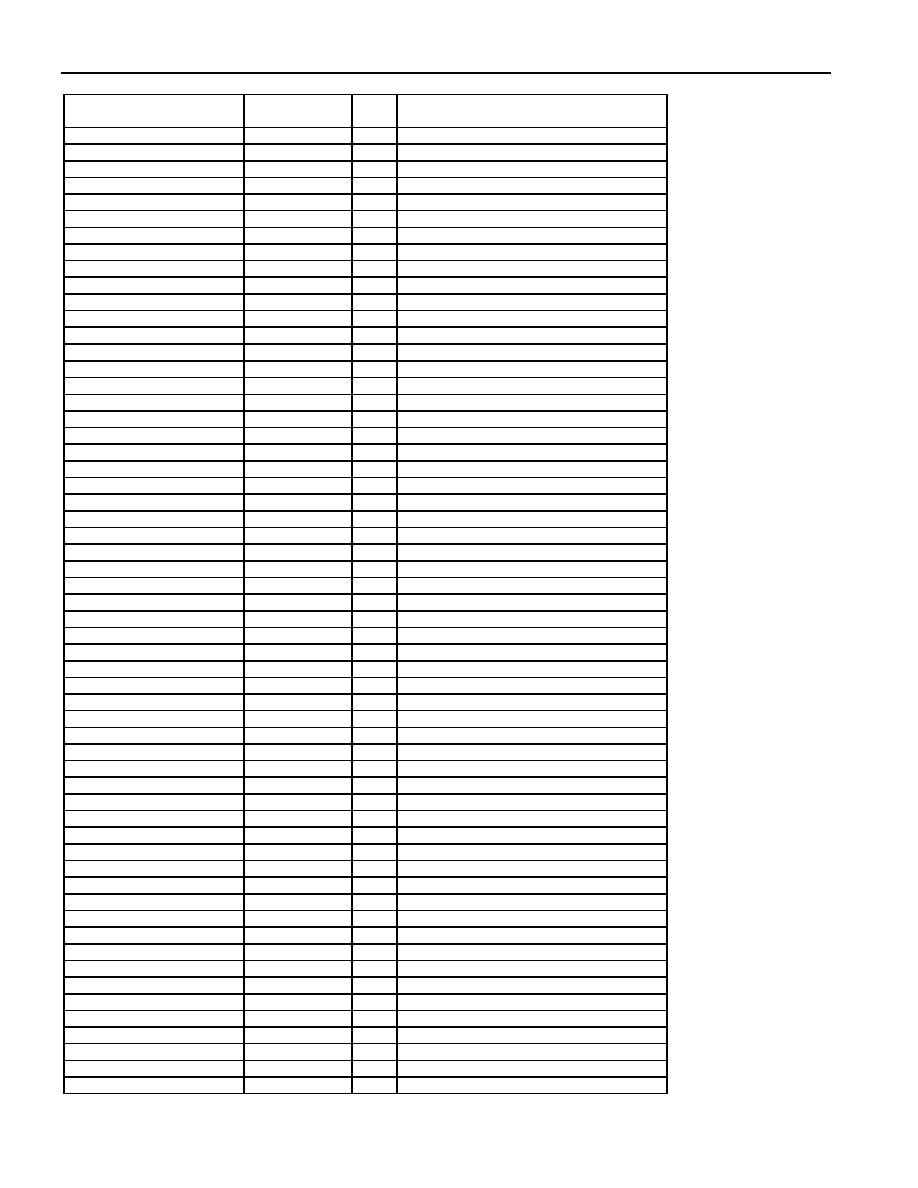

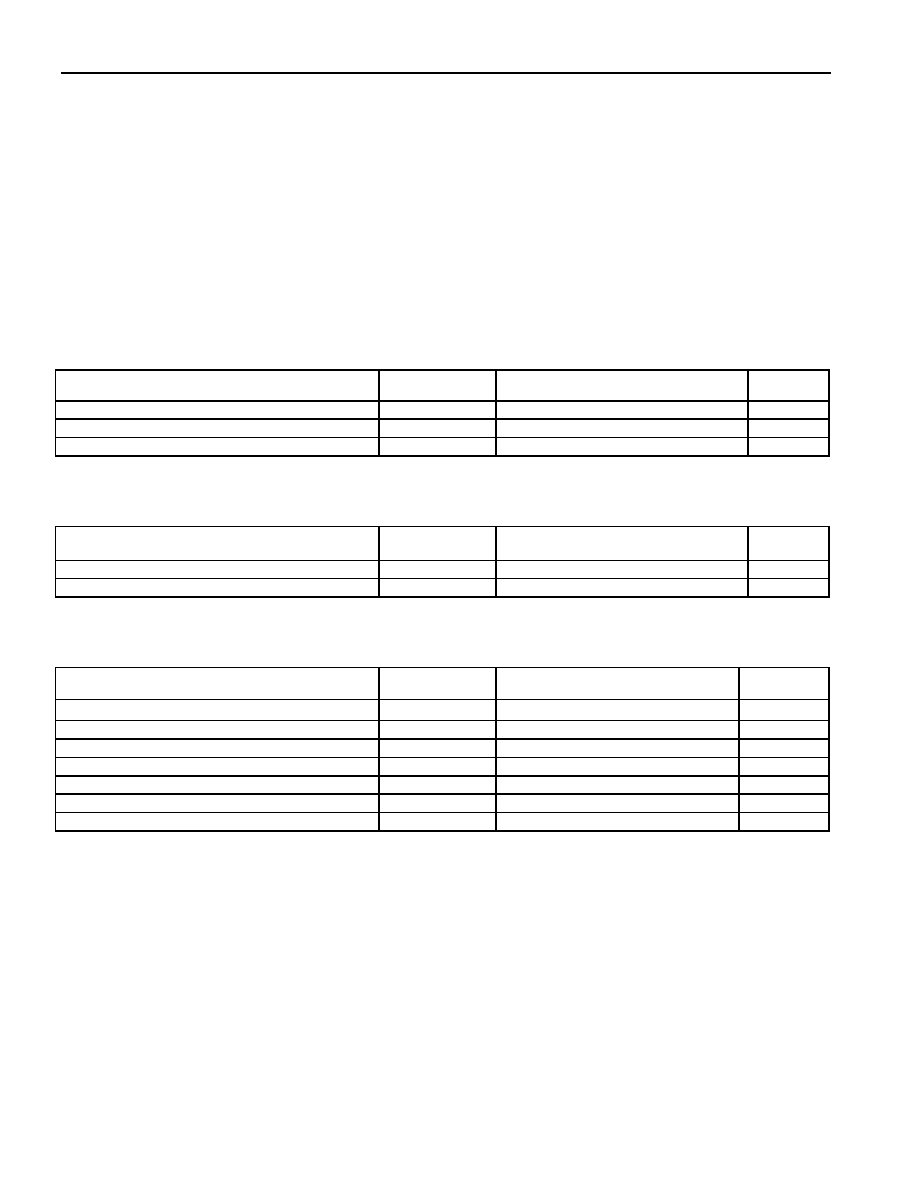

PIN NAME

I/O FUNCTION

T6

RCLK8

I

Rx Line Clock for Port 8

M7

RCLK9

I

Rx Line Clock for Port 9

D15

RD (DS)

I

Read Enable (Active Low)

B14

RDATA0

I

Rx Line Serial Data for Port 0

A13

RDATA1

I

Rx Line Serial Data for Port 1

T7

RDATA10

I

Rx Line Serial Data for Port 10

M8

RDATA11

I

Rx Line Serial Data for Port 11

P8

RDATA12

I

Rx Line Serial Data for Port 12

N9

RDATA13

I

Rx Line Serial Data for Port 13

R9

RDATA14

I

Rx Line Serial Data for Port 14

T10

RDATA15

I

Rx Line Serial Data for Port 15

A12

RDATA2

I

Rx Line Serial Data for Port 2

E11

RDATA3

I

Rx Line Serial Data for Port 3

C11

RDATA4

I

Rx Line Serial Data for Port 4

D10

RDATA5

I

Rx Line Serial Data for Port 5

B10

RDATA6

I

Rx Line Serial Data for Port 6

A9

RDATA7

I

Rx Line Serial Data for Port 7

N6

RDATA8

I

Rx Line Serial Data for Port 8

R6

RDATA9

I

Rx Line Serial Data for Port 9

L15

REFCLKIN

I

1.544MHz/2.048MHz Reference Clock

L14

RESET

I

Device Reset (Active Low)

C13

RFP0

I

Rx Frame Pulse for Port 0

D12

RFP1

I

Rx Frame Pulse for Port 1

R7

RFP10

I

Rx Frame Pulse for Port 10

T8

RFP11

I

Rx Frame Pulse for Port 11

M9

RFP12

I

Rx Frame Pulse for Port 12

P9

RFP13

I

Rx Frame Pulse for Port 13

N10

RFP14

I

Rx Frame Pulse for Port 14

R10

RFP15

I

Rx Frame Pulse for Port 15

B12

RFP2

I

Rx Frame Pulse for Port 2

A11

RFP3

I

Rx Frame Pulse for Port 3

E10

RFP4

I

Rx Frame Pulse for Port 4

C10

RFP5

I

Rx Frame Pulse for Port 5

D9

RFP6

I

Rx Frame Pulse for Port 6

B9

RFP7

I

Rx Frame Pulse for Port 7

P6

RFP8

I

Rx Frame Pulse for Port 8

N7

RFP9

I

Rx Frame Pulse for Port 9

N1

RLCD0

O

Rx Loss-of-Cell Delineation Port 0

N2

RLCD1

O

Rx Loss-of-Cell Delineation Port 1

R4

RLCD10

O

Rx Loss-of-Cell Delineation Port 10

N5

RLCD11

O

Rx Loss-of-Cell Delineation Port 11

T5

RLCD12

O

Rx Loss-of-Cell Delineation Port 12

P5

RLCD13

O

Rx Loss-of-Cell Delineation Port 13

R5

RLCD14

O

Rx Loss-of-Cell Delineation Port 14

M6

RLCD15

O

Rx Loss-of-Cell Delineation Port 15

N4

RLCD2

O

Rx Loss-of-Cell Delineation Port 2

N3

RLCD3

O

Rx Loss-of-Cell Delineation Port 3

P1

RLCD4

O

Rx Loss-of-Cell Delineation Port 4

P2

RLCD5

O

Rx Loss-of-Cell Delineation Port 5

R3

RLCD6

O

Rx Loss-of-Cell Delineation Port 6

T3

RLCD7

O

Rx Loss-of-Cell Delineation Port 7

P4

RLCD8

O

Rx Loss-of-Cell Delineation Port 8

T4

RLCD9

O

Rx Loss-of-Cell Delineation Port 9

J3

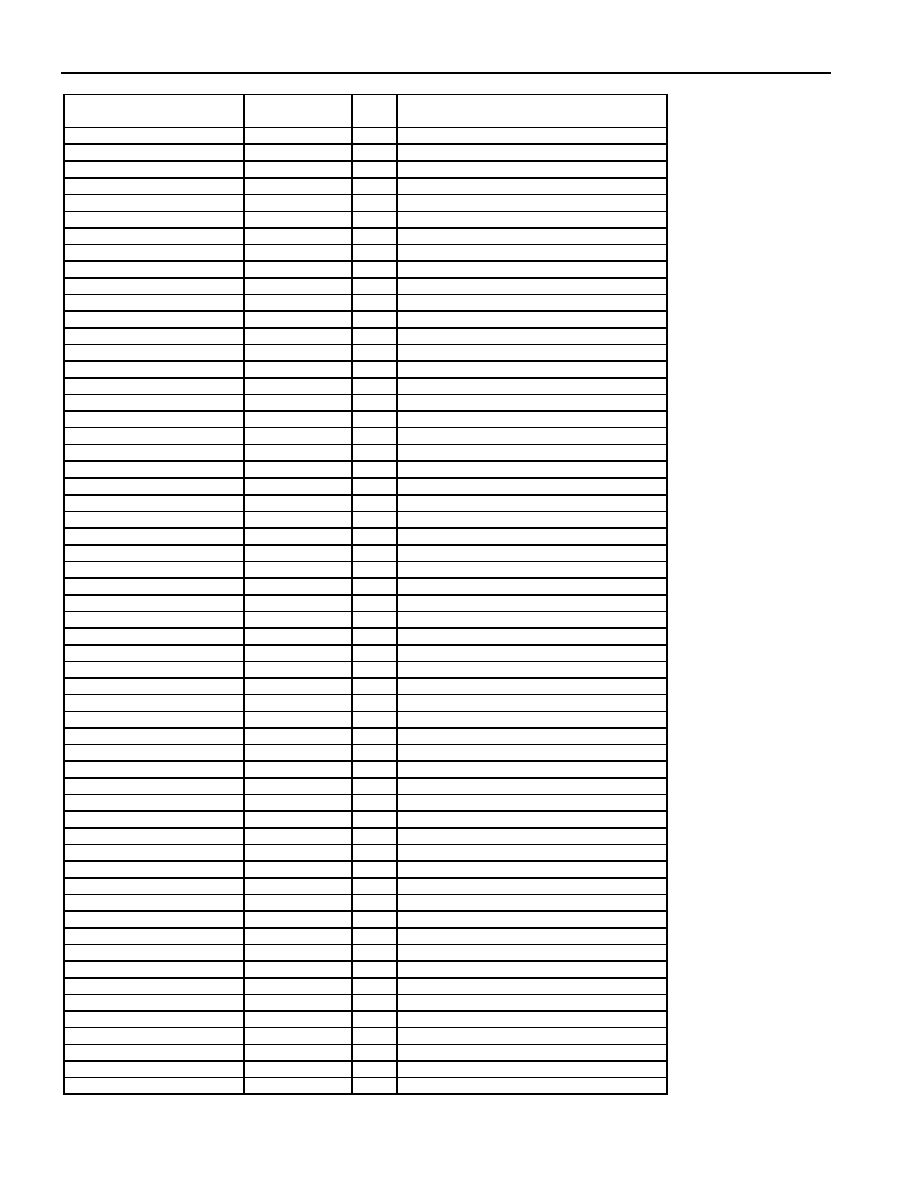

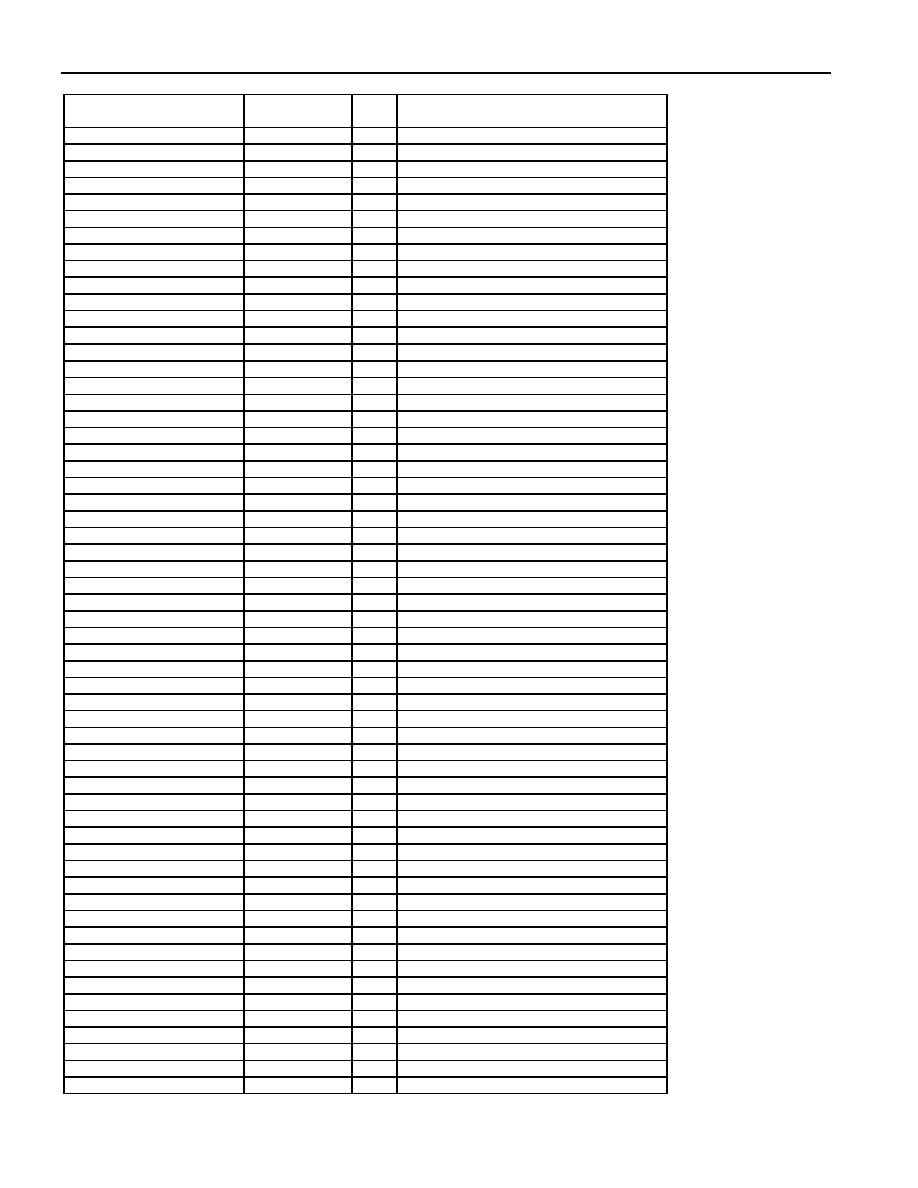

UR_ADDR0

I

Rx UTOPIA Address 0 (LSB)

J1

UR_ADDR1

I

Rx UTOPIA Address 1

J4

UR_ADDR2

I

Rx UTOPIA Address 2

J5

UR_ADDR3

I

Rx UTOPIA Address 3

H2

UR_ADDR4

I

Rx UTOPIA Address 4 (MSB)

DS26102 16-Port TDM-to-ATM PHY

10 of 64

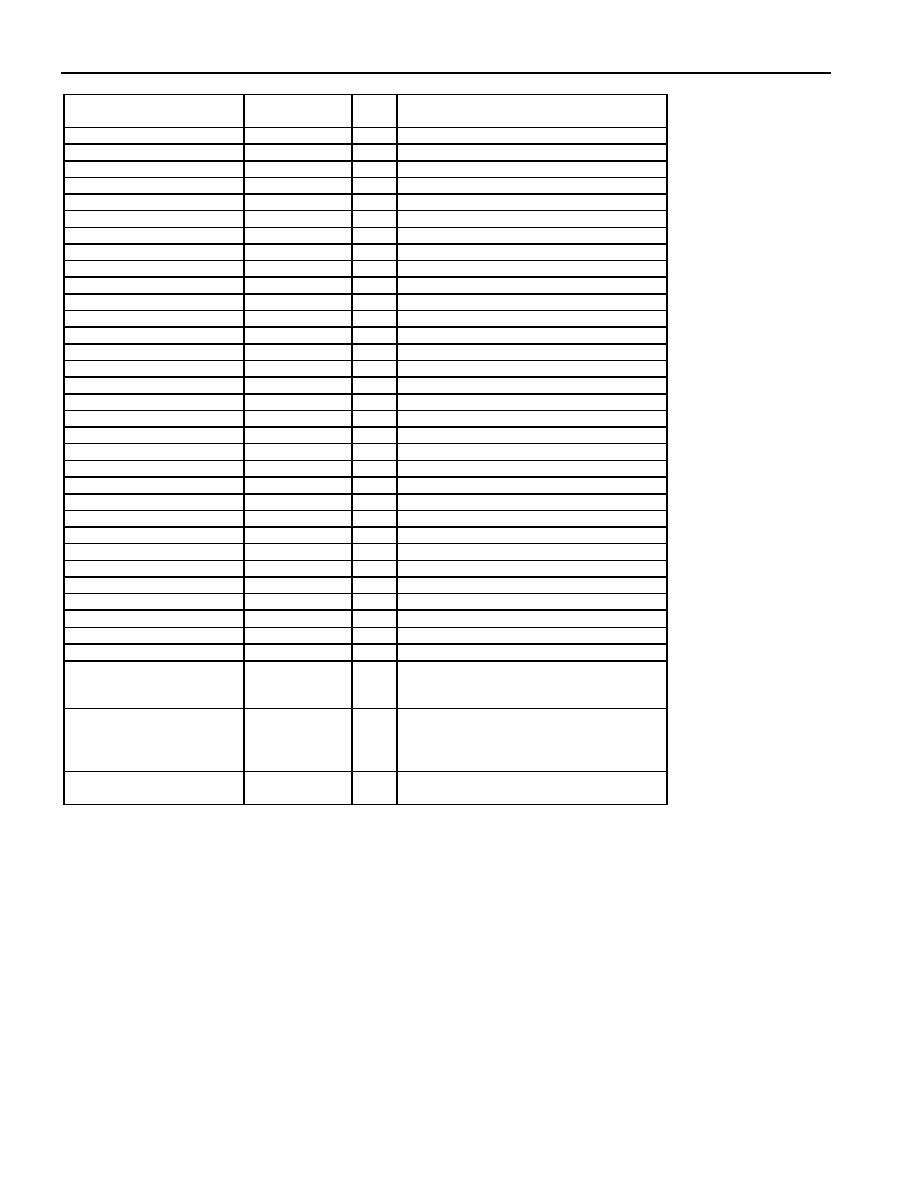

PIN NAME

I/O FUNCTION

M5

UR_CLAV0

O

Rx UTOPIA Cell Available 0

M4

UR_CLAV1

O

Rx UTOPIA Cell Available 1

M1

UR_CLAV2

O

Rx UTOPIA Cell Available 2

M3

UR_CLAV3

O

Rx UTOPIA Cell Available 3

K5

UR_CLK

I

Rx UTOPIA Clock

L3

UR_DATA0

O

Rx UTOPIA Data Bus 0 (LSB)

L1

UR_DATA1

O

Rx UTOPIA Data Bus 1

L4

UR_DATA2

O

Rx UTOPIA Data Bus 2

L5

UR_DATA3

O

Rx UTOPIA Data Bus 3

K2

UR_DATA4

O

Rx UTOPIA Data Bus 4

K3

UR_DATA5

O

Rx UTOPIA Data Bus 5

K1

UR_DATA6

O

Rx UTOPIA Data Bus 6

K4

UR_DATA7

O

Rx UTOPIA Data Bus 7 (MSB)

J2

UR_ENB

I

Rx UTOPIA Enable (Active Low)

M2

UR_PAR

O

Rx UTOPIA Parity Bit

L2

UR_SOC

O

Rx UTOPIA Start of Cell

D8

TCLK0

I

Tx Line Clock for Port 0

B8

TCLK1

I

Tx Line Clock for Port 1

T12

TCLK10

I

Tx Line Clock for Port 10

T13

TCLK11

I

Tx Line Clock for Port 11

P13

TCLK12

I

Tx Line Clock for Port 12

P14

TCLK13

I

Tx Line Clock for Port 13

M16

TCLK14

I

Tx Line Clock for Port 14

L12

TCLK15

I

Tx Line Clock for Port 15

A7

TCLK2

I

Tx Line Clock for Port 2

E6

TCLK3

I

Tx Line Clock for Port 3

C6

TCLK4

I

Tx Line Clock for Port 4

D5

TCLK5

I

Tx Line Clock for Port 5

B5

TCLK6

I

Tx Line Clock for Port 6

D4

TCLK7

I

Tx Line Clock for Port 7

N11

TCLK8

I

Tx Line Clock for Port 8

R11

TCLK9

I

Tx Line Clock for Port 9

E8

TDATA0

O

Tx Line Serial Data for Port 0

C8

TDATA1

O

Tx Line Serial Data for Port 1

N12

TDATA10

O

Tx Line Serial Data for Port 10

R12

TDATA11

O

Tx Line Serial Data for Port 11

N13

TDATA12

O

Tx Line Serial Data for Port 12

R14

TDATA13

O

Tx Line Serial Data for Port 13

M13

TDATA14

O

Tx Line Serial Data for Port 14

M15

TDATA15

O

Tx Line Serial Data for Port 15

D7

TDATA2

O

Tx Line Serial Data for Port 2

B7

TDATA3

O

Tx Line Serial Data for Port 3

A6

TDATA4

O

Tx Line Serial Data for Port 4

E5

TDATA5

O

Tx Line Serial Data for Port 5

C5

TDATA6

O

Tx Line Serial Data for Port 6

B4

TDATA7

O

Tx Line Serial Data for Port 7

M11

TDATA8

O

Tx Line Serial Data for Port 8

P11

TDATA9

O

Tx Line Serial Data for Port 9

K16 TEST

I

Test

Control

A8

TFP0

I/O

Tx Frame Pulse for Port 0

E7 TFP1

I/O

Tx Frame Pulse for Port 1

P12 TFP10

I/O

Tx Frame Pulse for Port 10

R13 TFP11

I/O

Tx Frame Pulse for Port 11

T14 TFP12

I/O

Tx Frame Pulse for Port 12

T15 TFP13

I/O

Tx Frame Pulse for Port 13

M14 TFP14

I/O

Tx Frame Pulse for Port 14

L13 TFP15

I/O

Tx Frame Pulse for Port 15

C7 TFP2

I/O

Tx Frame Pulse for Port 2

DS26102 16-Port TDM-to-ATM PHY

11 of 64

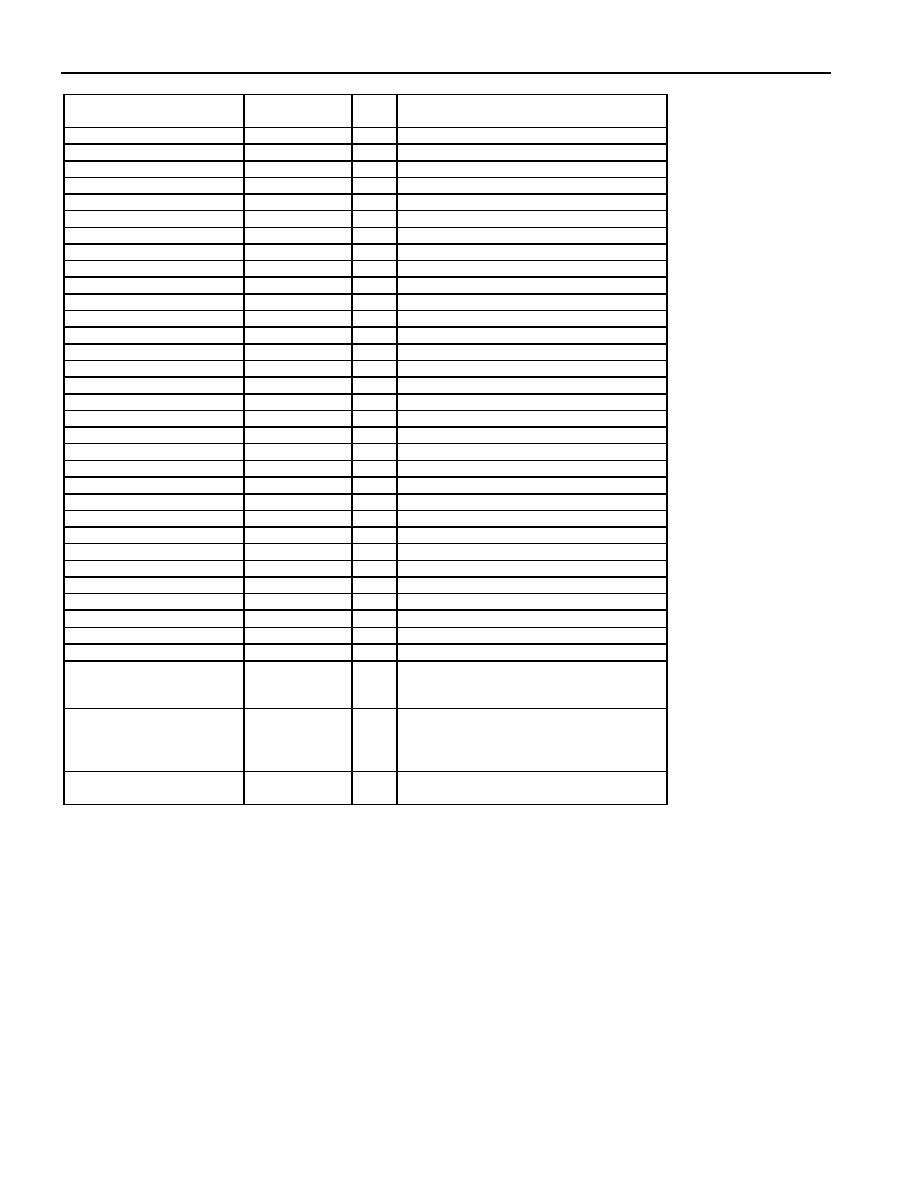

PIN NAME

I/O FUNCTION

D6 TFP3

I/O

Tx Frame Pulse for Port 3

B6 TFP4

I/O

Tx Frame Pulse for Port 4

A5 TFP5

I/O

Tx Frame Pulse for Port 5

A4 TFP6

I/O

Tx Frame Pulse for Port 6

C4 TFP7

I/O

Tx Frame Pulse for Port 7

T11 TFP8

I/O

Tx Frame Pulse for Port 8

M12 TFP9

I/O

Tx Frame Pulse for Port 9

G1

UT_2CLAV0

O

Tx UTOPIA 2 Cells Available 0

H4

UT_2CLAV1

O

Tx UTOPIA 2 Cells Available 1

H1

UT_2CLAV2

O

Tx UTOPIA 2 Cells Available 2

H3

UT_2CLAV3

O

Tx UTOPIA 2 Cells Available 3

D3

UT_ADDR0

I

Tx UTOPIA Address 0 (LSB)

A2

UT_ADDR1

I

Tx UTOPIA Address 1

C3

UT_ADDR2

I

Tx UTOPIA Address 2

B3

UT_ADDR3

I

Tx UTOPIA Address 3

A3

UT_ADDR4

I

Tx UTOPIA Address 4 (MSB)

G4

UT_CLAV0

O

Tx UTOPIA Cell Available 0

G3

UT_CLAV1

O

Tx UTOPIA Cell Available 1

G2

UT_CLAV2

O

Tx UTOPIA Cell Available 2

H5

UT_CLAV3

O

Tx UTOPIA Cell Available 3

F2

UT_CLK

I

Tx UTOPIA Clock

F1

UT_DATA0

I

Tx UTOPIA Data Bus 0 (LSB)

F4

UT_DATA1

I

Tx UTOPIA Data Bus 1

F5

UT_DATA2

I

Tx UTOPIA Data Bus 2

E2

UT_DATA3

I

Tx UTOPIA Data Bus 3

E3

UT_DATA4

I

Tx UTOPIA Data Bus 4

E1

UT_DATA5

I

Tx UTOPIA Data Bus 5

E4

UT_DATA6

I

Tx UTOPIA Data Bus 6

D2

UT_DATA7

I

Tx UTOPIA Data Bus 7 (MSB)

D1

UT_ENB

I

Tx UTOPIA Enable (Active Low)

G5

UT_PAR

I

Tx UTOPIA Parity Bit

F3

UT_SOC

I

Tx UTOPIA Start of Cell

F8, F9, G8, G9, H6, H7,

H10, H11, J6, J7, J10, J11,

K8, K9, L8, L9

VDD --

Positive

Supply

F6, F7, F10, F11, G6, G7,

G10, G11, H8, H9, J8, J9,

K6, K7, K10, K11, K14,

K15, L6, L7, L10, L11

VSS --

Ground

D13

WR (R/W)

I

Write Enable (Active Low)

Note 1: Address-latch enable for muxed bus.

Note 2: Open-drain output.

DS26102 16-Port TDM-to-ATM PHY

12 of 64

6. SIGNAL DEFINITIONS

6.1 TDM

Signals

Signal Name:

RCLK015

Signal Description:

Receive Line Clock (Ports 0 to 15)

Signal Type:

Input

The physical layer device uses the RCLK input to latch the RDATA and RFP signals. RDATA and RFP are sampled

by the receive section of the DS26102 at either the positive edge or negative edge of RCLK, as controlled by the

RAES (RCR2.2) control bit. RCLK is gapped during nonactive and framing bit positions in gapped-clock mode

(RPLIM = 1). RCLK should be glitch-free.

Signal Name:

RDATA015

Signal Description:

Receive Line Data (Ports 0 to 15)

Signal Type:

Input

The RDATA input carries the receive bit stream. If the RCLK is gapped at framing bit positions, RDATA is then

sampled at every RCLK tick. If RCLK is not gapped and RFP is used to indicate framing bit positions, the RDATA

bits that are not associated with framing-overhead bits are sampled and cell delineated. In clear E1, RDATA is

sampled at every RCLK tick.

Signal Name:

RFP015

Signal Description:

Receive Frame Pulse (Ports 0 to 15)

Signal Type:

Input

This active-high signal indicates the framing-overhead bit positions corresponding to RDATA. For T1/E1, this aligns

with the first bit of the T1/E1 frame. For T1, RDATA coming at the RFP position is ignored. For E1, RFP is used to

identify TS0 (RFP position is bit 0 of TS0) and TS16 locations, and RDATA coming at these slots are ignored. In

clear E1, RFP is ignored. In frame-pulse mode, the RFP should come once every 125

ms.

Signal Name:

TCLK015

Signal Description:

Transmit Line Clock (Ports 0 to 15)

Signal Type:

Input

The TCLK input is used by the DS26102's transmit section to launch TDATA and TFP (when configured as an

output) at either positive edge or negative edge, as controlled by the TAES (TCR2.2) control bit.

Signal Name:

TDATA015

Signal Description:

Transmit Line Data (Ports 0 to 15)

Signal Type:

Output

The TDATA output carries the transmit bit stream. ATM layer data bits are not transmitted during framing/overhead

bit locations. TDATA is output at the TCLK configured active edge.

Signal Name:

TFP015

Signal Description:

Transmit Frame Pulse (Ports 0 to 15)

Signal Type:

Input/Output

This active-high signal can be set as an input or an output by using the TFSD (TCR2.0) control bit. TFP indicates

the frame-overhead bit positions corresponding to TDATA. For T1/E1, this signal aligns with the first bit of the

T1/E1 frame. For T1, TDATA coming at the TFP position does not contain valid data bit. For E1, TFP is used to

identify TS0 (TFP position is bit 0 of TS0) and TS16. TDATA does not contain valid data at these locations. After

RESET, the DS26102 is configured to use this signal as an input. In frame-pulse mode, the TFP should occur once

every 125

ms.

6.2 UTOPIA-Side

Signals

Signal Name:

UR_CLK

Signal Description:

Receive UTOPIA Clock

Signal Type:

Input

This clock is used to register and control all other UTOPIA signals on the receive side.

DS26102 16-Port TDM-to-ATM PHY

13 of 64

Signal Name:

UR_ADDR[4:0]

Signal Description:

Receive UTOPIA Address

Signal Type:

Input

The ATM layer drives this 5-bit UTOPIA address bus to select the appropriate UTOPIA port. UR_ADDR4 is the

MSB and UR_ADDR0 is the LSB.

Signal Name:

UR_ENB

Signal Description:

Receive UTOPIA Enable

Signal Type:

Input

The ATM layer asserts this active-low signal to indicate that UR_DATA and UR_SOC are sampled at the end of the

next cycle.

Signal Name:

UR_SOC

Signal Description:

Receive UTOPIA Start of Cell

Signal Type:

Output

The DS26102 asserts this active-high, tri-statable signal when UR_DATA contains the first valid byte of a cell.

UR_SOC is enabled only in cycles following those with

UR_ENB asserted while a cell transfer is in progress.

Signal Name:

UR_DATA[7:0]

Signal Description:

Receive UTOPIA Data Bus

Signal Type:

Output

The DS26102 drives this byte-wide data bus in response to the selection of one of the UTOPIA ports by the ATM

layer for cell transfer. This bus is three-statable, and is enabled only in cycles following those that have

UR_ENB

asserted and a cell transfer in progress for a port. UR_DATA7 is the MSB and UR_DATA0 is the LSB.

Signal Name:

UR_CLAV[3:0]

Signal Description:

Receive UTOPIA Cell Available

Signal Type:

Output

The active-high UR_CLAV signals are asserted if a complete cell is available for transfer to the ATM layer for the

polled port. If UR_ADDR does not match any of the UTOPIA port addresses, this signal is tri-stated. UR_CLAV0 is

driven in multiplexed with 1 CLAV polling mode as well as direct status mode for port 1. UR_CLAV3, UR_CLAV2,

and UR_CLAV1 are driven only in direct status mode for ports 4, 3, and 2, respectively.

Signal Name:

UR_PAR

Signal Description:

Receive UTOPIA Parity Bit

Signal Type:

Output

This three-statable signal allows for parity error checking, as calculated for the 8-bits of the UR_DATA bus, and can

represent odd or even parity as determined by the receive parity select bit (RPS) in RCR1.

Signal Name:

UT_CLK

Signal Description:

Transmit UTOPIA Clock

Signal Type:

Input

This clock is used to register and control the UTOPIA signals on the transmit side.

Signal Name:

UT_ADDR[4:0]

Signal Description:

Transmit UTOPIA Address

Signal Type:

Input

The ATM layer drives this 5-bit-wide bus to poll and select the appropriate UTOPIA port. UT_ADDR4 is the MSB

and UT_ADDR0 is the LSB.

Signal Name:

UT_ENB

Signal Description:

Transmit UTOPIA Enable

Signal Type:

Input

The ATM layer asserts this active-low enable signal during cycles when UT_DATA contains valid cell data.

DS26102 16-Port TDM-to-ATM PHY

14 of 64

Signal Name:

UT_SOC

Signal Description:

Transmit UTOPIA Start of Cell

Signal Type:

Input

The ATM layer asserts this active-high signal when UT_DATA contains the first valid byte of the cell.

Signal Name:

UT_DATA[7:0]

Signal Description:

Transmit UTOPIA Data Bus

Signal Type:

Input

The ATM layer drives this byte-wide true data to one of the selected ports. UT_DATA7 is the MSB and UT_DATA0

is the LSB.

Signal Name:

UT_CLAV[3:0]

Signal Description:

Transmit UTOPIA Cell Available

Signal Type:

Output

The DS26102 asserts this active-high UT_CLAV signal if it has cell space available to accommodate a complete

cell from the ATM layer to the polled port. If UT_ADDR does not match with any one of the UTOPIA port

addresses, this signal is tri-stated. UT_CLAV0 is driven in multiplexed with 1 CLAV polling mode as well as direct

status mode for port 1. UT_CLAV3, UT_CLAV2, and UT_CLAV1 are driven only in direct status mode for ports 4,

3, and 2, respectively.

Signal Name:

UT_2CLAV[3:0]

Signal Description:

Transmit UTOPIA 2 Cells Available

Signal Type:

Output

The DS26102 asserts this active-high UT_2CLAV signal if it has cell space available to accommodate two

complete cells from the ATM layer. If UT_ADDR does not match with any one of the UTOPIA port addresses, this

signal is tri-stated. UT_2CLAV0 is driven in multiplexed with 2 CLAV polling mode as well as direct status mode for

port 1. UT_2CLAV3, UT_2CLAV2, and UT_2CLAV1 are driven only in direct status mode for ports 4, 3, and 2,

respectively.

Signal Name:

UT_PAR

Signal Description:

Transmit UTOPIA Parity Bit

Signal Type:

Input

This signal is used for parity checking as calculated for the 8 bits of the UT_DATA bus. Transmit parity errors are

reported in the port status register (PSR) at bit 6. This bit can represent odd or even parity, as determined by the

transmit parity select (TPRS) bit in TCR1.

6.3 Microprocessor and System Interface Signals

Signal Name:

A[6:0]

Signal Description:

Microprocessor Address Bus

Signal Type:

Input

This bus selects a specific register in the DS26102 during read/write access. A7 is the MSB and A0 is the LSB. A7

is also used as the address latch enable (ALE/AS) during multiplexed bus operation (MUX = 1).

Signal Name:

A7/ALE (AS)

Signal Description:

Address Latch Enable (Address Strobe) or A7

Signal Type:

Input

In nonmultiplexed bus operation (MUX = 0), the ALE serves as the upper address bit. In multiplexed bus operation

(MUX = 1), it serves to demultiplex the bus on a positive-going edge.

Signal Name:

D[7:0]/AD[7:0]

Signal Description:

Microprocessor Data Bus

Signal Type:

Input/Output

This 8-bit, bidirectional data bus is used for read/write access of the DS26102's information and control registers.

D7/AD7 is the MSB and D0/AD0 is the LSB. This bus also carries address information during multiplexed operation

(MUX = 1).

DS26102 16-Port TDM-to-ATM PHY

15 of 64

Signal Name:

CS

Signal Description:

Chip Select

Signal Type:

Input

This active-low signal is used to qualify register read/write accesses. The

RD and WR signals are qualified with CS.

Signal Name:

RD (DS)

Signal Description:

Read Enable

Signal Type:

Input

Along with CS, this active-low signal qualifies read access to one of the DS26102 registers. While

RD and CS are

both low, the DS26102 drives the D/AD bus with the contents of the addressed register.

Signal Name:

WR (R/W)

Signal Description:

Write Enable

Signal Type:

Input

Along with

CS, this active-low signal qualifies write access to one of the DS26102 registers. Data at D/AD[7:0] is

written into the addressed register at the rising edge of

WR while CS is low.

Signal Name:

INT

Signal Description:

Interrupt

Signal Type:

Output

This active-low, open-drain output is asserted when an unmasked interrupt event is detected.

INT is deasserted

when all interrupts have been acknowledged and serviced.

Signal Name:

MUX

Signal Description:

Bus Operation

Signal Type:

Input

Set this signal low to select nonmultiplexed bus operation. Set it high to select multiplexed bus operation.

Signal Name:

BTS

Signal Description:

Bus Type Select

Signal Type:

Input

Set this signal high to select Motorola bus timing; set it low to select Intel bus timing. This pin controls the function

of the

RD (DS), ALE (AS), and WR (R/W) pins. If BTS = 1, these pins assume the function listed in parentheses ().

Signal Name:

BLS0

Signal Description:

Block Select 0

Signal Type:

Input

This signal is available on the DS26102 to determine which octal block of ports is mapped to the microprocessor

control port.

Signal Name:

REFCLKIN

Signal Description:

Reference Clock

Signal Type:

Input

This continuous T1 (1.544MHz) or E1 (2.048MHz) clock is used to create GCLKOUT.

Signal Name:

GCLKOUT

Signal Description:

Global Clock Output

Signal Type:

Output

This output clock is 16x the REFCLKIN input (24.7MHz (typ) for T1). This pin is usually connected to GCLKIN.

Signal Name:

GCLKIN

Signal Description:

Global Clock Input

Signal Type:

Input

This is the primary clock for internal state machines. It can be connected to GCLKOUT or provided by the user.

The GCLKIN frequency must be at least 10x the T1 or E1 line rate.

DS26102 16-Port TDM-to-ATM PHY

16 of 64

Signal Name:

RESET

Signal Description:

System Reset

Signal Type:

Input

This is an active-low reset. Forcing this input low sets all internal registers to their default value.

Signal Name:

8KHZIN

Signal Description:

8kHz Reference Clock

Signal Type:

Input

This continuous clock is used to generate the internal one-second-timer pulse. It can be a T1/E1 frame sync.

Signal Name:

1SECOUT

Signal Description:

One-Second Clock Output

Signal Type:

Output

This is a one-second reference-pulse output created by dividing 8KHzIN by 8000. Using this signal is optional.

Signal Name:

EXSTAT0-8

Signal Description:

External Status Input (1 to 8)

Signal Type:

Input

A low-to-high transition on this pin sets the EXSTAT status bit in the port status register (PSR). EXSTAT1 maps to

the PSR for port 1 up to EXSTAT8, which maps to port 8. The EXSTAT bit can be enabled to generate an interrupt

by setting the EXSTATIM bit in RCR2. These signals could be connected to an external event timer, an external

status signal, or the 1SECOUT signal generated by the DS26102. Application of this signal is optional. If not used,

the EXSTAT signals should be grounded.

Signal Name:

RLCD015

Signal Description:

Receive Loss-of-Cell Delineation for Ports 1 to 15

Signal Type:

Output

This signal is the hardware representation of the LCDS status bit (PSR.2). For example, if RLCD3 is high (logic 1),

then port 3's receiver has lost cell delineation (synchronization) with the incoming data stream.

6.4 Test and JTAG Signals

Signal Name:

JTRST

Signal Description:

IEEE 1149.1 Test Reset

Signal Type:

Input

JTRST is used to asynchronously reset the test access port (TAP) controller. After power-up, JTRST must be

toggled from low to high. This action sets the device into the JTAG DEVICE ID mode. Pulling JTRST low restores

normal device operation. JTRST is pulled high internally through a 10k resistor operation. If boundary scan is not

used, this pin should be held low.

Signal Name:

JTMS

Signal Description:

IEEE 1149.1 Test Mode Select

Signal Type:

Input

This pin is sampled on the rising edge of JTCLK and is used to place the TAP into the various defined IEEE 1149.1

states. This pin has a 10k pullup resistor.

Signal Name:

JTCLK

Signal Description:

IEEE 1149.1 Test Clock Signal

Signal Type:

Input

This signal is used to shift data into JTDI on the rising edge and out of JTDO on the falling edge.

Signal Name:

JTDI

Signal Description:

IEEE 1149.1 Test Data Input

Signal Type:

Input

Test instructions and data are clocked into this pin on the rising edge of JTCLK. This pin has a 10k pullup

resistor.

DS26102 16-Port TDM-to-ATM PHY

17 of 64

Signal Name:

JTDO

Signal Description:

IEEE 1149.1 Test Data Output

Signal Type:

Output

Test instructions and data are clocked out of this pin on the falling edge of JTCLK. If not used, this pin should be

left unconnected.

Signal Name:

TEST

Signal Description:

Test Mode

Signal Type:

Input

When TEST is set to logic 1, the REFCLKIN input is connected to the internal SYS_CLK for the IP01 logic cores.

In this mode, the signal on REFCLKIN should be phase-aligned to GCLKIN with a frequency of GCLK/2. Also,

when TEST = 1 and

RESET = 0, all outputs of the DS26102 should be tri-stated.

7. TRANSMIT OPERATION

The DS26102 interface to the ATM layer is fully compliant to the ATM Forum's UTOPIA Level 2 specification. The

DS26102 supports multiplexed with 1 CLAV handshaking only. Each octal block can be configured to use any of

the address ranges (0 to 7, 8 to 15, 16 to 23, or 24 to 30) as UTOPIA port addresses. Each octal block on the bus

must be configured for a different UTOPIA address range. The depth of the Tx FIFO is configurable to 2, 3, or 4

cells. When a port is polled and has cell space available, the DS26102 generates a cell-available signal for that

port.

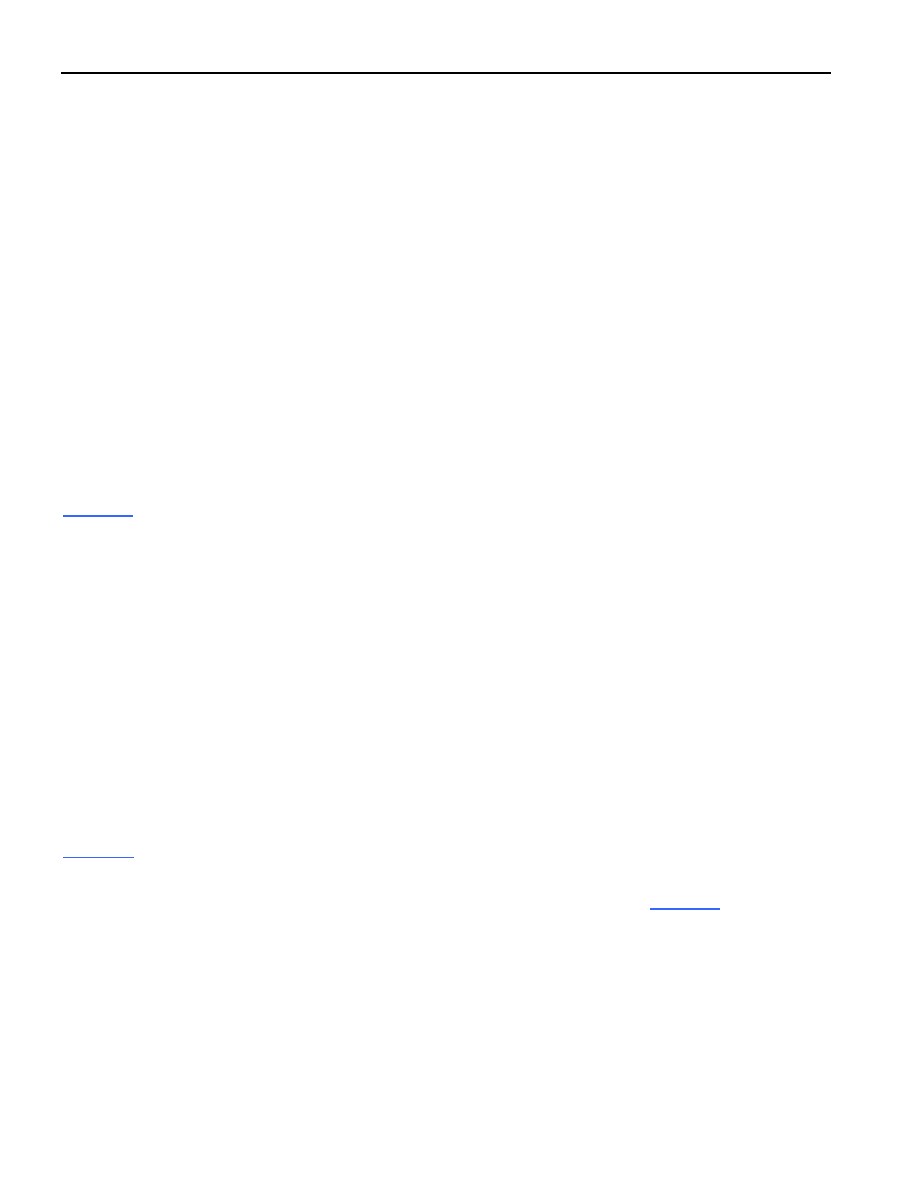

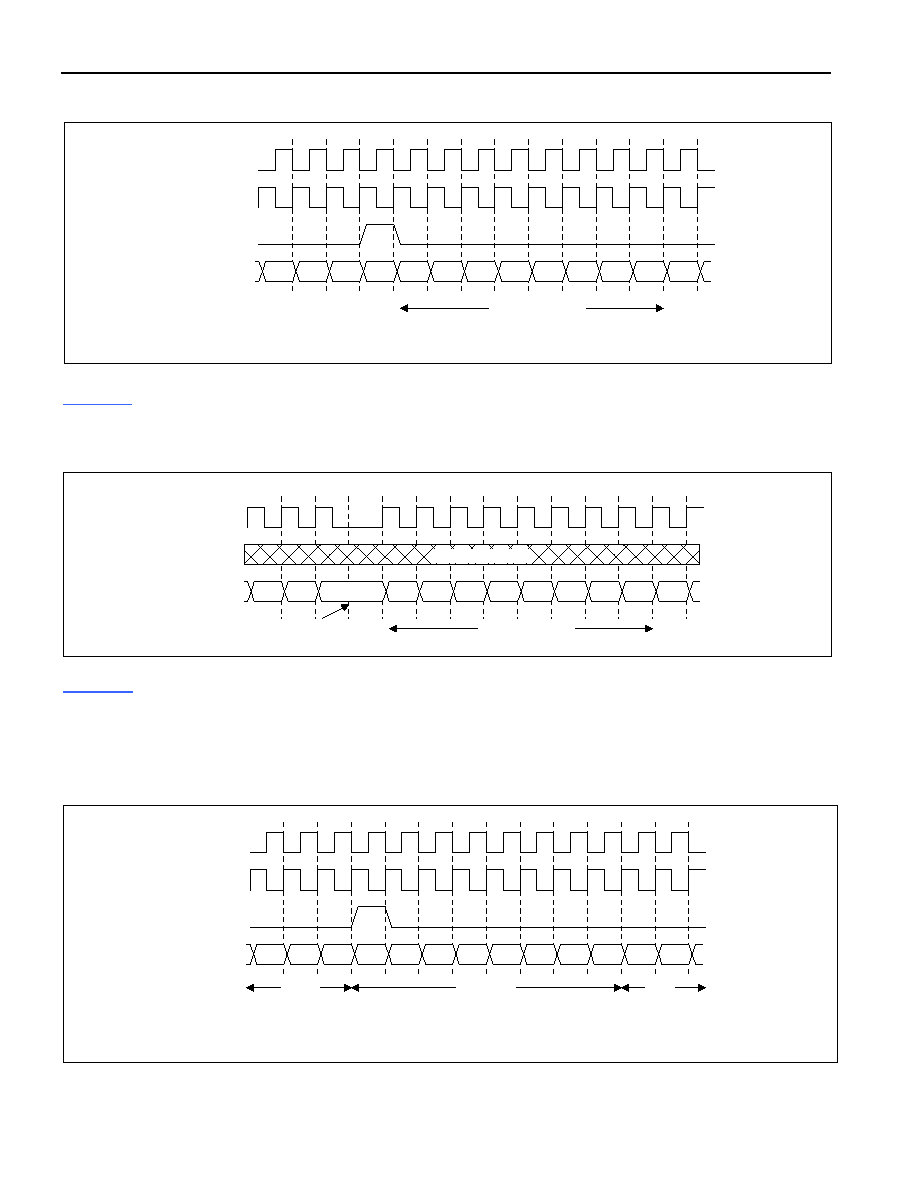

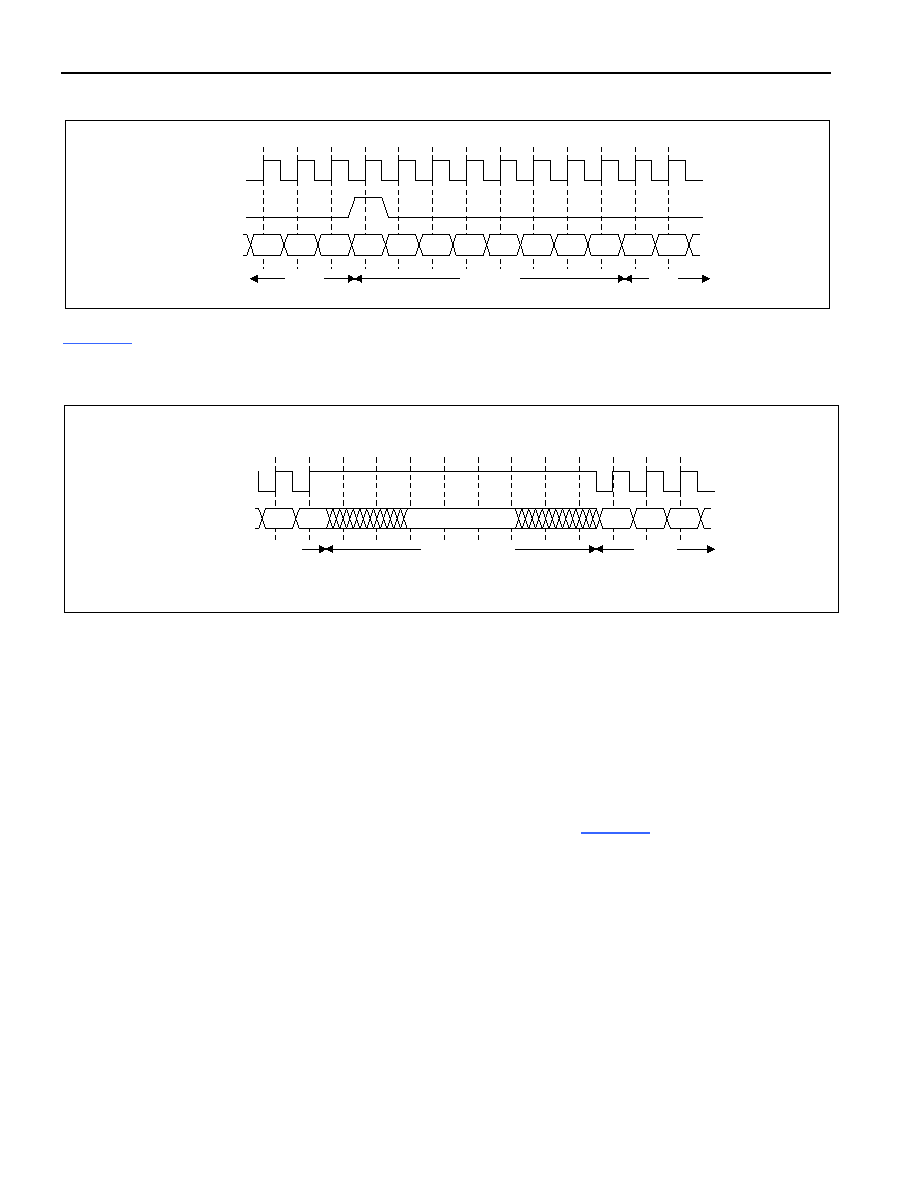

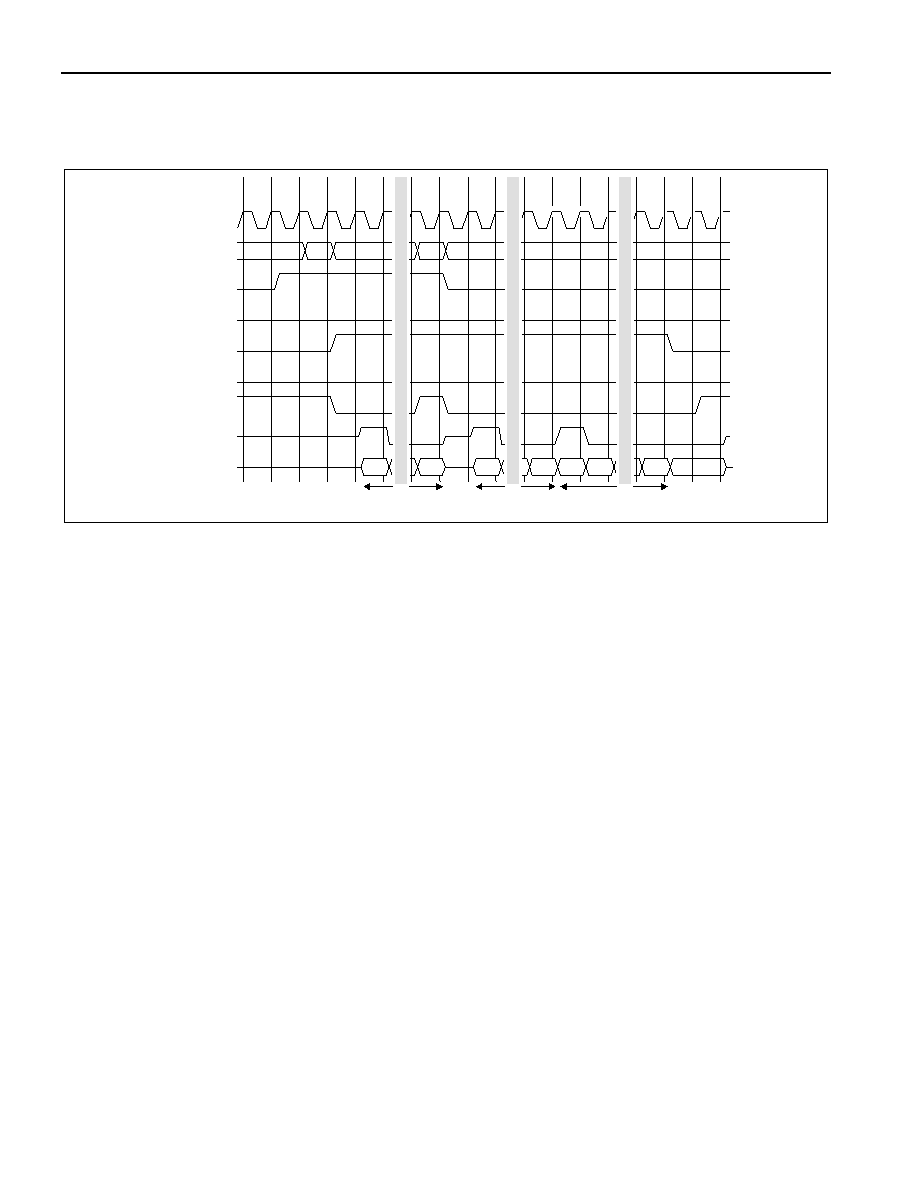

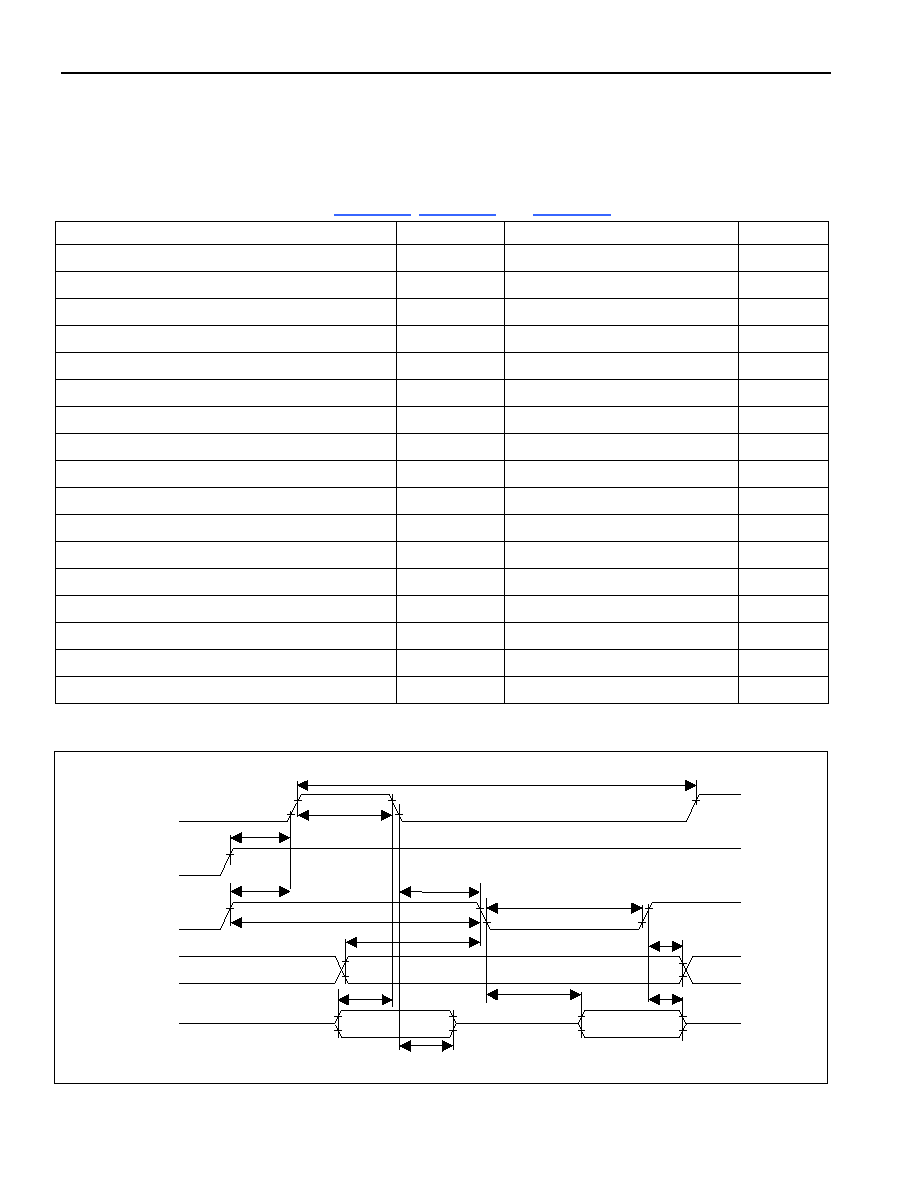

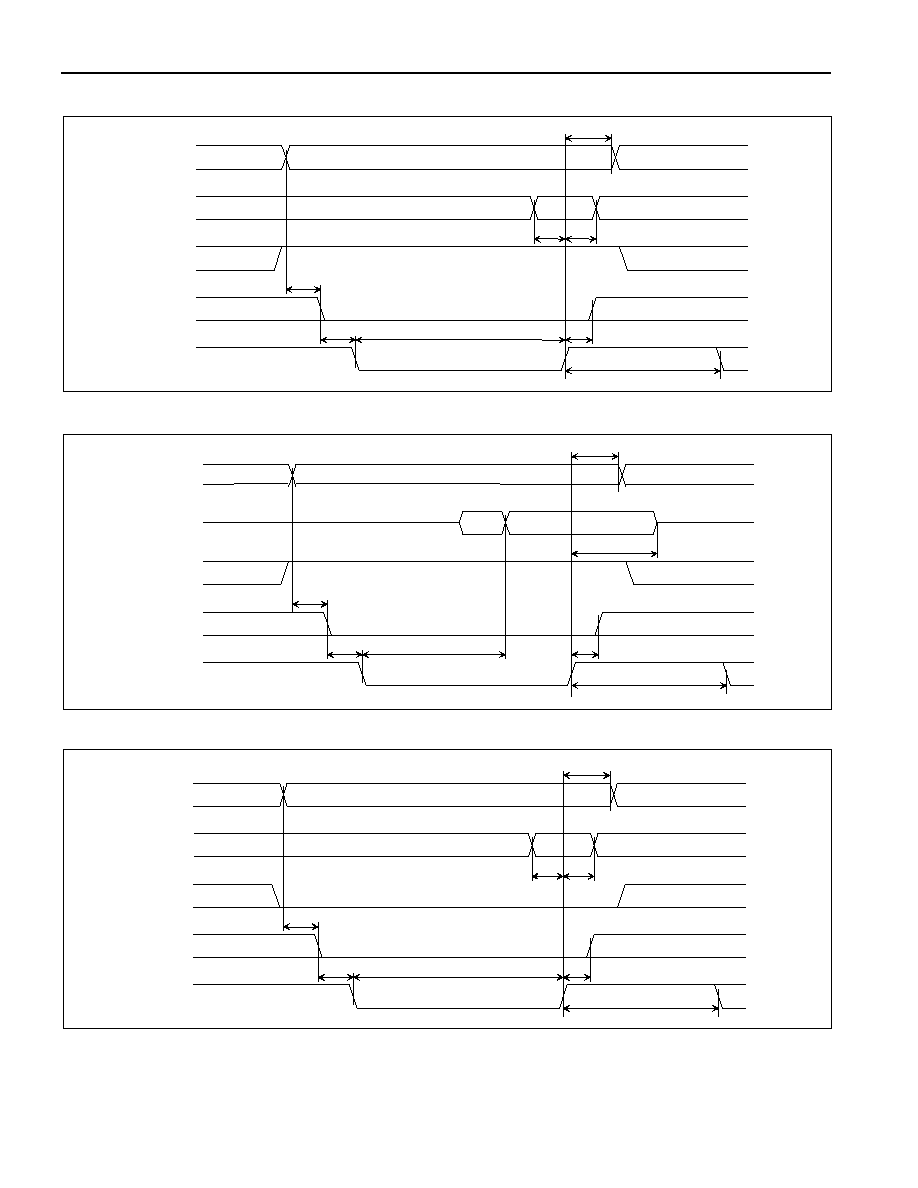

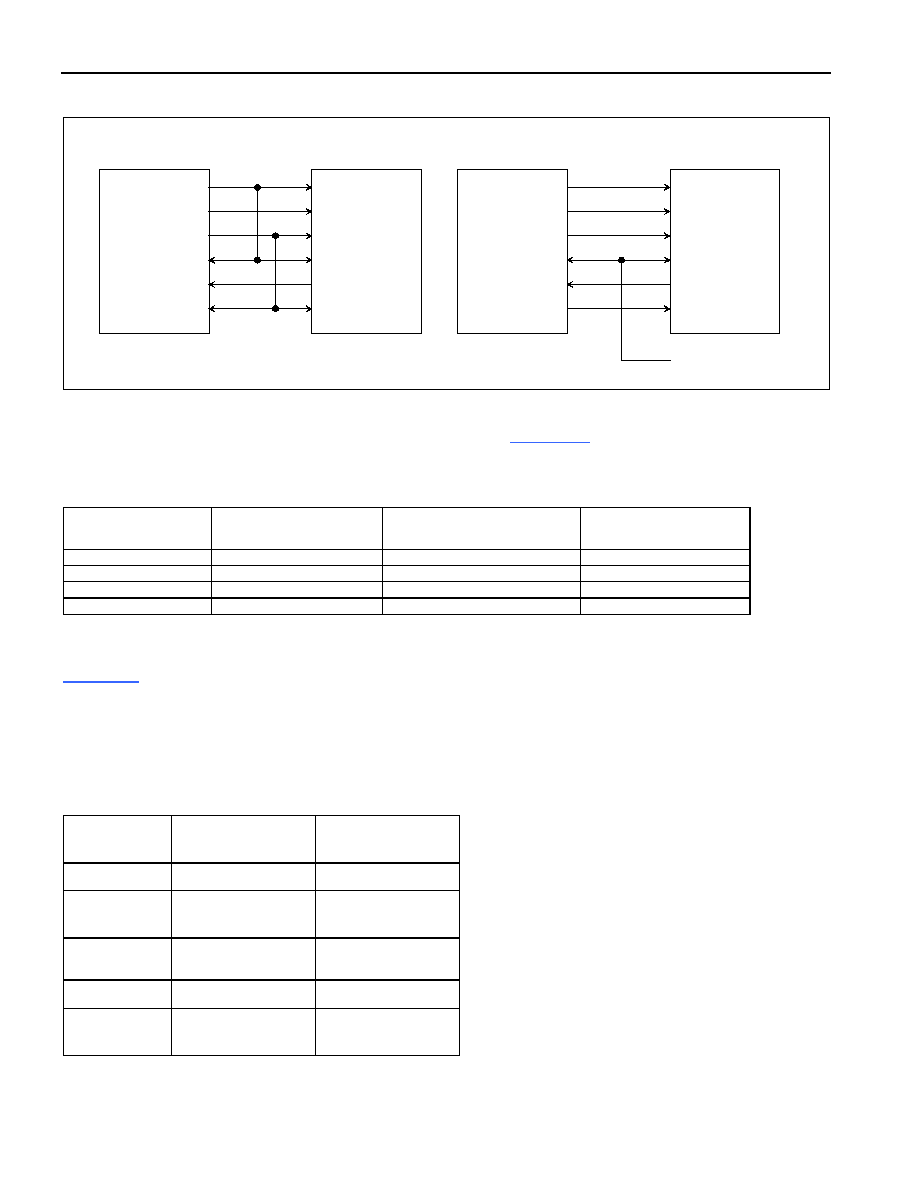

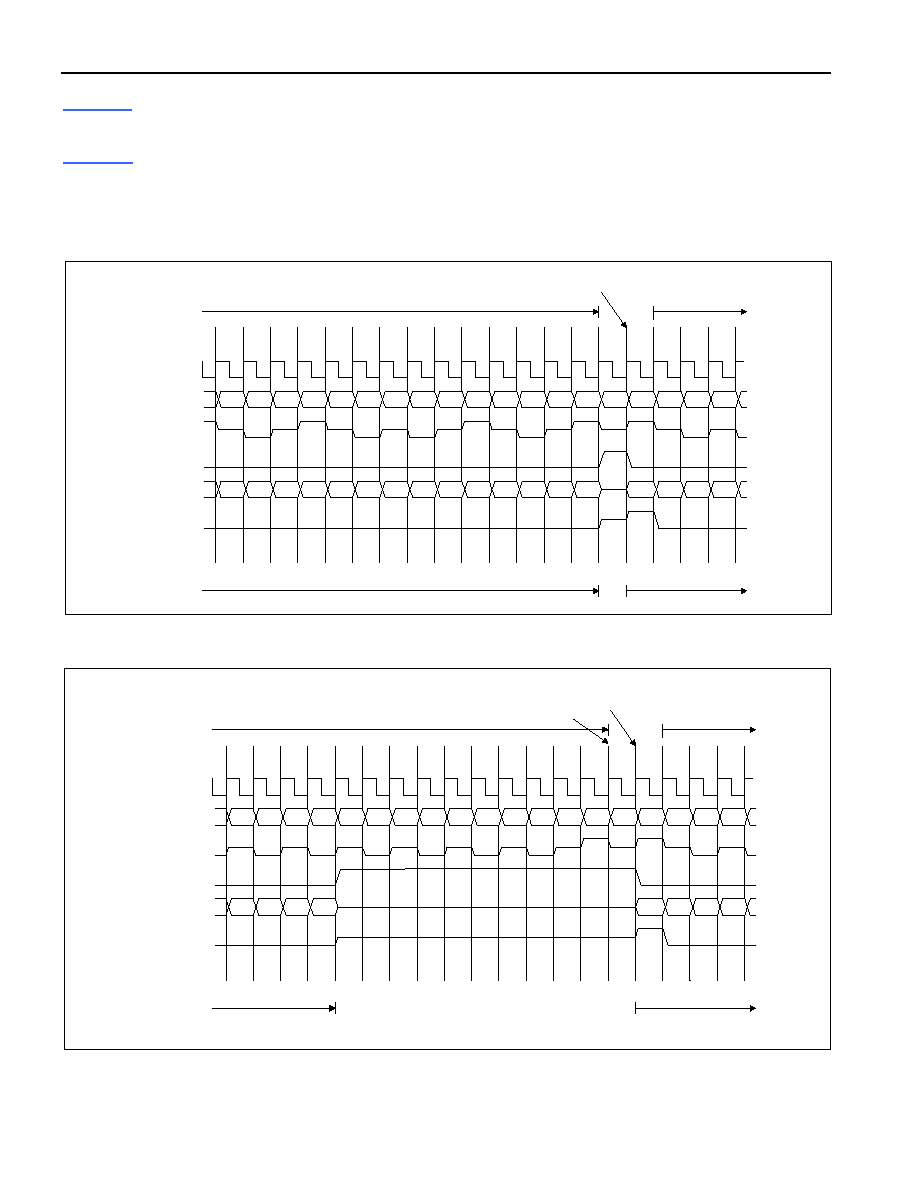

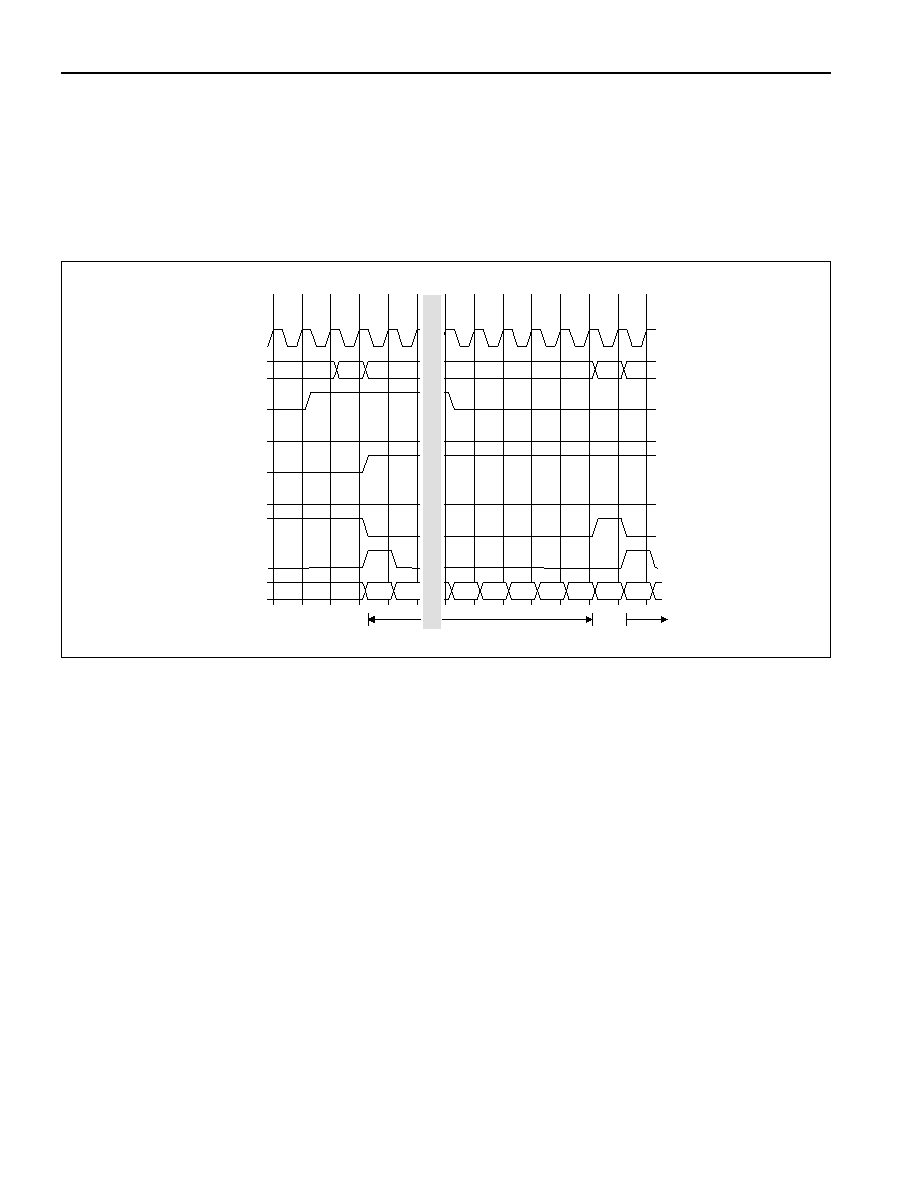

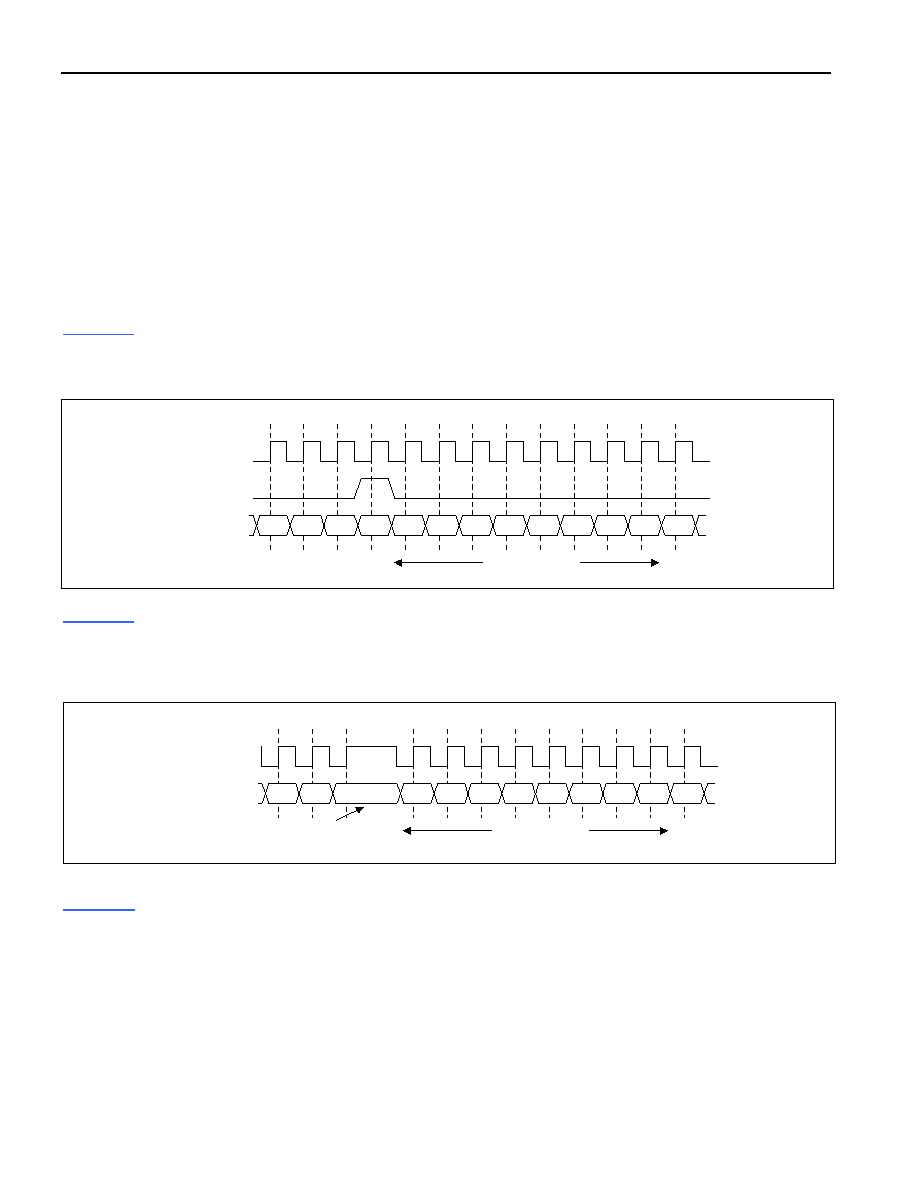

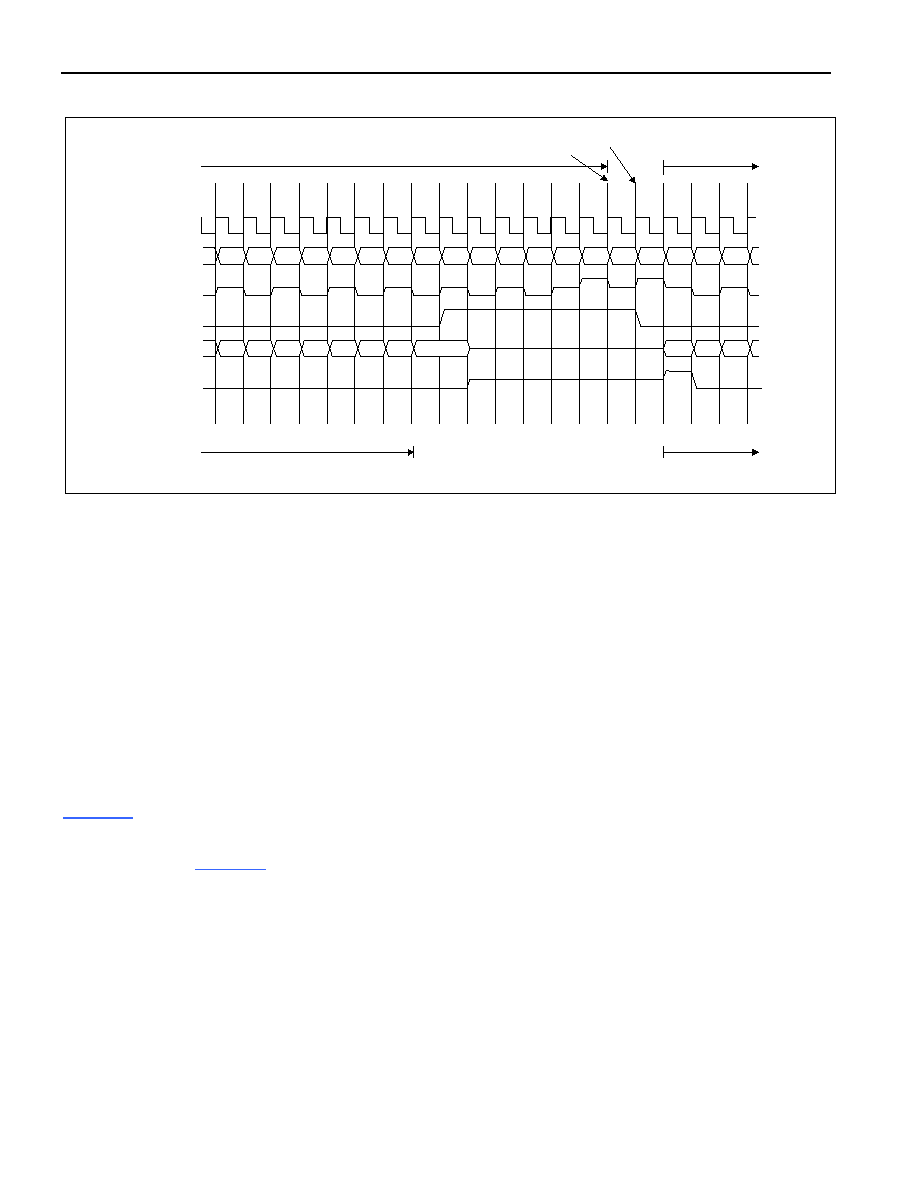

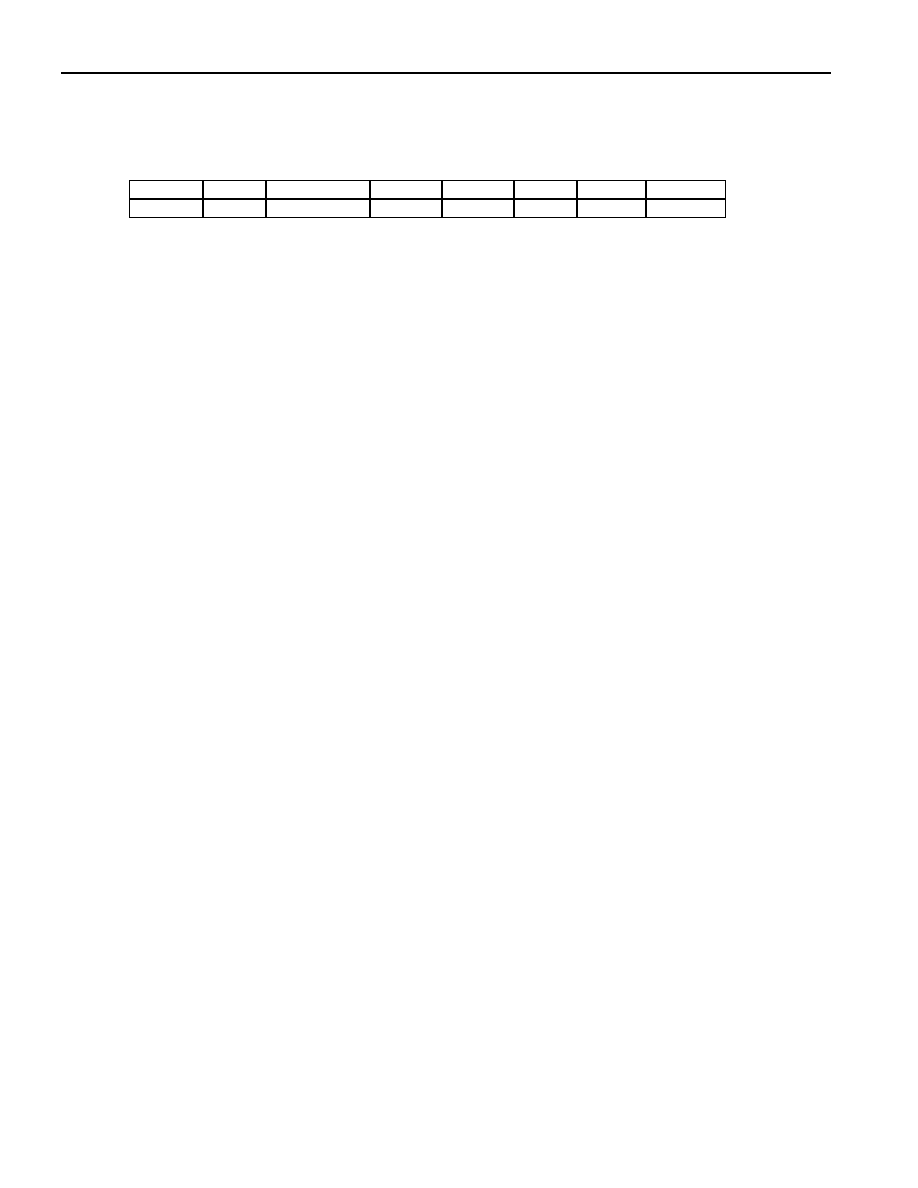

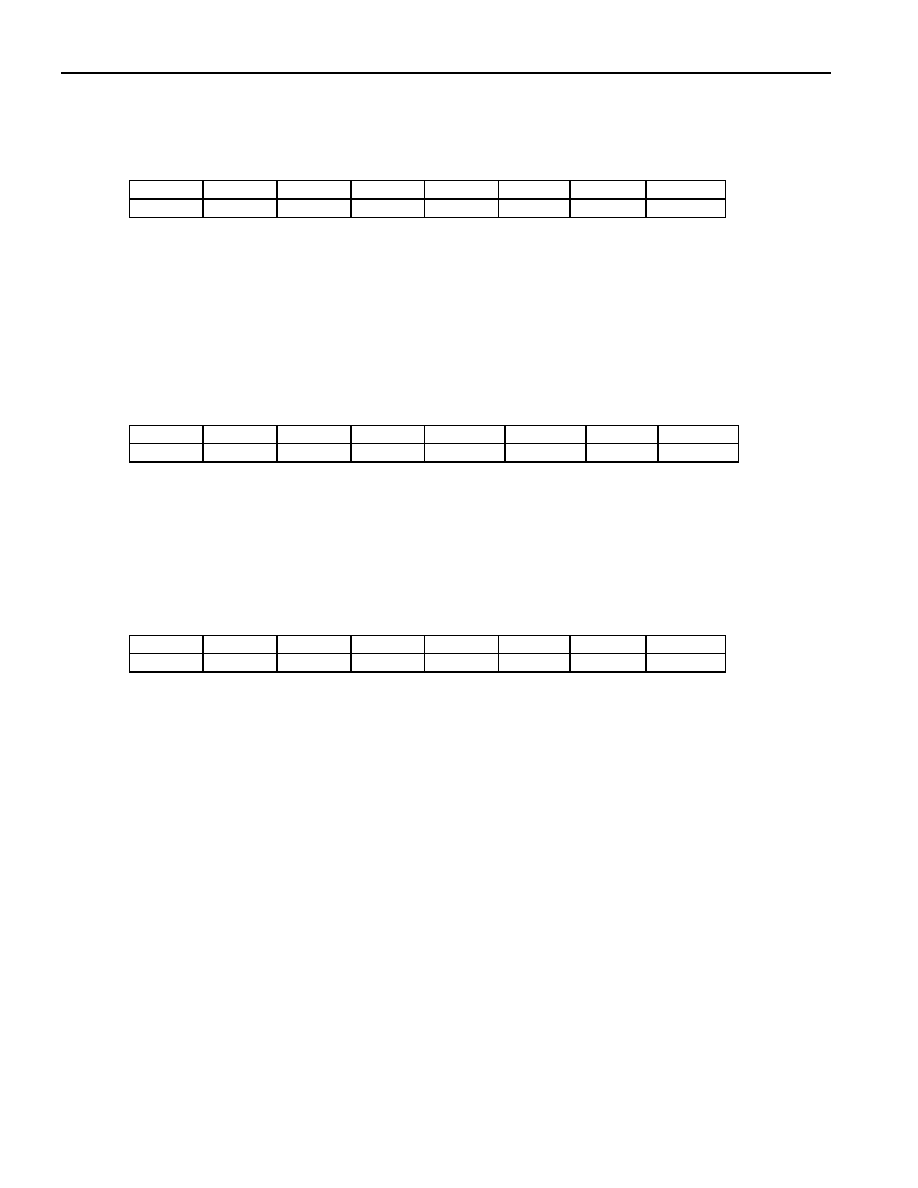

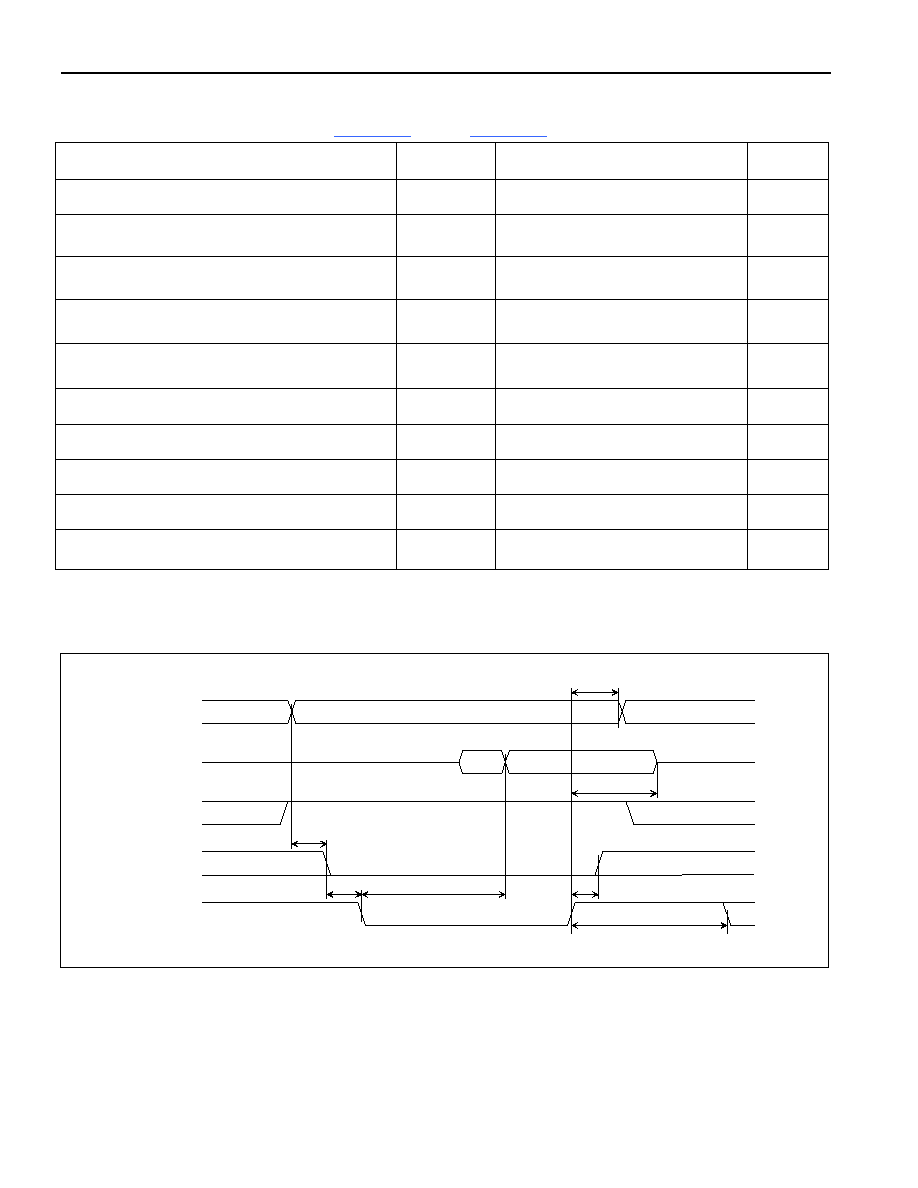

Figure 7-1

shows the polling and cell transfer cycles to UTOPIA ports in the DS26102. Note that UT_SOC must be

aligned with the first byte transfer. The DS26102 uses UT_SOC to detect the first byte of a cell. If a spurious

UT_SOC comes during a cell transfer, then the DS26102 aligns with the latest UT_SOC and ignores the bytes

(partial cell) received thus far.

7.1 UTOPIA-Side Transmit--Muxed Mode with 1 TXCLAV

In Level 1 UTOPIA there is only one PHY layer device. It uses UT_CLAV to convey transfer status to the ATM

layer. In Level 2 UTOPIA only one MPHY port at a time is selected for a cell transfer. However, another MPHY port

can be polled for its UT_CLAV status, while the selected MPHY port (device) transfers data. The ATM layer polls

the UT_CLAV status of an MPHY port by placing its address on UT_ADDR. The MPHY port (device) drives

UT_CLAV during each cycle, following one with its address on the UT_ADDR lines. The ATM layer selects an

MPHY port for transfer by placing the desired MPHY port address onto UT_ADDR, when UT_ENB is deasserted

during the current clock cycle and asserted during the next clock cycle. All MPHY devices only examine the value

on UT_ADDR for selection purposes when UT_ENB is deasserted. The MPHY port is selected starting from the

cycle after its address is on the UT_ADDR lines and UT_ENB is deasserted; a new MPHY port is addressed for

selection ending in the cycle and UT_ENB is deasserted. Once a MPHY port is selected, the cell transfer is

accomplished as described by the cell-level handshake of UTOPIA Level 1. To operate an MPHY device in a single

PHY environment, the address pins should be set to the value programmed by the management interface.

Figure 7-1

shows an example where PHYs are polled until the end of a cell transmission cycle. The UT_CLAV

signal shows that PHYs N - 3 and N + 3 can accept cells and that PHY N + 3 is selected. The PHY is selected with

the rising clock edge 16. Immediately after the beginning of cell transmission to PHY N + 3, the ATM layer starts

polling again. Up to 26 PHYs can be polled using the 2-clock polling cycles shown in

Figure 7-1

. This maximum

value can only be reached if all responses occur in minimum delays, e.g., as the figure shows, where the response

of the last PHY is obtained with clock edge 15, immediately followed by the UT_ENB pulse to the PHYs. If an ATM

implementation needs additional clock cycles to select the PHY, fewer than 26 PHY can be polled during one cell

cycle. Note that if the ATM decides to select PHY N again for the next cell transmission, it could leave the UT_ENB

line asserted and start transmitting the next cell with clock edge 15. This results in back-to-back cell transmission.

Note that the active PHY (PHY N) is polled in octet P48. According to the UTOPIA Level 1 specification, the PHY's

UT_CLAV signal at this time indicates the possibility of a subsequent cell transfer. Polling of PHY N before octet

P44 would be possible, but it does not indicate availability of the next cell.

DS26102 16-Port TDM-to-ATM PHY

18 of 64

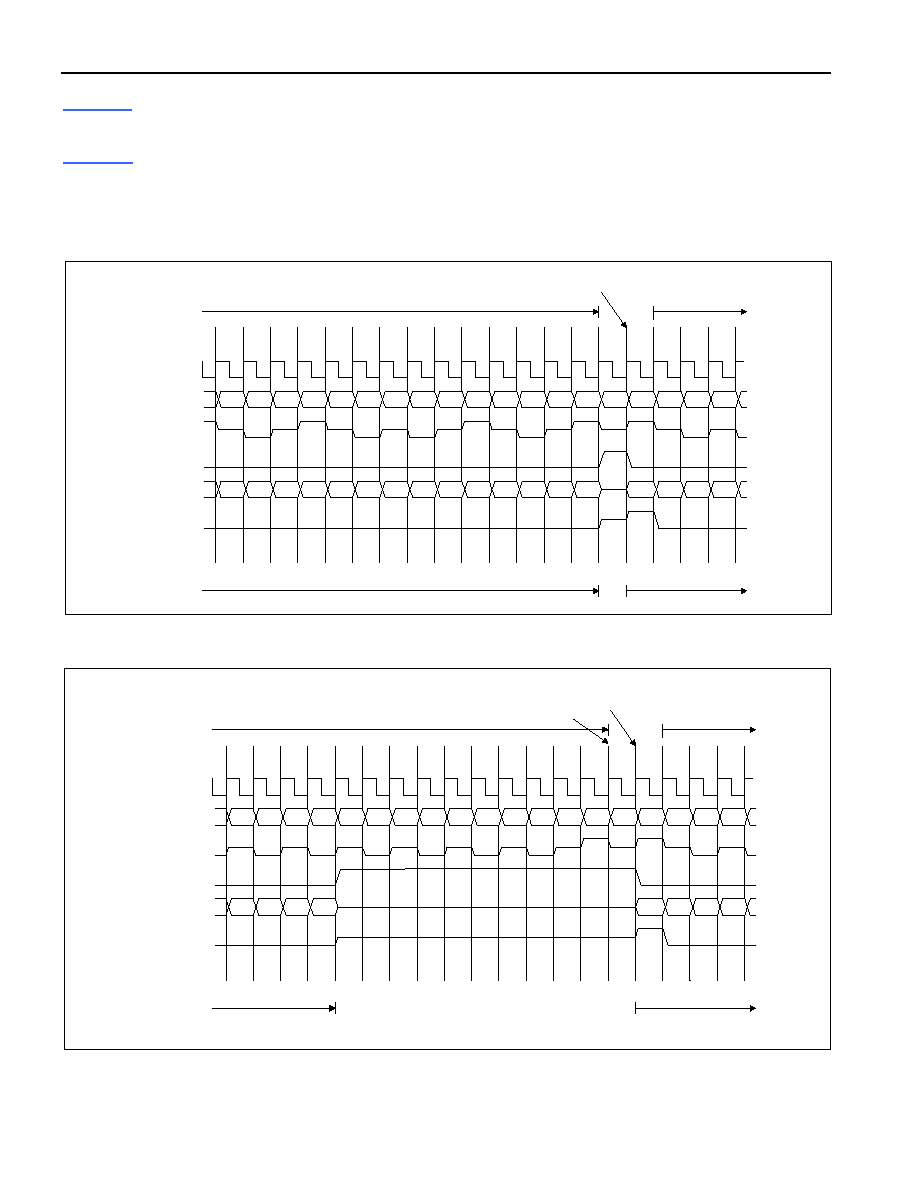

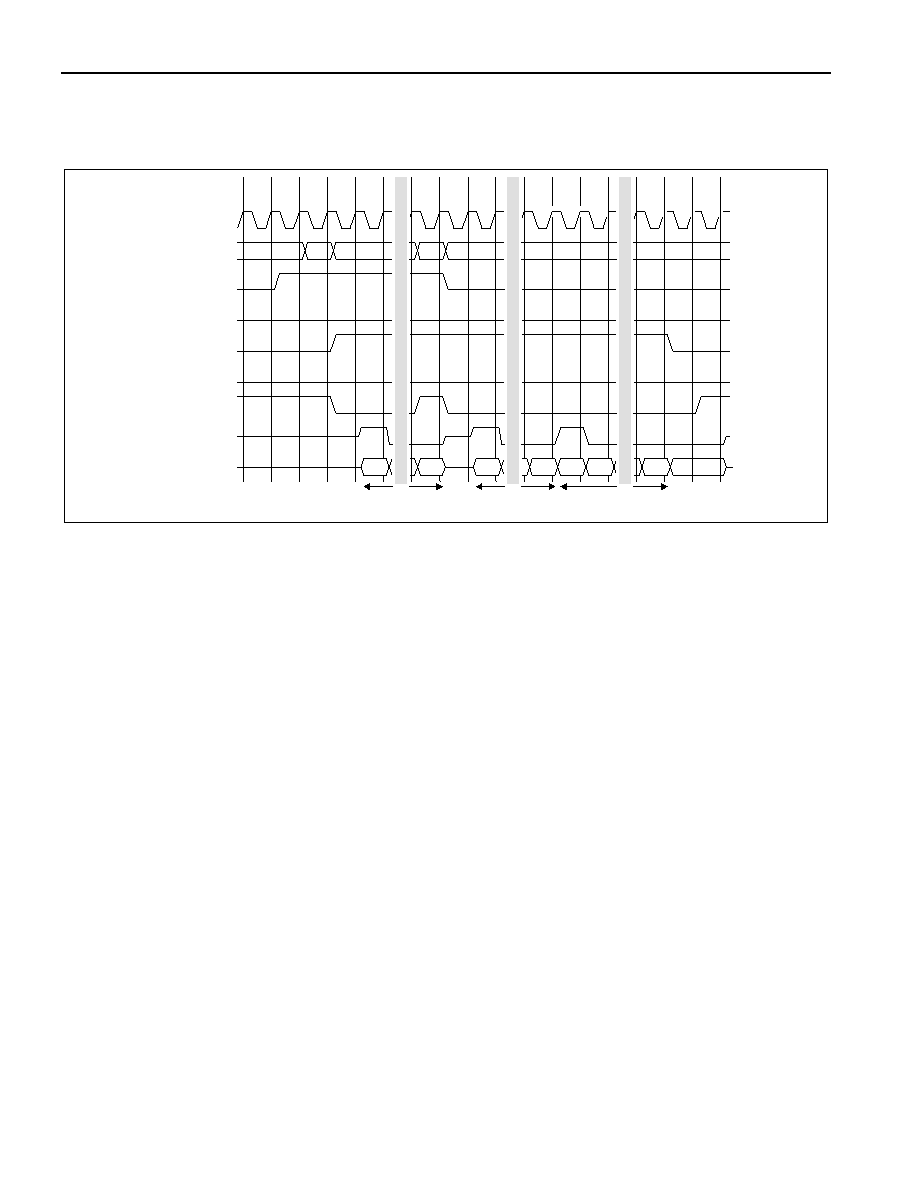

Figure 7-2

shows an example where the transmission of cells through the transmit interface is stopped by the ATM,

as no PHY is ready to accept cells. Polling then continues. Several clock cycles later one PHY gets ready to accept

a cell. During the transmission pause the UT_DATA and UT_SOC may go into high-impedance state, as shown in

Figure 7-2

. UT_ENB is held in deasserted state. When a PHY is found that is ready to accept a cell (PHY_N + 3 in

this case), the address of this PHY must be applied again to select it. This is necessary because of the 2-clock

polling cycle, where the PHY is detected at clock edge 15. At this time, the address of PHY N + 3 is no longer on

the bus, therefore, it must be applied again in the next clock cycle. PHY N + 3 is selected with clock edge 16.

Figure 7-1. Polling Phase and Selection Phase at Transmit Interface

Figure 7-2. End and Restart of Cell at Transmit Interface

N+1

1F

N-3

1F

N-2

1F

N-1

1F

N+3

N+1

1F

N

1F

N+3

1F

N+1

1F

N-1

1F

N+2

N-3

N-2

N-1

N+3

N+1

N

N+3

N+1

P35

P36

P37

P38

P39

P40

P41

P42

P43

P45

P46

P47

P48

H1

H2

H3

H4

P44

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

UT_CLK

UT_ADDR[4:0]

UT_CLAV[0]

UT_ENB

UT_DATA[7:0]

UT_SOC

CELL XMIT TO:

PHY N

PHY N+3

POLLING

POLLING

SELECTION

N+1

1F

N

1F

N+3

1F

N+2

1F

N-1

N

1F

N+3

1F

N+3

1F

N-2

1F

N-3

1F

N

P45

P46

P47

P48

H1

H2

H3

H4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

UT_CLK

UT_ADDR[4:0]

UT_CLAV[0]

UT_ENB

UT_DATA[7:0]

UT_SOC

CELL XMIT TO:

PHY N

PHY N+3

POLLING

POLLING

SELECTION

N+1

N

N+3

N+2

N-1

N+3

N+3

N-2

DETECTION

DS26102 16-Port TDM-to-ATM PHY

19 of 64

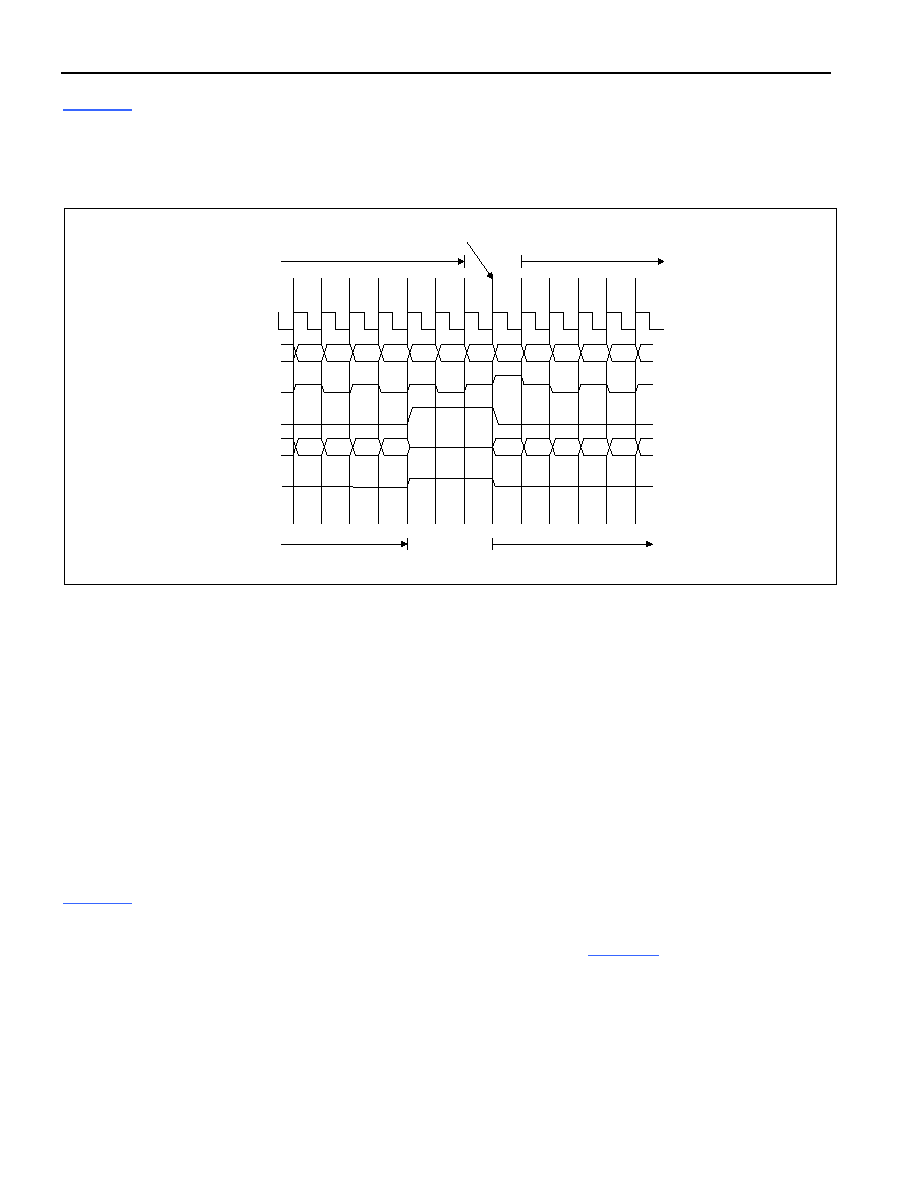

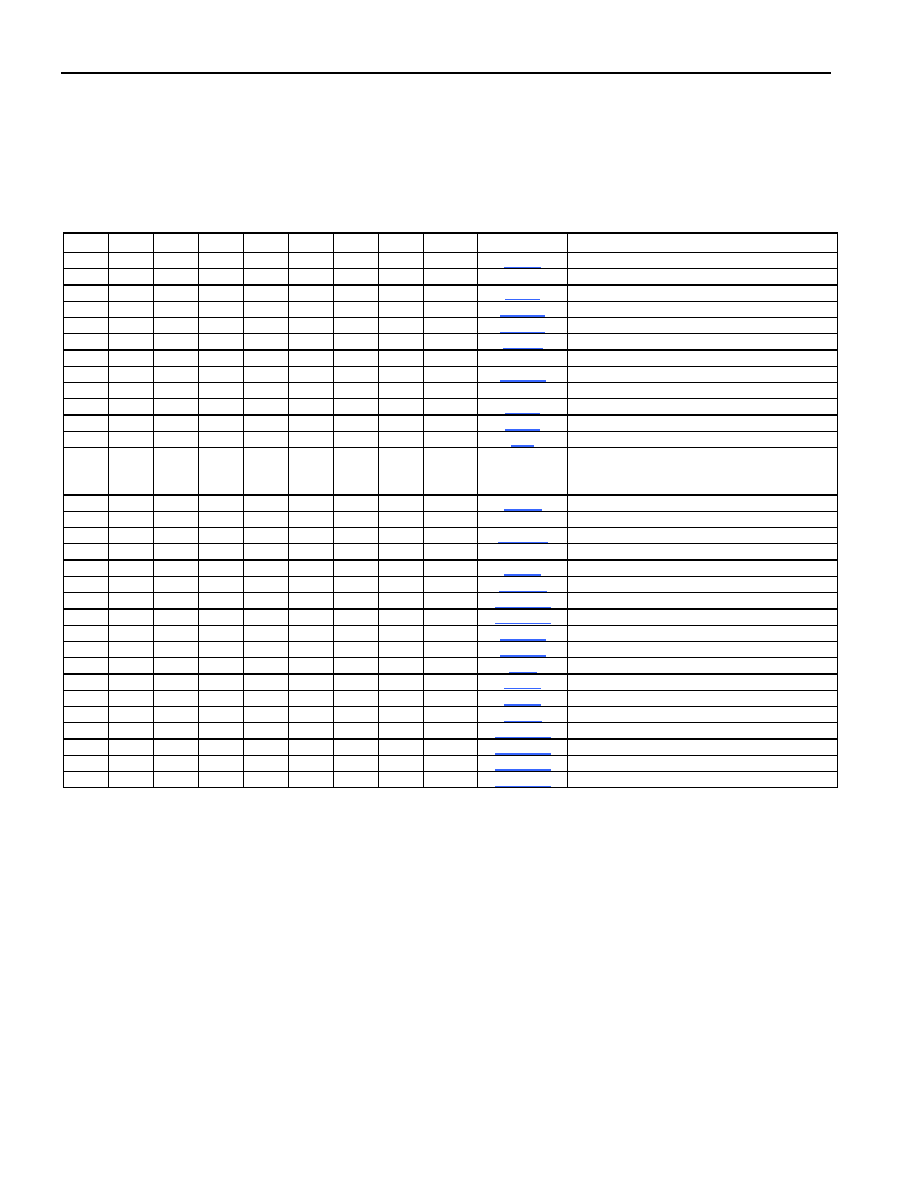

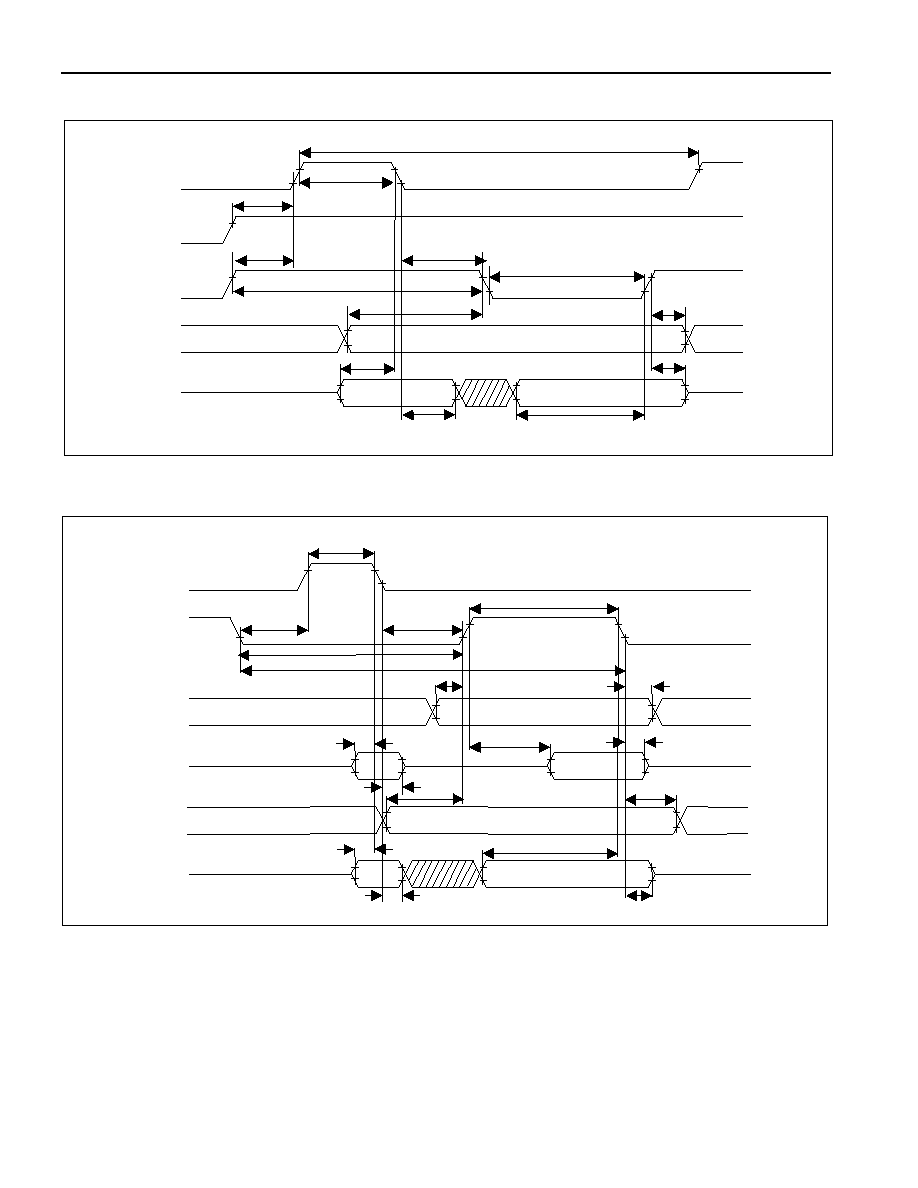

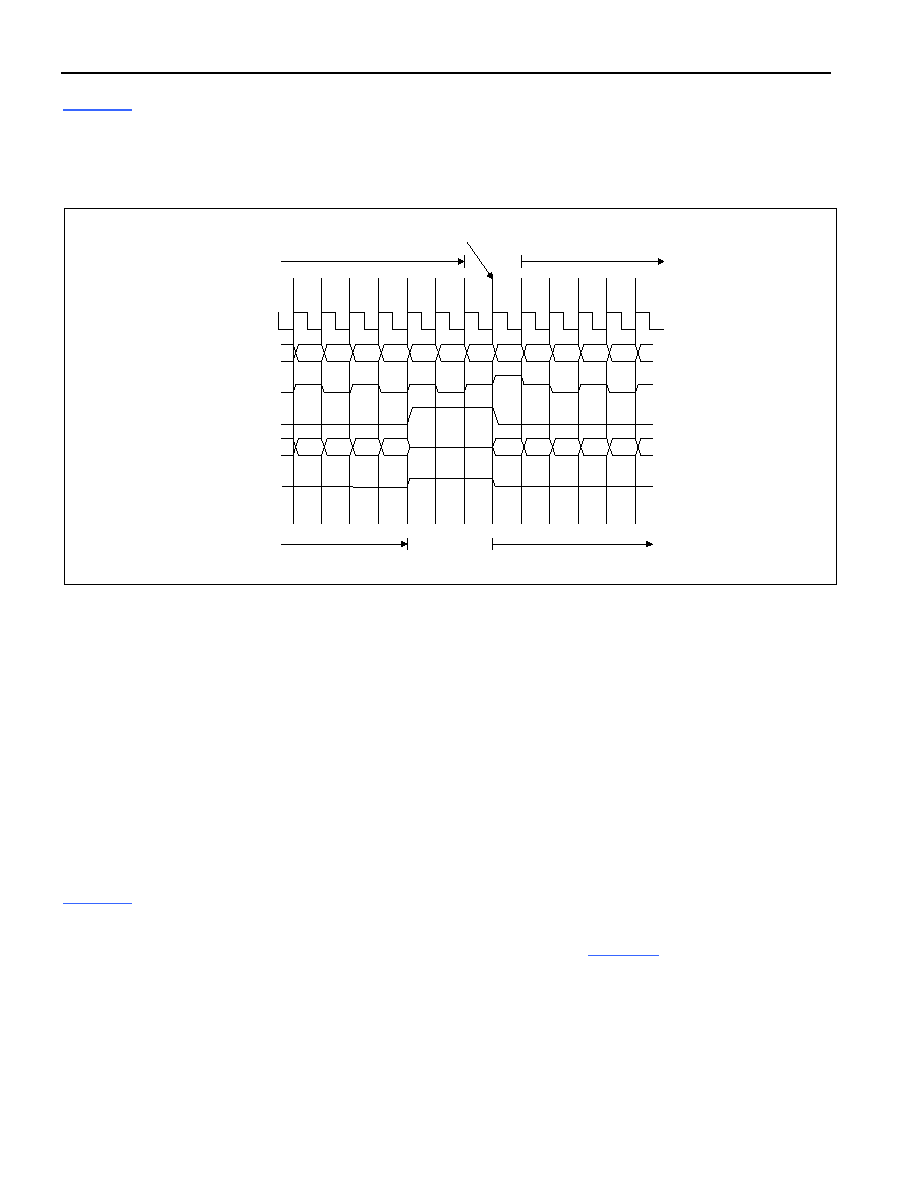

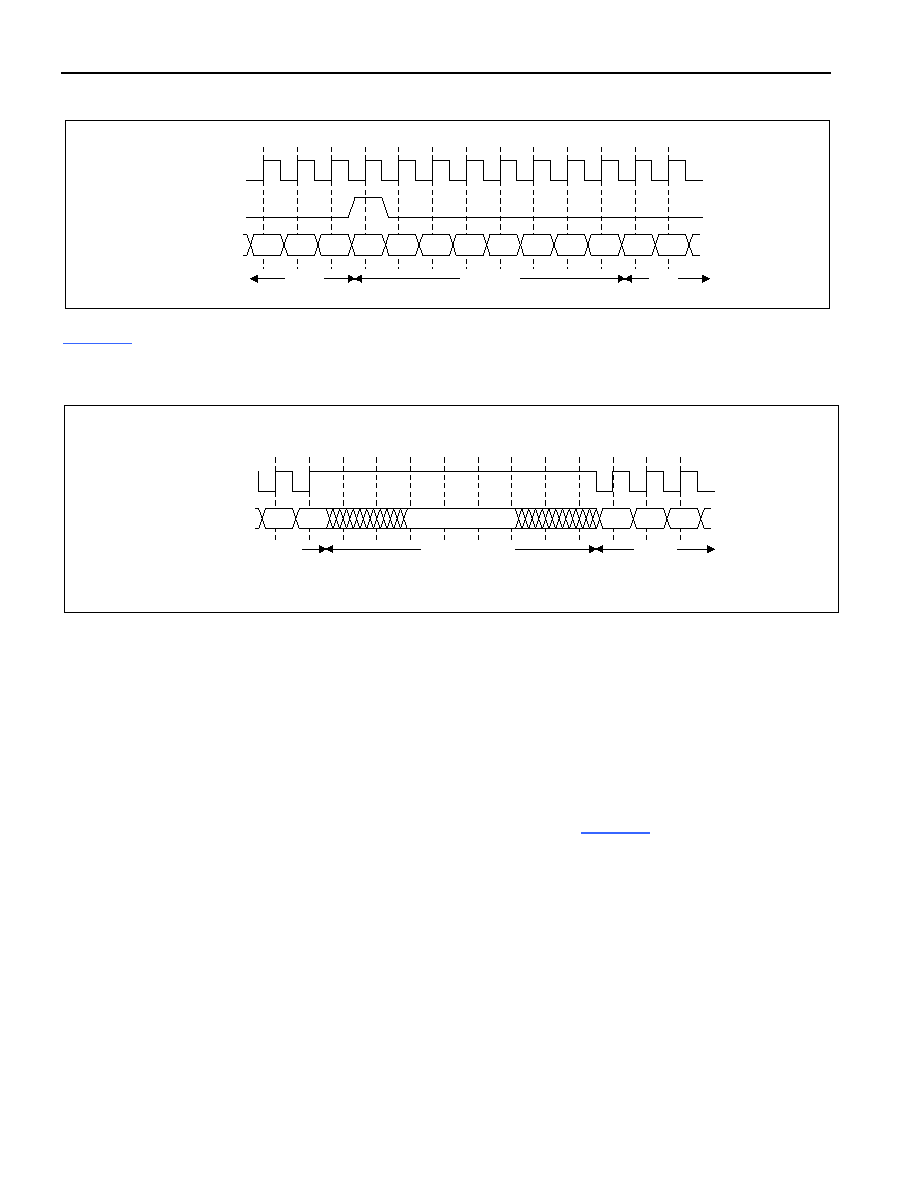

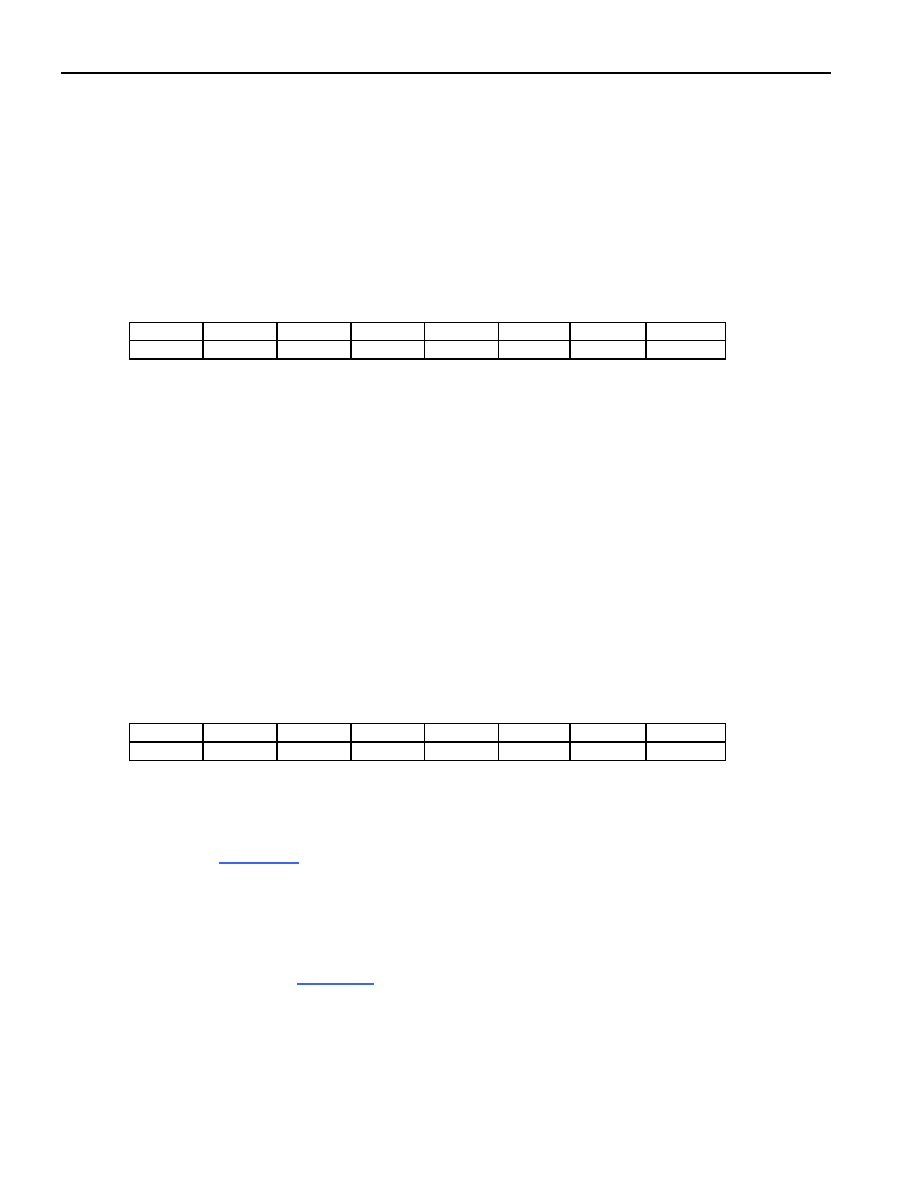

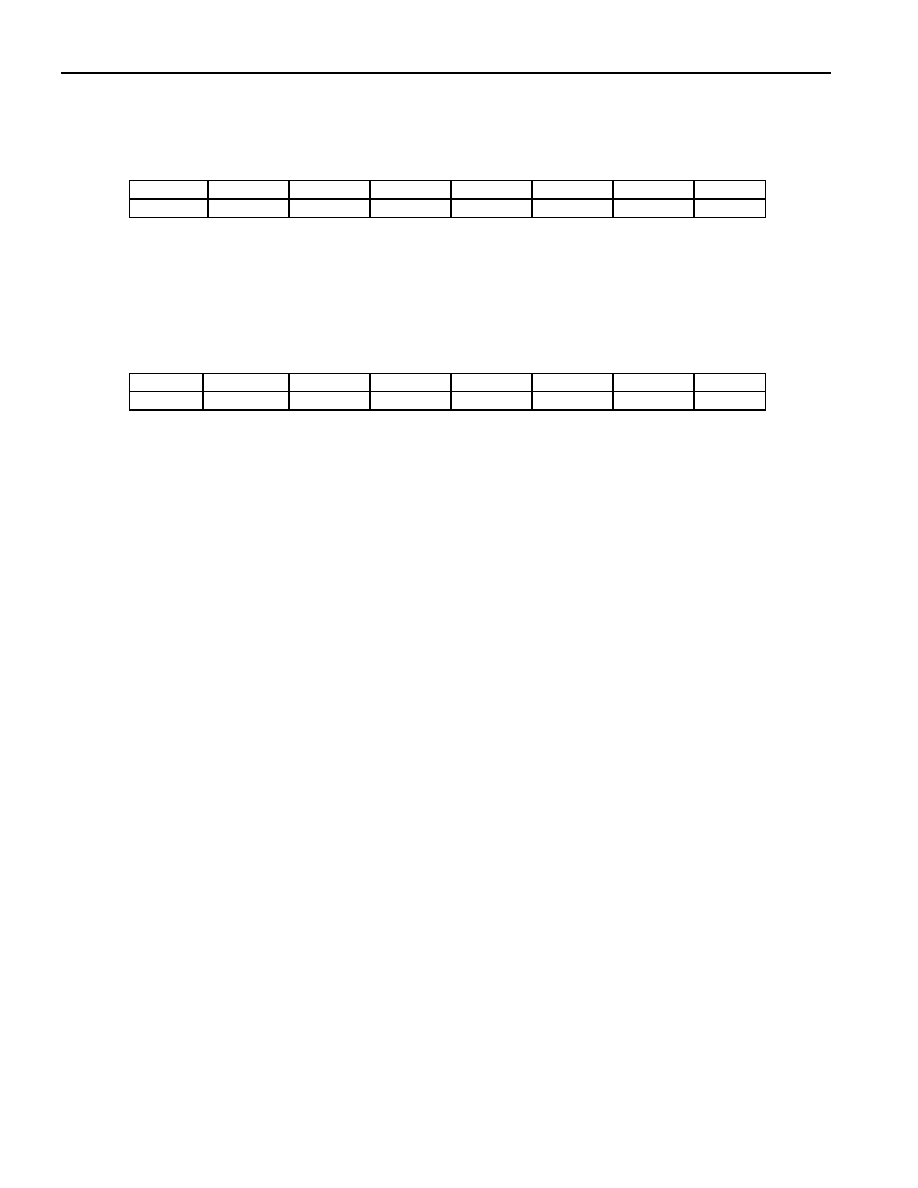

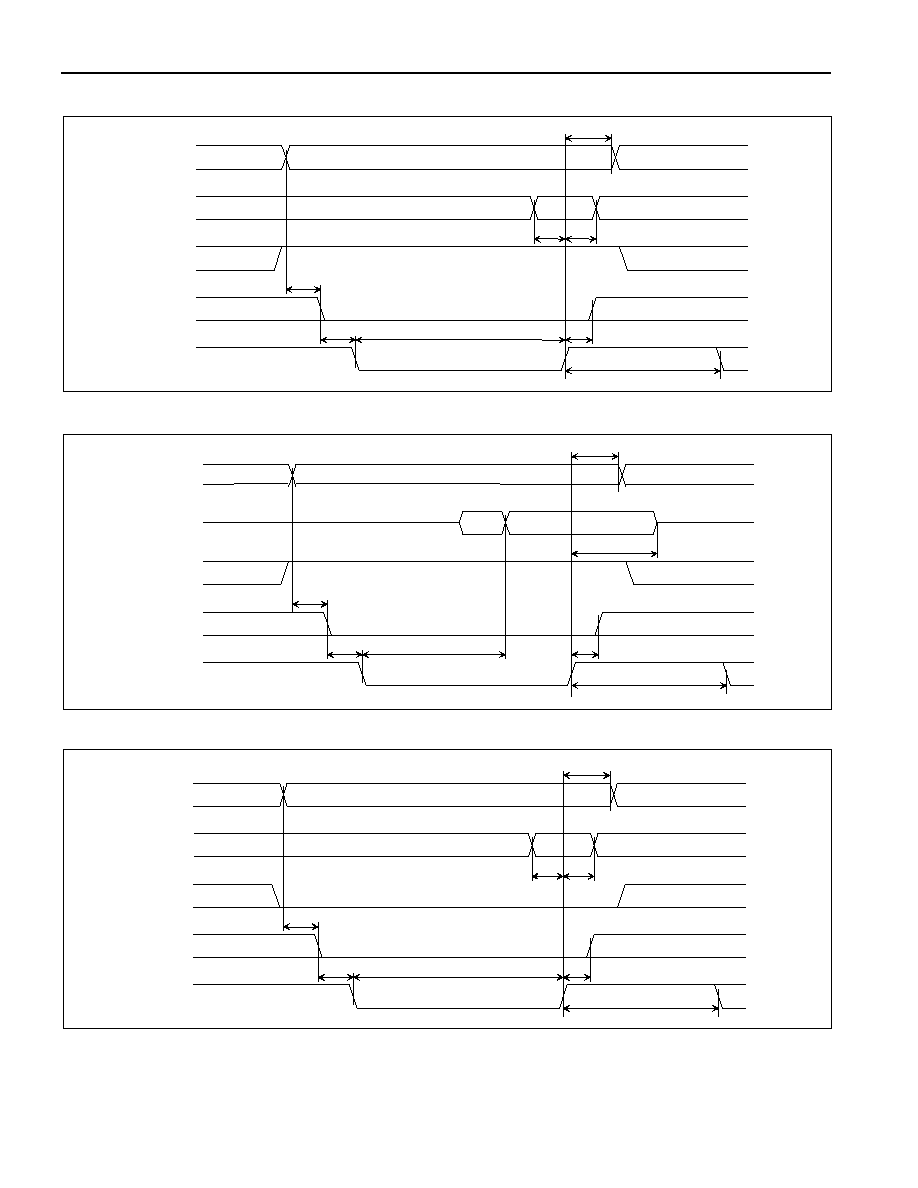

Figure 7-3

shows an example where the ATM must pause the data transmission, as it has no data available (in this

case, for three clock cycles). This is done by deasserting UT_ENB and (optionally) setting UT_DATA and UT_SOC

into high-impedance state. Polling may continue. In the last clock cycle, before restarting the transmission, the

address "M" of the previously selected PHY is put on the UT_ADDR bus to reselect PHY M again.

Figure 7-3. Transmission to PHY Paused for Three Cycles

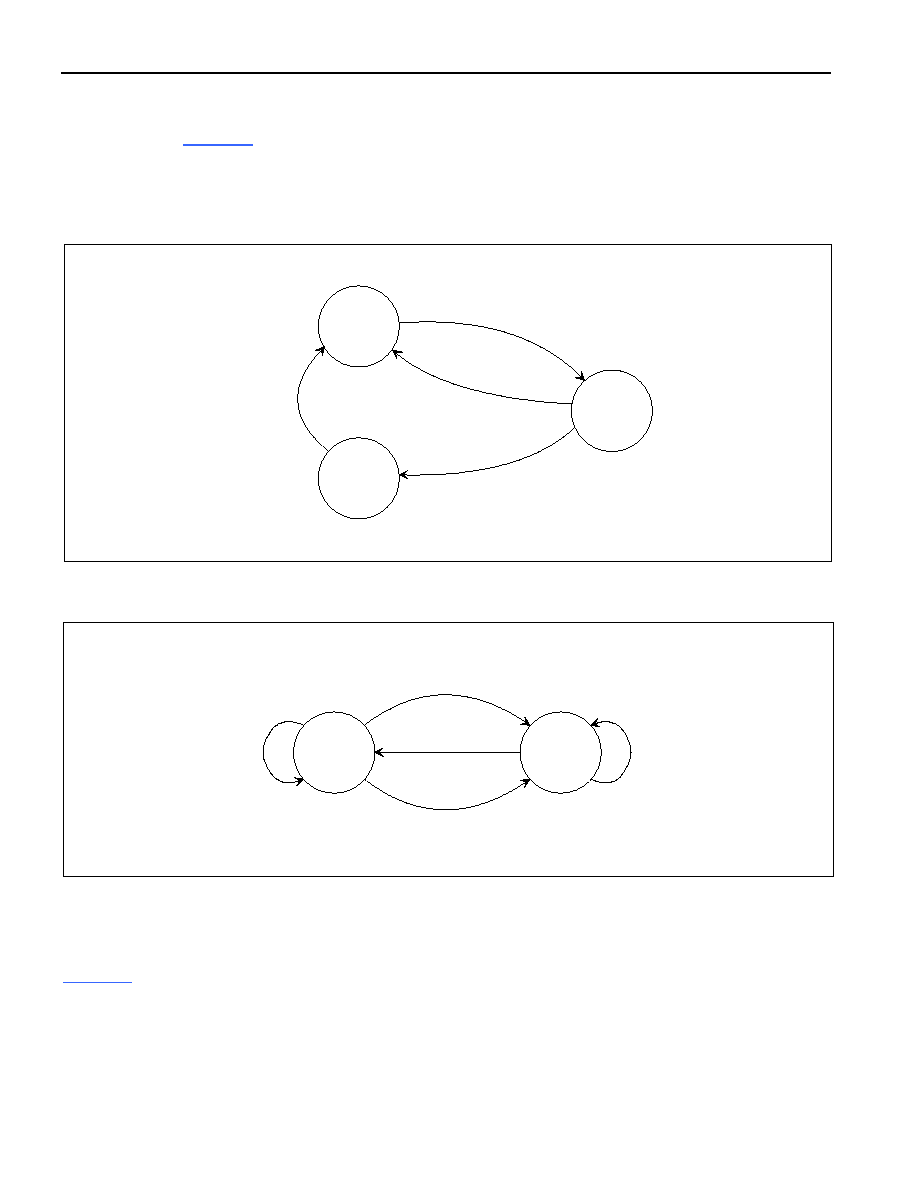

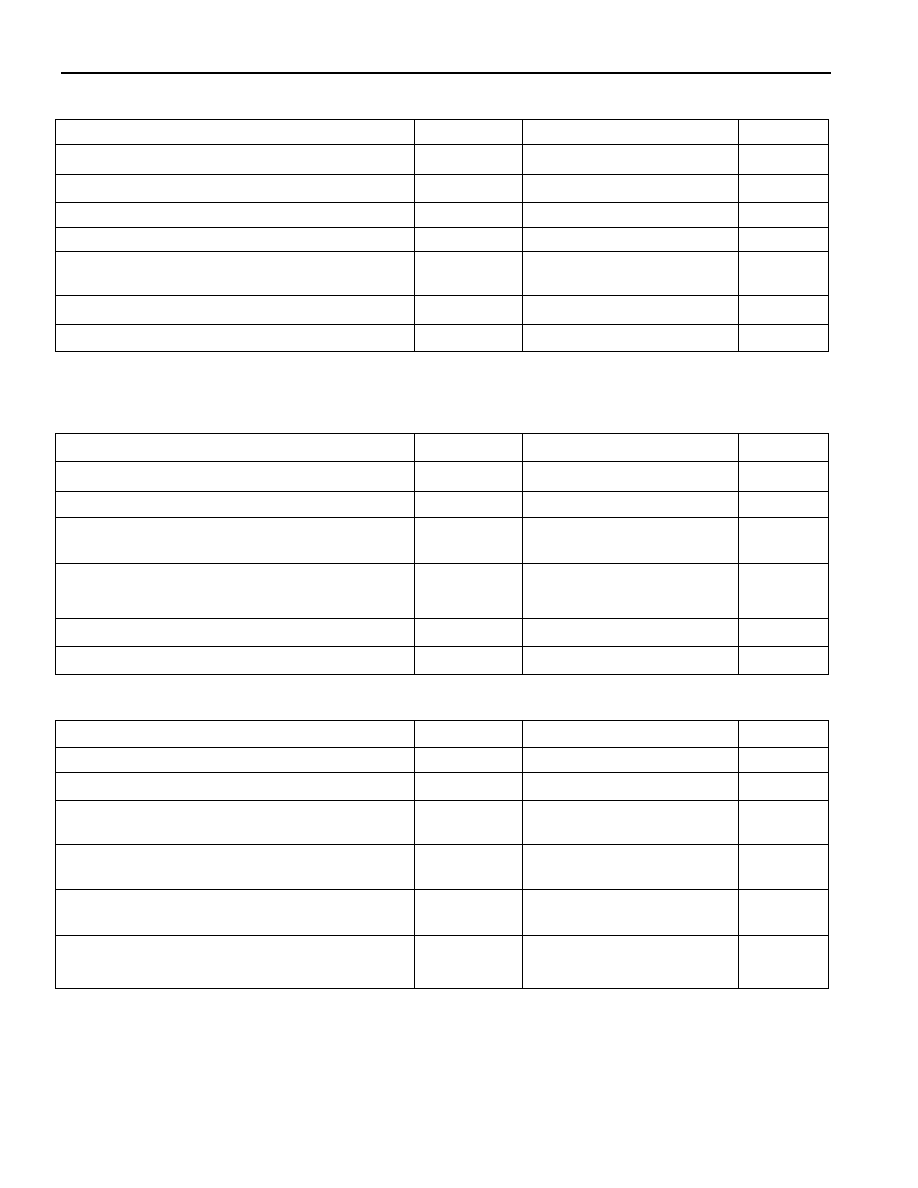

7.2 UTOPIA-Side Transmit--Direct Status Mode (MULTITXCLAV)

The DS26102 supports direct status mode per af-phy-0039.000 for a maximum of four PHY ports connected to one

ATM layer. For each PHY port, the status signals UR_CLAV and UT_CLAV are permanently available, according

to UTOPIA Level 1 specification. PHY devices with up to four on-chip PHY ports have up to four UR_CLAV and up

to four UT_CLAV status signals, one pair of UR_CLAV and UT_CLAV for each PHY port.

Status signals and cell transfers are independent of each other. No address information is needed to obtain status

information. Address information must be valid only for selecting a PHY port prior to one or multiple cell transfers.

With respect to the status signals UR_CLAV and UT_CLAV, this mode of operation corresponds to that of four

individual PHY devices, according to UTOPIA Level 1. With respect to the cell transfer, this mode of operation

corresponds to that as described in other parts of this document. The ATM layer selects a PHY port for cell transfer

by placing the desired port on the address lines (UR_ADDR[4:0], UT_ADDR[4:0]), while the enable signal

(

UR_ENB, UT_ENB) is deasserted. All PHY ports only examine the value on the address lines for possible selection

when the enable signal is deasserted. In case the ATM suspends transmission for a specific PHY port during a cell

transfer, no cells to/from other PHY ports can be transferred during this time.

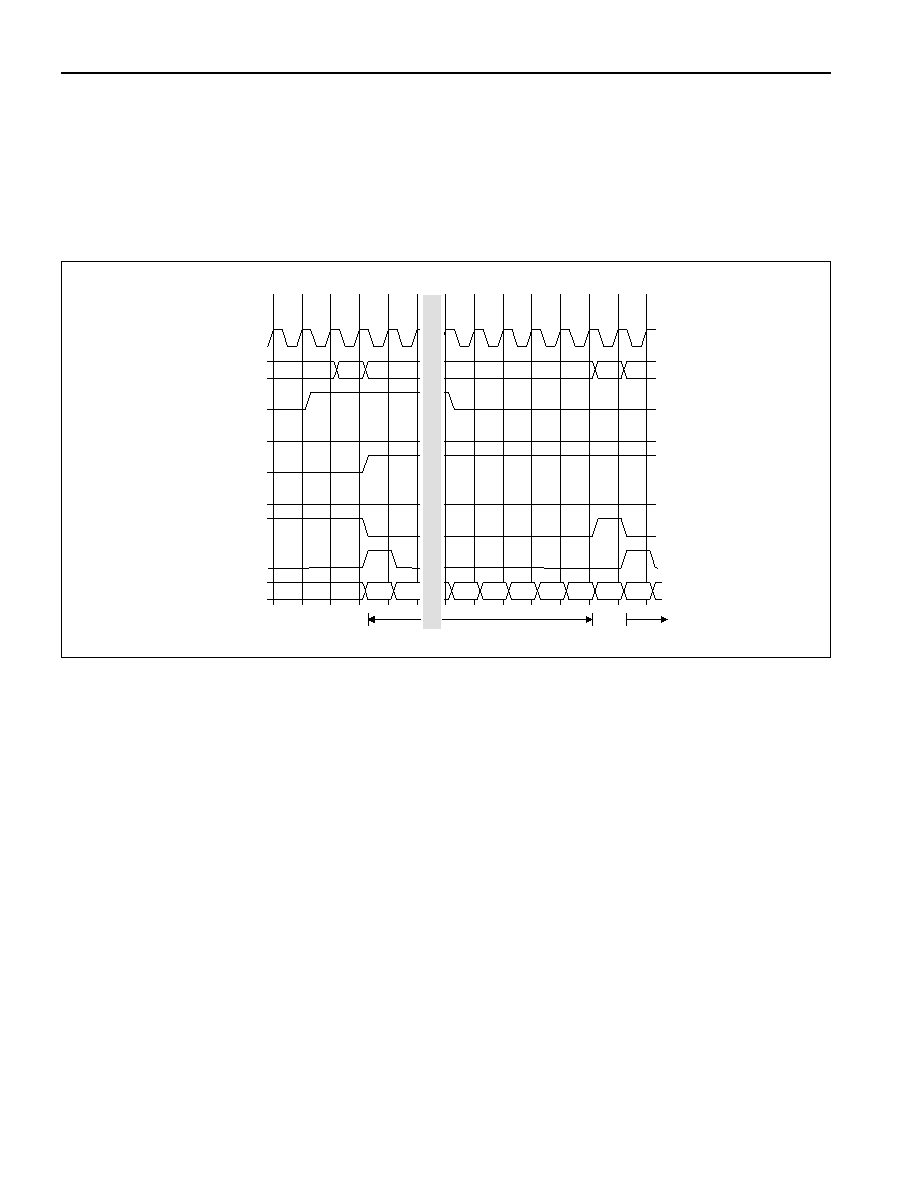

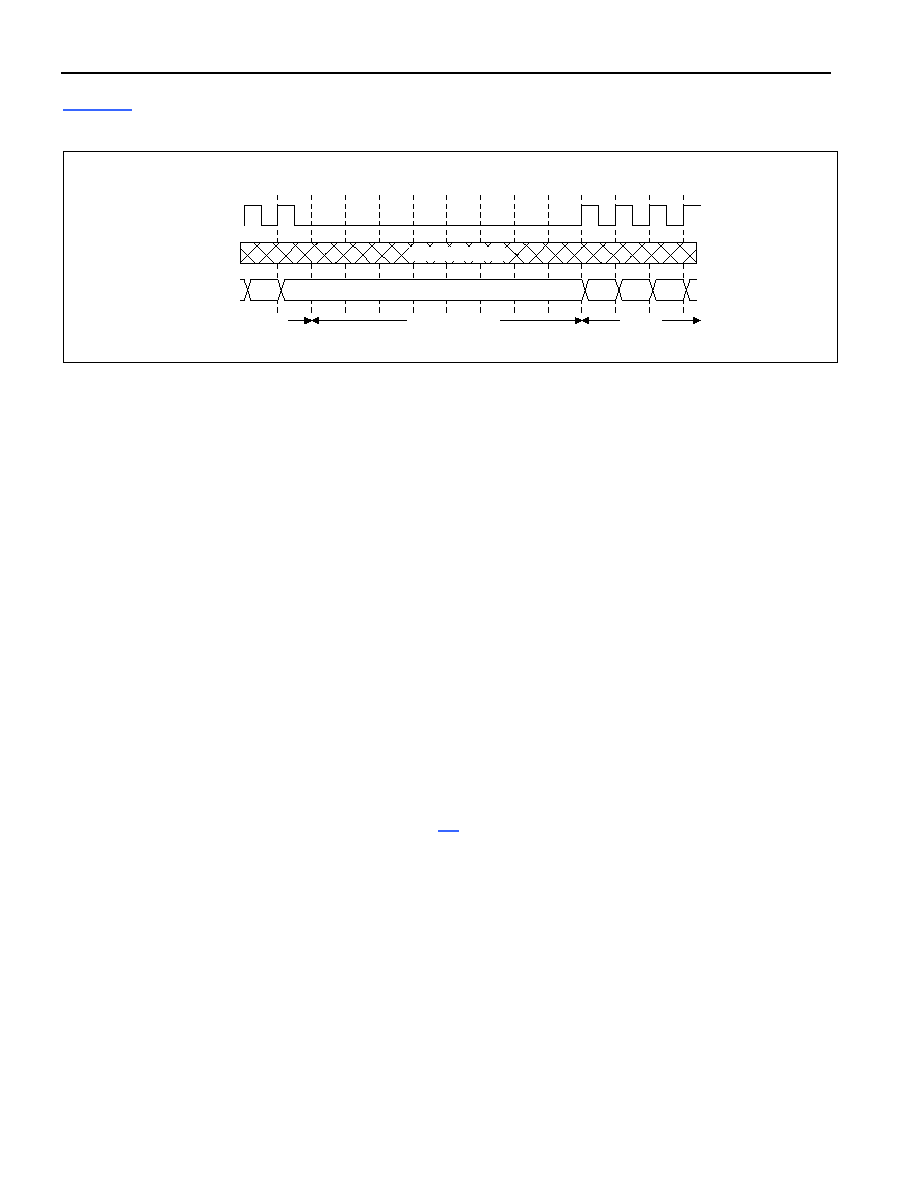

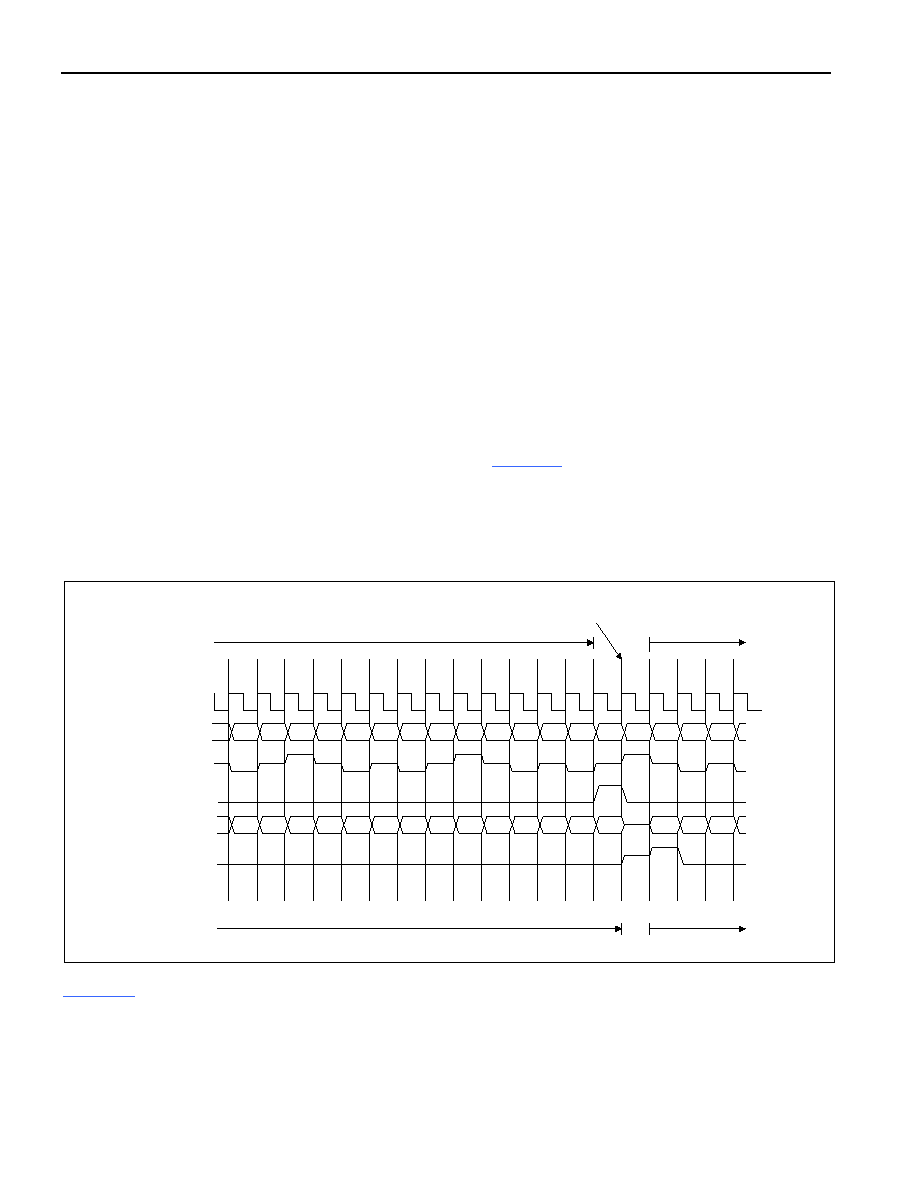

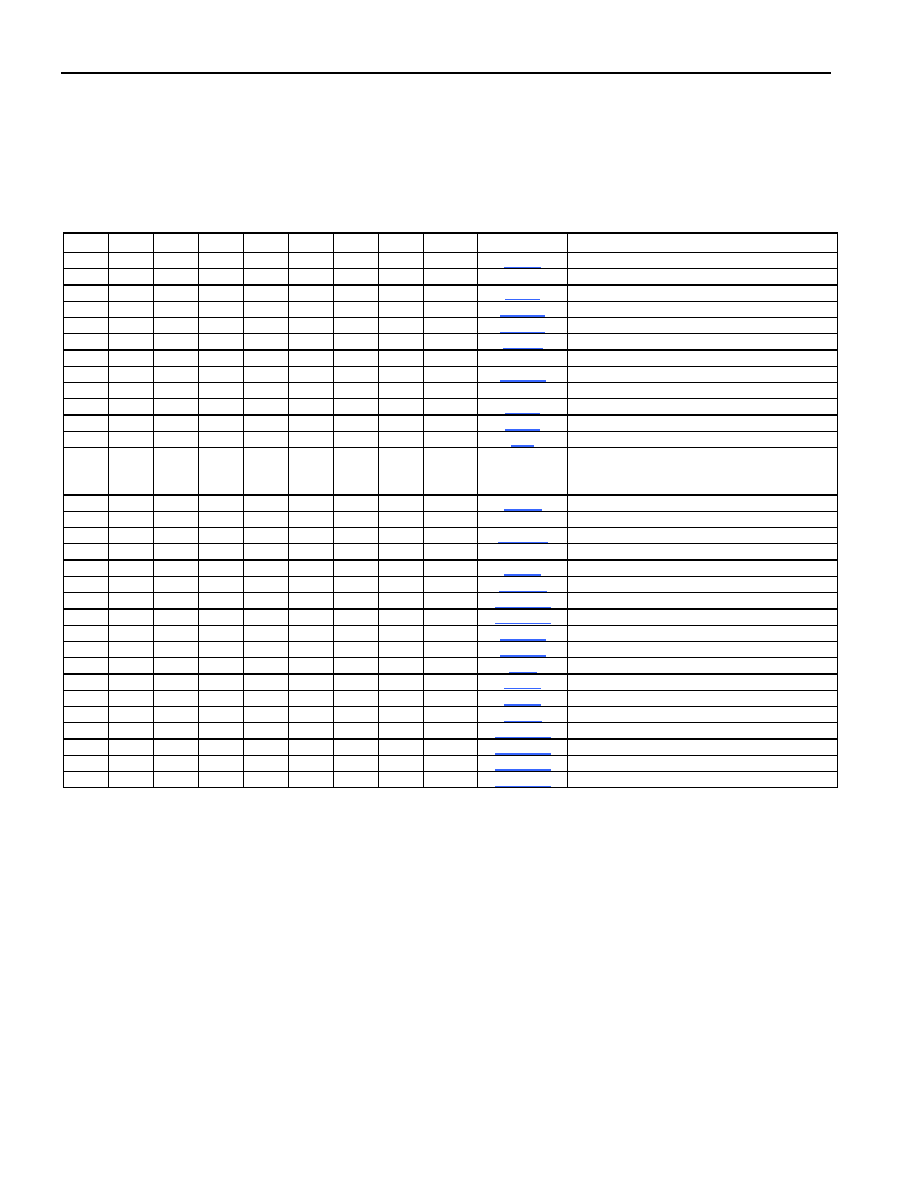

Figure 7-4

shows a direct status example for the transmit direction. Signals UT_CLAV[3:0] are associated with PHY

port addresses 4, 3, 2, and 1. There is no need for a unique null device, therefore, "X = don't care" represents any

address between 0 and 31 on the address lines UT_ADDR[4:0] or any data on the data bus. In this mode, the

DS26102 supports address

ranges 0 to 3, 8 to 11, 16 to 19, or 24 to 27. In

Figure 7-4

the polling of PHY ports

starts while no cell transfer takes place. The ATM layer has pending cells for all four PHY ports (one individual

queue for each PHY port), but all four PHY ports cannot accept a cell. With rising clock edge 2, PHY port 1

indicates that it can accept a complete cell (UT_CLAV0 asserted). The ATM layer detects this at clock edge 3. It

selects that PHY port by placing address 1 on the address lines with rising clock edge 3. PHY port 1 detects this at

clock edge 4. At clock edge 5, PHY port 1 detects UT_ENB asserted, thus cell transfer for PHY port 1 starts with

rising clock edge 5 (byte H1).

N

1F

N+1

1F

N-4

1F

M

1F

N+2

N+3

1F

1F

N

N+1

N-4

M

N+2

N+3

P31

P32

P33 P34

P35 P36

P38 P39

P37

1

2

3

4

5

6

7

8

9

10

11

12

13

UT_CLK

UT_ADDR[4:0]

UT_CLAV[0]

UT_ENB

UT_DATA[7:0]

UT_SOC

CELL XMIT TO:

PHY M

POLLING

PHY M

PAUSE

XMIT

POLLING

SELECTION

DS26102 16-Port TDM-to-ATM PHY

20 of 64

At clock edge 5, the ATM layer detects a cell available at PHY port 3 (UT_CLAV2 asserted). With rising clock edge

52, PHY port 1 indicates that it cannot accept an additional cell by deasserting UT_CLAV0. Thus, at clock edge 57,

the ATM layer detects only UT_CLAV2 asserted (UT_CLAV1 and UT_CLAV3 remain deasserted). The ATM layer

deselects PHY port 1 and selects PHY port 3 for cell transfer with rising clock edge 57 by placing address 3 on the

address lines and deasserting UT_ENB. PHY port 1 and PHY port 3 detect this at clock edge 58. At clock edge 59,

PHY port 3 detects

UT_ENB asserted, thus cell transfer for PHY port 3 starts with rising clock edge 59 (byte H1).

For additional examples, refer to ATM Forum document af-phy-0039.000.

Figure 7-4. Example of Direct Status Indication, Transmit Direction

7.3 Transmit

Processing

The DS26102 can insert a valid HEC byte in the cell header, or it can be programmed to transparently transmit the

HEC byte from ATM layer. When inserting a valid HEC byte, COSET (0x55) addition can be disabled. The

generator polynomial used is 1 + X + X

2

+ X

8

. For idle/unassigned cell insertion (used for cell-rate decoupling), the

DS26102 inserts a valid HEC byte with or without COSET addition, depending on the TCRDS (TCR1.3)

microprocessor register bit. The DS26102 can scramble payload bytes, depending on the TPSE (TCR1.4) register

bit. The polynomial used for scrambling is X

43

+ 1. For debugging purposes, the DS26102 can be configured to

introduce a single-bit HEC error in the cell header of transmitted cells. When configured in HEC error-insertion

mode, the DS26102 inserts HEC errors in "HEC on period" number of cells and turns off HEC error insertion for

"HEC off period" number of cells, as set in the transmit HEC error-pattern register (THEPR). This process repeats

periodically until HEC error insertion is disabled through the THEIE bit (TCR1.1).

N-4

1

2

3

4

5

6

53

54

55

56

57

58

UT_CLK

UT_ADDR[4:0]

UT_CLAV0

UT_ENB

UT_SOC

59

H1

P45 P46

P48

X

P47

UT_DATA[7:0]

X

1

X

X = Don't Care

3

X

UT_CLAV1

UT_CLAV2

UT_CLAV3

PORT 1

PORT 2

PORT 3

PORT 4

H2

X

P44

H1

Port 1 Transfer

Port 3

52

DS26102 16-Port TDM-to-ATM PHY

21 of 64

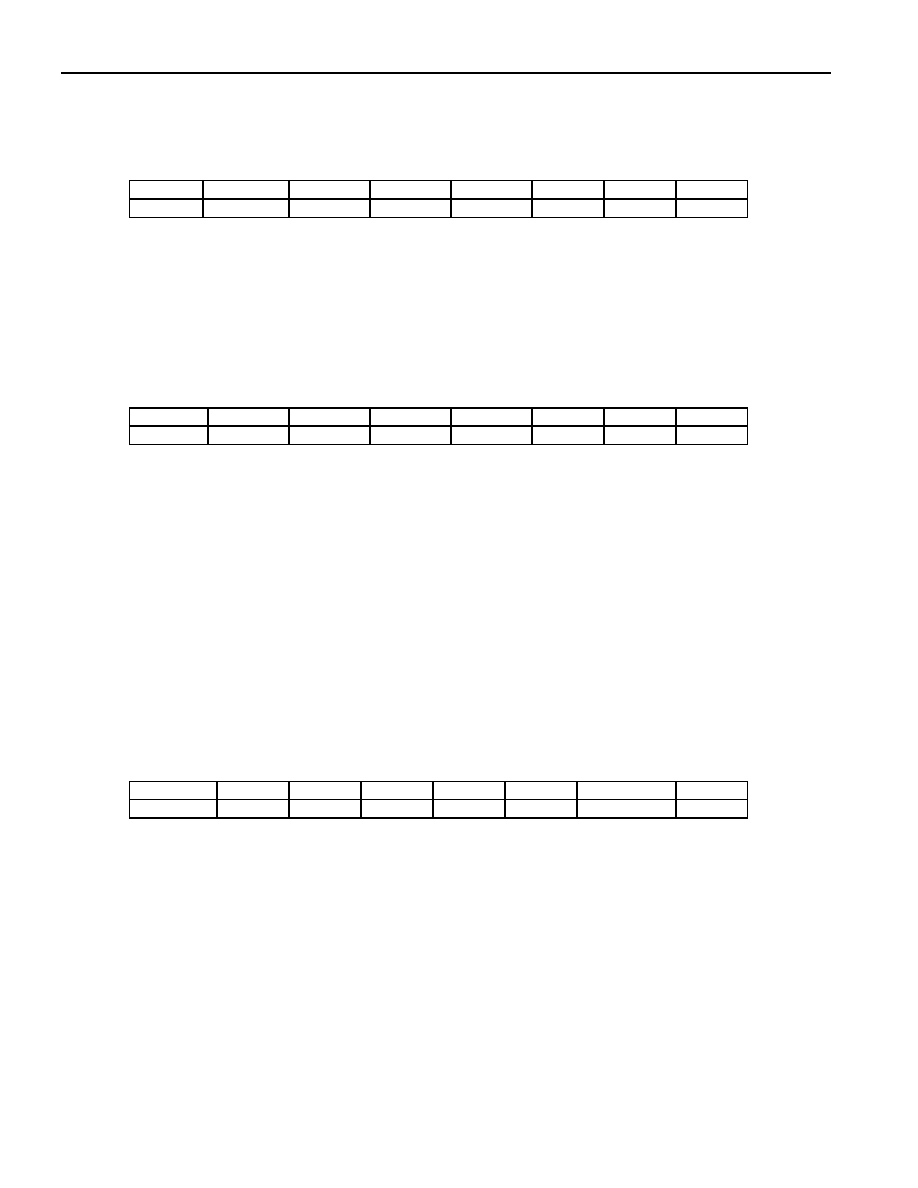

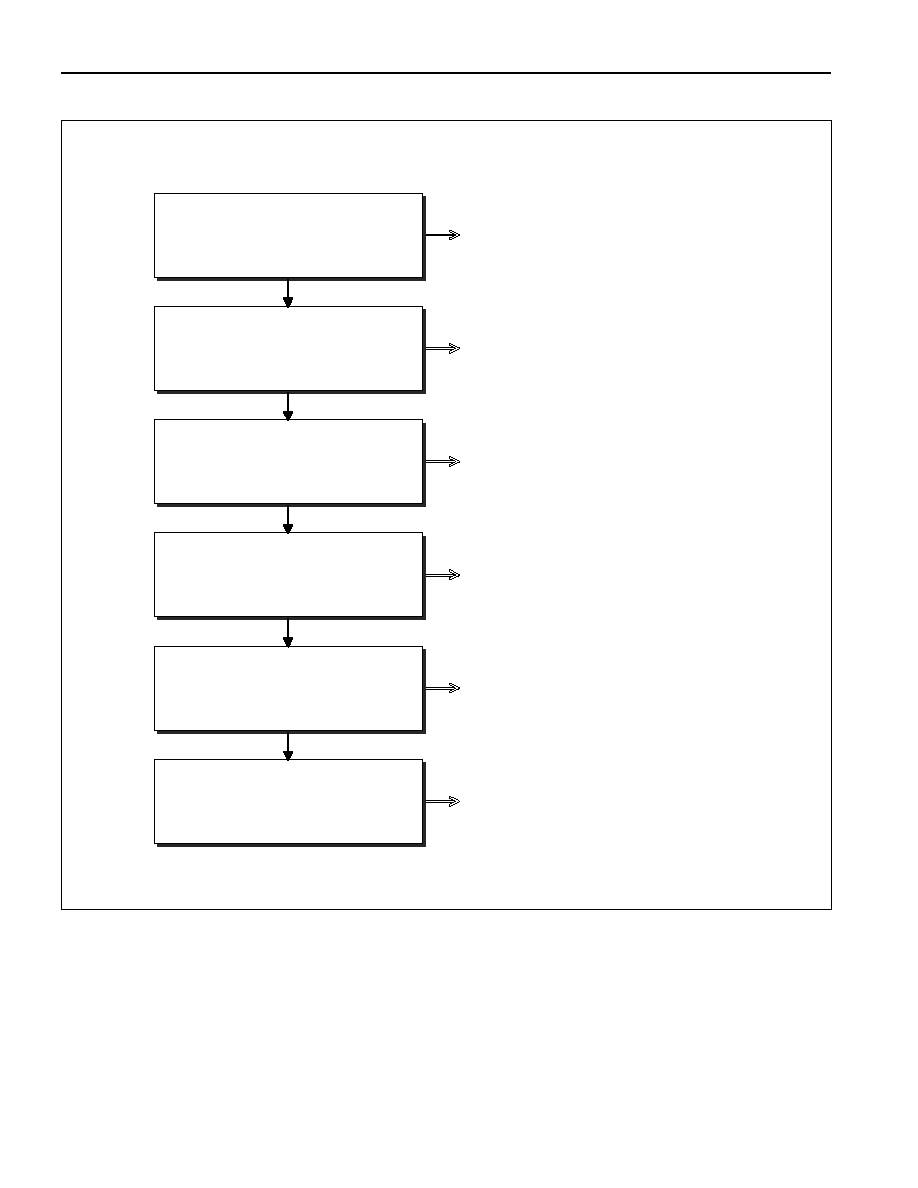

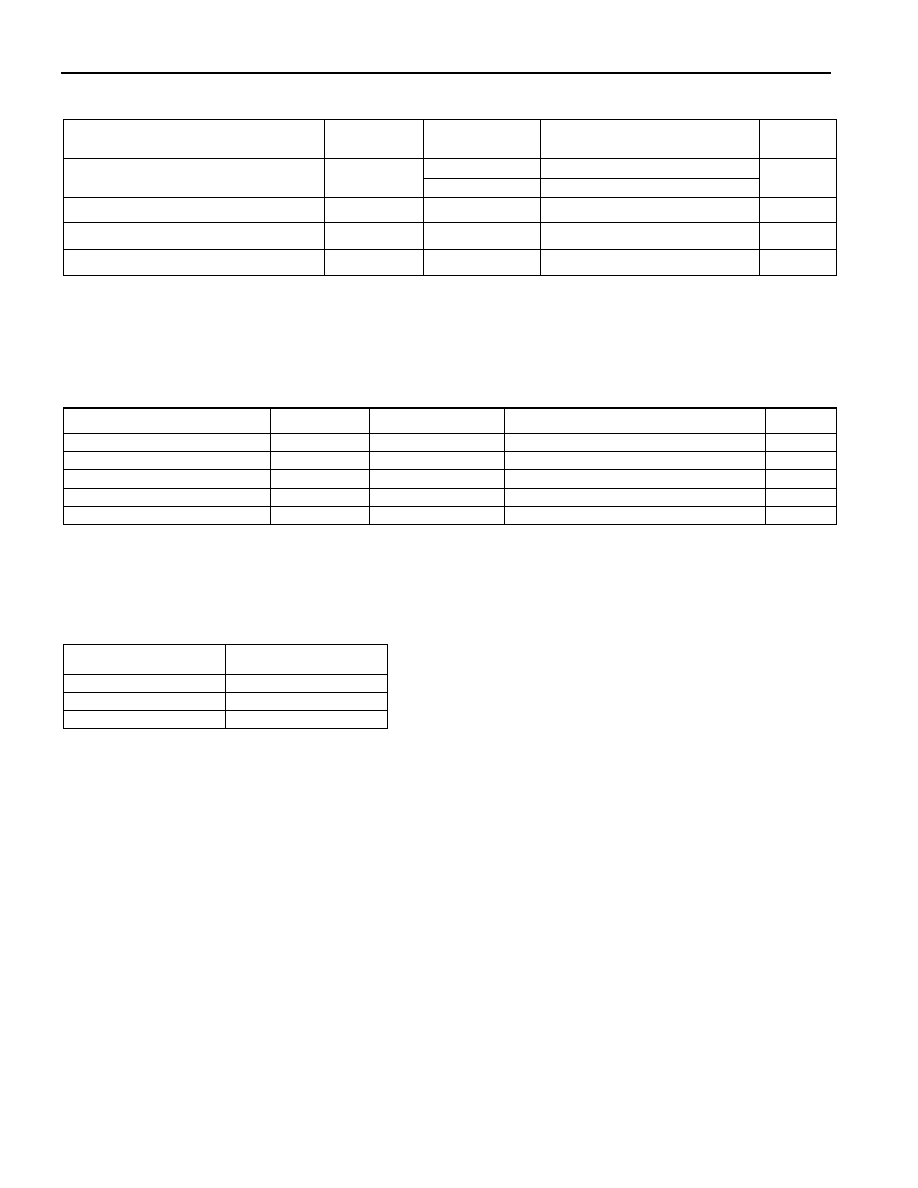

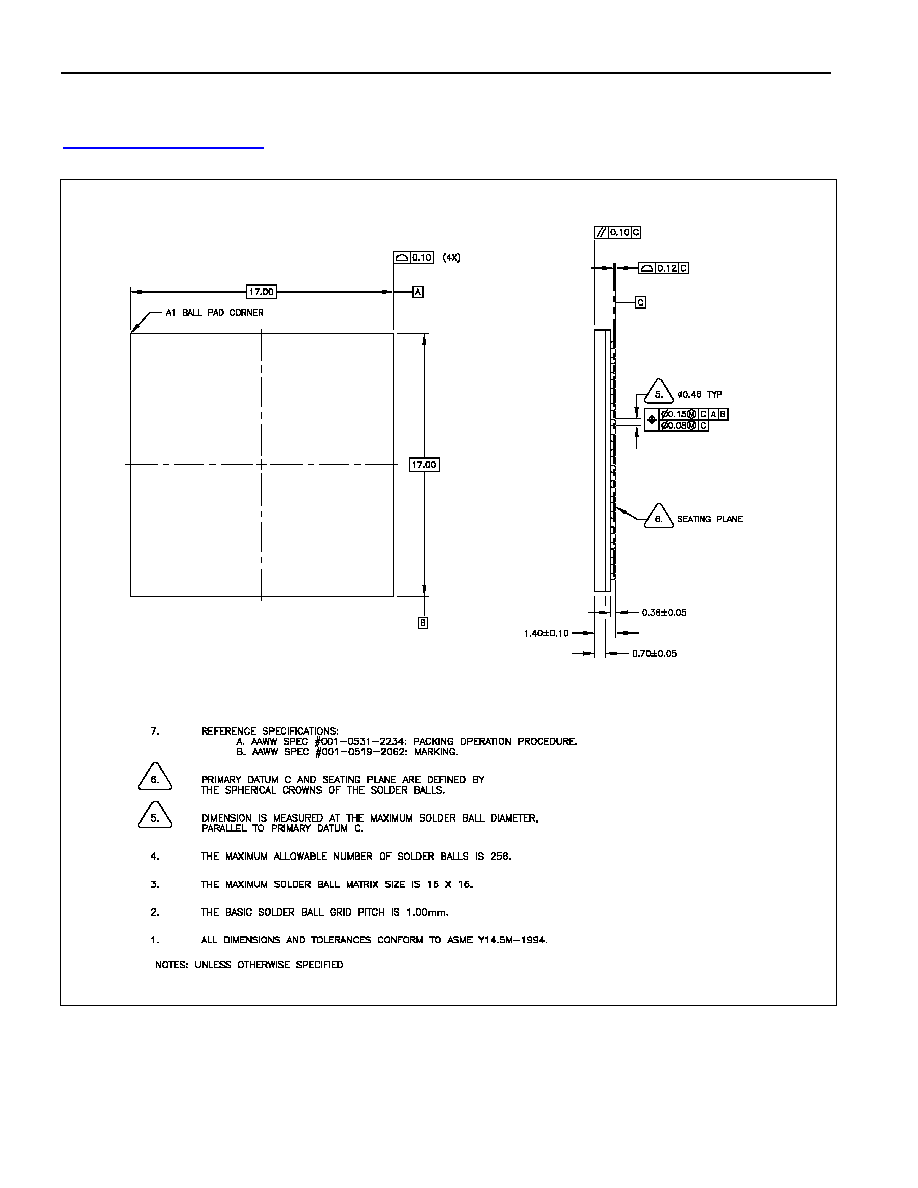

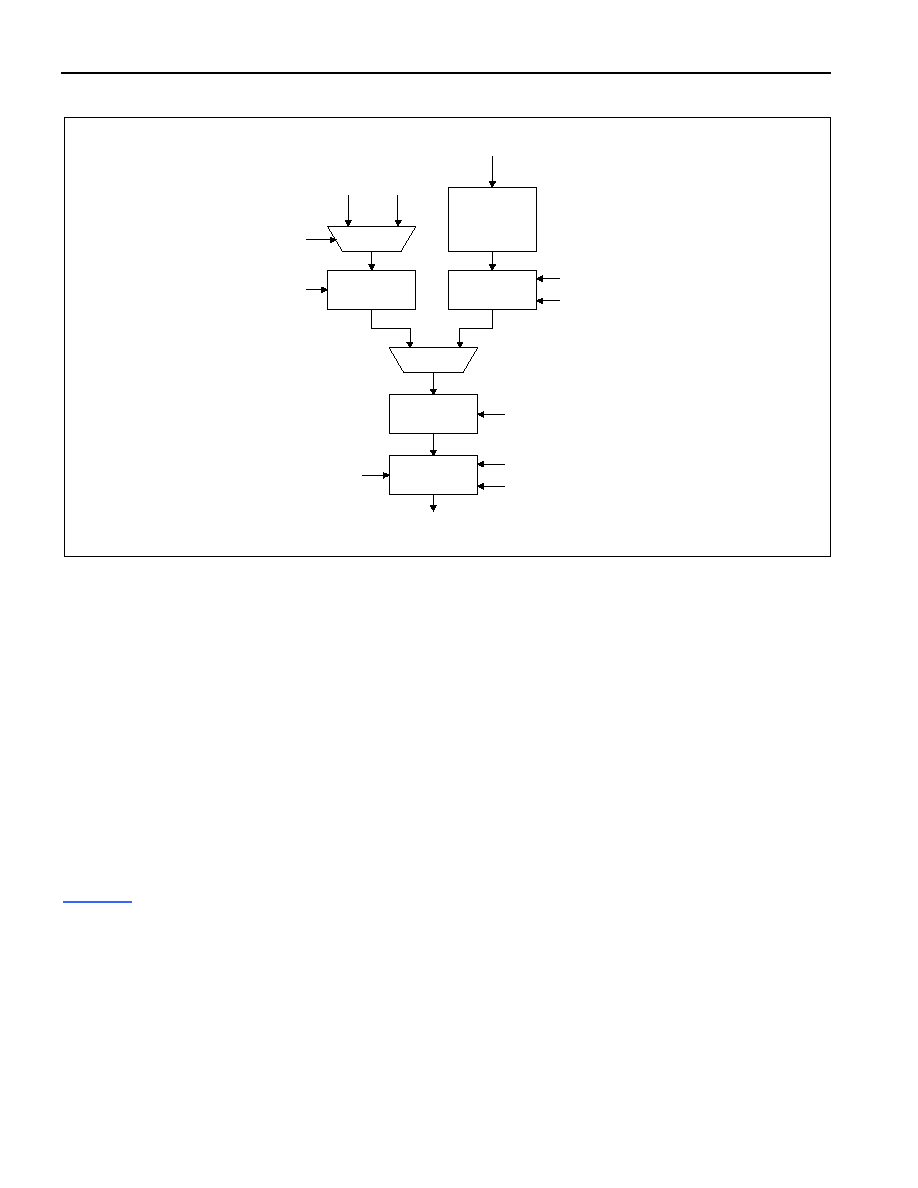

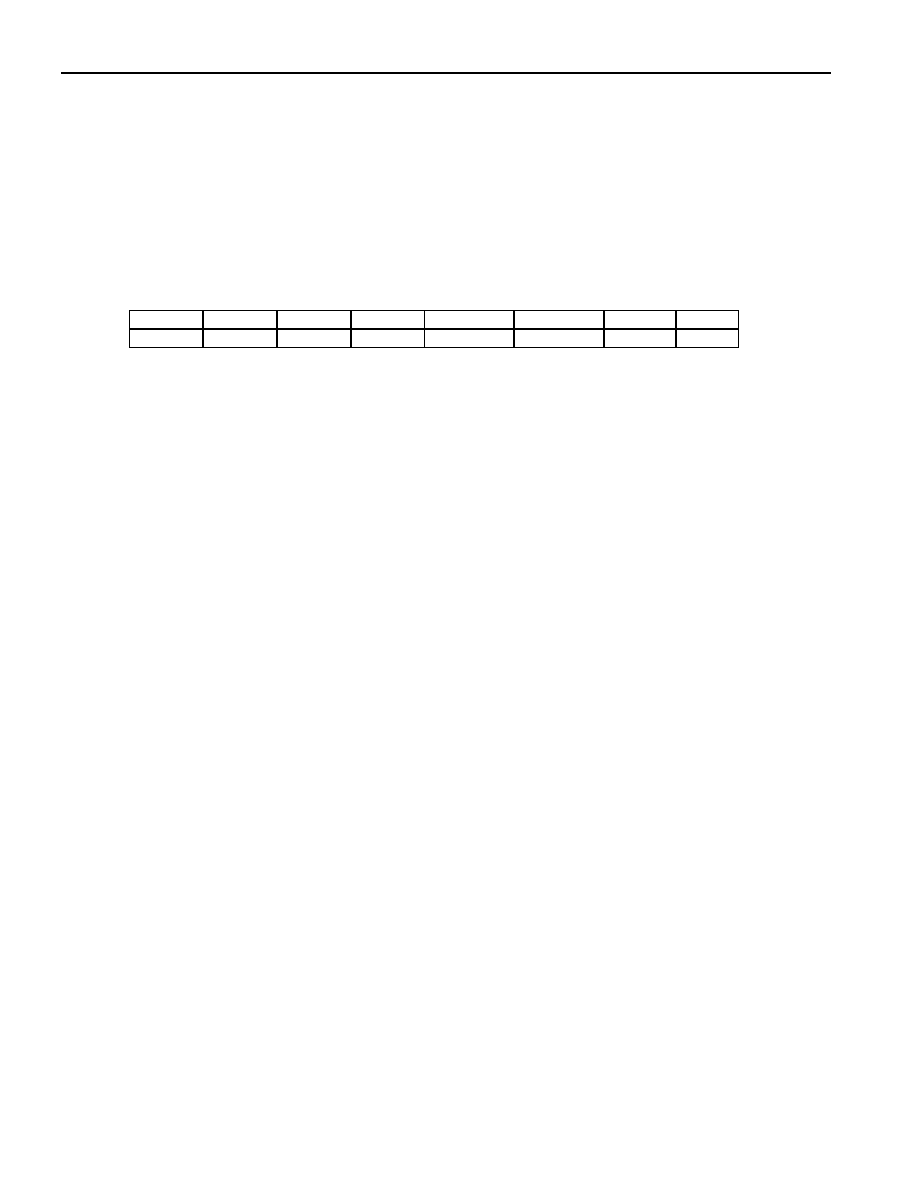

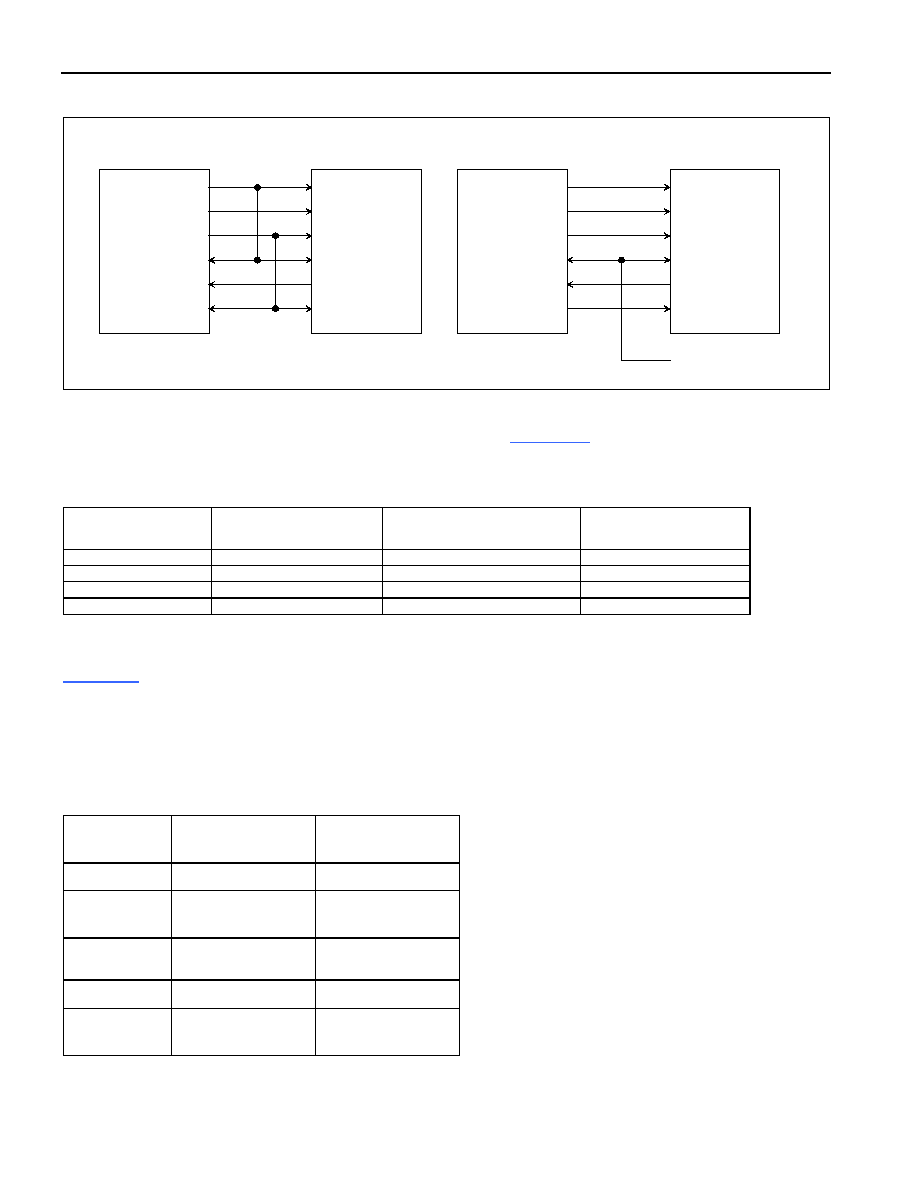

Figure 7-5. Transmit Cell Flow and Processing

7.4 Physical-Side Transmit

The transmit framer interface operates in one of two modes:

1)

Gapped clock + data

2)

Clock + data + frame-pulse indication

The mode can be selected on a per-port basis by the TPLIM control bit (TCR2.1). If configured in frame-pulse-

indication mode, valid data bits are not sent during frame-pulse positions in the case of T1 and during TS0 and

TS16 positions in case of E1 direct mapping. The TS0 and TS16 locations are identified from the frame-pulse

indication signal aligned with bit 0 of the E1 frame. The TPC (TCFR.0) bit determines T1 or E1 configuration. ATM

cell octets are byte-aligned with respect to the frame-pulse-indication signal. In clear E1 mode, valid data bits are

transmitted at every clock tick. The DS26102 can either output the frame-pulse signal or use it as an input as

controlled through TFSD (TCR2.0).

The active edge of the transmit clock can be selected through the TAES control bit (TCR2.2). The active edge used

by the transmit interface should be configured to the opposite edge of that used by the external framer.

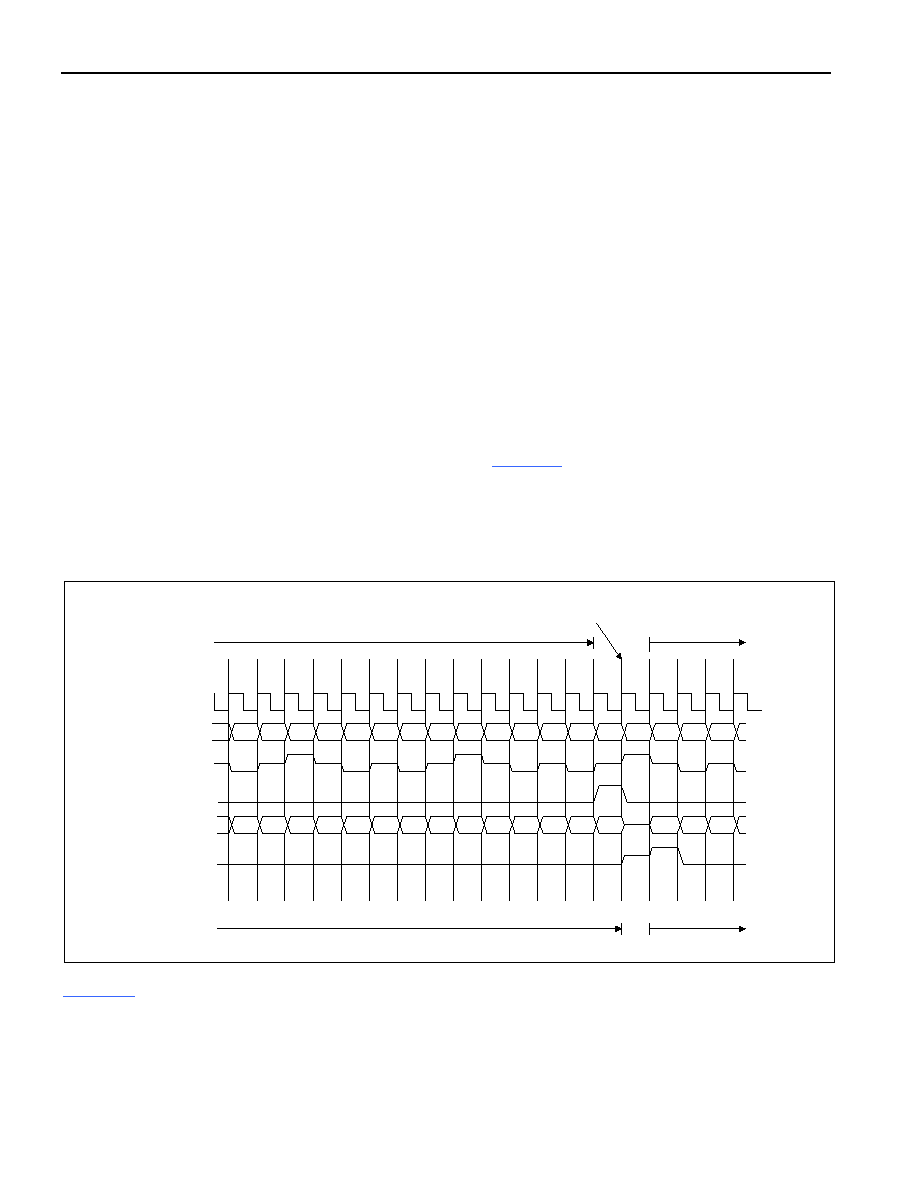

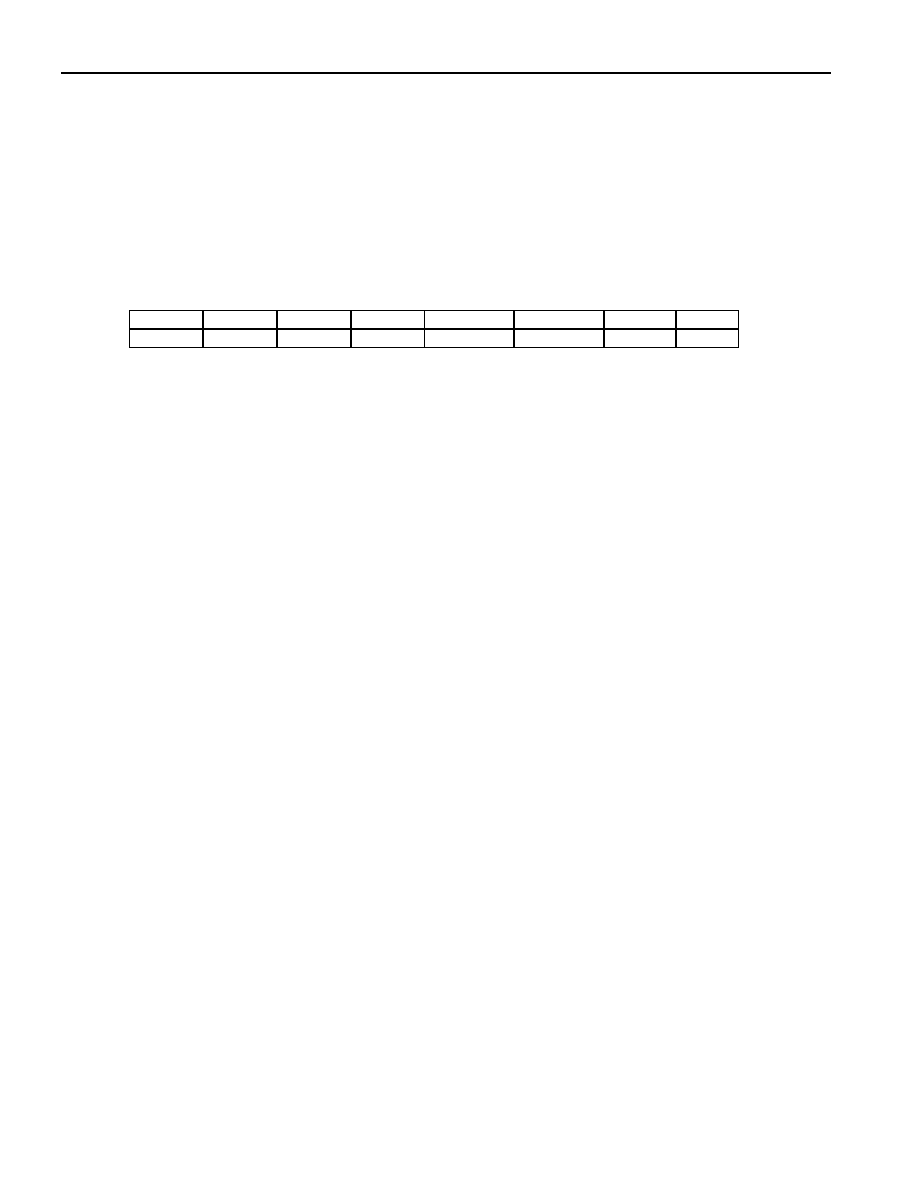

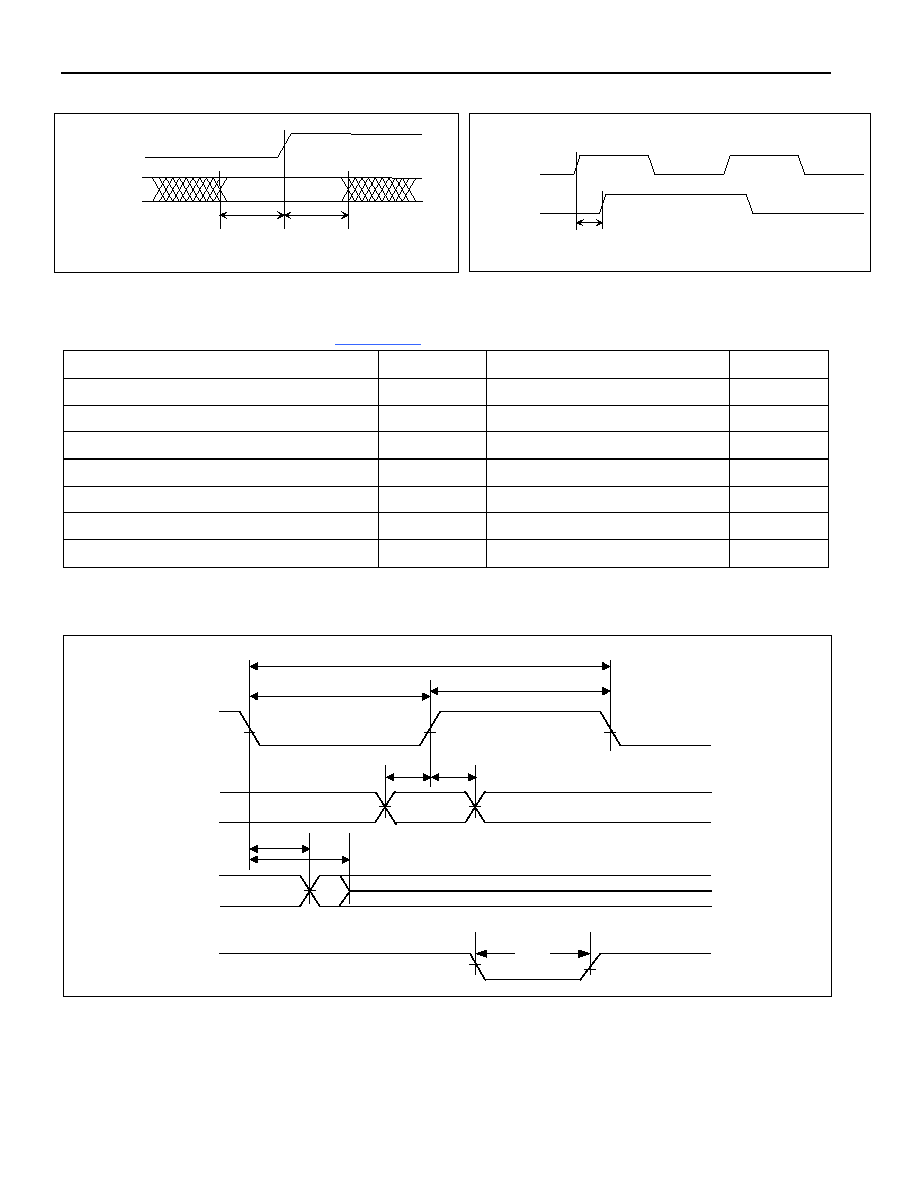

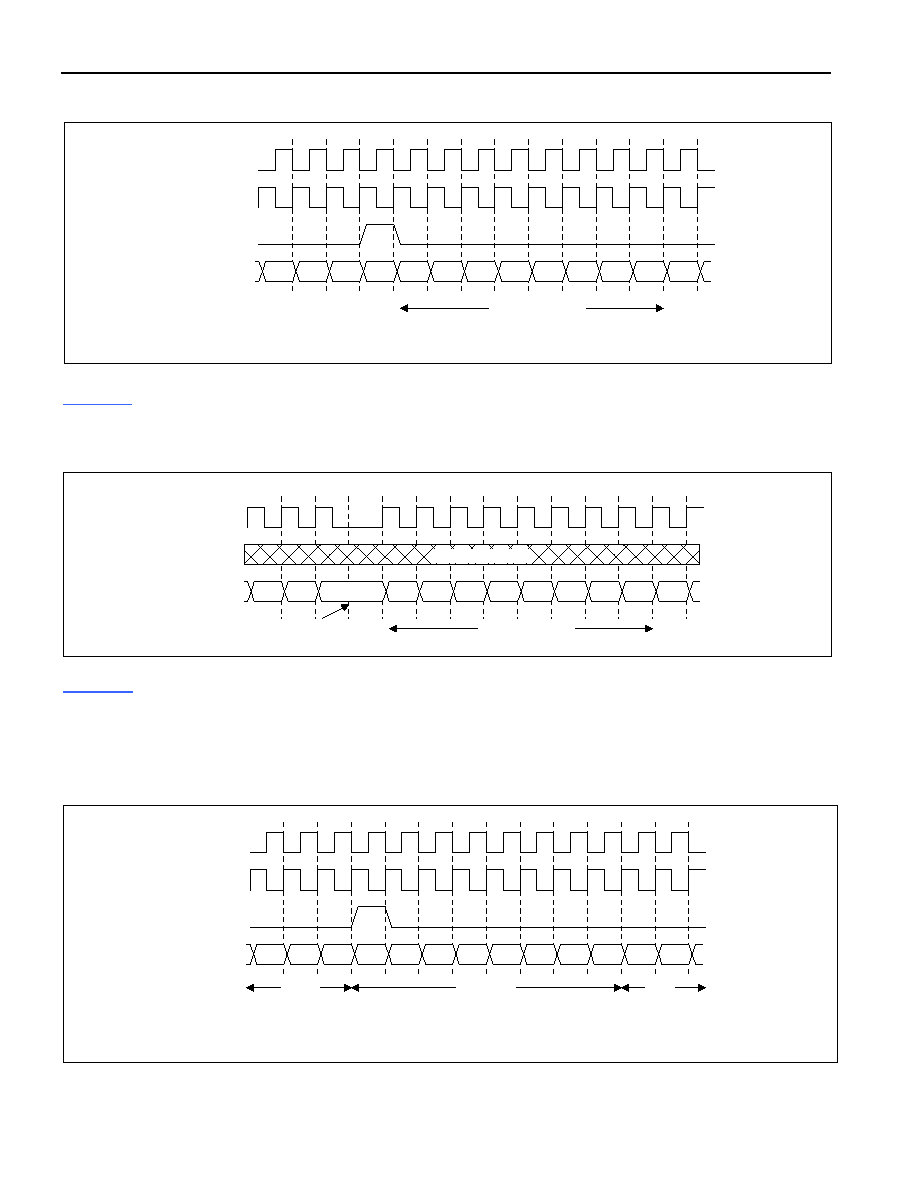

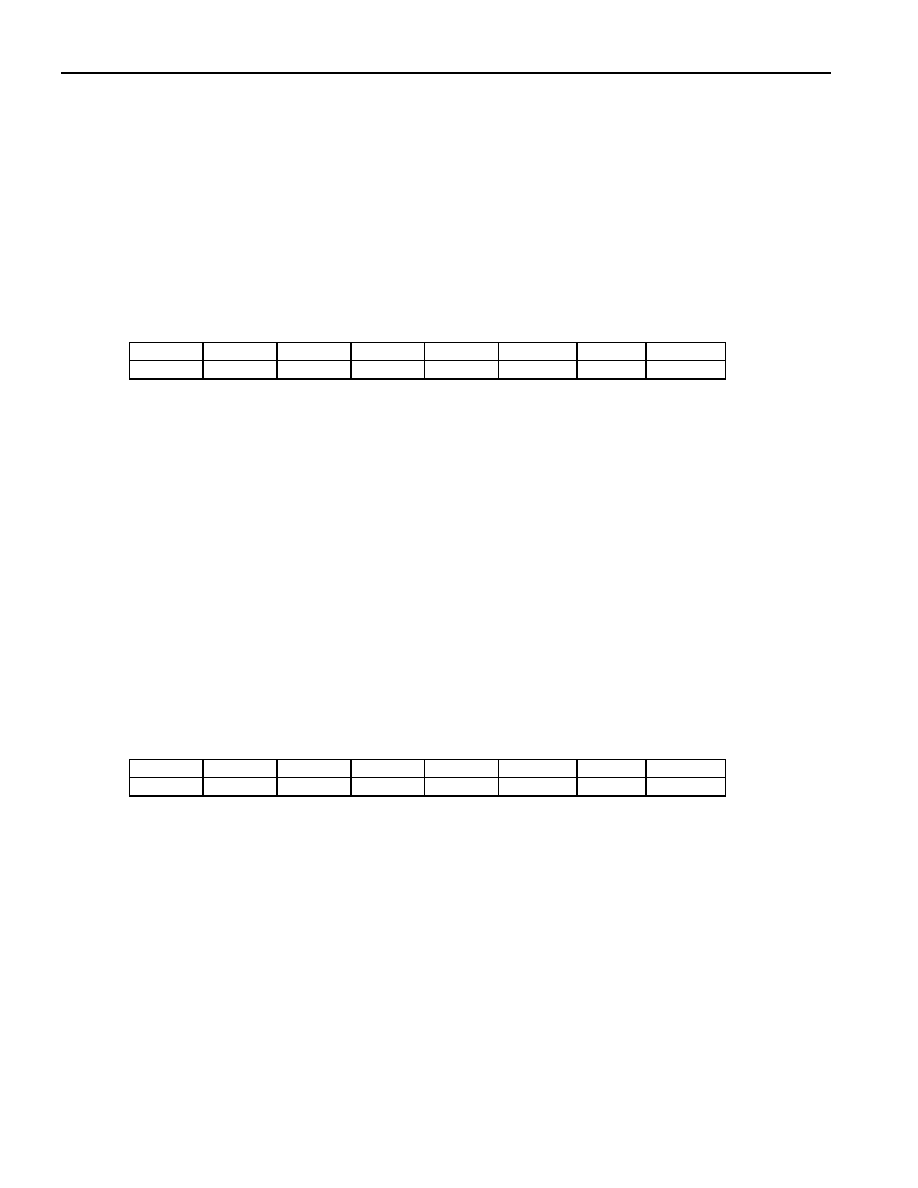

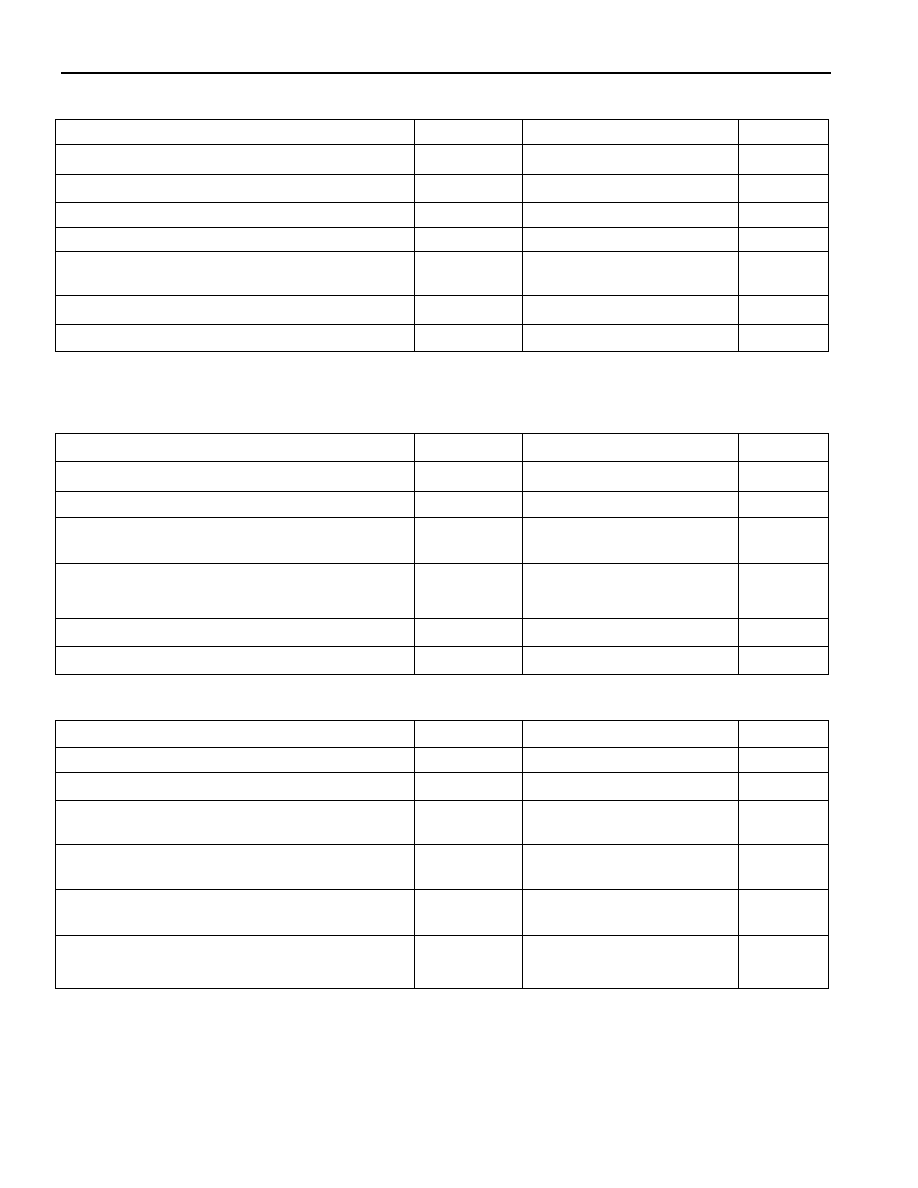

Figure 7-6

shows the transmit-framer-interface operation in frame-pulse mode for T1. In this example, the DS26102

uses the positive edge of TCLK to launch TDATA and TFP. Bit B1 is the MSB of a valid cell octet and B8 is the

LSB.

The TFP signal should be aligned with the framing bit position. When interfacing to framers where the framing

pulse and data active edges are individually configurable, it should be ensured that the sampling and updating

should happen in opposite edges.

UTOPIA II

Data Input

Transmit

FIFO

HEC Insertion

ON/OFF

HEC Insertion

ON

Payload

Scrambling

ON/OFF

HEC Error

Insertion

ON/OFF

Idle

Cell

Unassigned

Cell

TCRDS

(TCR1.3)

TCAE

(TCR1.2)

THIE (TCR1.0)

TCAE (TCR1.2)

TPSE (TCR1.4)

THEIE (TCR1.1)

HONP[4:0]

(THEPR)

HOFFP[2:0]

(THEPR)

Cell Data

to Framer (PHY)

DS26102 16-Port TDM-to-ATM PHY

22 of 64

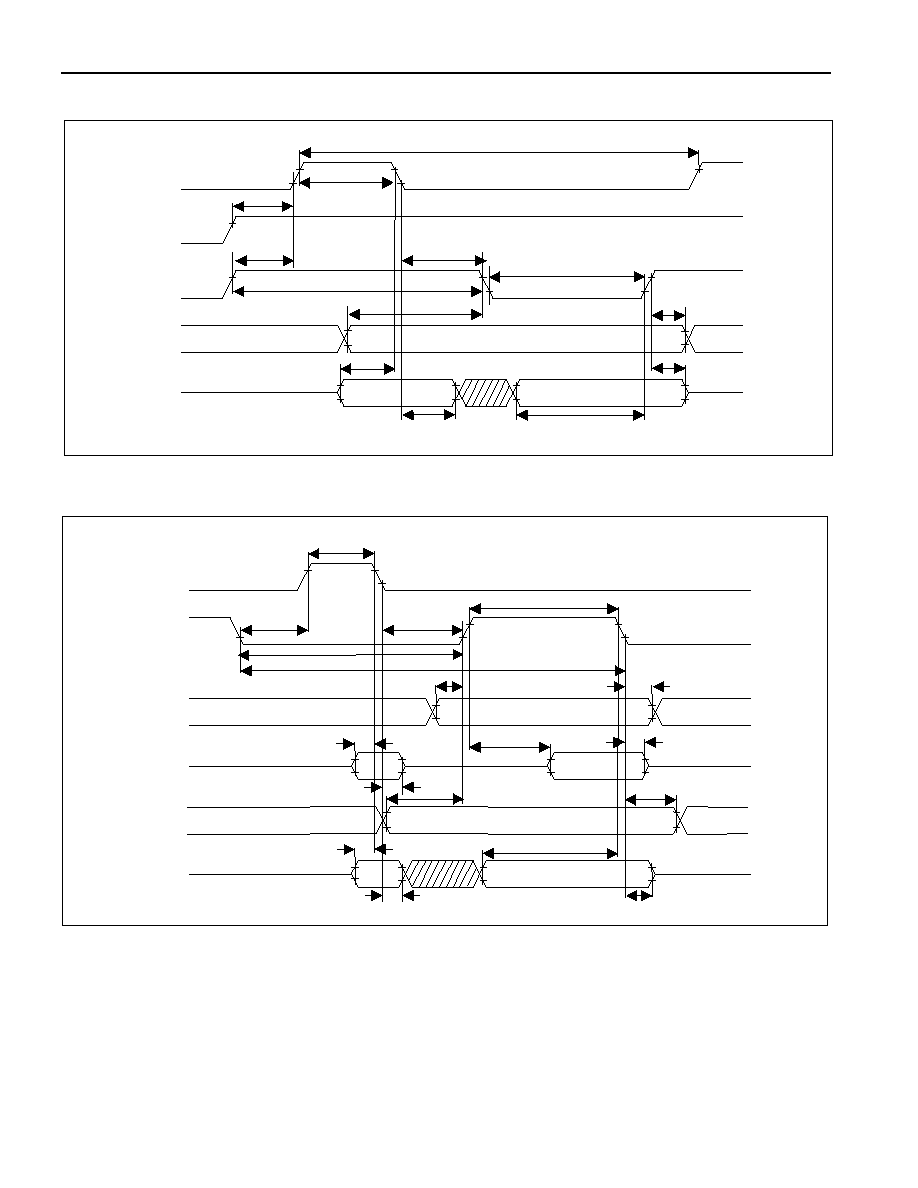

Figure 7-6. Transmit Framer Interface in TFP Mode for T1

Figure 7-7

shows the transmit-framer-interface operation for T1 in gapped-clock mode. The framing overhead-bit

position is gapped. In this diagram, DS26102 uses the positive edge to launch TDATA.

Figure 7-7. Transmit Framer Interface in Gapped-Clock Mode for T1

Figure 7-8

shows the E1 transmit-framer-interface operation using TFP to indicate the beginning of the E1 frame.

The DS26102 uses the positive edge to launch TDATA and TFP. Using TFP, the DS26102 identifies TS0 and

TS16 slots and does not send valid data on TDATA in these slots. In this case, B0 to B7 are not valid data bits of a

cell so that B8 is the MSB of the cell octet. The timing requirements for the TFP signal are the same as in the T1

case.

Figure 7-8. Transmit Framer Interface in TFP Mode for E1

TCLK[x]

1

TCLK[x]

2

TFP[x]

3

TDATA[x]

1) TCLK negative edge active

2) TCLK positive edge active

3) TFP as input or output

DSO Channel 1

F

B192

B191

B190

B1

B2

B3

B4

B5

B6

B7

B8

B9

TCLK[x]

TFP[x]

TDATA[x]

DSO Channel 1

TFP is Don't Care

F-Bit Gapped

B191

B190

B1

B2

B3

B4

B5

B6

B7

B8

B9

B192

TCLK[x]

1

TCLK[x]

2

TFP[x]

3

TDATA[x]

1) TCLK negative edge active

2) TCLK positive edge active

3) TFP as input or output (TFP_IN or TFP_OUT)

TS0 Slot

TS31

TS1

B0

B255

B254

B253

B1

B2

B3

B4

B5

B6

B7

B8

B9

DS26102 16-Port TDM-to-ATM PHY

23 of 64

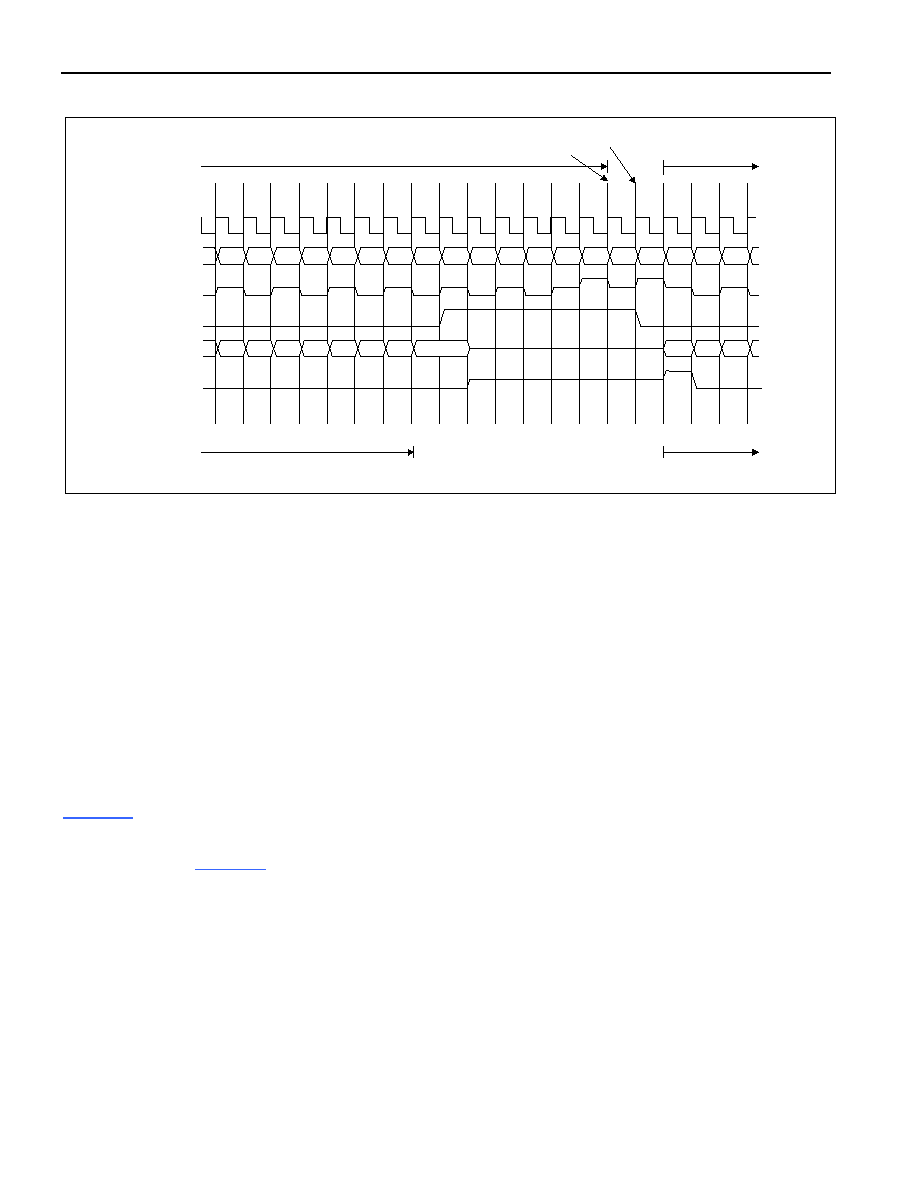

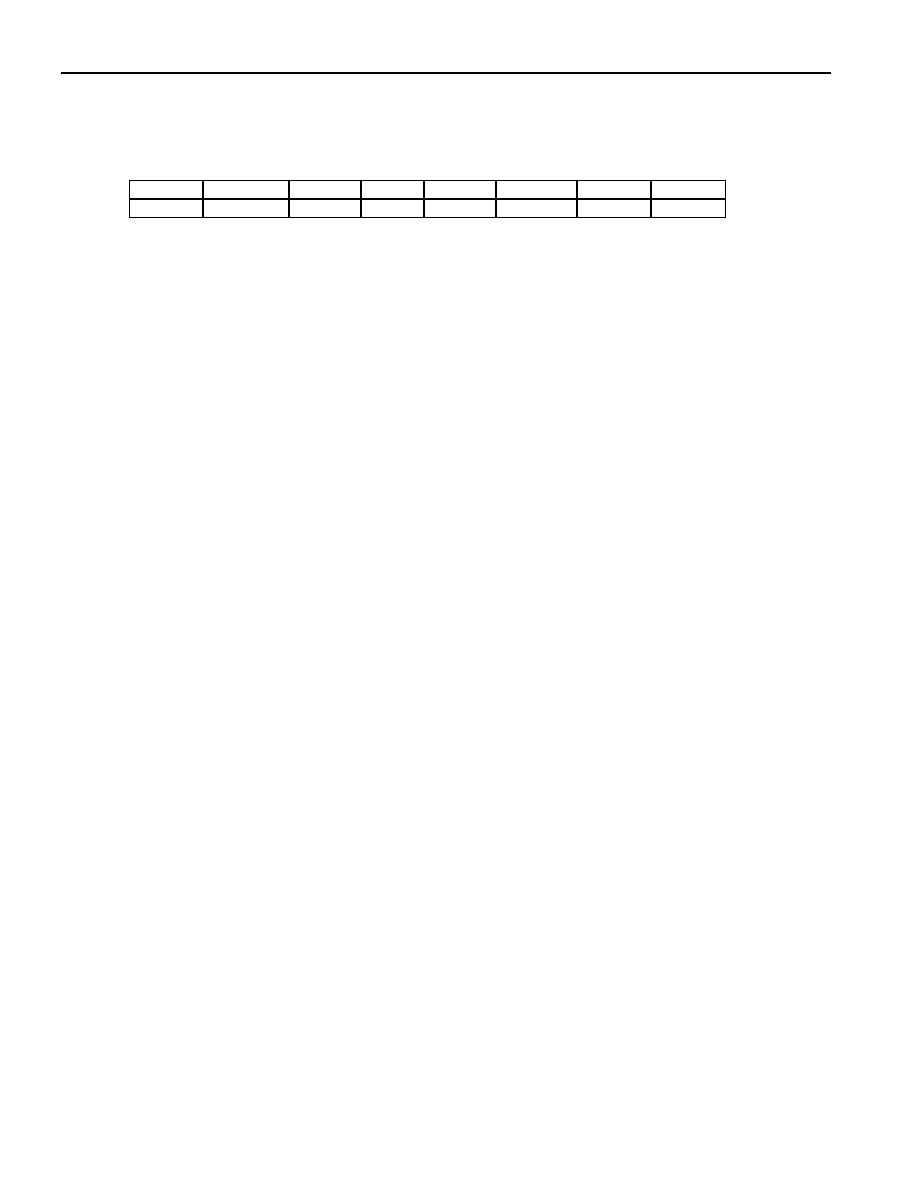

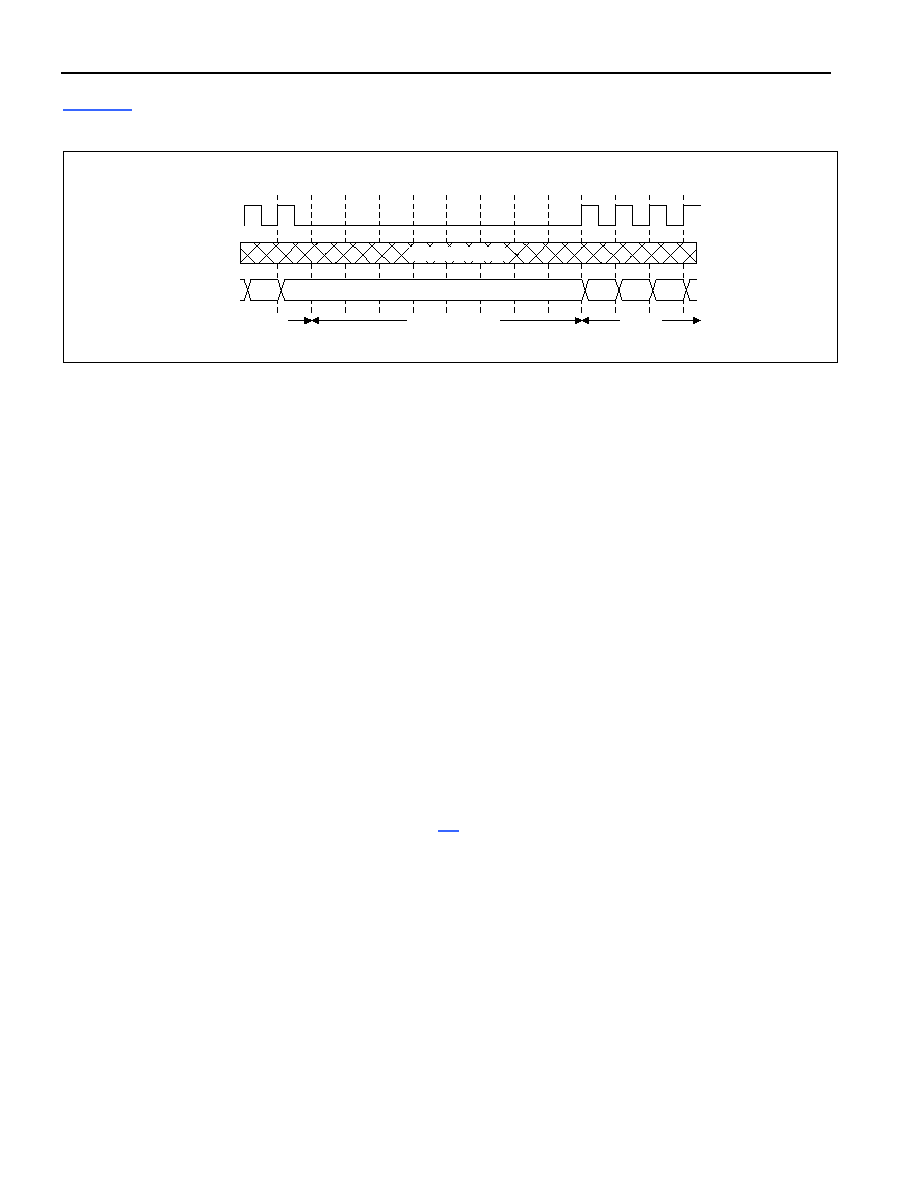

Figure 7-9

shows the transmit framer-interface operation for E1 in gapped-clock mode.

Figure 7-9. Transmit Framer Interface in Gapped-Clock Mode for E1

The fractional T1 (N x DS0) is supported in TFP and gapped-clock modes of the physical interface. In TFP mode,

the framer must generate TFP during frame-overhead-bit and nonactive-DS0-channel positions. Fractional T1 is

not supported if TFP is generated by the DS26102. In gapped-clock mode, TCLK should be gapped during frame-

overhead-bit and nonactive-DS0-channel positions. In E1, to achieve a rate in multiples of 64kbps up to

2.048Mbps, the DS26102 should be configured in gapped-clock mode, and TCLK should be gapped during

nonactive time slots. TFP mode (for both input and output TFP configurations) is not supported in fractional E1

configuration.

The DS26102 can either use the T1/E1 clock from the framer or use an internally generated low-frequency clock at

the transmit line interface. The low-frequency clock is the system clock (1/2 x GCLKIN) divided by 8. This clock is

used primarily for diagnostic loopback.

The TLICS bit (TCR2.6) selects between the framer clock and the internally generated clock. The internally

generated clock should be used only in diagnostic loopback (otherwise, the framer and DS26102 are

operating for different clocks). During diagnostic loopback, this clock is fed to the receive line interface

unit.

8. RECEIVE OPERATION

The receive interface of the DS26102 is fully compliant to the ATM Forum's UTOPIA Level 2 specifications. Each

octal block of the DS26102 can be configured to use one of the address ranges (0 to 7, 8 to 15, 16 to 23, and 24 to

30) as UTOPIA port addresses. If Rx FIFO is not empty, cell available is asserted. After cell transfer from a port,

the external cell-available signal is updated based on the receive-FIFO fill level one clock cycle after cell transfer

completion. During this one-clock cycle, cell-available indication for this port is kept in the deasserted state. In other

words, one-clock minimum latency between two cell transfers from the same UTOPIA port is needed by the

DS26102 to update its internal cell pointers. Section

8.3

gives additional details concerning the UTOPIA-side

interface.

8.1 Physical-Side

Receive

The receive framer interface operates in one of two modes:

1)

Gapped clock + data

2)

Clock + data + frame-pulse indication

The mode can be selected on a per-port basis with the receive physical-layer interface mode control bit (RPLIM) at

RCR2.1. If configured in frame-pulse-indication mode, the bits coming at frame-pulse-indication positions are

ignored in case of T1 direct mapping, and bits coming at TS0 and TS16 positions are ignored in case of E1 direct

mapping. TS0 and TS16 slots are identified using the frame-pulse indication aligned with bit 0 of the E1 frame. The

control bit RPC (RCFR.0) determines T1 or E1 configuration. If no frame-pulse indication is given, bits are sampled

at every receive clock tick. If clear E1 operation is needed, the interface should be configured to operate in gapped

TCLK[x]

TFP[x]

TDATA[x]

TS31

TFP is Don't Care

TS0 (gapped)

TS1

B254

B8

B9

B10

B255

DS26102 16-Port TDM-to-ATM PHY

24 of 64

clock + data mode, in which case the external frame-pulse-indication signal is ignored and the data bits are clocked

at every clock tick.

The active edge of the receive clock can be selected through the RAES (RCR2.2) control bit. The active edge

selected for the Rx framer interface should be opposite the active edge that is used by the transmitting device

(either an external framer or the transmit section of DS26102, when enabled for diagnostic loopback).

Diagnostic loopback toward the ATM layer side (UTOPIA side) can be enabled through the DLBE (RCR2.0) control

bit. In diagnostic loopback, data, clock, and frame-pulse indication generated by the transmit section of the

DS26102 are used instead of the corresponding signals from the physical layer device. Rx physical-interface mode

should be configured with same value as the Tx physical-interface mode. The Rx active-edge selection bit should

be configured as the opposite edge of that used by the transmit section of the DS26102.

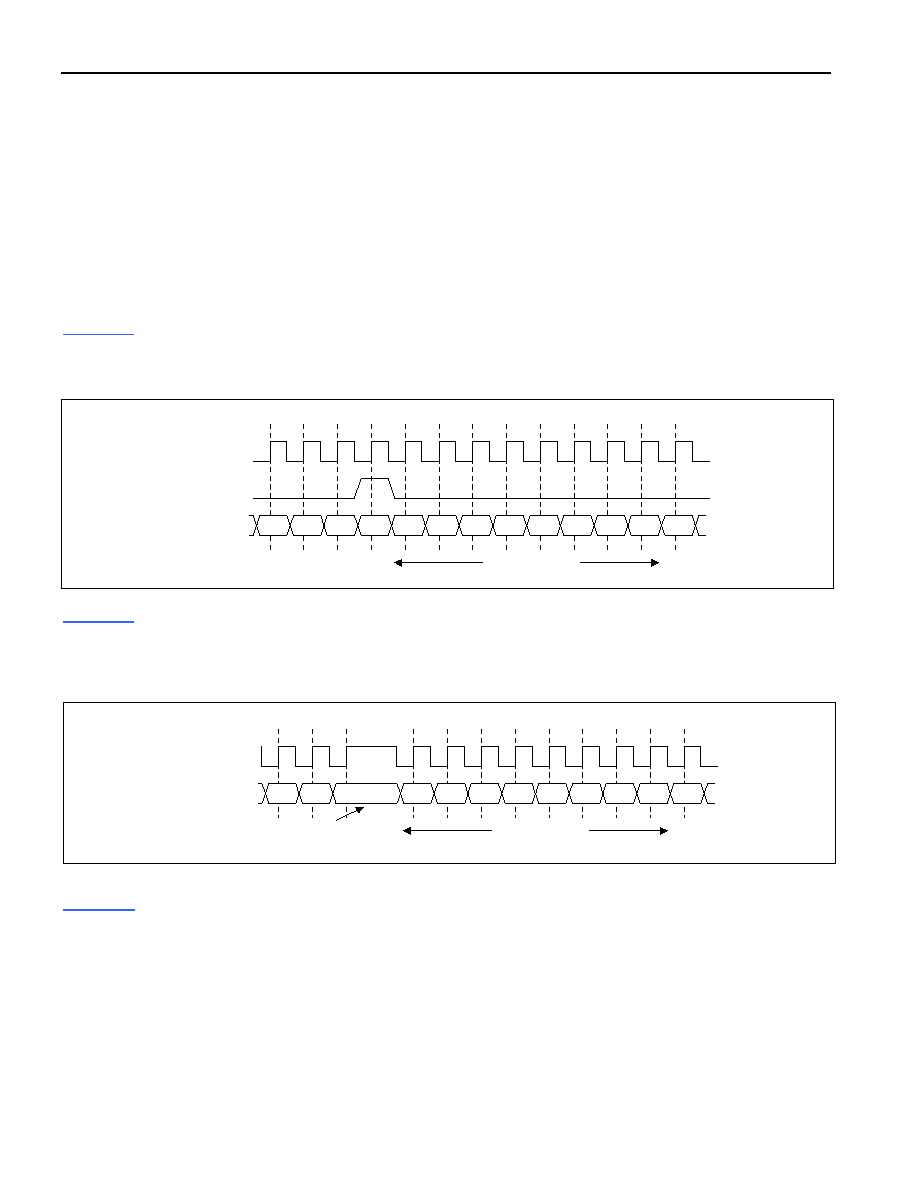

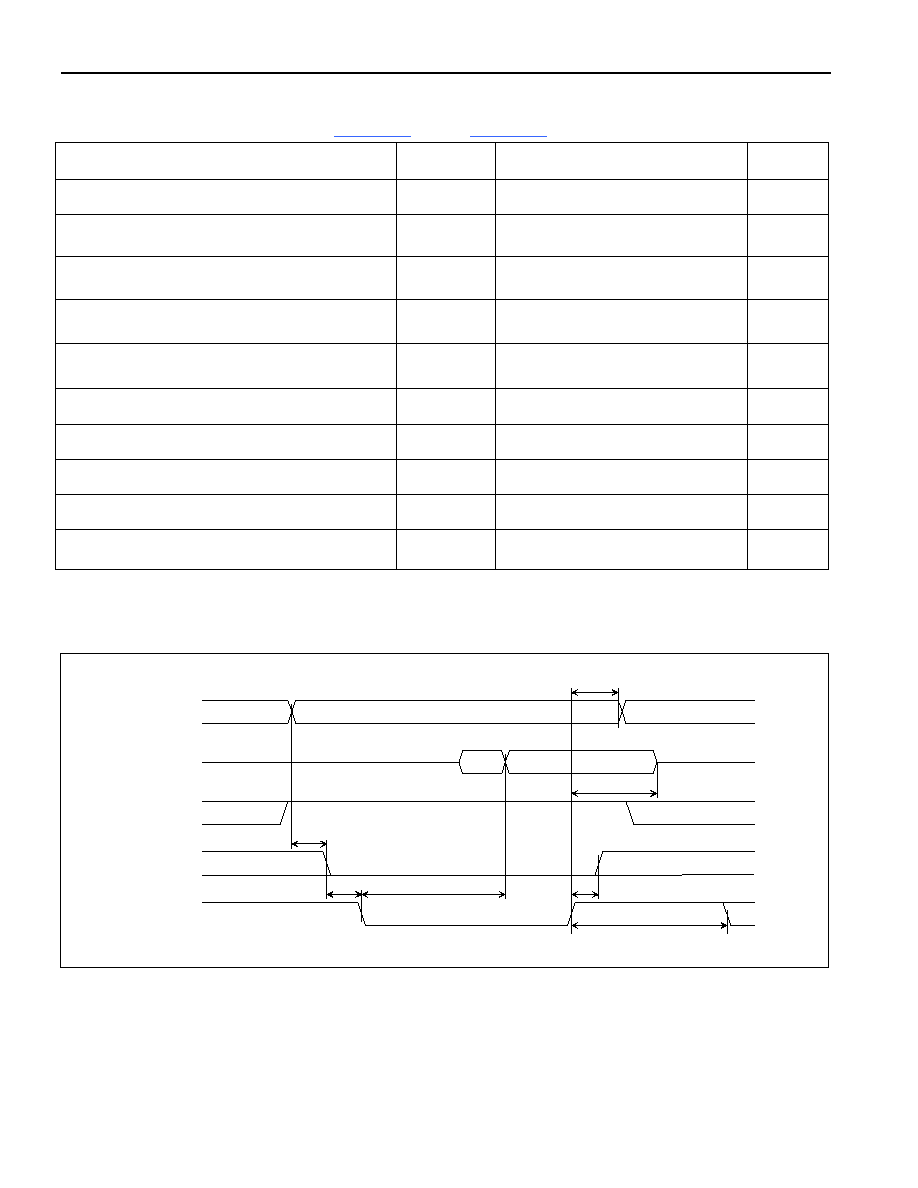

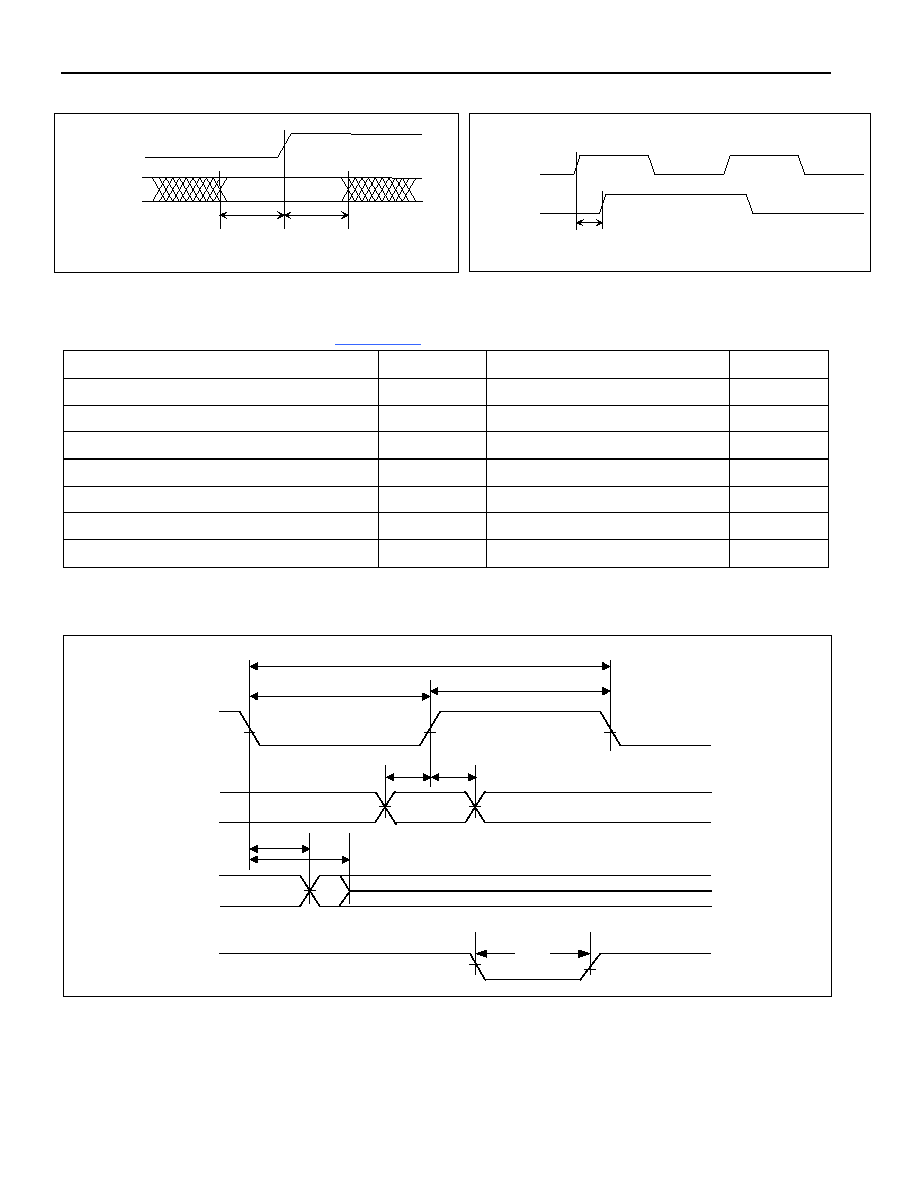

Figure 8-1

shows the receive framer-interface operation for T1 mode with the DS26102 using the positive clock

edge to sample RDATA and RFP and the framer using the negative edge to launch RDATA and RFP.

Figure 8-1. Receive Framer Interface in RFP Mode for T1

Figure 8-2

shows the receive-framer-interface operation for T1 in gapped-clock mode. The framing overhead-bit

position is gapped. In this figure, the DS26102 uses the positive edge to sample RDATA and RFP. RFP is don't

care.

Figure 8-2. Receive Framer Interface in Gapped-Clock Mode for T1

Figure 8-3

shows the receive-framer-interface operation for E1 using RFP to indicate the beginning of the E1

frame. The DS26102 uses the positive edge of RCLK to sample RDATA and RFP. Using RFP, the DS26102

identifies TS0 and TS16 slots and ignores RDATA coming in these slots.

RCLK[x]

RFP[x]

RDATA[x]

DSO Channel 1

F

B192

B191

B190

B1

B2

B3

B4

B5

B6

B7

B8

B9

RCLK[x]

RDATA[x]

DSO Channel 1

F-Bit Gapped

B192

B191

B190

B1

B2

B3

B4

B5

B6

B7

B8

B9

DS26102 16-Port TDM-to-ATM PHY

25 of 64

Figure 8-3. Receive Framer Interface in RFP Mode for E1

Figure 8-4

shows the receive-framer-interface operation for E1 in gapped-clock mode. In this mode, RCLK is

gapped during TS0 and TS16 locations.

Figure 8-4. Receive Framer Interface in Gapped-Clock Mode for E1

The fractional T1 (N x DS0) is supported in both RFP and gapped-clock modes of physical interface. In RFP mode,

the framer must generate RFP during frame-overhead-bit and nonactive-DS0-channel positions. In gapped-clock

mode, RCLK should be gapped during frame-overhead-bit and nonactive-DS0-channel positions. In E1 mode, the

DS26102 should be configured in gapped-clock mode and RCLK should be gapped during nonactive time slots.

RFP mode is not supported in fractional E1 configuration.

8.2 Receive

Processing

The received bits, after ignoring framing-overhead bits, are checked for possible HEC pattern. The polynomial used

for HEC check is G(X) = 1 + X + X

2

+ X

8

, per ITU I.432. Clearing the microprocessor interface register bit RCSE

(RCR1.0) can disable the COSET subtraction (0x55).

The cell boundaries in the incoming bit stream are identified based on HEC.

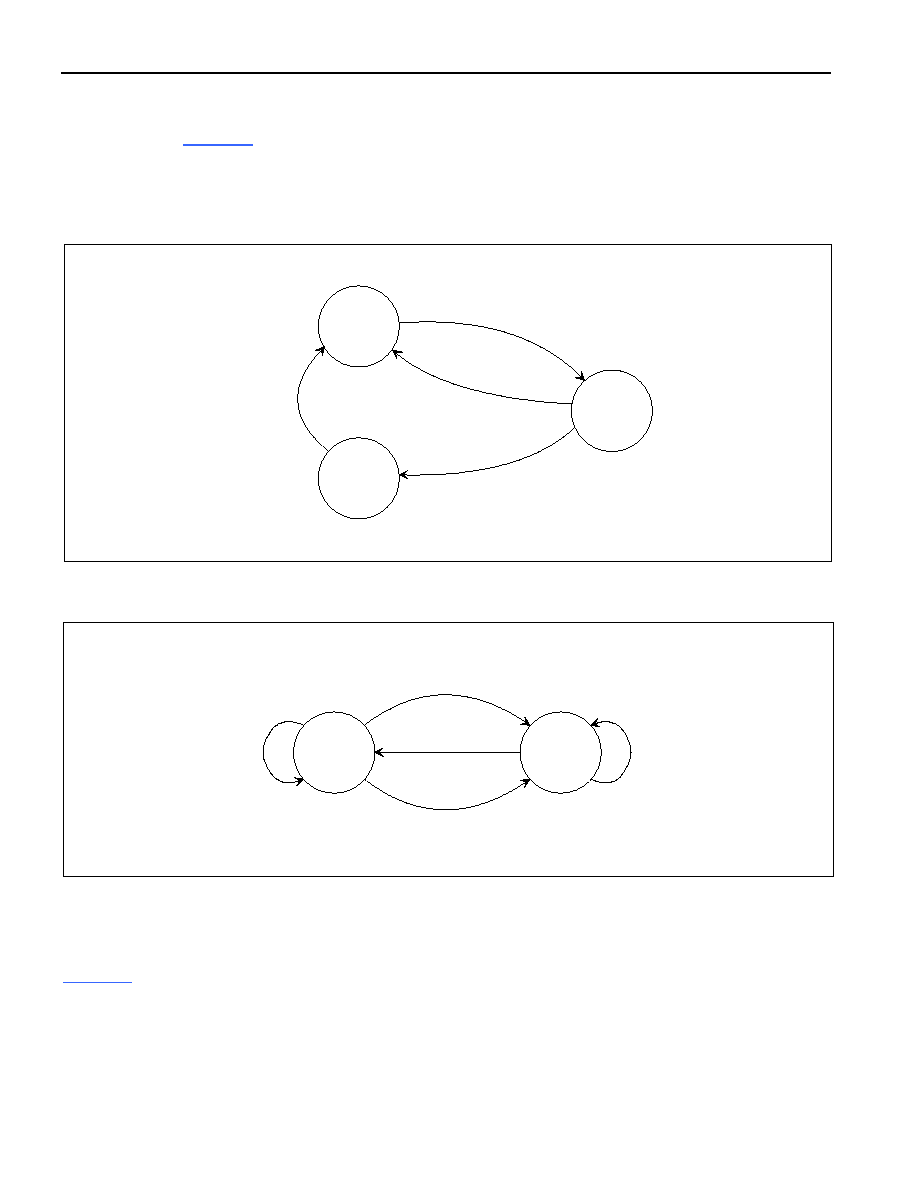

Figure 8-5

shows the cell-delineation

state machine. The cell-delineation state machine is initially in HUNT state. In HUNT state, it performs bit-by-bit

hunting for correct HEC. If correct HEC is found, it transitions to the PRESYNC state where it checks cell-by-cell for

correct HEC patterns. If DELTA-consecutive-correct patterns are received in PRESYNC, the cell-delineation state

machine transitions to SYNC state. Otherwise, it goes to HUNT state and reinitiates bit-by-bit hunting. In SYNC

state, if ALPHA-consecutive-incorrect HEC patterns are received, cell delineation is lost and it goes to HUNT state.

In PRESYNC and SYNC states, only cell-by-cell checking for the proper HEC pattern is performed. For the

DS26102, ALPHA = 7 and DELTA = 6.

The persistence of the out-of-cell delineation (OCD) event is integrated into LCD, based on programmable

integration time period (Rx-LCD integration-period register). If OCD persists for the programmed time, LCD is

declared. LCD is deasserted only when cell delineation persists in SYNC for the same-programmed integration

time. Whenever there is a change in LCD status (namely "into LCD" or "out of LCD"), an external interrupt is

generated when enabled by the corresponding mask bit RCR2.4. The persistence is checked every system clock

period (SYS_CLK) divided by 16,383. The default value of the Rx LCD integration-period register provides for an

integration time of 100ms for a 16.5MHz SYS_CLK.

RCLK[x]

RFP[x]

RDATA[x]

TS0 Slot

TS31

TS1

B0

B255

B254

B253

B1

B2

B3

B4

B5

B6

B7

B8

B9

RCLK[x]

RDATA[x]

TS31

TS0 (gapped)

TS1

B8

B9

B10

B255

B254

Don't Care

DS26102 16-Port TDM-to-ATM PHY

26 of 64

If single-bit header-error correction is enabled, the receiver mode of operation state machine follows the state

machine given in

Figure 8-6

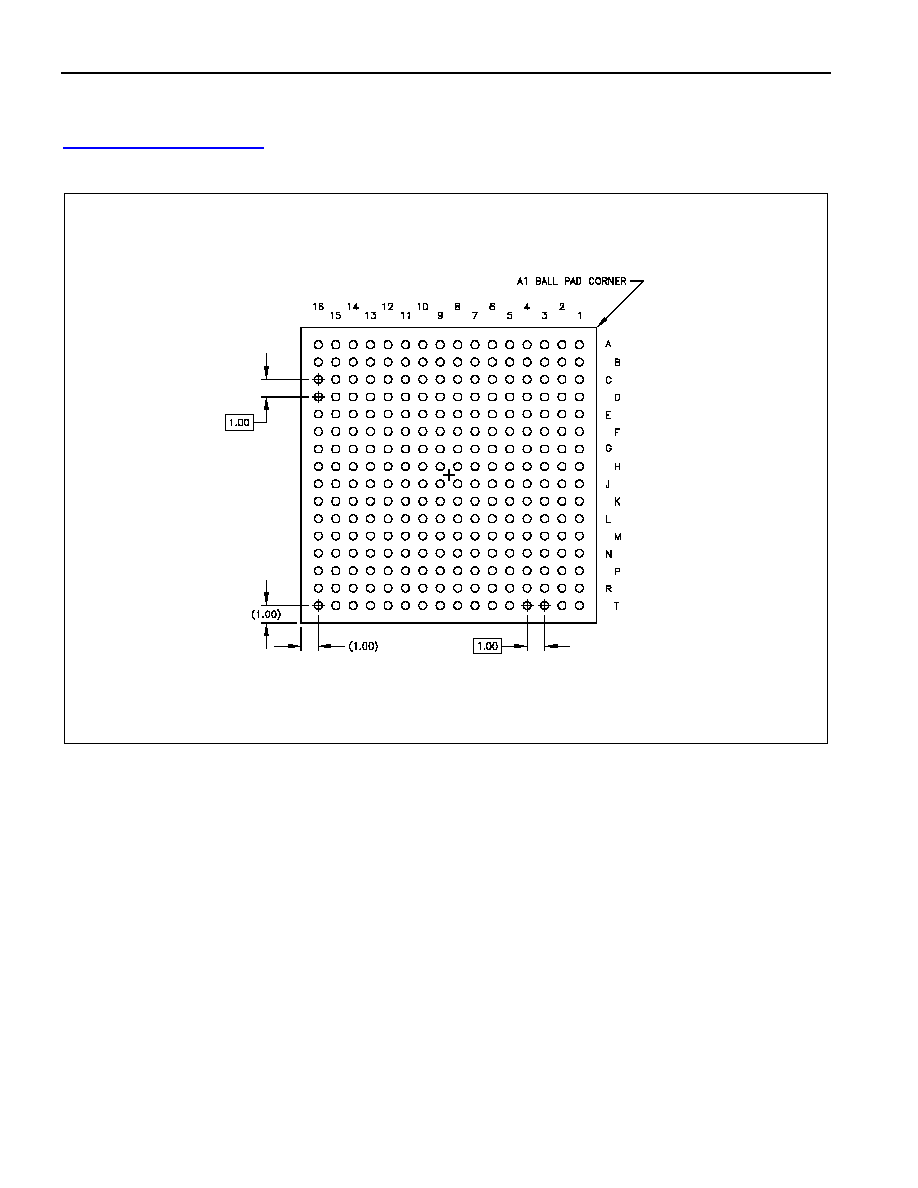

. Single-bit correction is done only if correction is enabled and the state machine is in