| ÐлекÑÑоннÑй компоненÑ: DS33Z44 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1 of 181

REV:

120304

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here:

www.maxim-ic.com/errata

.

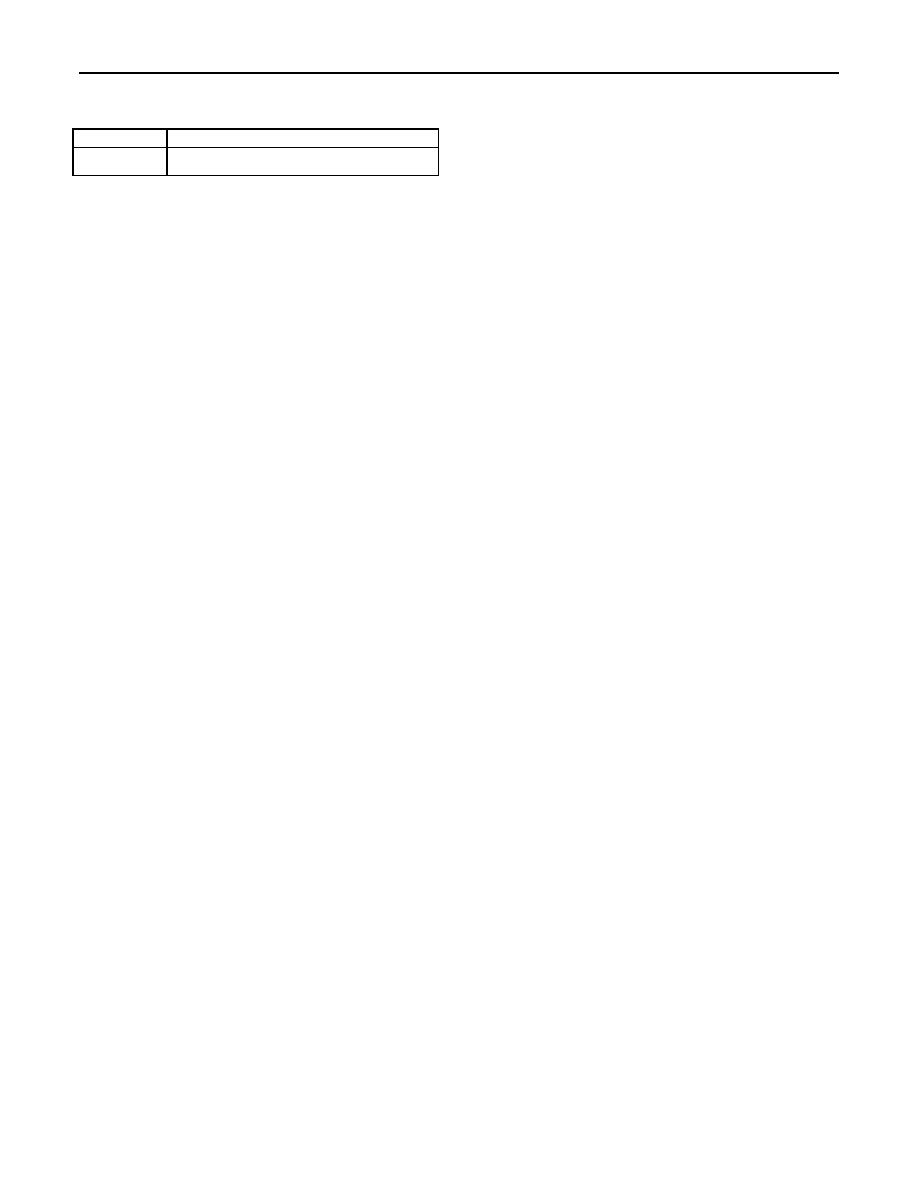

GENERAL DESCRIPTION

The DS33Z44 extends four 10/100 Ethernet LAN

segments by encapsulating MAC frames in HDLC or

X.86 (LAPS) for transmission over four PDH/TDM

data streams. The serial links support bidirectional

synchronous interconnect up to 52Mbps over xDSL,

T1/E1/J1, T3/E3, V.35/Optical, OC-1/EC-1, or

SONET/SDH Tributary.

The device performs store-and-forward of packets

with full wire-speed transport capability. The built-in

Committed Information Rate (CIR) controllers

provide fractional bandwidth allocation up to the line

rate in increments of 512kbps. The DS33Z44 can

operate with an inexpensive external processor,

EEPROM or in a stand-alone hardware mode.

APPLICATIONS

Transparent LAN Service

LAN Extension

Ethernet Delivery Over T1/E1/J1, T3/E3,

OC-1/EC-1, G.SHDSL, or HDSL2/4

FUNCTIONAL DIAGRAM

FEATURES

§ Four 10/100 IEEE 802.3 Ethernet MACs (MII and

RMII) Half/Full Duplex with Automatic Flow

Control

§ Four 52Mbps Synchronous TDM Serial Ports

with independent transmit and receive timing.

§ HDLC/LAPS Encapsulation with Programmable

FCS and Interframe Fill

§ Committed Information Rate Controllers Provide

Fractional Allocations in 512kbps Increments

§ Programmable BERT for Serial (TDM) Interfaces

§ External 16MB, 100MHz SDRAM Buffering

§ Parallel Microprocessor Interface

§ SPI Interface and Hardware Mode for Operation

Without a Host Processor

§ 1.8V Operation with 3.3V Tolerant I/O

§ IEEE 1149.1 JTAG Support

Features Continued on Page

10

.

ORDERING INFORMATION

PART TEMP

RANGE

PIN-PACKAGE

DS33Z44

-40°C to +85°C

256 CSBGA

Go to

www.maxim-ic.com/telecom

for a complete list of

Telecommunications data sheets, evaluation kits, application

notes, and software downloads.

DS33Z44

Quad Ethernet Mapper

www.maxim-ic.com

4 10/100

MACs

SDRAM

4 MII/RMII

PROM

OR

mC

CONFIG.

LOADER

DS33Z44

4 10/100

ETHERNET

PHYs

4 SERIAL

PORTS

TRANSCEIVERS/

SERIAL DRIVERS

BERT

HDLC/X.86

MAPPER

DS33Z44 Quad Ethernet Mapper

2 of 181

DOCUMENT REVISION HISTORY

REVISION DESCRIPTION

120304

New Product Release

DS33Z44 Quad Ethernet Mapper

3 of 181

TABLE OF CONTENTS

1

DESCRIPTION....................................................................................................................9

2

FEATURE HIGHLIGHTS...................................................................................................10

2.1

G

ENERAL

................................................................................................................................. 10

2.2

S

ERIAL

I

NTERFACES

................................................................................................................. 10

2.3

HDLC...................................................................................................................................... 10

2.4

C

OMMITTED

I

NFORMATION

R

ATE

(CIR) C

ONTROLLERS

............................................................... 10

2.5

X.86 S

UPPORT

......................................................................................................................... 10

2.6

SDRAM I

NTERFACE

................................................................................................................. 11

2.7

MAC I

NTERFACES

.................................................................................................................... 11

2.8

M

ICROPROCESSOR

I

NTERFACE

................................................................................................. 11

2.9

S

ERIAL

SPI I

NTERFACE

--M

ASTER

M

ODE

O

NLY

......................................................................... 11

2.10

D

EFAULT

C

ONFIGURATIONS

...................................................................................................... 11

2.11

T

EST AND

D

IAGNOSTICS

........................................................................................................... 11

2.12

S

PECIFICATIONS

C

OMPLIANCE

................................................................................................... 12

3

APPLICATIONS ................................................................................................................13

4

ACRONYMS AND GLOSSARY ........................................................................................16

5

MAJOR OPERATING MODES .........................................................................................17

6

BLOCK DIAGRAMS .........................................................................................................18

7

PIN DESCRIPTIONS.........................................................................................................19

7.1

P

IN

F

UNCTIONAL

D

ESCRIPTION

................................................................................................. 19

8

FUNCTIONAL DESCRIPTION..........................................................................................30

8.1

PROCESSOR INTERFACE.................................................................................................... 30

8.1.1

Read-Write/Data Strobe Modes ..........................................................................................................31

8.1.2

Clear On Read ....................................................................................................................................31

8.1.3

Interrupt and Pin Modes......................................................................................................................31

8.2

SPI SERIAL EEPROM INTERFACE....................................................................................... 31

8.3

CLOCK STRUCTURE ............................................................................................................ 32

8.3.1

Serial Interface Clock Modes ..............................................................................................................34

8.3.2

Ethernet Interface Clock Modes..........................................................................................................34

8.4

RESETS AND LOW-POWER MODES................................................................................... 35

8.5

INITIALIZATION AND CONFIGURATION .............................................................................. 36

8.6

GLOBAL RESOURCES.......................................................................................................... 36

8.7

PER-PORT RESOURCES...................................................................................................... 36

8.8

DEVICE INTERRUPTS........................................................................................................... 37

8.9

SERIAL INTERFACES ........................................................................................................... 39

8.10

CONNECTIONS AND QUEUES............................................................................................. 39

8.11

ARBITER................................................................................................................................ 42

8.12

FLOW CONTROL................................................................................................................... 42

8.12.1

Full Duplex Flow control......................................................................................................................43

8.12.2

Half Duplex Flow control .....................................................................................................................44

8.12.3

Host-Managed Flow control ................................................................................................................44

8.13

ETHERNET INTERFACES..................................................................................................... 45

8.13.1

DTE and DCE Mode ...........................................................................................................................47

8.14

ETHERNET MAC ................................................................................................................... 48

8.14.1

MII Mode Options................................................................................................................................50

8.14.2

RMII Mode...........................................................................................................................................50

8.14.3

PHY MII Management Block and MDIO Interface...............................................................................51

DS33Z44 Quad Ethernet Mapper

4 of 181

8.15

BERT...................................................................................................................................... 53

8.15.1

Receive Data Interface........................................................................................................................53

8.15.2

Repetitive Pattern Synchronization .....................................................................................................54

8.15.3

Pattern Monitoring...............................................................................................................................55

8.15.4

Pattern Generation..............................................................................................................................55

8.16

SERIAL INTERFACES ........................................................................................................... 56

8.17

TRANSMIT PACKET PROCESSOR....................................................................................... 56

8.18

RECEIVE PACKET PROCESSOR ......................................................................................... 57

8.19

X.86 ENCODING AND DECODING ....................................................................................... 59

8.20

COMMITTED INFORMATION RATE CONTROLLER............................................................. 62

8.21

HARDWARE MODE ............................................................................................................... 64

9

DEVICE REGISTERS .......................................................................................................68

9.1

R

EGISTER

B

IT

M

APS

................................................................................................................. 69

9.1.1

Global Register Bit Map ......................................................................................................................69

9.1.2

Arbiter Register Bit Map ......................................................................................................................70

9.1.3

BERT Register Bit Map .......................................................................................................................70

9.1.4

Serial Interface Register Bit Map ........................................................................................................71

9.1.5

Ethernet Interface Register Bit Map ....................................................................................................73

9.1.6

MAC Register Bit Map.........................................................................................................................74

9.2

G

LOBAL

R

EGISTER

D

EFINITIONS

................................................................................................ 76

9.3

A

RBITER

R

EGISTERS

................................................................................................................ 90

9.3.1

Arbiter Register Bit Descriptions .........................................................................................................90

9.4

BERT R

EGISTERS

.................................................................................................................... 93

9.5

S

ERIAL

I

NTERFACE

R

EGISTERS

............................................................................................... 100

9.5.1

Serial Interface Transmit and Common Registers ............................................................................100

9.5.2

Serial Interface Transmit Register Bit Descriptions ..........................................................................100

9.5.3

Transmit HDLC Processor Registers................................................................................................101

9.5.4

X.86 Registers...................................................................................................................................107

9.5.5

Receive Serial Interface ....................................................................................................................109

9.6

E

THERNET

I

NTERFACE

R

EGISTERS

.......................................................................................... 122

9.6.1

Ethernet Interface Register Bit Descriptions .....................................................................................122

9.6.2

MAC Registers ..................................................................................................................................134

10

FUNCTIONAL TIMING....................................................................................................151

10.1

F

UNCTIONAL

S

ERIAL

I/O T

IMING

.............................................................................................. 151

10.2

MII

AND

RMII I

NTERFACES

...................................................................................................... 152

10.3

SPI I

NTERFACE

M

ODE AND

EEPROM P

ROGRAM

S

EQUENCE

.................................................... 154

11

OPERATING PARAMETERS .........................................................................................157

11.1

MII I

NTERFACE

....................................................................................................................... 160

11.2

RMII I

NTERFACE

.................................................................................................................... 162

11.3

MDIO I

NTERFACE

................................................................................................................... 164

11.4

T

RANSMIT

WAN I

NTERFACE

................................................................................................... 165

11.5

R

ECEIVE

WAN I

NTERFACE

..................................................................................................... 166

11.6

SDRAM T

IMING

..................................................................................................................... 167

11.7

M

ICROPROCESSOR

B

US

AC C

HARACTERISTICS

....................................................................... 169

11.8

EEPROM I

NTERFACE

T

IMING

................................................................................................. 172

11.9

JTAG I

NTERFACE

T

IMING

....................................................................................................... 173

12

JTAG INFORMATION.....................................................................................................174

12.1

JTAG/TAP C

ONTROLLER

S

TATE

M

ACHINE

D

ESCRIPTION

......................................................... 175

12.2

I

NSTRUCTION

R

EGISTER

......................................................................................................... 177

12.2.1

SAMPLE:PRELOAD .........................................................................................................................178

12.2.2

BYPASS............................................................................................................................................178

12.2.3

EXTEST ............................................................................................................................................178

12.2.4

CLAMP..............................................................................................................................................178

DS33Z44 Quad Ethernet Mapper

5 of 181

12.2.5

HIGHZ ...............................................................................................................................................178

12.2.6

IDCODE ............................................................................................................................................178

12.3

JTAG ID C

ODES

.................................................................................................................... 179

12.4

T

EST

R

EGISTERS

.................................................................................................................... 179

12.5

B

OUNDARY

S

CAN

R

EGISTER

................................................................................................... 179

12.6

B

YPASS

R

EGISTER

................................................................................................................. 179

12.7

I

DENTIFICATION

R

EGISTER

...................................................................................................... 179

12.8

JTAG F

UNCTIONAL

T

IMING

..................................................................................................... 180

13

PACKAGE INFORMATION.............................................................................................181

13.1

17

MM X

17

MM

256-CSBGA .................................................................................................... 181

Document Outline