| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MIC708SM | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

The MIC706P/R/S/T and MIC708R/S/T are inexpensive

microprocessor supervisory circuits that monitor power

supplies in 3.0 and 3.3 Volt microprocessor based

systems. The circuit functions include a watchdog timer,

microprocessor reset, power failure warning and a

debounced manual reset input.

The MIC706 offers a watchdog timer function, while the

MIC708 has no watchdog timer but has an active high

reset output in addition to the active low reset output.

The R, S, and T versions are similar in all respects

except for supply voltage reset threshold levels. The

threshold levels are 2.63, 2.93, and 3.08V respectively.

When the supply voltage drops below the reset

threshold level, RESET (and RESET for the MIC708) is

asserted.

The MIC706P is identical to the MIC706R, except that

the Reset output is asserted high.

1

2

3

4

V

CC

GND

PFI

8

7

6

5

WDO

RESET

WDI

PFO

MIC706

MR

PFO

1

2

3

4

V

CC

GND

PFI

8

7

6

5

RESET

RESET

NC

PFO

MIC708

MR

PFO

(RESET for MIC706P)

Top View

N Package - 8 Lead Plastic DIP Package

M Package - 8 Lead Plastic SOIC Package

Part

Package

Temp. Range

MIC70_ _N

8-Lead PDIP

-40∞C to +85∞C

MIC70_ _M

8-Lead SOIC

-40∞C to +85∞C

∑

Laptop Computers

∑

Intelligent Instruments

∑

Critical Microprocessor Power Monitoring

∑

Printers

∑

Computers

∑

Controllers

∑

30

µ

A Maximum Supply Current

∑

Debounced Manual Reset Input is

TTL/CMOS Compatible

∑

Reset Pulse Width, 200ms

∑

Watchdog Timer, 1.6s (MIC706)

∑

Precision Supply Voltage Monitor

∑

Early Power Fail Warning

or Low Battery

Detect

VCC

RESET

µP

RESET

VCC

MIC706

+3.0 or +3.3V (Regulated)

MR

WDI

I/O Line

PFO

Interrupt

PFI

DC Voltage

(Unregulated)

Manual

Reset

WDO

NMI

Typical Operating Circuit

Features

Description

Pin Configuration

Ordering Information

Typical Applications

MIC706P/R/S/T, MIC708R/S/T µP Supervisory Circuits

MIC706P/R/S/T, MIC708R/S/T

µP Supervisory Circuits

MIC706P/R/S/T, MIC708R/S/T

µ

P Supervisory Circuits

2

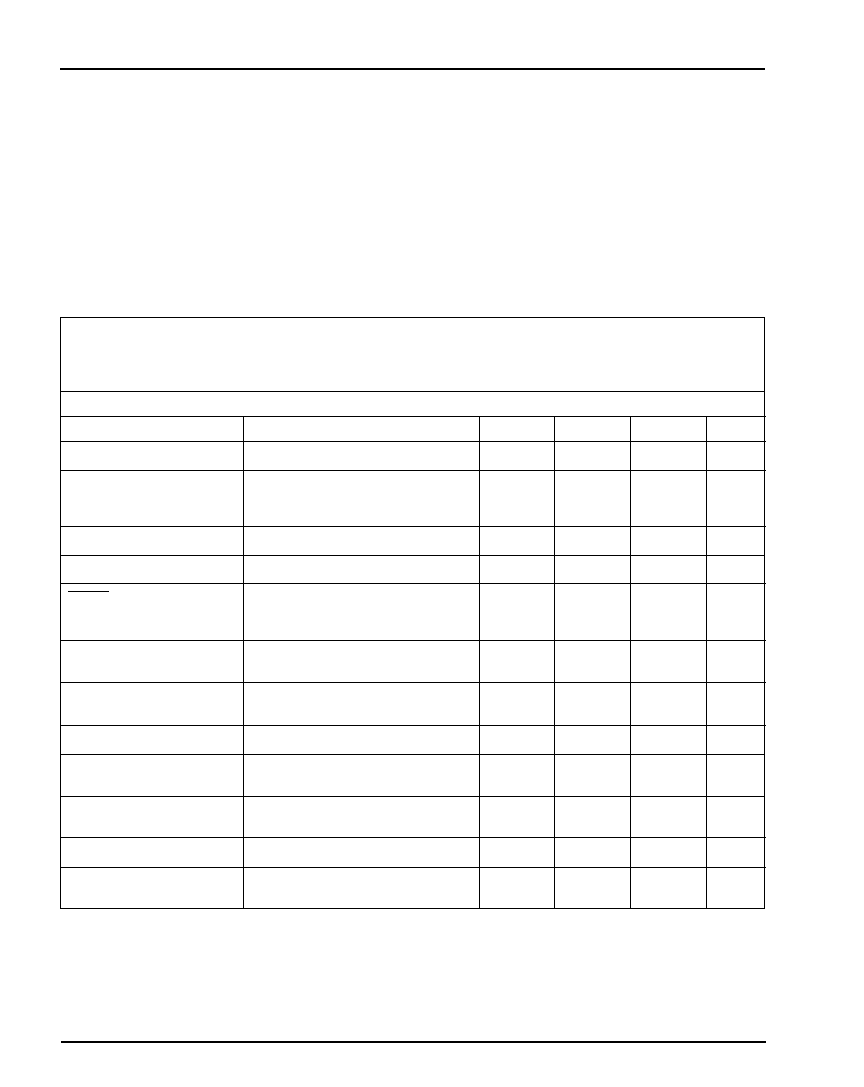

Electrical Characteristics

VCC = 2.70V to 5.5V for MIC70_P/R, VCC = 3.00V to 5.5V for MIC70_S, VCC = 3.15V to 5.5V for MIC70_T, T

A

= -40∞C to 85∞C

unless otherwise noted.

Parameter

Conditions

Min

Typ

Max

Units

Operating Voltage Range, VCC

1.4

5.5

V

Supply Current

30

µ

A

Reset Voltage Threshold

MIC70_P/R

2.55

2.63

2.70

V

MIC70_S

2.85

2.93

3.00

MIC70_T

3.00

3.08

3.15

Reset Threshold Hysteresis

20

mV

Reset Pulse Width, t

RS

140

200

280

ms

RESET Output Voltage

ISource = 200

µ

A

0.8 x VCC

V

(MIC70_R/S/T)

ISink = 1.2mA

0.3

ISink = 50

µ

A, VCC = 1.4V

0.3

RESET Output Voltage

ISource = 200

µ

A

0.8 x VCC

V

(MIC706P)

ISink = 1.2mA

0.3

RESET Output Voltage

ISource = 200

µ

A

0.8 x VCC

V

(MIC708R/S/T)

ISink = 500

µ

A

0.3

Watchdog Timeout Period, t

WD

1.0

1.6

2.25

sec

WDI Minimum Input Pulse, t

WP

VIL = 0.4V, VIH = 80% of VCC

100

ns

VIL = 0.4V, VIH = 80% of VCC>4.5V

50

ns

WDI Threshold Voltage

VIH

0.7 x VCC

V

VIL

0.6

WDI Input Current

WDI = 0V or VCC

-1

1

µ

A

WDO Output Voltage

ISource = 200

µ

A

0.8 x VCC

V

ISink = 500

µ

A

0.3

Absolute Maximum Ratings

Terminal Voltage

VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 6.0V

All Other Inputs . . . . . . . . . . . . -0.3V to (VCC + 0.3V)

Input Current

VCC, Gnd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25mA

Output Current (all outputs) . . . . . . . . . . . . . . . . . 20mA

Operating Temperature Range

MIC70_N, MIC70_M . . . . . . . . . . . . . . . . . -40∞C to 85∞C

Storage Temperature Range . . . . . . . . . . . . .-65∞C to 150∞C

Lead Temperature (Soldering - 10 sec.) . . . . . . . . . . . 300∞C

Power Dissipation (PDIP) . . . . . . . . . . . . . . . . . . . . 475mW

Power Dissipation (SOIC) . . . . . . . . . . . . . . . . . . . . 400mW

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute

maximum ratings for extended periods may affect device reliability. Operating ranges define those limits between which the functionality of the device is guaranteed.

MIC706P/R/S/T, MIC708R/S/T

µ

P Supervisory Circuits

3

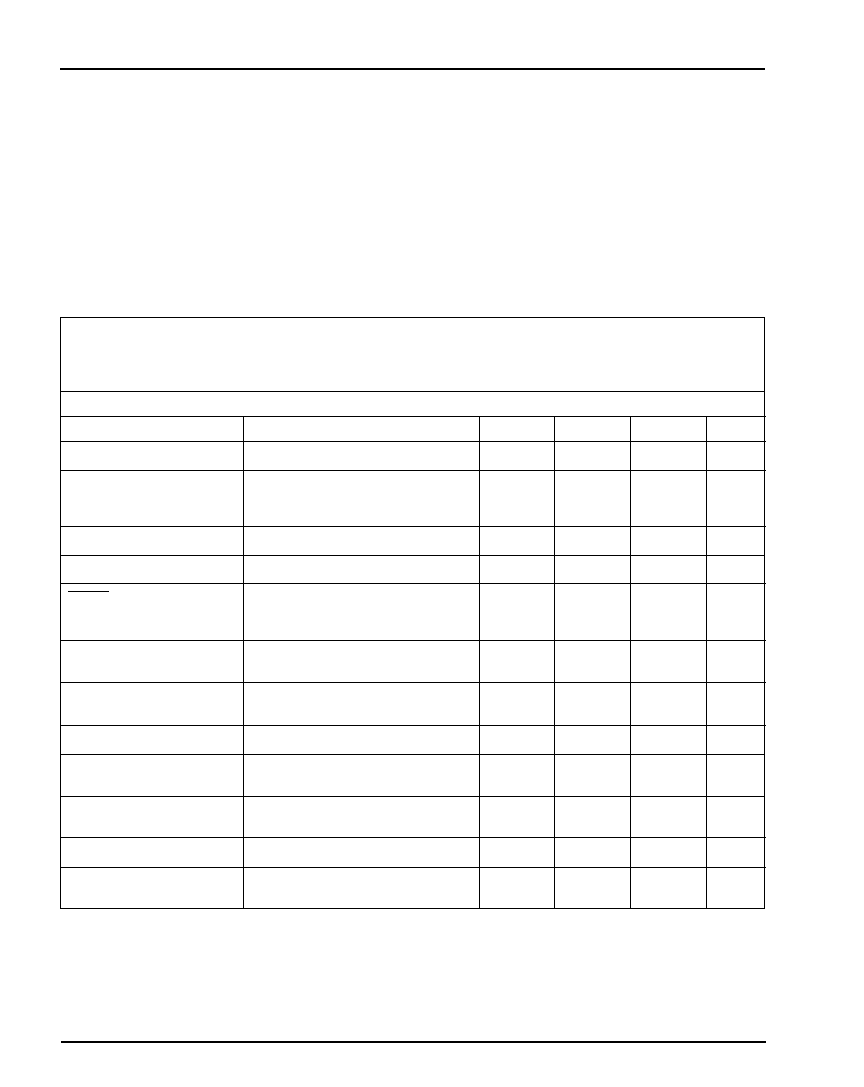

Electrical Characteristics

VCC = 2.70V to 5.5V for MIC70_P/R, VCC = 3.00V to 5.5V for MIC70_S, VCC = 3.15V to 5.5V for MIC70_T, T

A

= -40∞C to 85∞C

unless otherwise noted.

Parameter

Conditions

Min

Typ

Max

Units

MR Pull-Up Current

MR = 0V

20

250

600

µ

A

MR Pulse Width, t

MR

500

nS

VCC > 4.5V

150

nS

MR Input Threshold

VIL

0.6

V

VIH

0.7 x VCC

MR to Reset Output Delay, t

MD

750

nS

PFI Input Threshold

1.2

1.25

1.3

V

PFI Input Current

-25

0.01

+25

nA

PFO Output Voltage

ISink = 1.2mA

0.3

V

ISource = 200

µ

A

0.8 x VCC

4

Manual Reset Input forces reset outputs to assert when

pulled below 0.8V. An internal pull-up current of 250

µ

A on

this input forces it high when left floating. This input can

also be driven from TTL or CMOS logic.

Primary supply input, +5V.

IC ground pin, 0V reference.

Power fail input. Internally connected to the power fail

comparator which is referenced to 1.25V. The power fail

output (PFO) remains high if PFI is above 1.25V. PFI

should be connected to GND or VOUT if the power fail

comparator is not used.

Power fail output. The power fail comparator is

independent of all other functions on this device.

Watchdog input. The WDI input monitors microprocessor

activity, an internal watchdog timer resets itself with each

transition on the watchdog input. If the WDI pin is held high

or low for longer than the watchdog timeout period, WDO is

forced to active low. The watchdog function cannot be

disabled.

No Connect

RESET is asserted if either VCC goes below the reset

threshold or by a low signal on the manual reset input (MR).

RESET remains asserted for one reset timeout period

(200ms) after VCC exceeds the reset threshold or after the

manual reset pin transitions from low to high. The

watchdog timer will not assert RESET unless WDO is

connected to MR.

Output for the watchdog timer. The watchdog timer resets

itself with each transition on the watchdog input. If the WDI

pin is held high or low for longer than the watchdog timeout

period, WDO is forced low. WDO will also be forced low if

VCC is below the reset threshold and will remain low until

VCC returns to a valid level.

RESET is the compliment of RESET and is asserted if

either VCC goes below the reset threshold or by a low

signal on the manual reset input (MR). RESET is suitable

for microprocessors systems that use an active high reset.

Pin No.

Pin Name

MIC706

MIC706P

MIC708

R/S/T

MR

1

1

1

VCC

2

2

2

GND

3

3

3

PFI

4

4

4

PFO

5

5

5

WDI

6

6

N/A

N/C

N/A

N/A

6

RESET

7

N/A

7

WDO

8

8

N/A

RESET

N/A

7

8

Pin Functions

MIC706P/R/S/T, MIC708R/S/T

µ

P Supervisory Circuits

5

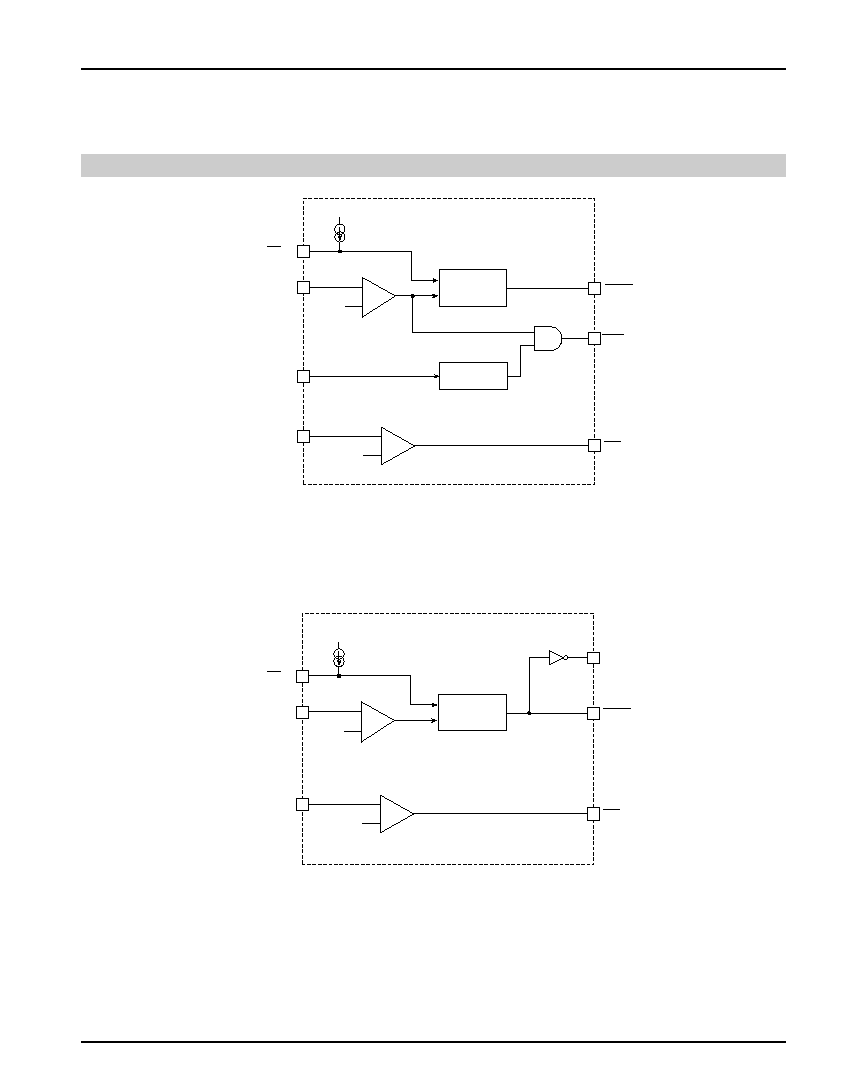

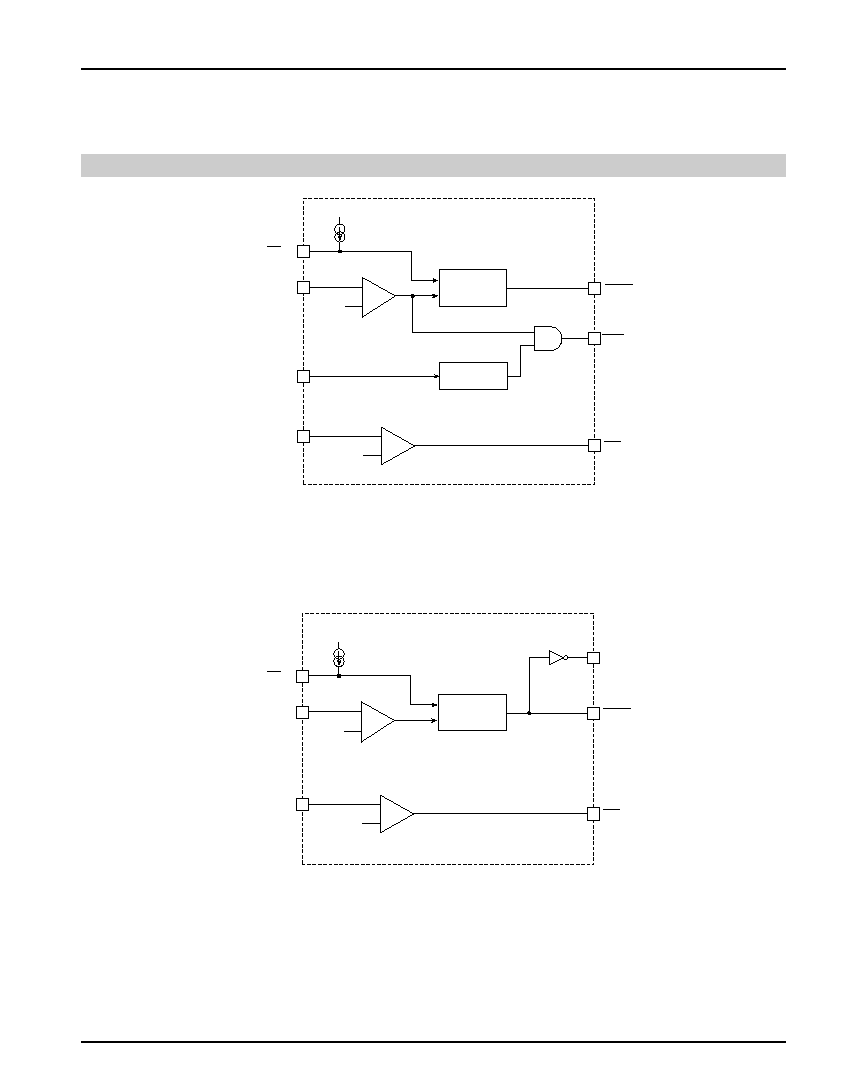

+

-

VTHR*

RESET

GENERATOR

+

-

1.25V

WATCHDOG

TIMER

VCC (2)

MR (1)

PFO (5)

RESET (7)

WDO (8)

WDI (6)

PFI (4)

VCC

250•A

(RESET for MIC706P)

+

-

VTHR*

RESET

GENERATOR

+

-

1.25V

VCC (2)

MR (1)

PFO (5)

RESET (7)

PFI (4)

VCC

RESET (8)

250•A

Figure 1. MIC706 Block Diagram

Figure 2. MIC708 Block Diagram

Block Diagram

* 2.63, 2.93, or 3.08V

* 2.63, 2.93, or 3.08V

MIC706P/R/S/T, MIC708R/S/T

µ

P Supervisory Circuits