MOSEL VITELIC

1

V62C31161024

64K x 16 STATIC RAM

PRELIMINARY

INFORMATION

V62C31161024 Rev. 1.5 September 1999

Features

s

High-speed: 35, 70 ns

s

Ultra low DC operating current of 4mA (max.)

≠ TTL Standby: 0.5 mA (Max.)

≠ CMOS Standby: 10

µ

A (Max.)

s

Fully static operation

s

All inputs and outputs directly TTL compatible

s

Three state outputs

s

Ultra low data retention current (V

CC

= 2V)

s

Extended Operating Voltage: 2.7V ≠ 3.6V

s

Packages

≠ 44-pin TSOP (Standard)

≠ 44-pin 400 mil SOJ

Description

The V62C31161024 is a 1,048,576-bit static

random-access memory organized as 65,536

words by 16 bits. It is built with MOSEL VITELIC's

high performance CMOS process. Inputs and

three-state outputs are TTL compatible and allow

for direct interfacing with common system bus

structures.

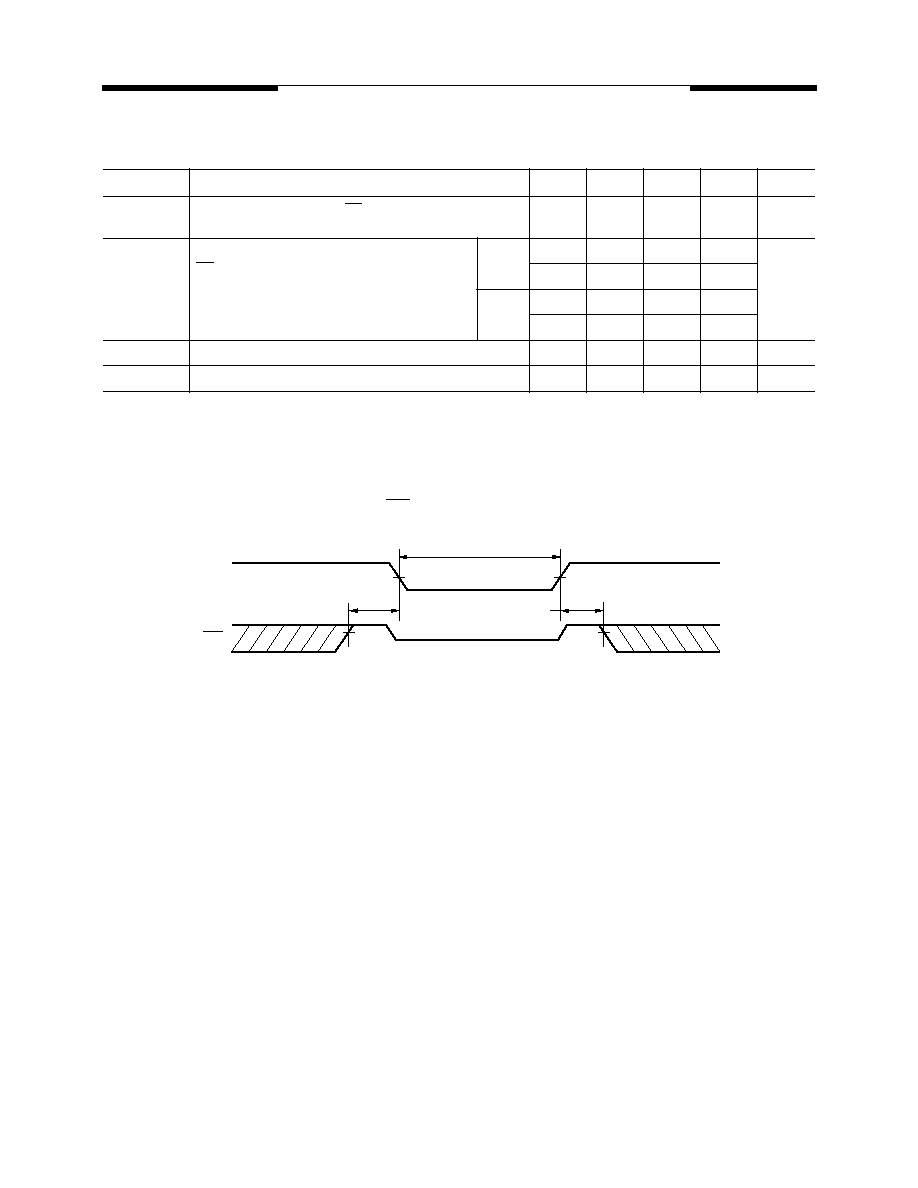

Device Usage Chart

Operating

Temperature

Range

Package Outline Access Time (ns) Power

Temperature

Mark

T K 35 70 L LL

0

∞

C to 70

∞

C ∑ ∑ ∑ ∑ ∑ ∑ Blank

≠40

∞

C to +85

∞

C

∑

∑

∑

∑

I

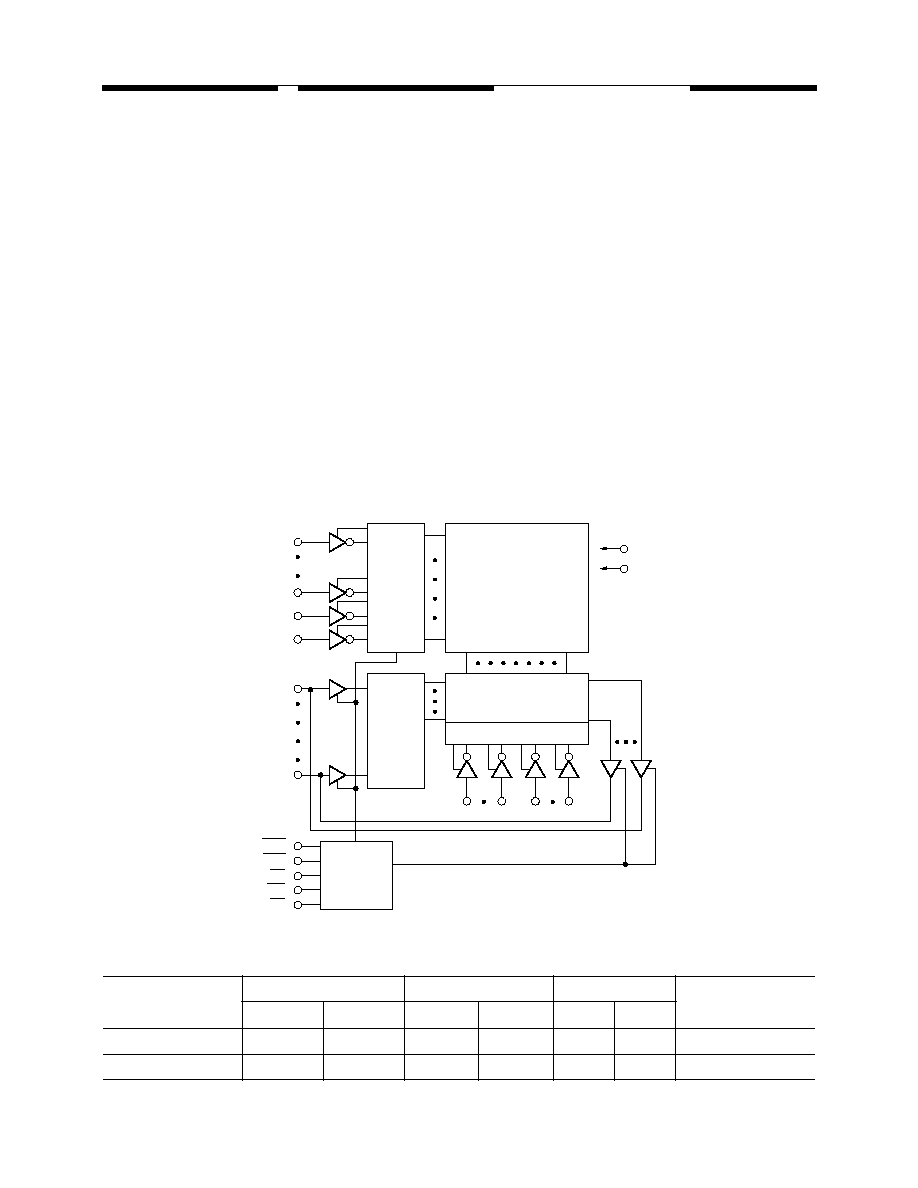

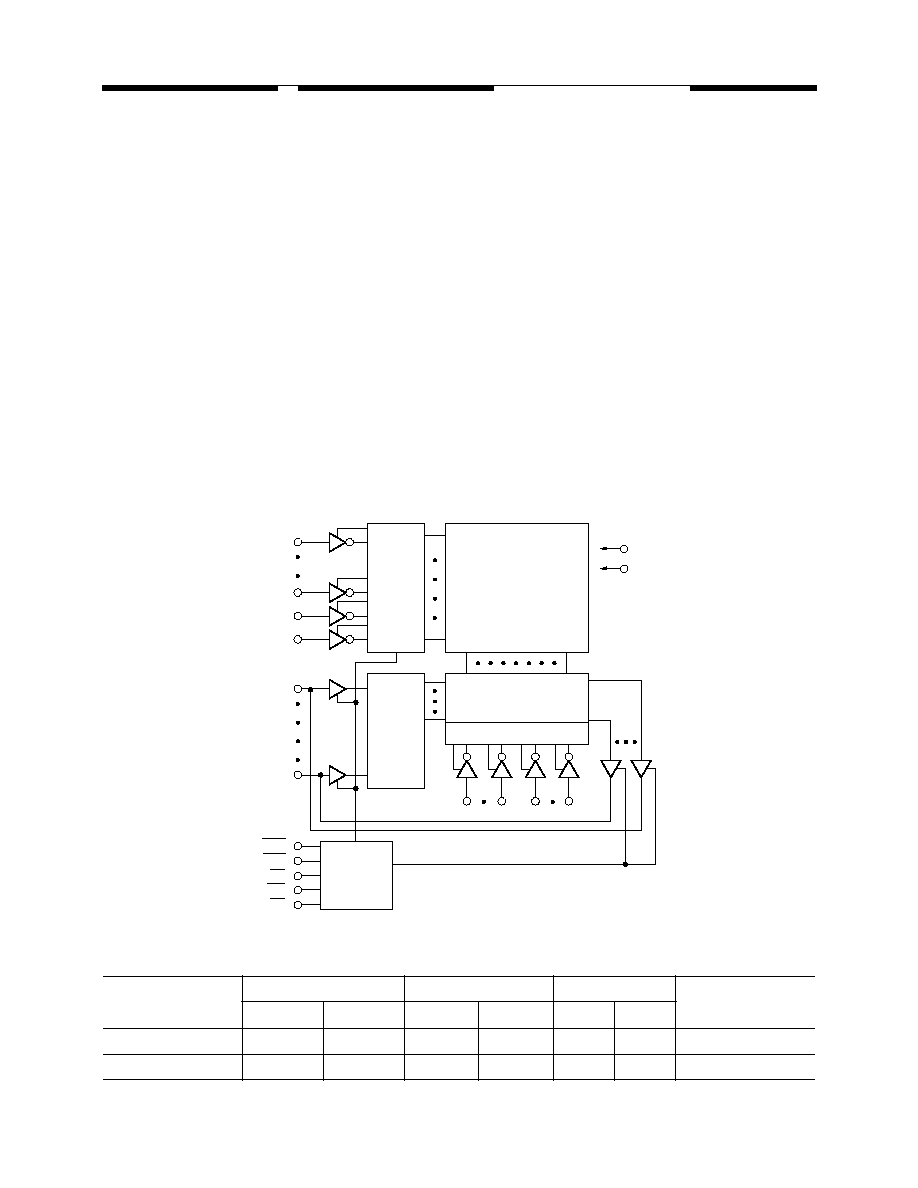

Functional Block Diagram

Row

Decoder

1024 x 1024

Memory Array

Input

Data

Circuit

Column I/O

Column Decoder

Control

Circuit

V

CC

GND

A

0

31161024-01

A

15

A

11

A

7

I/O

0

I/O

15

LBE

OE

WE

UBE

A

8

A

10

A

12

A

14

CE

2

V62C31161024 Rev. 1.5 September 1999

MOSEL VITELIC

V62C31161024

Pin Descriptions

A

0

≠A

15

Address Inputs

These 16 address inputs select one of the 64K x 16

bit segments in the RAM.

CE

Chip Enable Input

CE is active LOW. It must be active to read from or

write to the device. If chip enable is not active, the

device is deselected and is in a standby power

mode. The I/O pins will be in the high-impedance

state when deselected.

OE

Output Enable Input

The output enable input is active LOW. When OE

is Low with CE Low and WE High, data will be pre-

sented on the I/O pins. The I/O pins will be in the

high impedance state when OE is High.

UBE, LEB

Byte Enable

Active low inputs. These inputs are used to enable

the upper or lower data byte.

WE

Write Enable Input

The write enable input is active LOW and controls

read and write operations. With the chip enabled,

when WE is HIGH and OE is LOW, output data will

be present at the I/O pins; when WE is LOW and

OE is HIGH, the data present on the I/O pins will be

written into the selected memory locations.

I/O

0

≠I/O

15

Data Input and Data Output Ports

These 16 bidirectional ports are used to read data

from and write data into the RAM.

V

CC

Power Supply

GND Ground

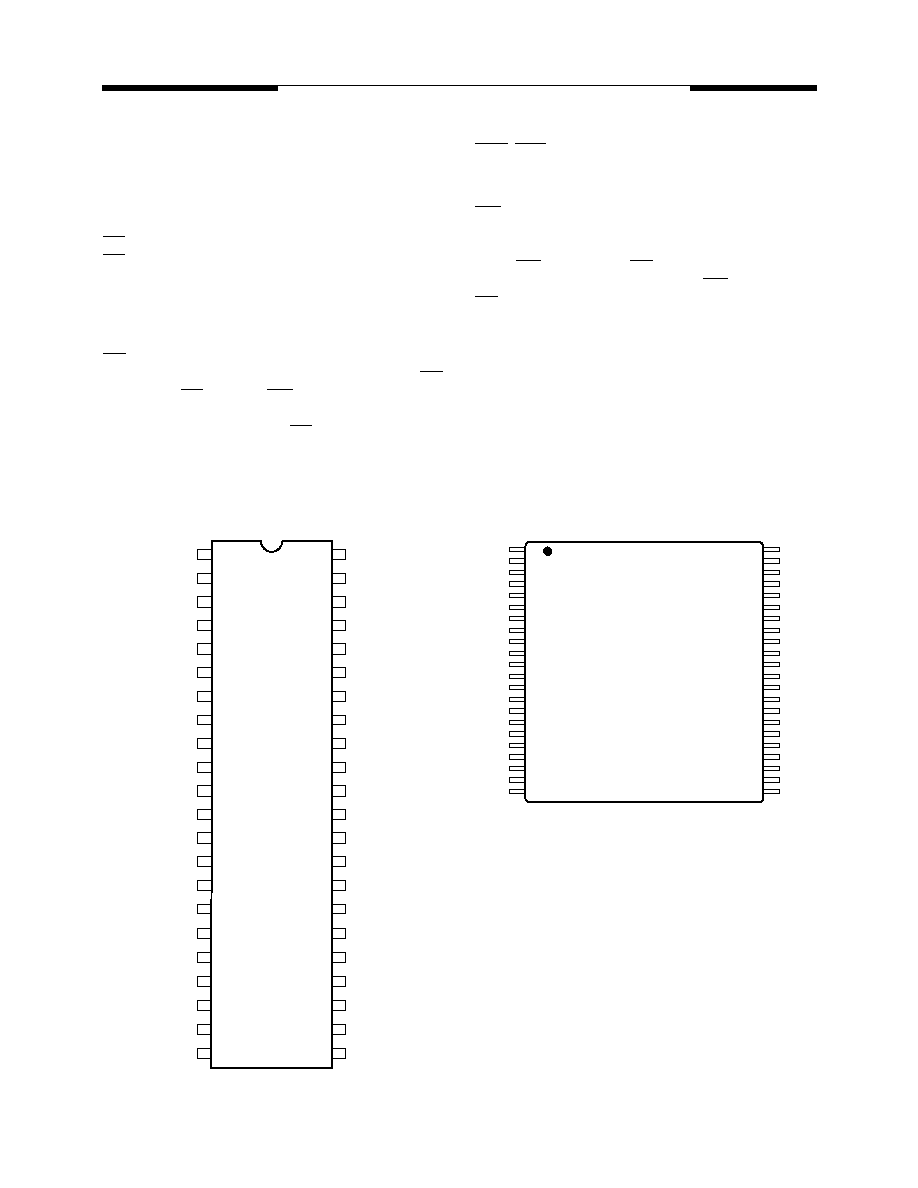

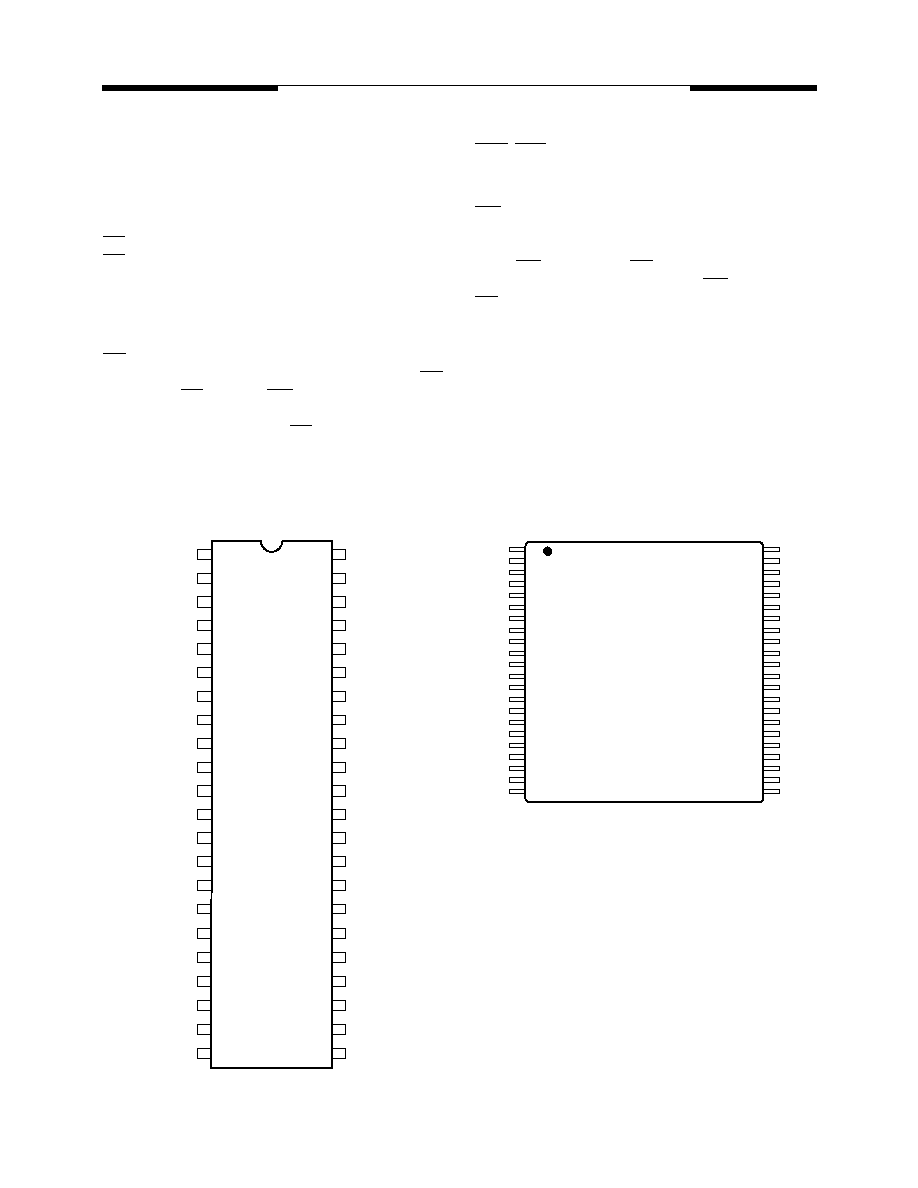

Pin Configurations (Top View)

44-Pin SOJ 44-Pin TSOP-II (Standard)

1

44

31161024-02

2 43

3 42

4

41

5

40

6 39

7 38

8

37

9

36

10 35

11 34

12 33

13 32

14 31

15 30

16 29

A

3

A

4

A

2

A

1

A

0

CE

I/O

0

I/O

1

I/O

2

I/O

3

V

CC

GND

I/O

4

I/O

5

I/O

6

I/O

7

WE

A

6

A

7

OE

UBE

LBE

I/O

15

I/O

14

I/O

13

I/O

12

V

CC

GND

I/O

11

I/O

10

I/O

9

I/O

8

17 28

A

15

NC

18 27

A

14

A

8

19 26

A

13

A

9

20 25

A

12

A

10

21 24

NC

A

11

22 23

NC

A

5

A4

A3

A2

A1

A0

CE

I/O0

I/O1

I/O2

I/O3

VCC

GND

I/O4

I/O5

I/O6

I/O7

WE

A15

A14

A13

A12

NC

A5

A6

A7

OE

UBE

LBE

I/O15

I/O14

I/O13

I/O12

GND

VCC

I/O11

I/O10

I/O9

I/O8

NC

A8

A9

A10

A11

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

31161024-03

MOSEL VITELIC

V62C31161024

3

V62C31161024 Rev. 1.5 September 1999

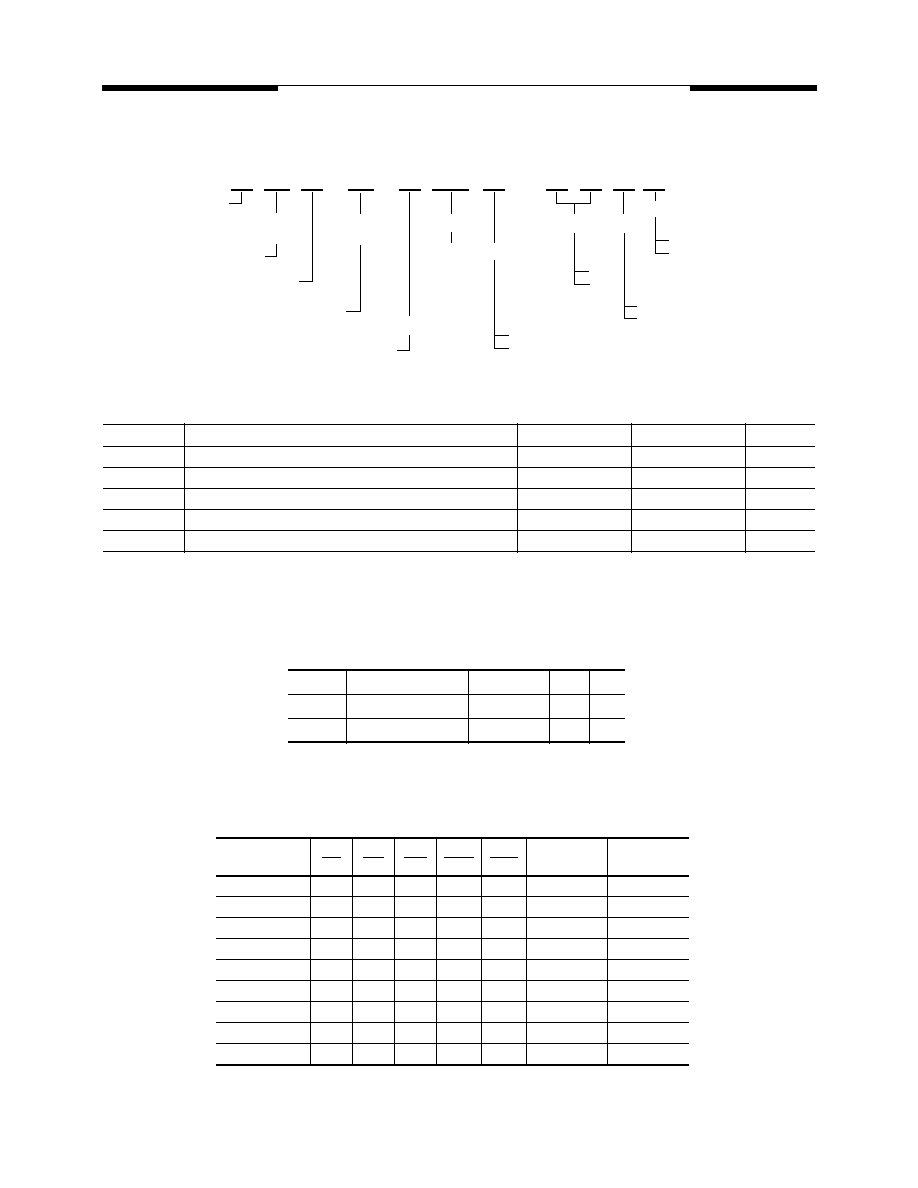

Part Number Information

Absolute Maximum Ratings

(1)

NOTE:

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Symbol Parameter Commercial Industrial Units

V

CC

Supply Voltage -0.5 to V

CC

+ 0.5 -0.5 to V

CC

+ 0.5 V

V

N

Input Voltage -0.5 to V

CC

+ 0.5 -0.5 to V

CC

+ 0.5 V

V

DQ

Input/Output Voltage Applied V

CC

+ 0.3 V

CC

+ 0.3 V

T

BIAS

Temperature Under Bias -10 to +125 -65 to +135

∞

C

T

STG

Storage Temperature -55 to +125 -65 to +150

∞

C

SRAM

FAMILY

C = CMOS PROCESS

62 = STANDARD

31 = 2.7V ≠ 3.6V

OPERATING

VOLTAGE

1024K

ORGANIZATION

PKG

SPEED

31161024-04

62 C 16

31 1024 ≠

MOSEL-VITELIC

MANUFACTURED

V

16 = 16-bit

35 ns

70 ns

TEMP.

BLANK = 0

∞

C to 70

∞

C

I = -40

∞

C to +85

∞

C

T = TSOP STANDARD

K = 400 mil SOJ

DENSITY

PWR.

L = LOW POWER

LL = DOUBLE LOW POWER

Capacitance*

T

A

= 25

∞

C, f = 1.0MHz

NOTE:

1. This parameter is guaranteed and not tested.

Symbol Parameter Conditions Max. Unit

C

IN

Input Capacitance V

IN

= 0V 6 pF

C

OUT

Output Capacitance V

I/O

= 0V 8 pF

Truth Table

NOTE:

X = Don't Care, L = LOW, H = HIGH

Mode CE

OE

WE

UBE

LBE

I/O

8-15

Operation

I/O

0-7

Operation

Standby H X X X X High Z High Z

Output Disable L X X H H High Z High Z

Output Disable L H H X X High Z High Z

Read L L H L L D

OUT

D

OUT

Read L L H L H D

OUT

High Z

Read L L H H L High Z D

OUT

Write L X L L L D

IN

D

IN

Write L X L L H D

IN

High Z

Write L X L H L High Z D

IN

4

V62C31161024 Rev. 1.5 September 1999

MOSEL VITELIC

V62C31161024

DC Electrical Characteristics

(over all temperature ranges, V

CC

= 2.7V≠3.6V)

NOTES:

1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

2. V

IL

(Min.) = -3.0V for pulse width < 20ns.

3. f

MAX

= 1/t

RC

.

4. Maximum values.

Symbol Parameter Test Conditions Min. Typ. Max. Units

V

IL

Input LOW Voltage

(1,2)

-0.3 -- 0.4 V

V

IH

Input HIGH Voltage

(1)

2.2 -- V

CC

+ 0.3 V

I

IL

Input Leakage Current V

CC

= Max, V

IN

= 0V to V

CC

-1 -- 1

µ

A

I

OL

Output Leakage Current V

CC

= Max, CE = V

IH

, V

OUT

= 0V to V

CC

-1 -- 1

µ

A

V

OL

Output LOW Voltage V

CC

= Min, I

OL

= 2.1mA -- -- 0.4 V

V

OH

Output HIGH Voltage V

CC

= Min, I

OH

= -1mA 2.4 -- -- V

Symbol Parameter Power Com.

(4)

Ind. Units

I

CC

Operating Power Supply Current, CE = V

IL

,

Output Open, V

CC

= Max., f = 0

L

4

5

mA

LL 3 4

I

CC1

Average Operating Current, CE

1

= V

IL

, Output Open,

V

CC

= Max., f = f

MAX

(3)

60 80 mA

I

SB

TTL Standby Current

CE

V

IH

, V

CC

= Max., f = f

MAX

(3)

L

4

6

mA

LL 3 5

I

SB1

CMOS Standby Current, CE

V

CC

≠ 0.2V,

V

IN

V

CC

≠ 0.2V or V

IN

0.2V, V

CC

= Max., f = 0

L

50

60

µ

A

LL 10 15

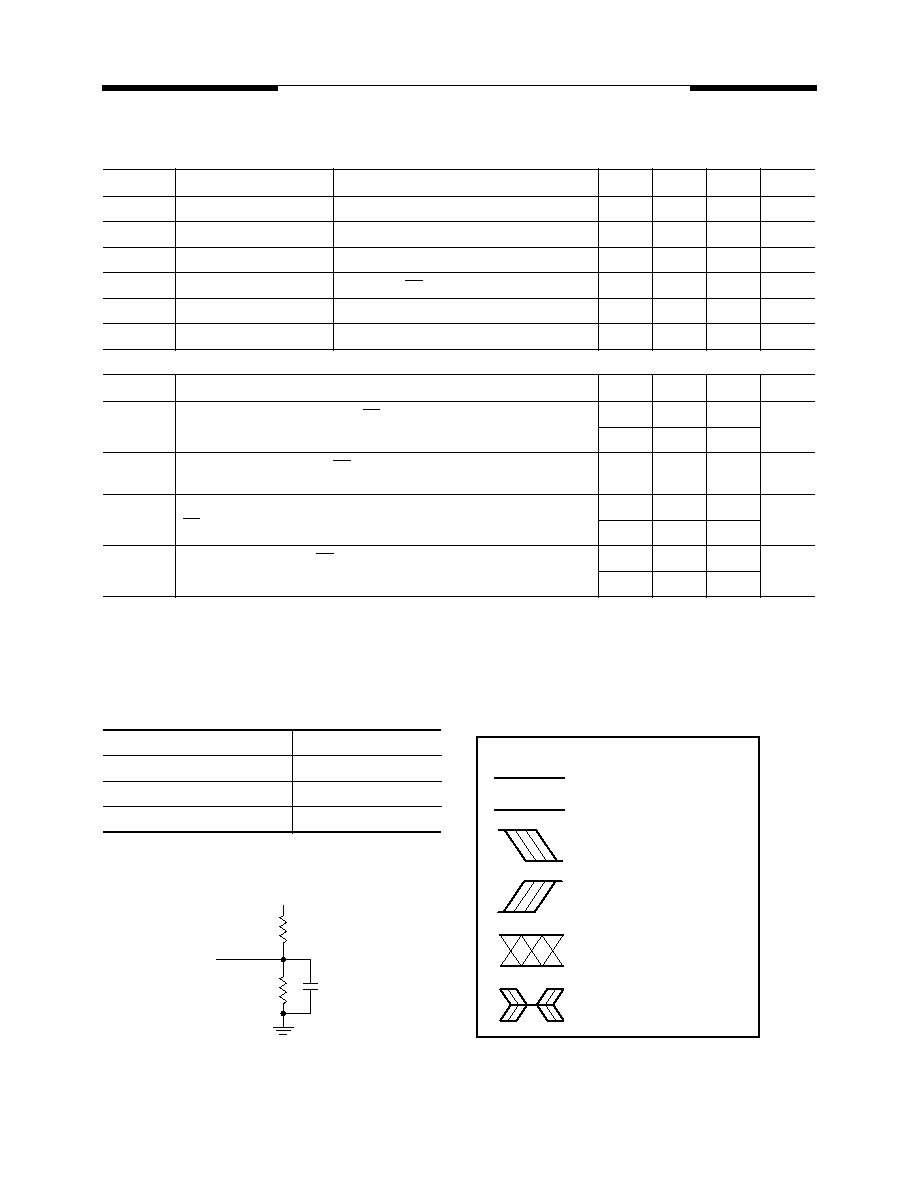

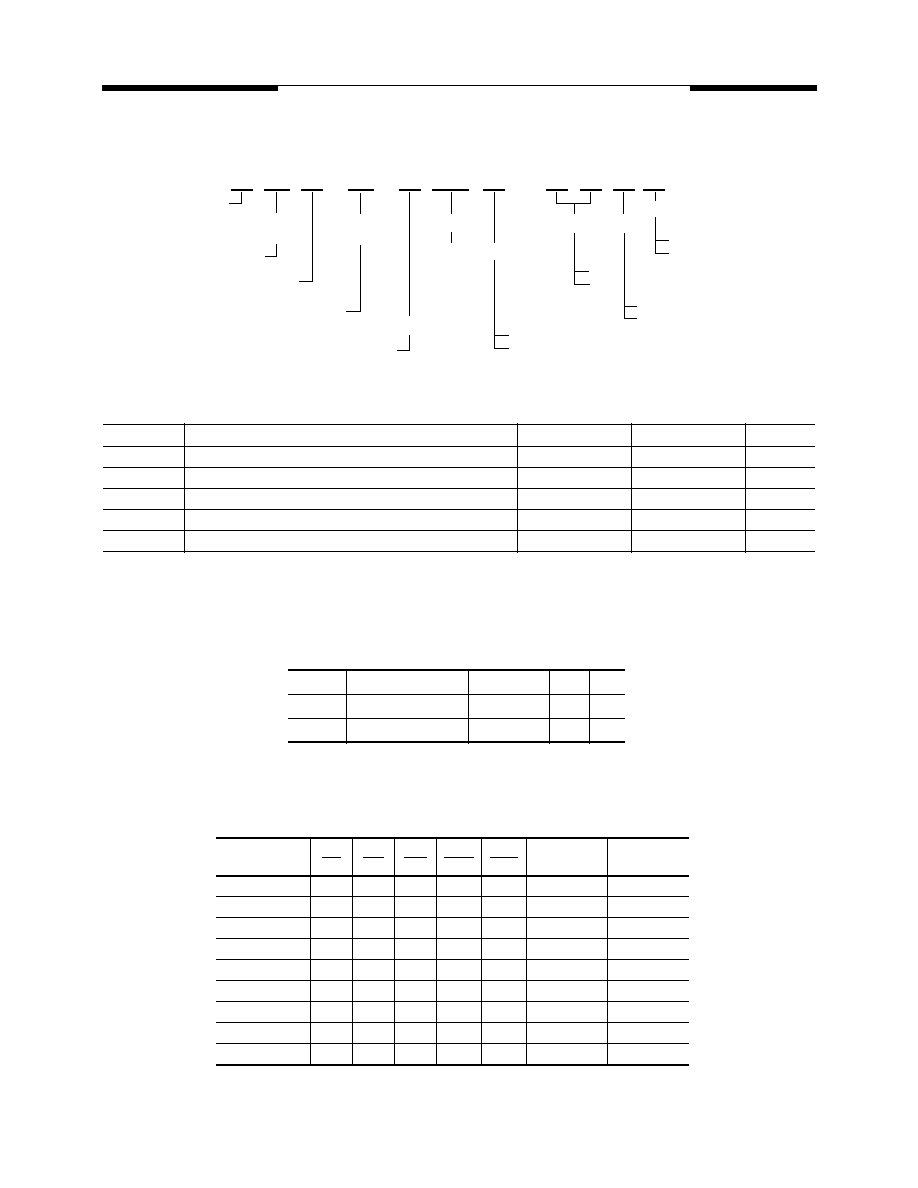

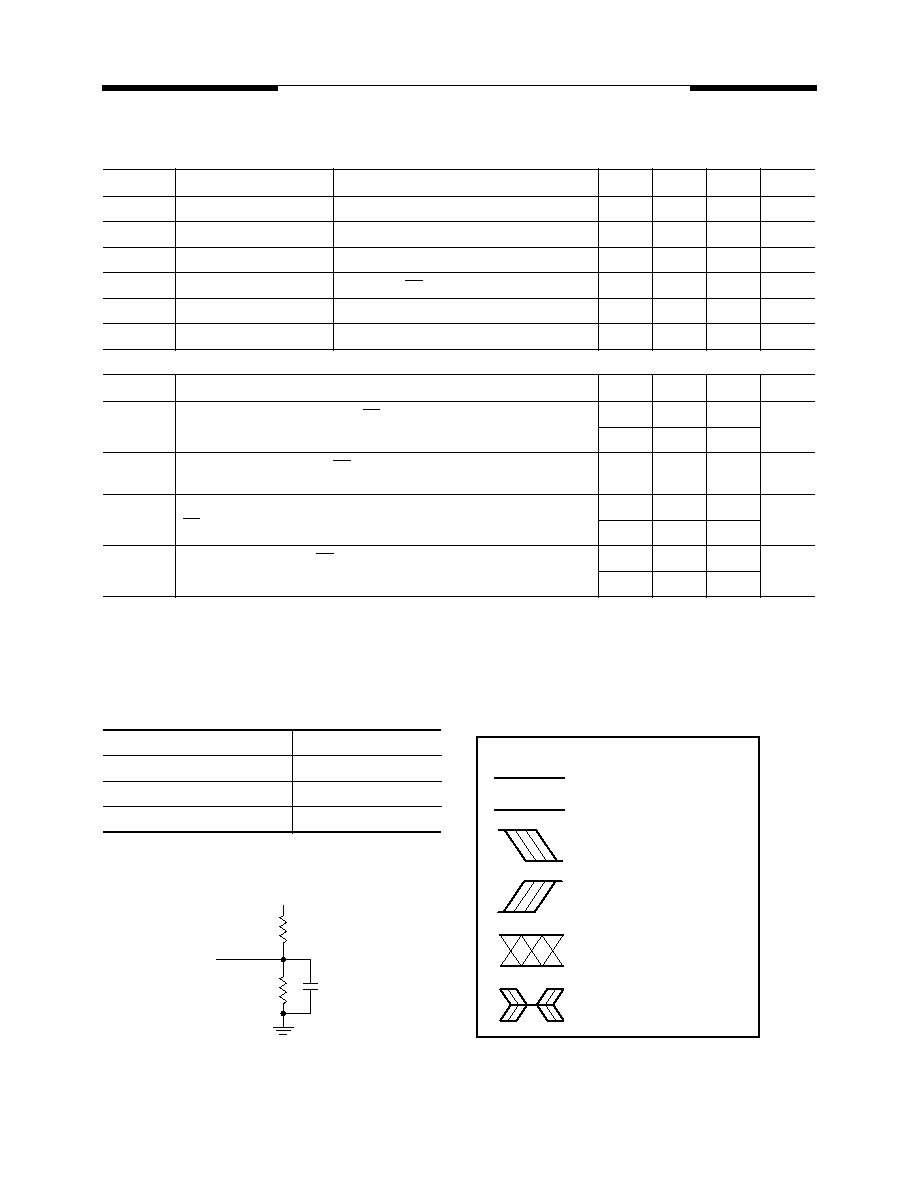

AC Test Conditions

AC Test Loads and Waveforms

Key to Switching Waveforms

Input Pulse Levels 0 to 3V

Input Rise and Fall Times 5 ns

Timing Reference Levels 1.5V

Output Load see below

+5V

1800

990

* Includes scope and jig capacitance

I/O Pins

C

L

= 30 pF*

31161024-05

WAVEFORM INPUTS OUTPUTS

MUST BE

STEADY

WILL BE

STEADY

MAY CHANGE

FROM H TO L

WILL BE

CHANGING

FROM H TO L

MAY CHANGE

FROM L TO H

WILL BE

CHANGING

FROM L TO H

DON'T CARE:

ANY CHANGE

PERMITTED

CHANGING:

STATE

UNKNOWN

DOES NOT

APPLY

CENTER

LINE IS HIGH

IMPEDANCE

"OFF" STATE

MOSEL VITELIC

V62C31161024

5

V62C31161024 Rev. 1.5 September 1999

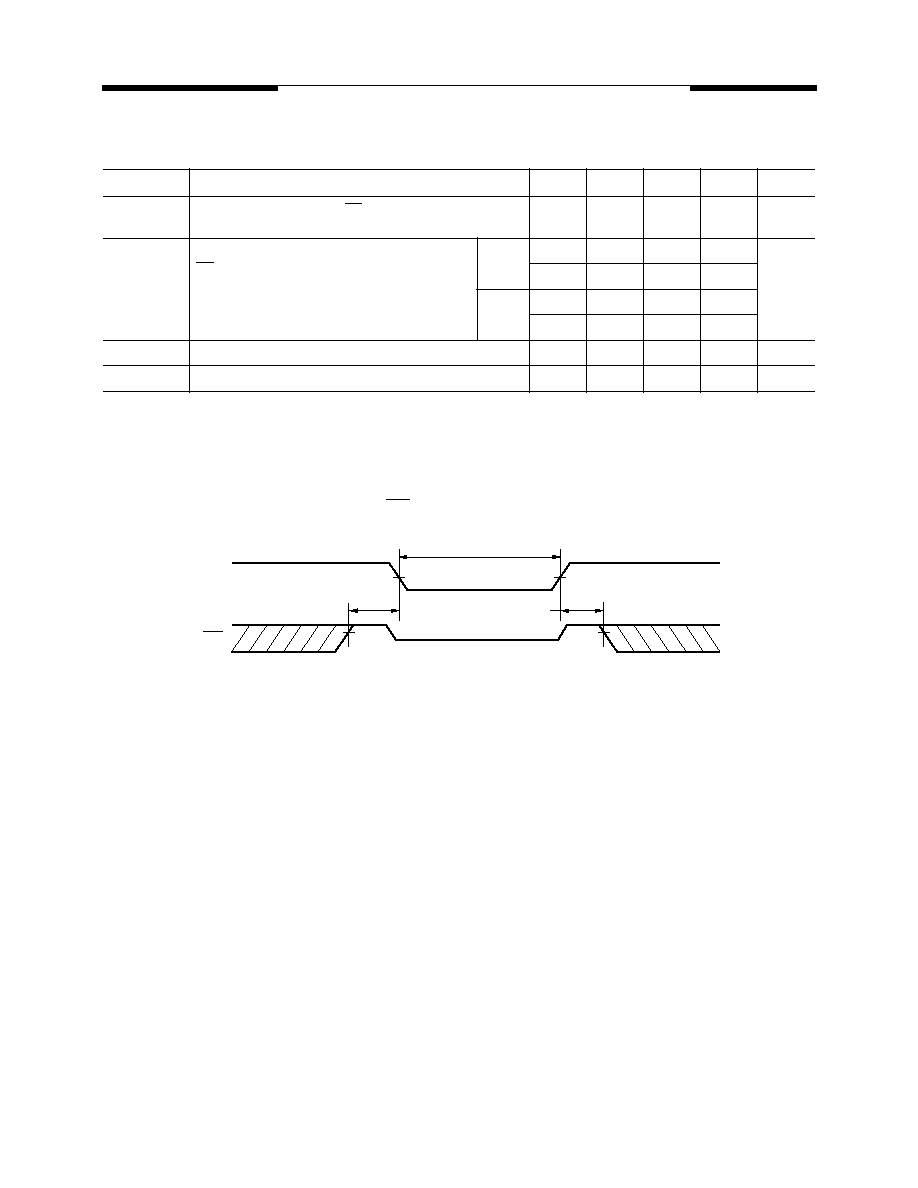

Data Retention Characteristics

NOTES:

1. t

RC

= Read Cycle Time

2. T

A

= +25

∞

C.

Low V

CC

Data Retention Waveform (CE Controlled)

Symbol Parameter Power Min. Typ.

(2)

Max. Units

V

DR

V

CC

for Data Retention CE

V

CC

≠ 0.2V, V

IN

V

CC

≠ 0.2V,

or V

IN

0.2V

2.0 -- 3.6 V

I

CCDR

Data Retention Current

CE

V

DR

≠0.2V, V

IN

V

CC

≠ 0.2V, or V

IN

0.2V

Com'l L -- 1 50

µ

A

LL -- 0.5 10

Ind. L -- -- 100

LL -- -- 15

t

CDR

Chip Deselect to Data Retention Time 0 -- -- ns

t

R

Operation Recovery Time (see Retention Waveform) t

RC

(1)

--

--

ns

V

CC

31161024-06

Data Retention Mode

CE

V

CC

≠ 0.2V

CE

2.2V 2.2V

2.7V

t

CDR

t

R

V

DR

2V 2.7V