| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CS5830 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

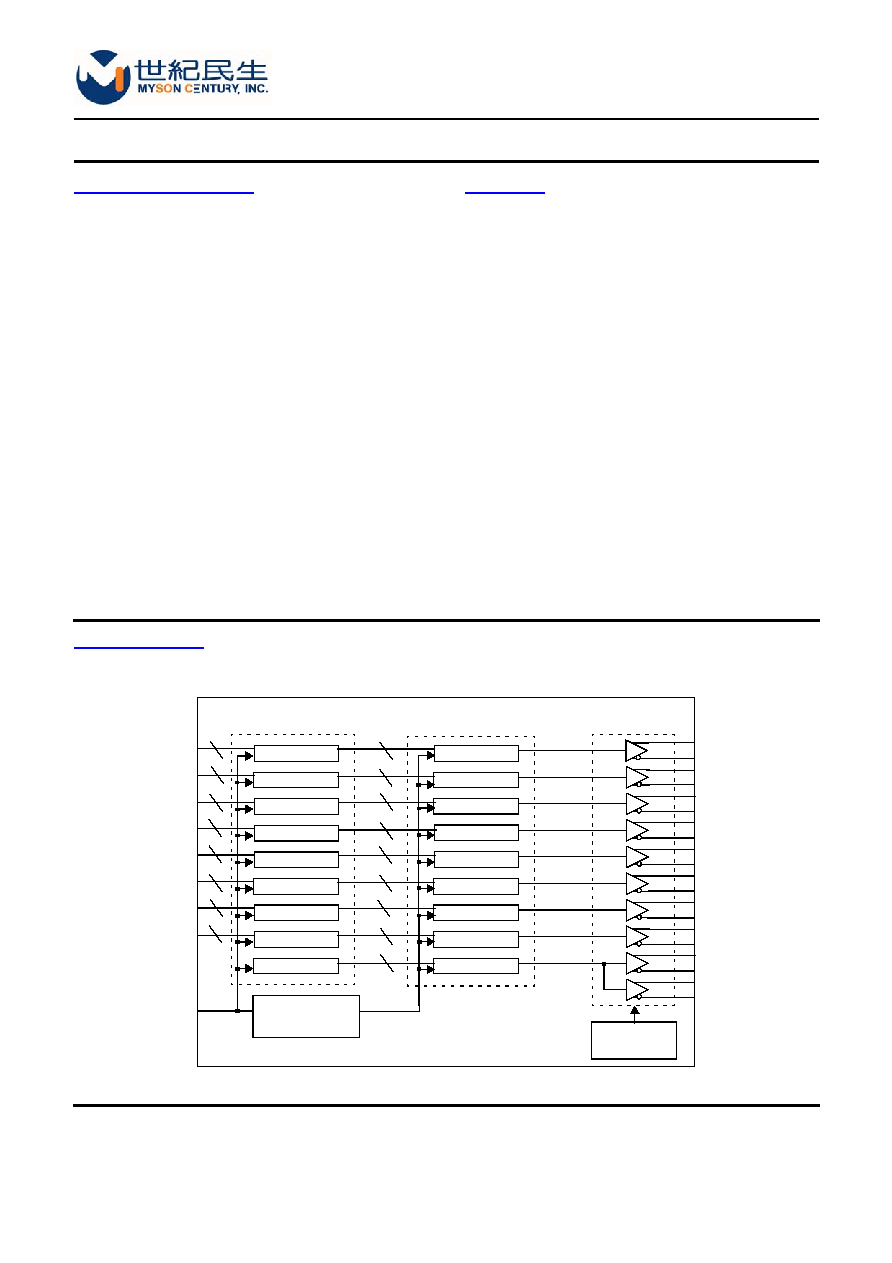

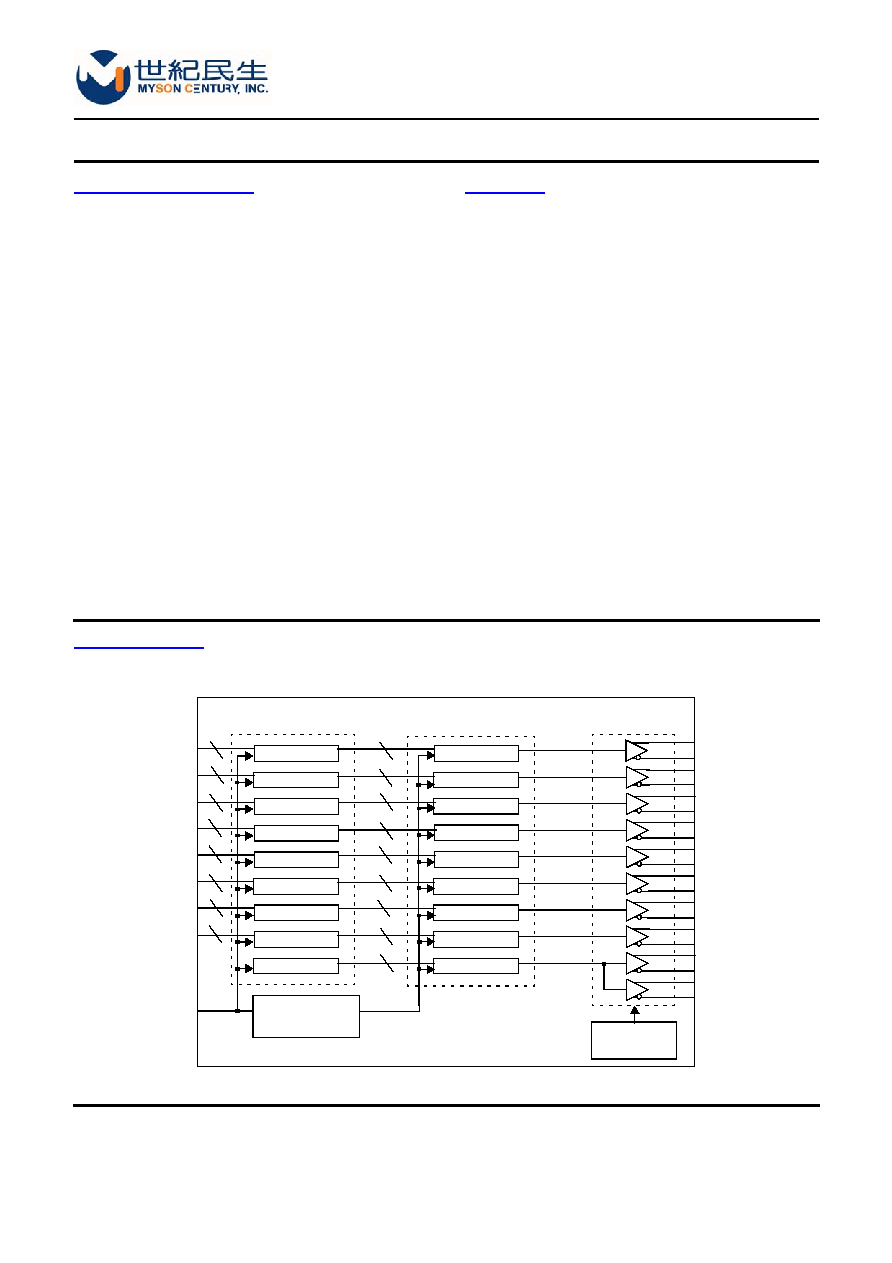

BLOCK DIAGRAM

GENERAL DESCRIPTION

FEATURES

CS5830

Dual Pixel LVDS Display Interface (LDI) Transmitter

USA:

4020 Moorpark Avenue, Suite 115

San Jose, CA, 95117

Tel: 408-243-8388 Fax: 408-243-3188

Sales@myson.com.tw

www.myson.com.tw

Rev.1.0 August 2002

page 1 of 19

Myson Century, Inc.

Taiwan:

No. 2, Industry East Rd. III,

Science-Based Industrial Park, Hsin-Chu, Taiwan

Tel: 886-3-5784866 Fax: 886-3-5784349

The CS5830 converts 48 bits (Dual pixel 24-bit

color) of CMOS/TTL data into 8 LVDS (Low Voltage

Differential Signalling) data streams. Control signals

(VSYNC, HSYNC, DE and two user-defined signals)

are sent during blanking intervals.

The CS5830 provides 3 operating modes: Single-

In-Single-Out, Dual-In-Dual-Out and Single-In-Dual-

Out. In Single-In-Single-Out and Dual-In-Dual-Out

modes, single pixel data can be clocked into CS5830

at a maximum rate of 85MHz. In Single-In-Dual-Out

mode, CS5830 supports a maximum clock rate of

170MHz.

DC balancing on a cycle-to-cycle basis, is also

provided to reduce ISI (Inter-Symbol Interference).

With DC balancing, a low distortion eye-pattern is

provided at the receiver end of the cable.

∑ Complies with OpenLDI specification for digital

display interface.

∑ 30 to 85 (170)MHz clock support.

∑ Supports SVGA through UXGA panel resolutions.

∑ Drives long, low cost cables.

∑ DC balance data transmission to reduce ISI

distortion.

∑ Supports single and dual pixel GUI interface

∑ Rejects cycle-to-cycle jitter.

∑ 5V tolerant on data and control input pins.

∑ Programmable data and control strobe select

(rising or falling edge strobe)

∑ Support for two additional user-defined control

signals in DC balanced mode

∑ Compatible with TIA/EIA LVDS standard.

∑ 100-pin LQFP.

DATA_DCBAL

DATA_DCBAL

DATA_DCBAL

DATA_DCBAL

DATA_DCBAL

DATA_DCBAL

DATA_DCBAL

DATA_DCBAL

CLK_DCBAL

PLL

P2S

P2S

P2S

P2S

P2S

P2S

P2S

P2S

P2S

CLK

7xCLK

REF

OutBuf

CS5830

page 2 of 19

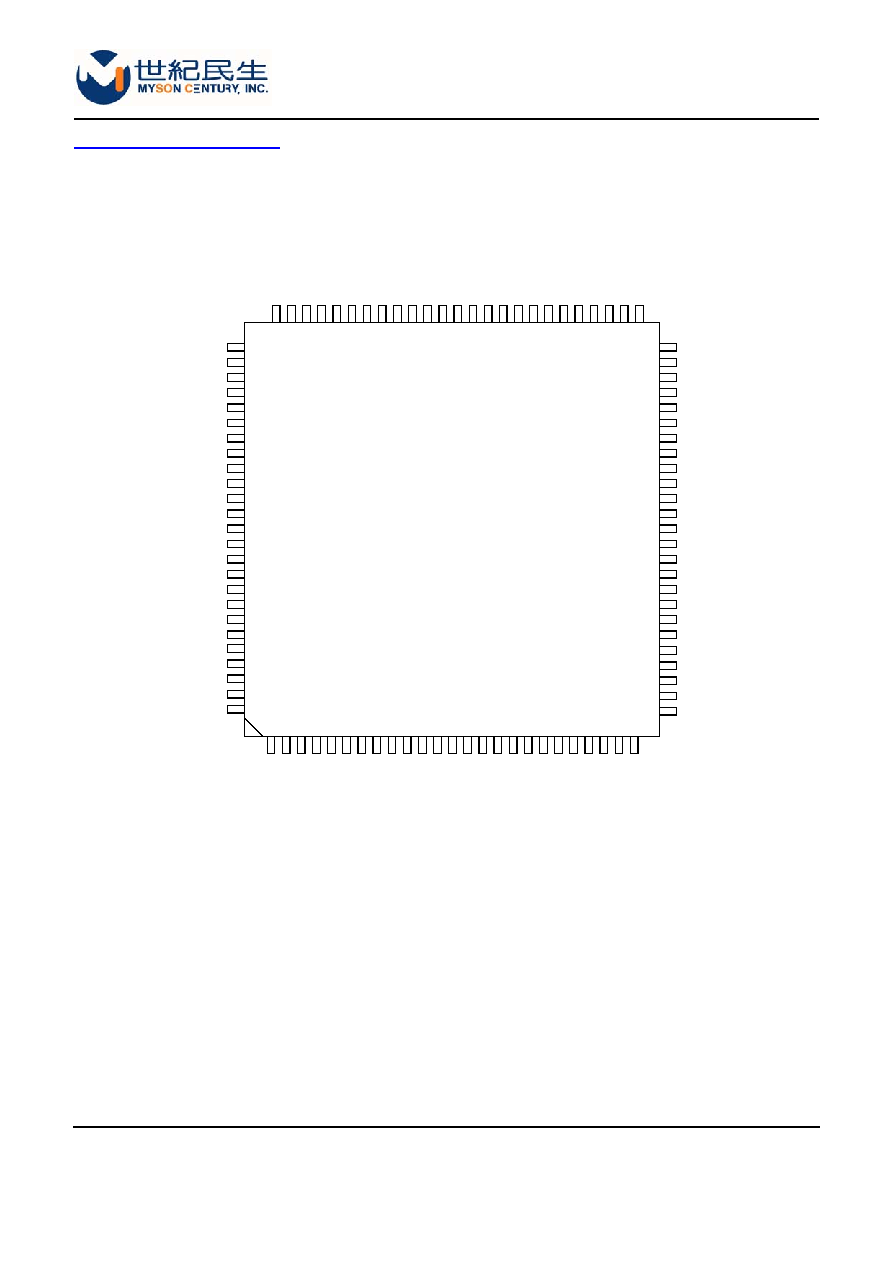

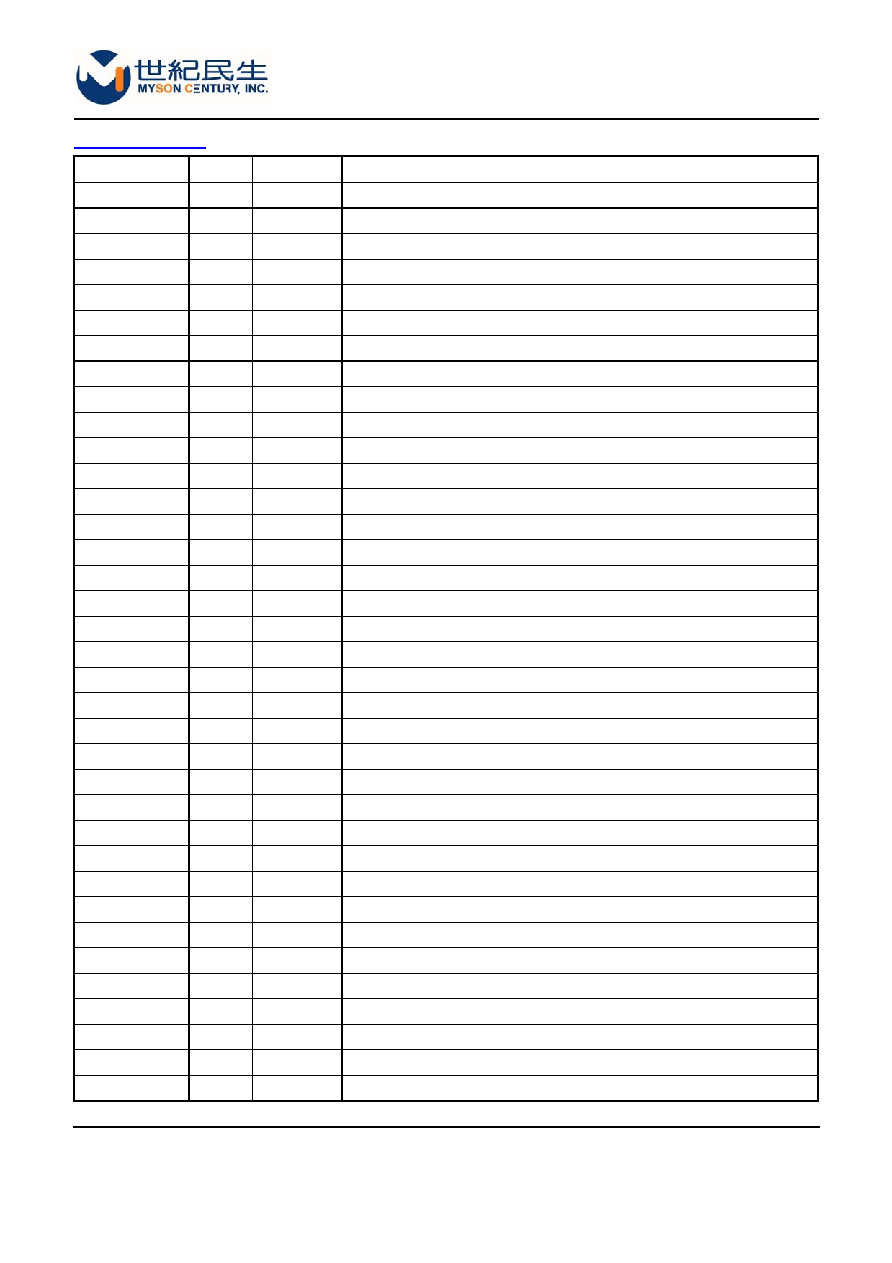

PIN CONNECTION DIAGRAM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

TXOM0

TXOP0

LVDSVdd

TXOM1

TXOP1

TXOM2

TXOP2

LVDSVss

TXCLKM

TXCLKP

LVDSVdd

TXOM3

TXOP3

TXOM4

TXOP4

LVDSVss

TXOM5

TXOP5

TXOM6

TXOP6

LVDSVdd

TXOM7

TXOP7

TXCLKM2

TXCLKP2

TXIN30

TXIN29

TXIN28

TXIN27

TXIN26

TXIN25

Vdd

Vss

TXIN24

TXIN23

TXIN22

TXIN21

TXIN20

TXIN19

TXIN18

TXIN17

TXIN16

TXIN15

TXIN14

TXIN13

TXIN12

Vdd

Vss

TXIN11

TXIN10

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

TX

IN31

TX

IN32

TX

IN33

TX

IN34

TX

IN35

TX

IN36

TX

IN37

Vss

Vdd

TX

IN38

TX

IN39

TX

IN40

TX

IN41

TX

IN42

TX

IN43

TX

IN44

TX

IN45

TX

IN46

TX

IN47

DE

VS

ync

HS

ync

Vdd

Vss

LV

D

S

V

s

s

TX

IN9

TX

IN8

TX

IN7

TX

IN6

TX

IN5

TX

IN4

TX

IN3

TX

IN2

TX

IN1

TX

IN0

TX

CLKI

N

PLL

V

dd

Vss

PR

E

PLL

S

E

L

PLL

V

ss

PLL

V

ss

PLL

V

dd

PLL

V

ss

R_FB

R_FD

E

PD

B

Dual

BA

L

LV

D

S

V

s

s

CS5830

CS5830

page 3 of 19

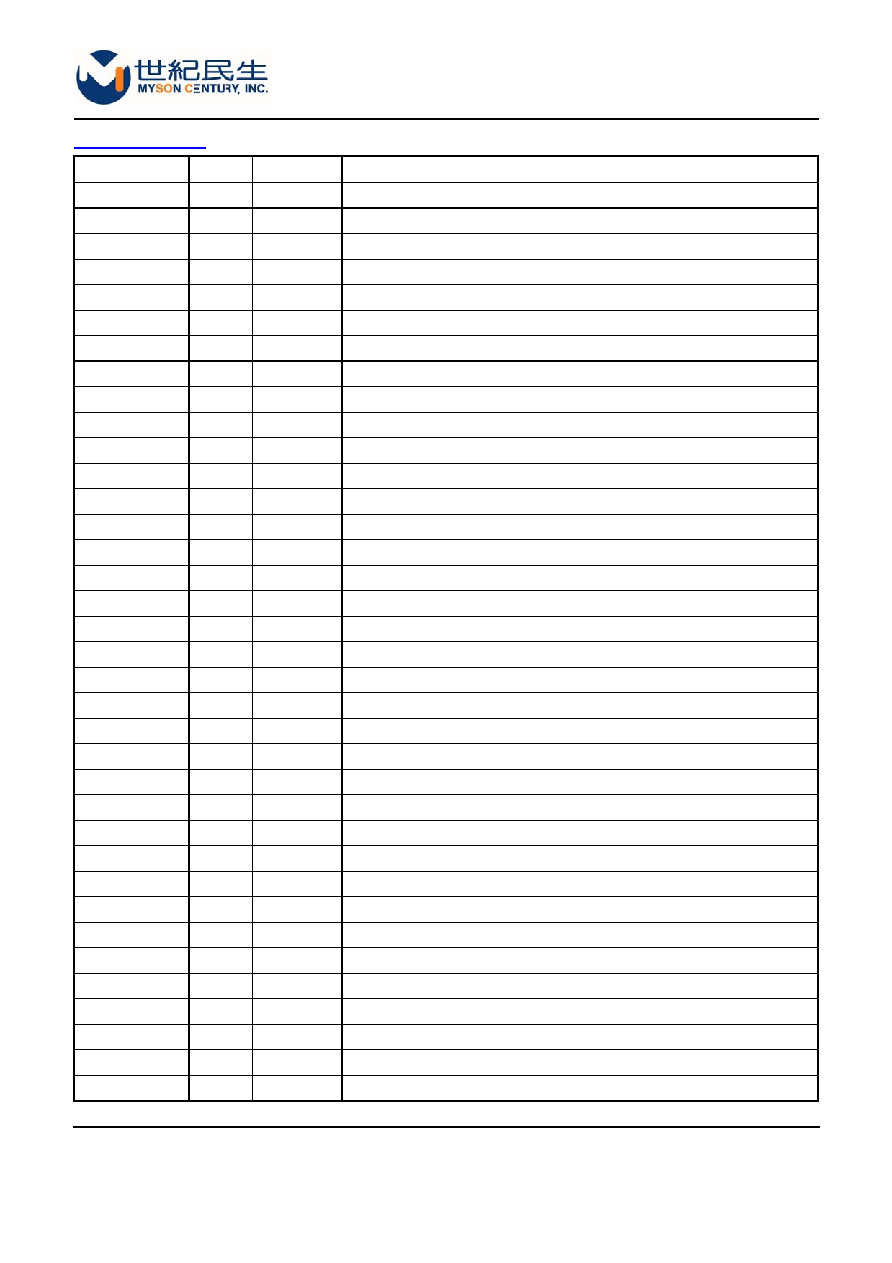

PIN DESCRIPTION

Name

I/O

Pin

Description

TXIN0

I

10

TTL level input. R10.

TXIN1

I

9

TTL level input. R11.

TXIN2

I

8

TTL level input. R12.

TXIN3

I

7

TTL level input. R13.

TXIN4

I

6

TTL level input. R14.

TXIN5

I

5

TTL level input. R15.

TXIN6

I

4

TTL level input. R16.

TXIN7

I

3

TTL level input. R17.

TXIN8

I

2

TTL level input. G10.

TXIN9

I

1

TTL level input. G11.

TXIN10

I

100

TTL level input. G12.

TXIN11

I

99

TTL level input. G13.

TXIN12

I

96

TTL level input. G14.

TXIN13

I

95

TTL level input. G15.

TXIN14

I

94

TTL level input. G16.

TXIN15

I

93

TTL level input. G17.

TXIN16

I

92

TTL level input. B10.

TXIN17

I

91

TTL level input. B11.

TXIN18

I

90

TTL level input. B12.

TXIN19

I

89

TTL level input. B13.

TXIN20

I

88

TTL level input. B14.

TXIN21

I

87

TTL level input. B15.

TXIN22

I

86

TTL level input. B16.

TXIN23

I

85

TTL level input. B17.

TXIN24

I

84

TTL level input. R20.

TXIN25

I

81

TTL level input. R21.

TXIN26

I

80

TTL level input. R22.

TXIN27

I

79

TTL level input. R23.

TXIN28

I

78

TTL level input. R24.

TXIN29

I

77

TTL level input. R25.

TXIN30

I

76

TTL level input. R26.

TXIN31

I

75

TTL level input. R27.

TXIN32

I

74

TTL level input. G20.

TXIN33

I

73

TTL level input. G21.

TXIN34

I

72

TTL level input. G22.

TXIN35

I

71

TTL level input. G23.

CS5830

page 4 of 19

TXIN36

I

70

TTL level input. G24.

TXIN37

I

69

TTL level input. G25.

TXIN38

I

66

TTL level input. G26.

TXIN39

I

65

TTL level input. G27.

TXIN40

I

64

TTL level input. B20.

TXIN41

I

63

TTL level input. B21.

TXIN42

I

62

TTL level input. B22.

TXIN43

I

61

TTL level input. B23.

TXIN44

I

60

TTL level input. B24.

TXIN45

I

59

TTL level input. B25.

TXIN46

I

58

TTL level input. B26. CNTLF.

TXIN47

I

57

TTL level input. B27. CNTLE.

DE

I

56

Data Enable.

VSYNC

I

55

V Sync.

HSYNC

I

54

H Sync.

TXOM0

O

50

Negative LVDS differential data output.

TXOP0

O

49

Positive LVDS differential data output.

TXOM1

O

47

Negative LVDS differential data output.

TXOP1

O

46

Positive LVDS differential data output.

TXOM2

O

45

Negative LVDS differential data output.

TXOP2

O

44

Positive LVDS differential data output.

CKOM1

O

42

Negative LVDS differential clock output.

CKOP1

O

41

Positive LVDS differential clock output.

TXOM3

O

39

Negative LVDS differential data output.

TXOP3

O

38

Positive LVDS differential data output.

TXOM4

O

37

Negative LVDS differential data output.

TXOP4

O

36

Positive LVDS differential data output.

TXOM5

O

34

Negative LVDS differential data output.

TXOP5

O

33

Positive LVDS differential data output.

TXOM6

O

32

Negative LVDS differential data output.

TXOP6

O

31

Positive LVDS differential data output.

TXOM7

O

29

Negative LVDS differential data output.

TXOP7

O

28

Positive LVDS differential data output.

CKOM2

O

27

Negative LVDS differential clock output.

CKOP2

O

26

Positive LVDS differential clock output.

BAL

I

24

DC-balanced enable.

Name

I/O

Pin

Description

CS5830

page 5 of 19

DUAL

I

23

Three-mode select. (Internal biasd to Vdd/2)

DUAL Mode Description

H dual pixel All LVDS active

L single pixel TXOP/TXOM 0-3 and CKOP/CKOM 1 active

F single in

dual out

PDB

I

22

Power-down. Active low.

R_FDE

I

21

Programmable DE strobe select.

R_FDE Mode

H DE active high

L DE active low

R_FB

I

20

Programmable data strobe select.

R_FB Mode

H TXIN strobed at TXCLKIN rising edge

L TXIN strobed at TXCLKIN falling edge

PLLSEL

I

15

LVDS channel drive current select.

PLLSEL Mode

H 7.0mA current output

L/F 3.5mA current output

PRE

I

14

Pre-emphasis level select. (CS5830 has NO pre-emphasis circuit

implementation.)

TXCLKIN

I

11

Clock input.

V

dd

I

53, 67, 82

97

Power supply pins for TTL inputs and digital circuits.

V

ss

I

13, 52, 68,

83, 98

Ground pins for TTL inputs and digital circuits.

PLLV

dd

I

12, 18

Power supply pins for PLL and REF.

PLLV

ss

I

16,17,19

Ground pins for PLL and REF.

LVDSV

dd

I

30, 40, 48

Power supply pins for LVDS outputs.

LVDSV

ss

I

25, 35, 43

51

Ground pins for LVDS outputs.

Name

I/O

Pin

Description