Document Outline

- COVER

- DESCRIPTION

- FEATURES

- ORDERING INFORMATION

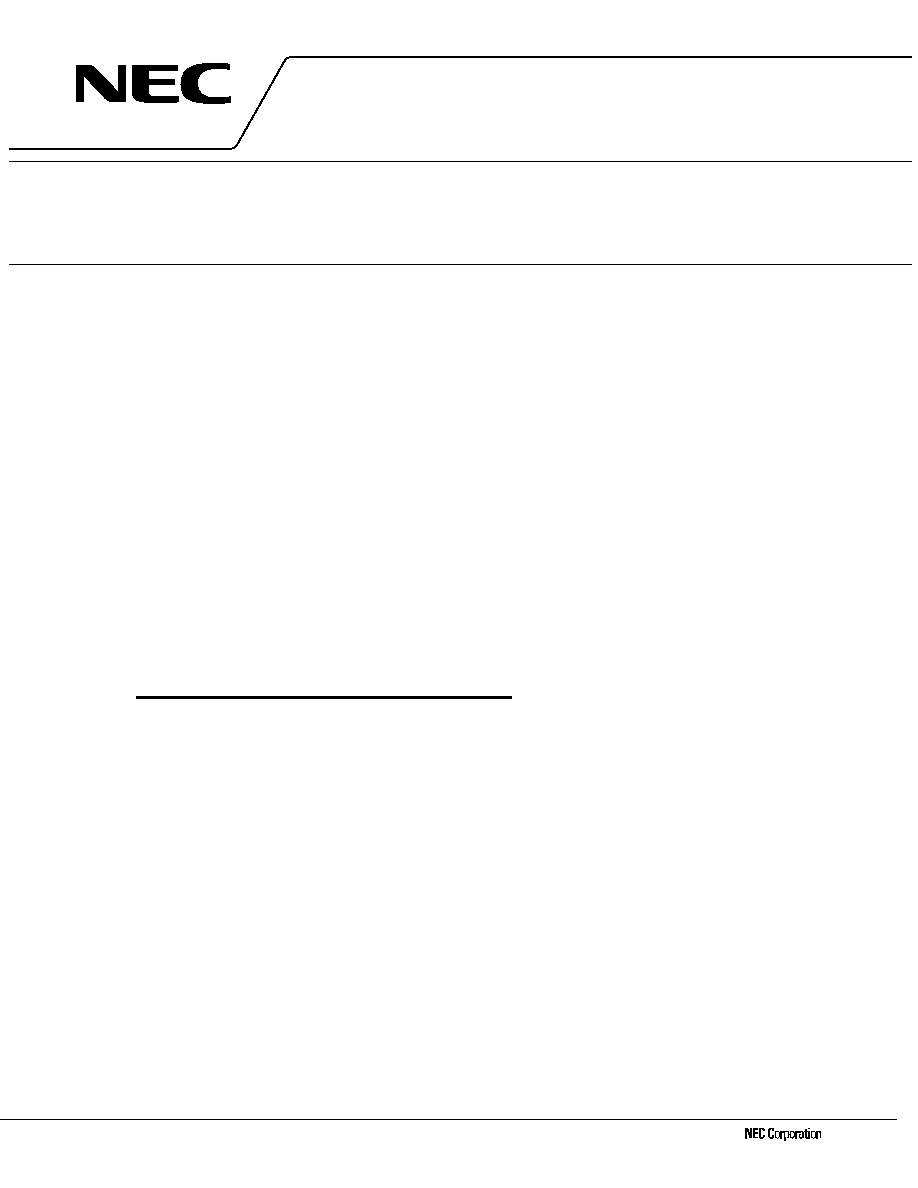

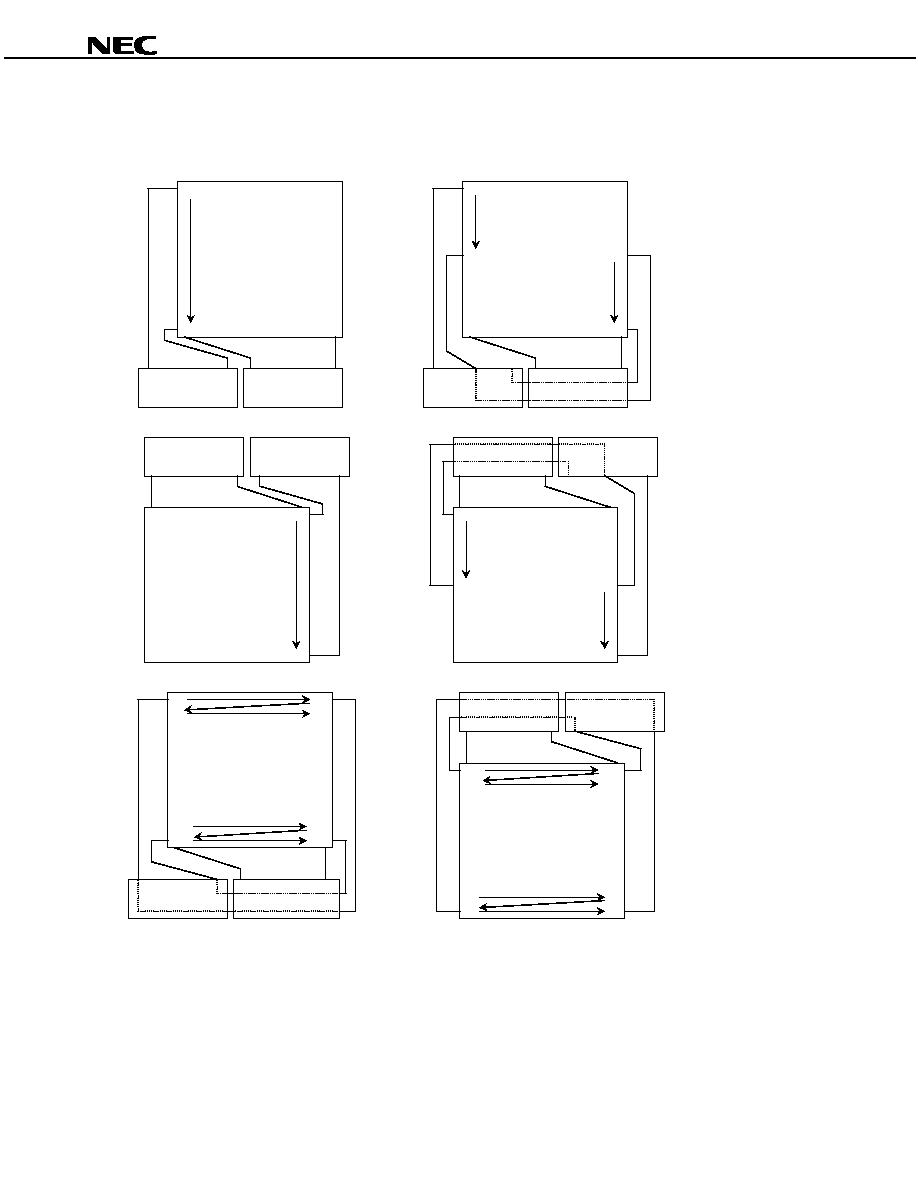

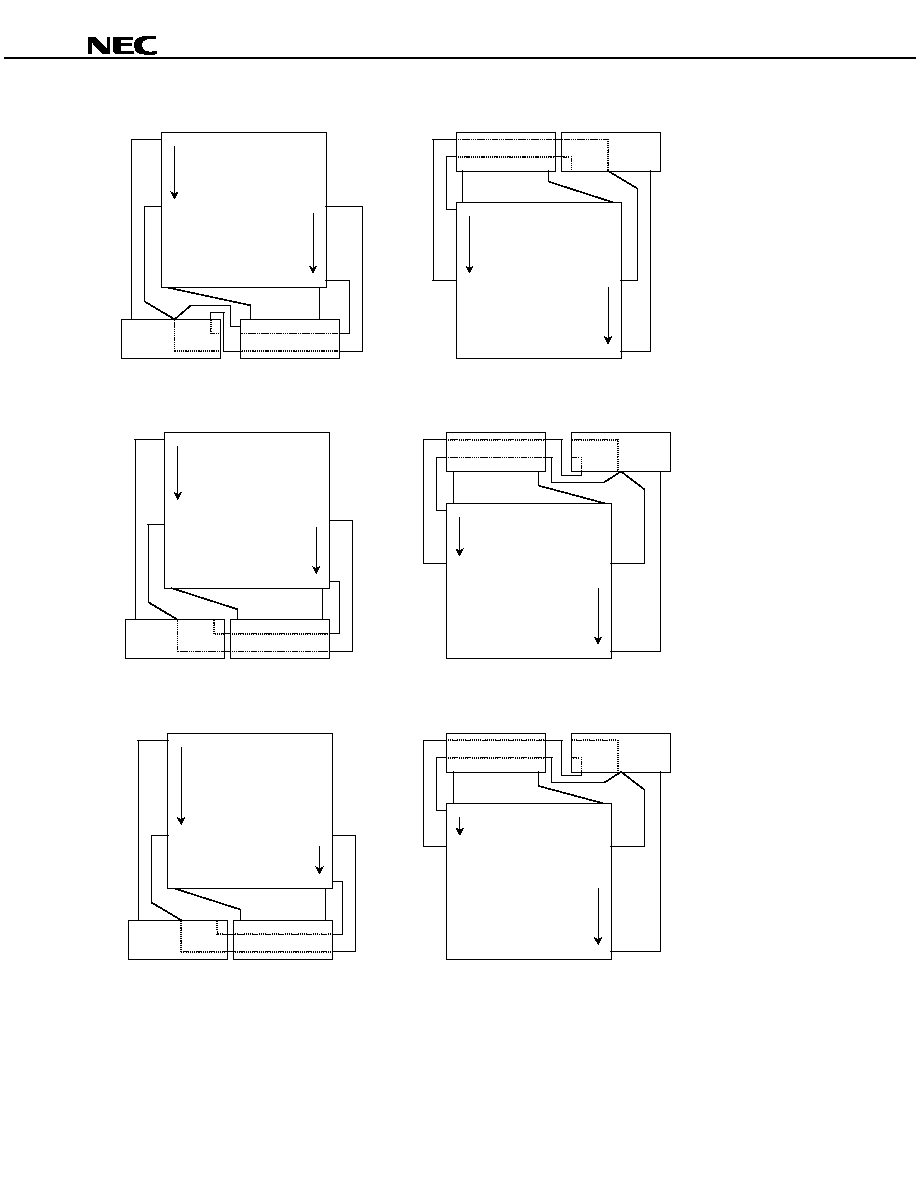

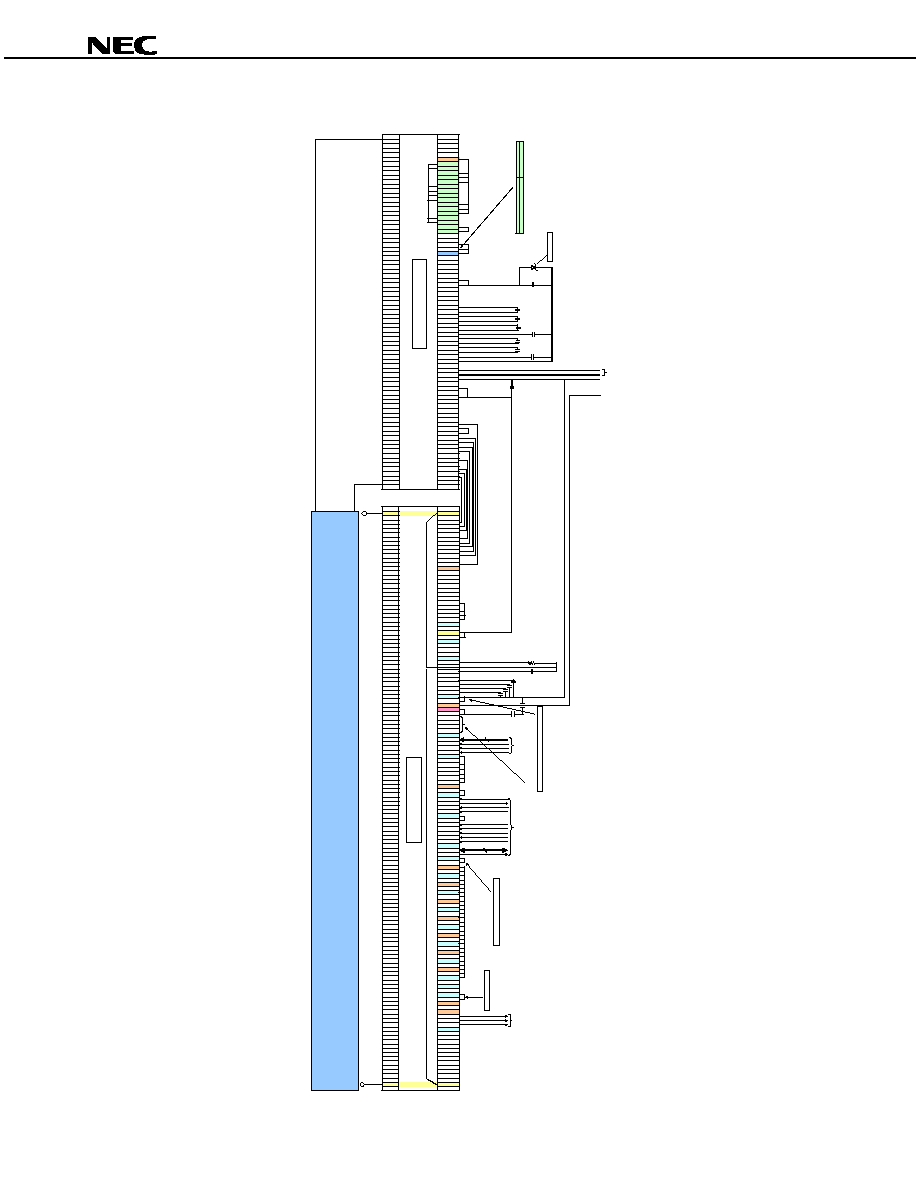

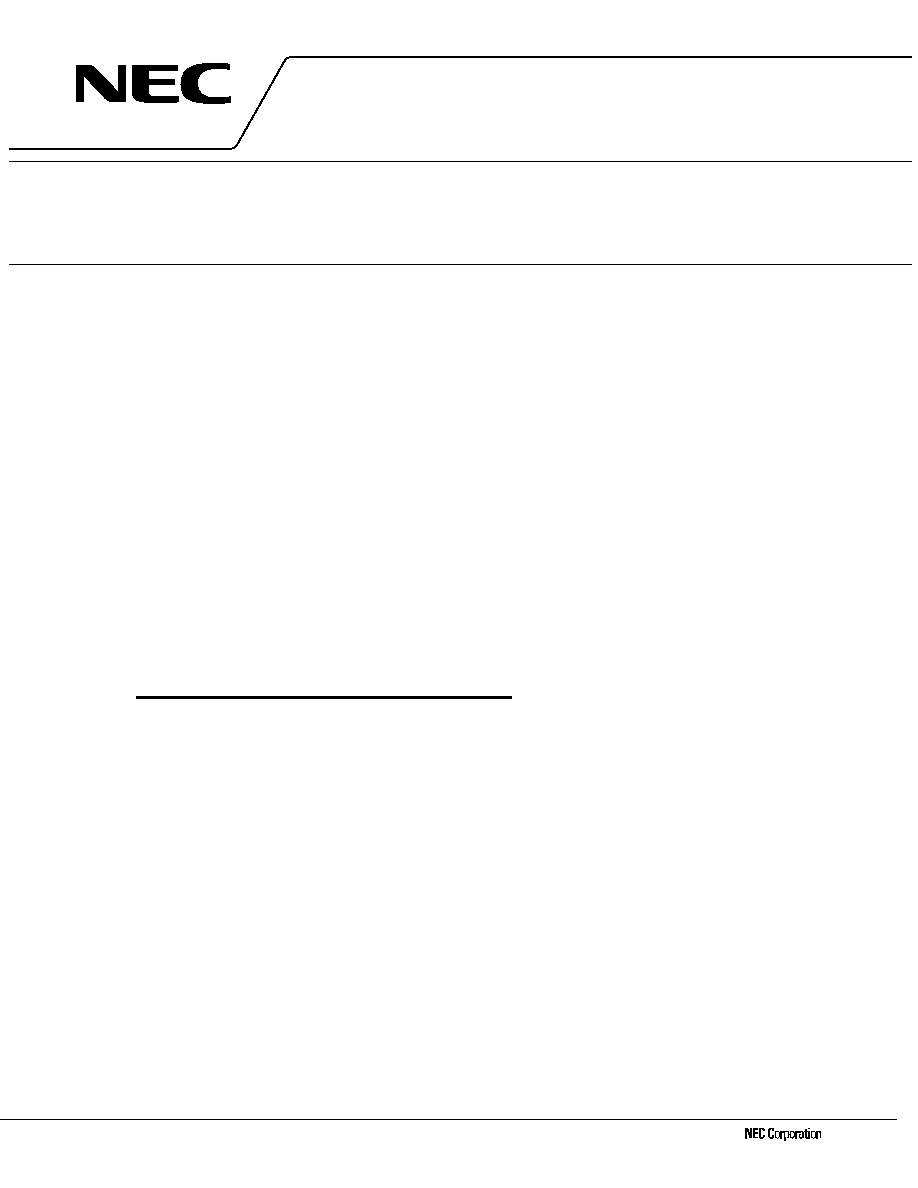

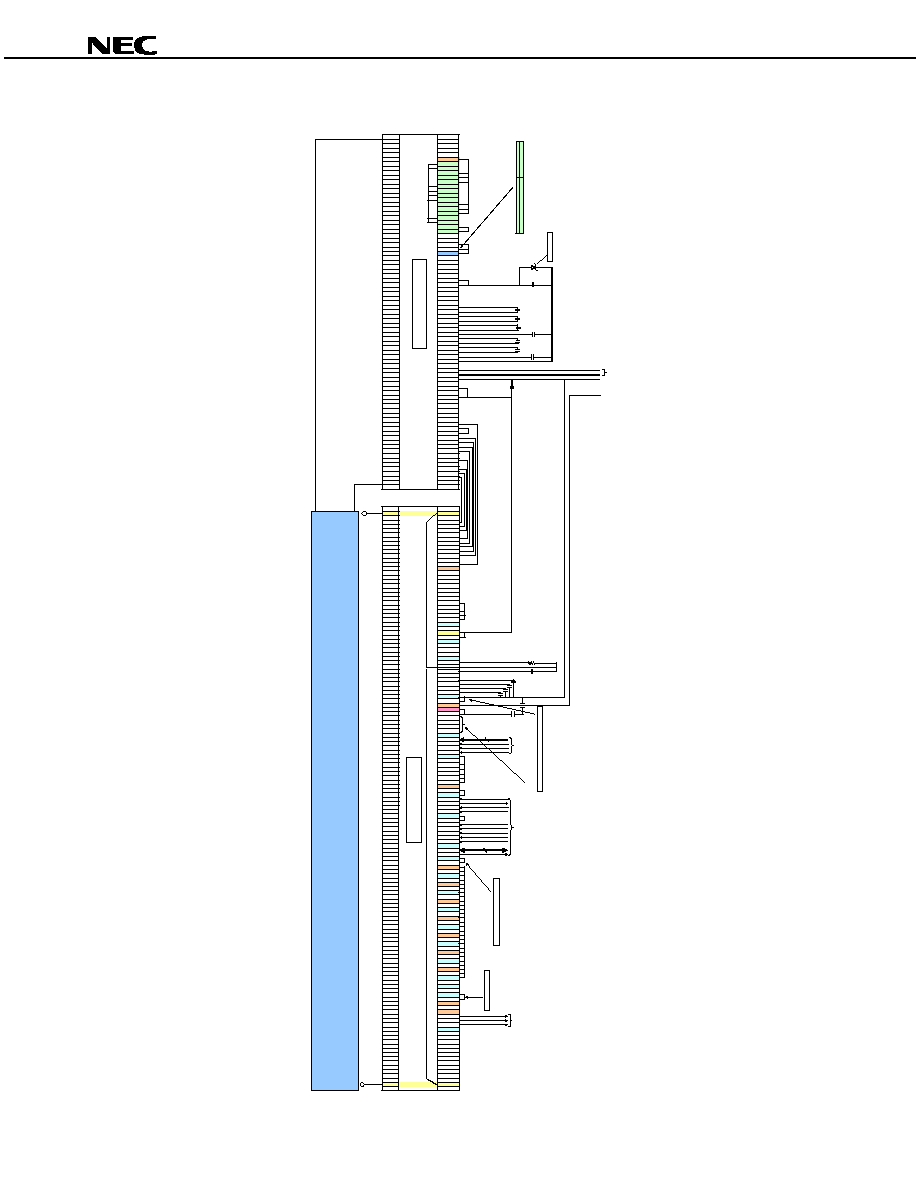

- 1. BLOCK DIAGRAM/SYSTEM DIAGRAM

- 1.1 Boost Voltage Construction

- 1.2 Boost Voltage Auto Start and Rising Order

- 1.3 VS_AMP Circuit

- 1.4 Common Drive Circuit

- 1.5 Variable Boost Steps

- 2. PIN CONFIGURATION (Pad Layout)

- 3. PIN FUNCTIONS

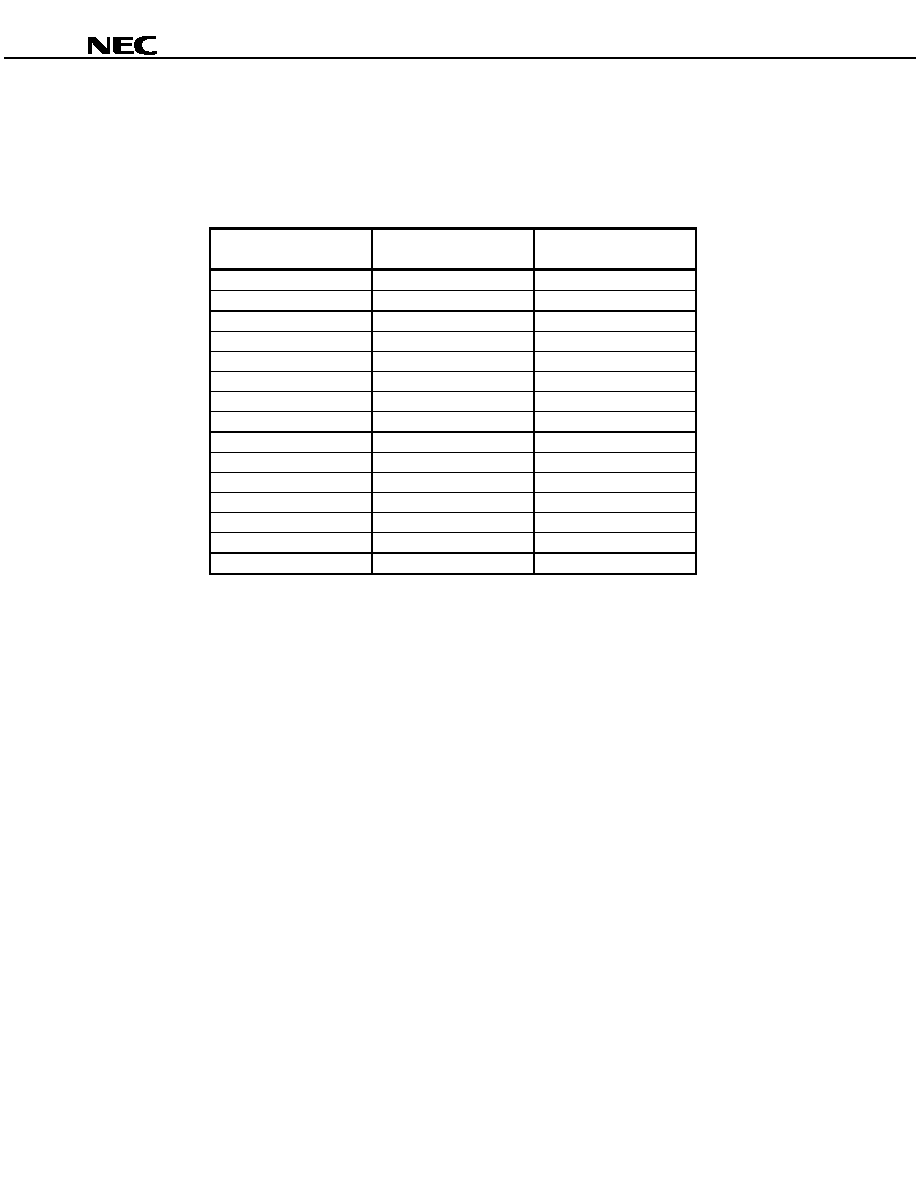

- 4. COMMAND

- 4.1 Command List

- 4.2 Command Description

- 4.3 Command Setting Values When IFSEL = H (When Using Control Pins)

- 5. MODE DESCRIPTION

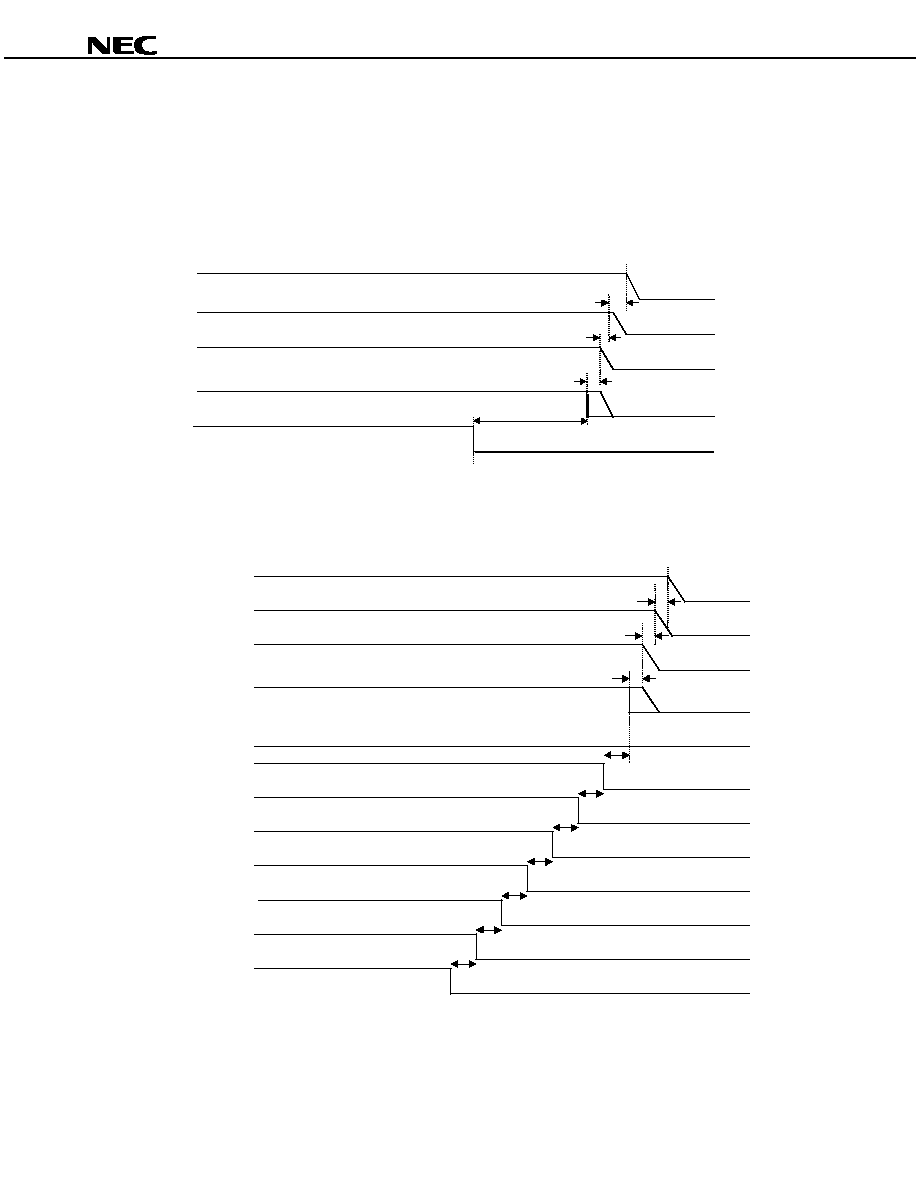

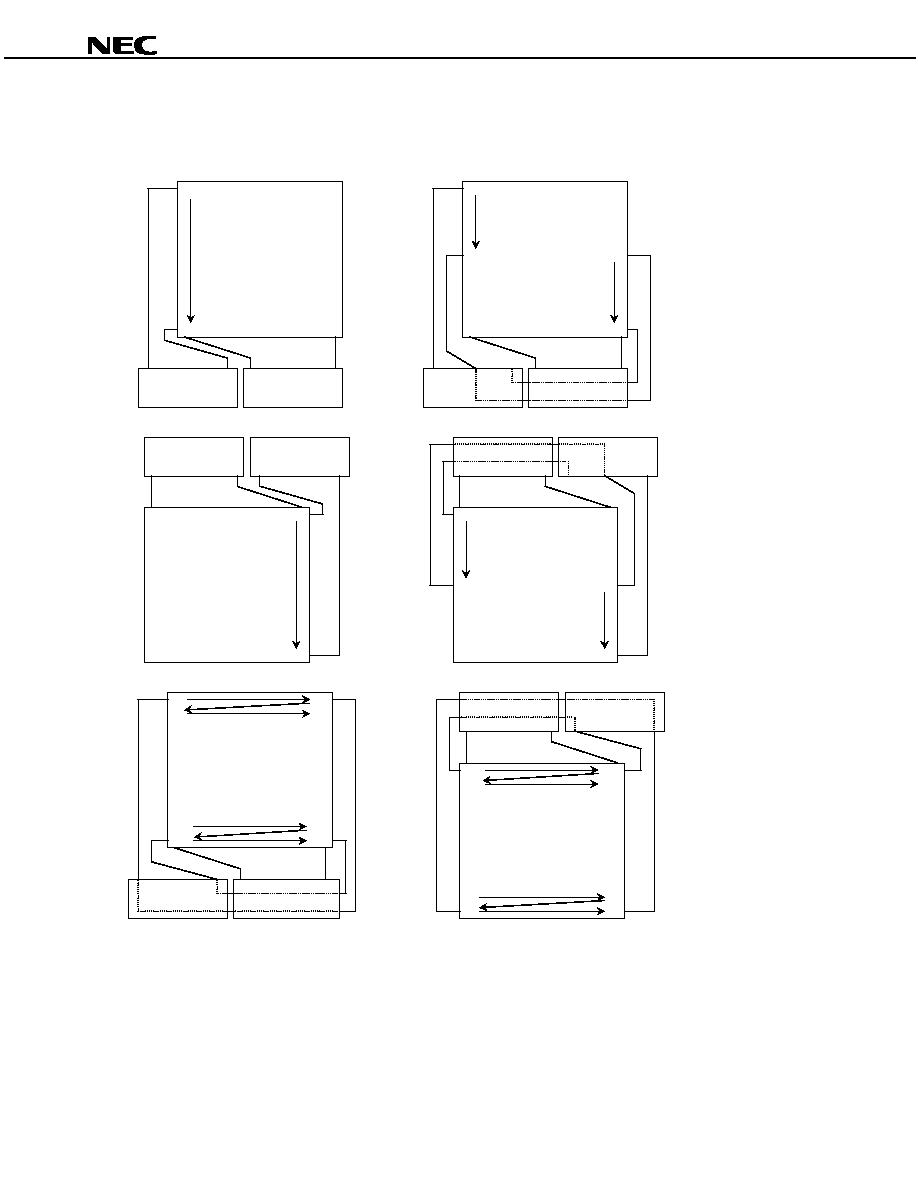

- 5.1 Output Mode and Gate Scan Selection

- 5.2 DC/DC OSC Frequency Selection

- 5.3 DC/DC Converter Control

- 5.4 VDD2 Boost Selection

- 5.5 Division Ratio Selection of the DC/DC Converter at Power on

- 5.6 DC/DC Converter Power on Time Selection

- 5.7 Division Ratio Selection of the DC/DC Converter OSC Frequency

- 5.8 Amp. Current Selection

- 5.9 VR Regulator Selection Output

- 5.10 VS Regulator Selection Output

- 5.11 Control of VM Output Control, VCOM Output

- 5.12 VCOM Output Frequency Adjustment

- 5.13 VCOM Output Center Adjustment

- 5.14 VCOM Center Adjustment Selection

- 6. PANNEL CONNECTION

- 7. CONNECTION EXAMPLE WITH SOURCE DRIVER

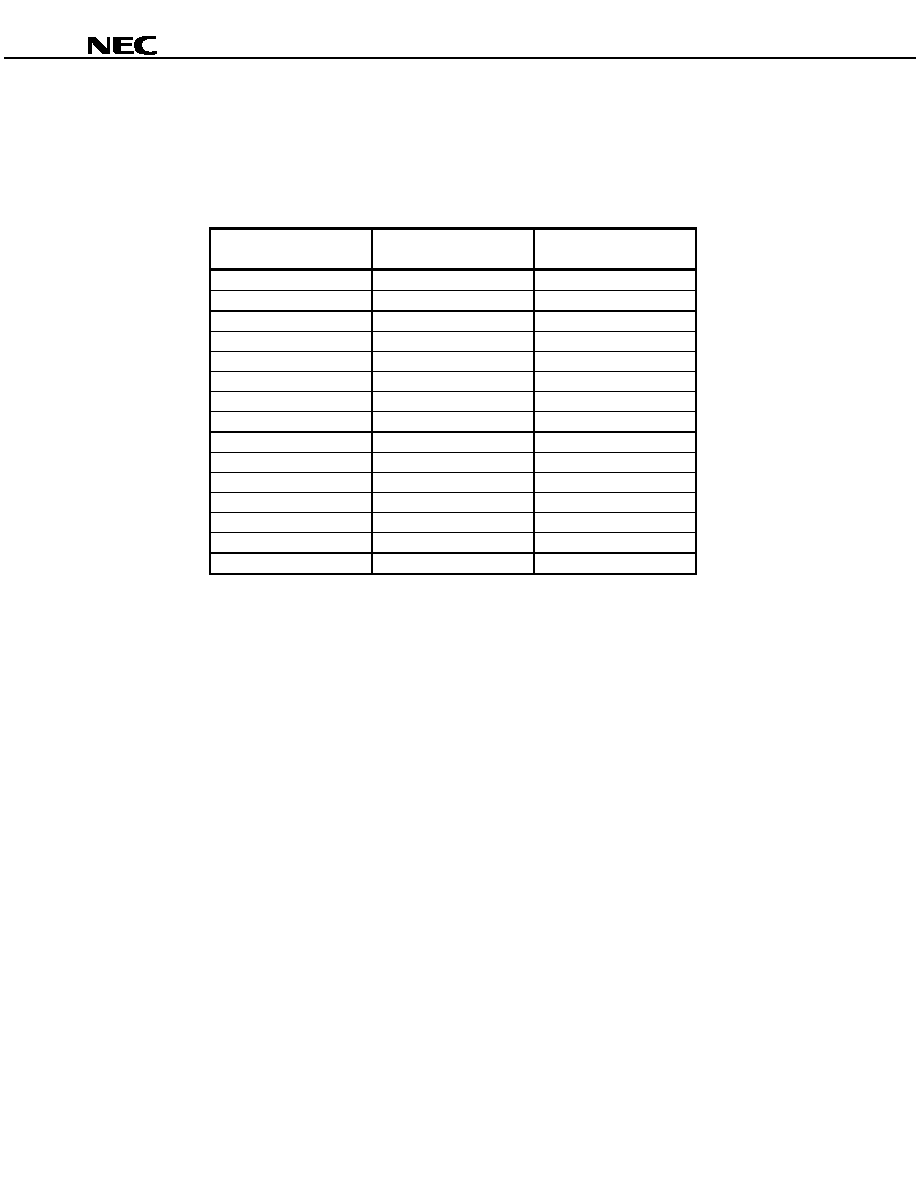

- 8. VALUE OF WIRING RESISTANCE TO EACH PIN

- 9. RECOMMENDED CAPACITANCE VALUES OF EXTERNAL CAPACITOR

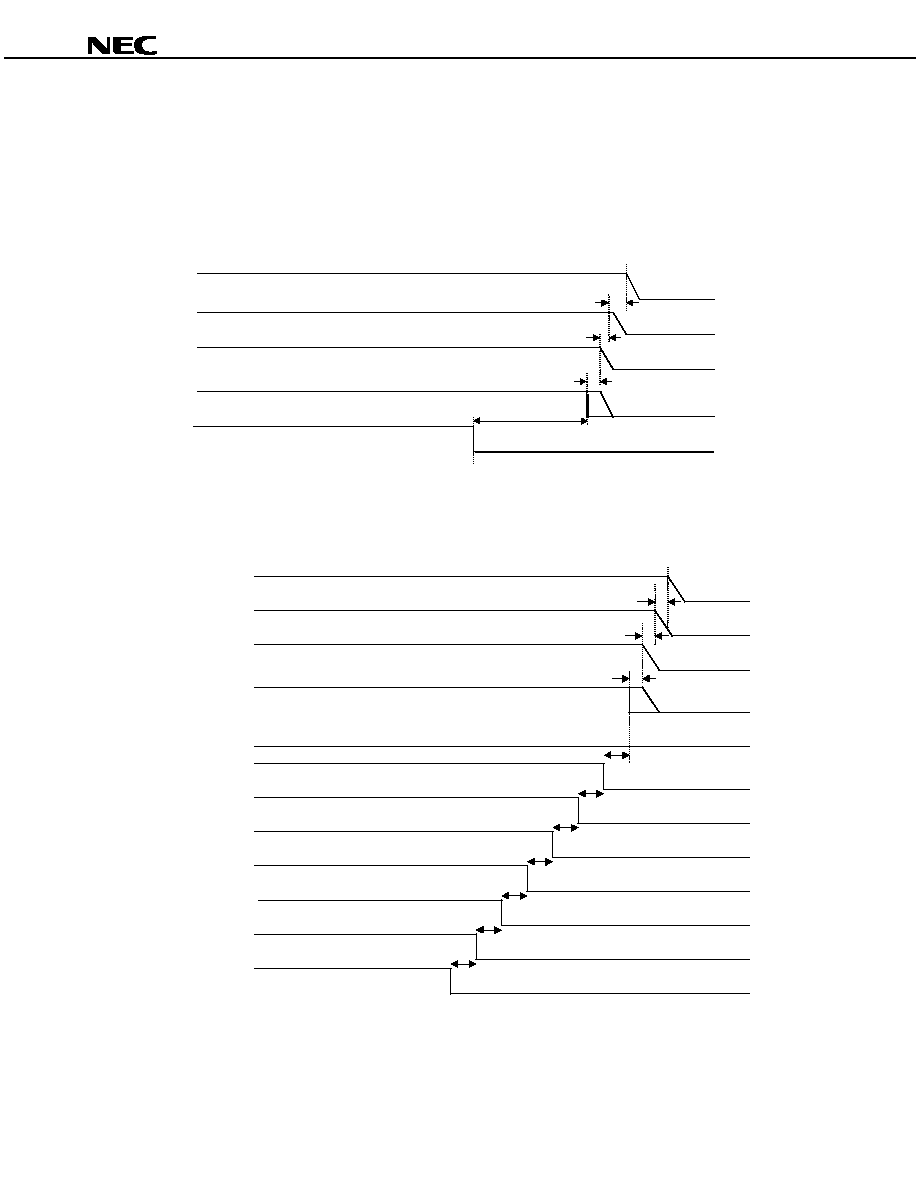

- 10. SERIAL INTERFACE

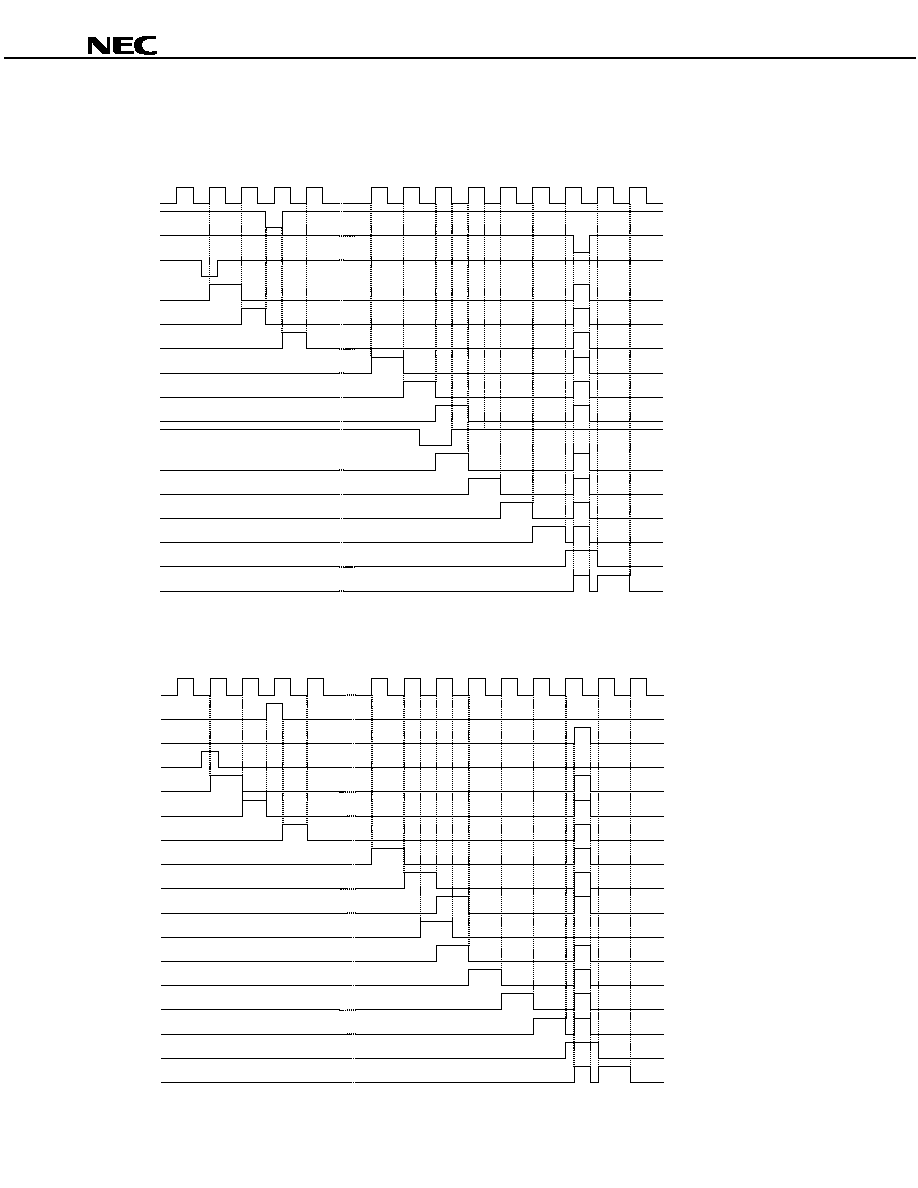

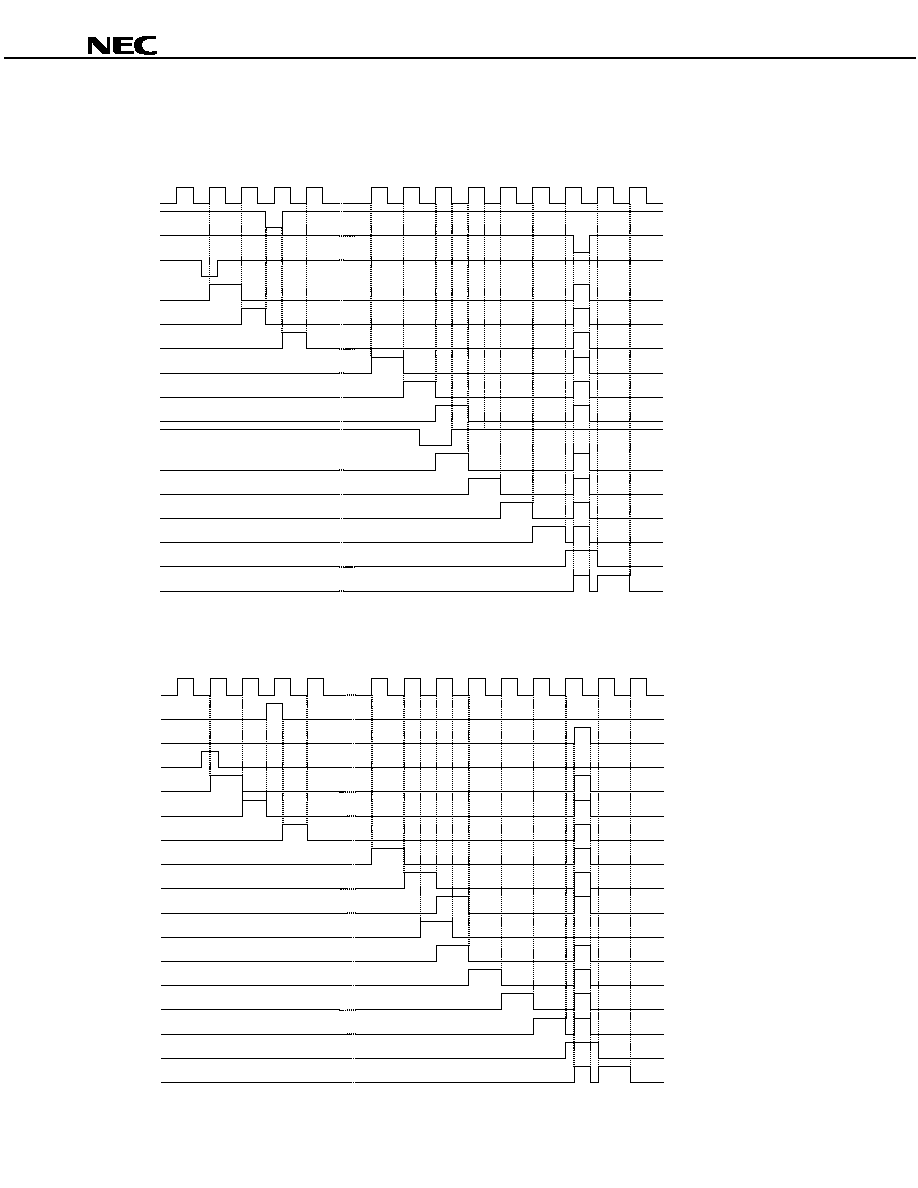

- 11. TIMING CHARTS (MODE1: SCN0 = 1, SCN1 = 1, SCN2 = 1)

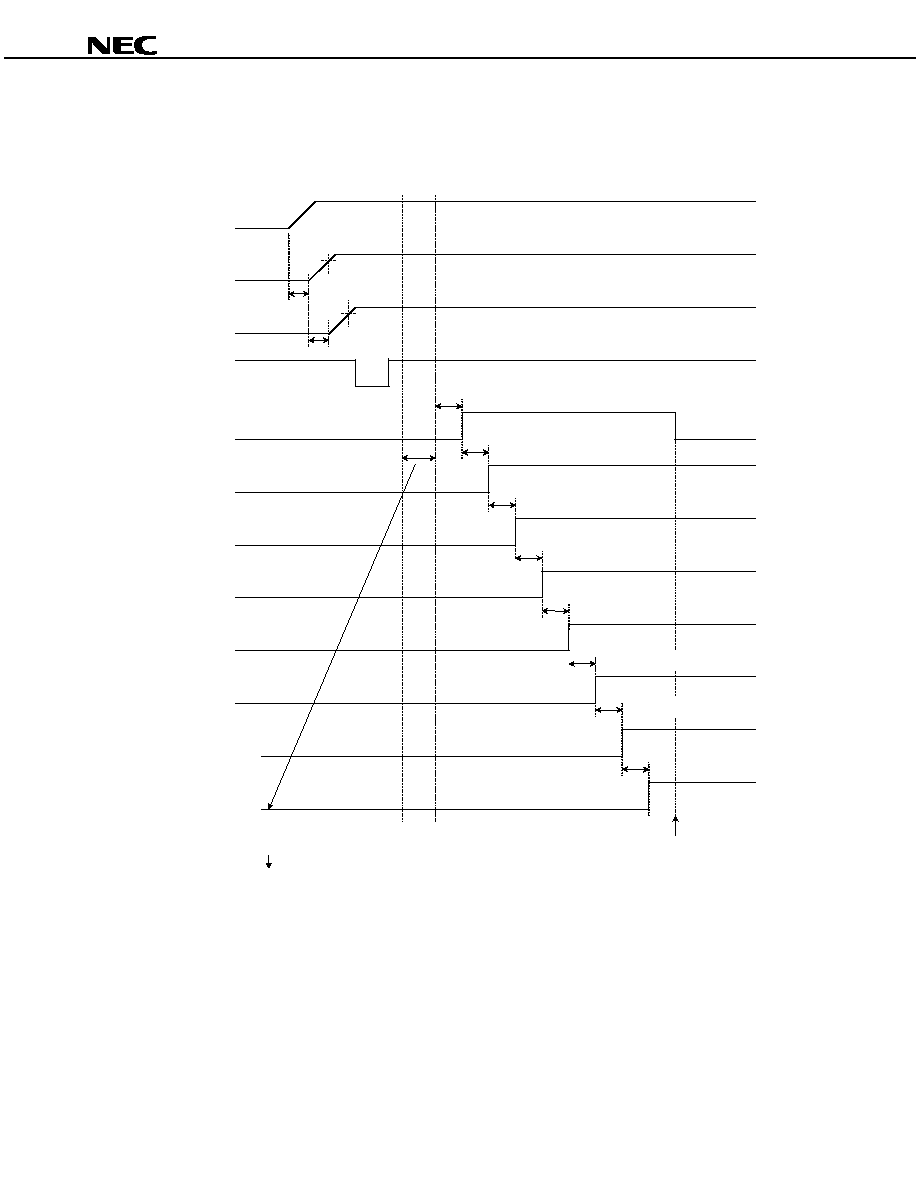

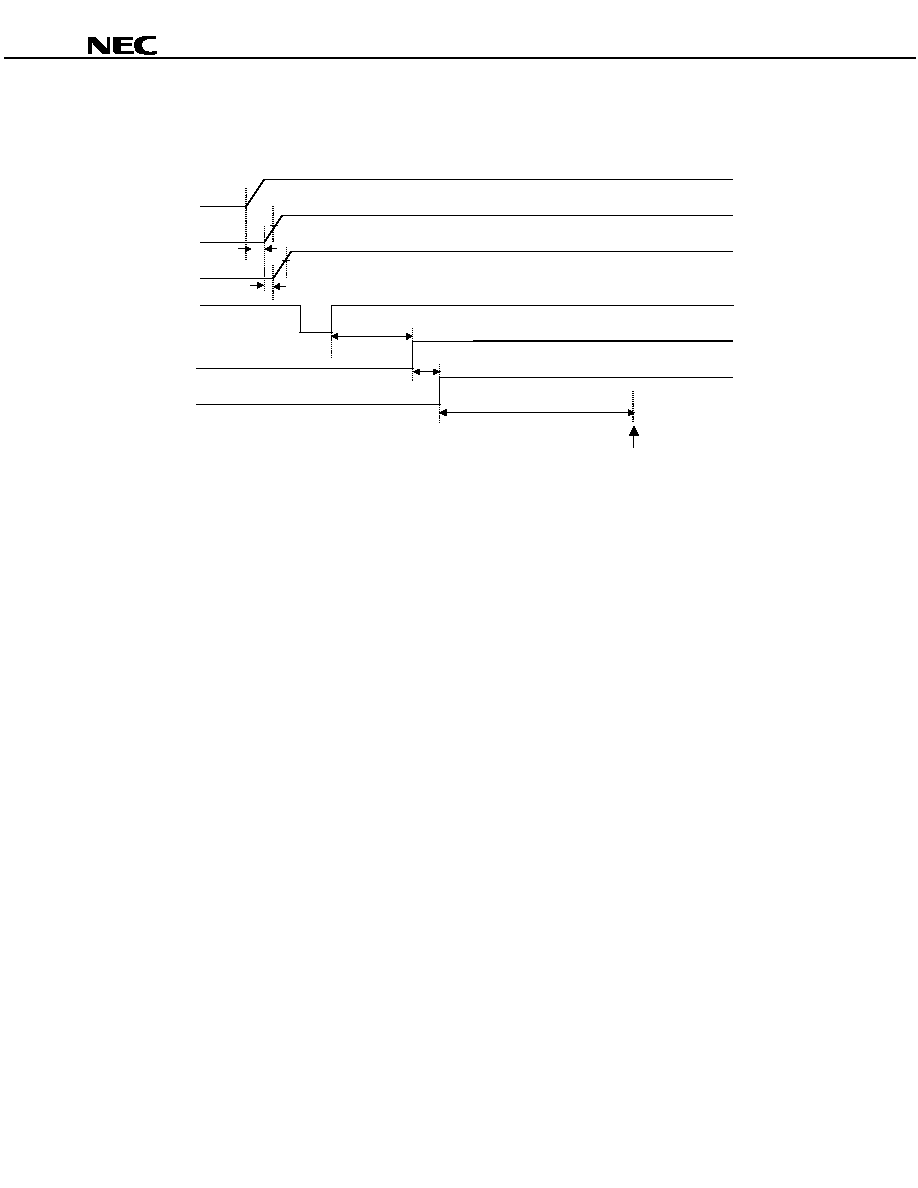

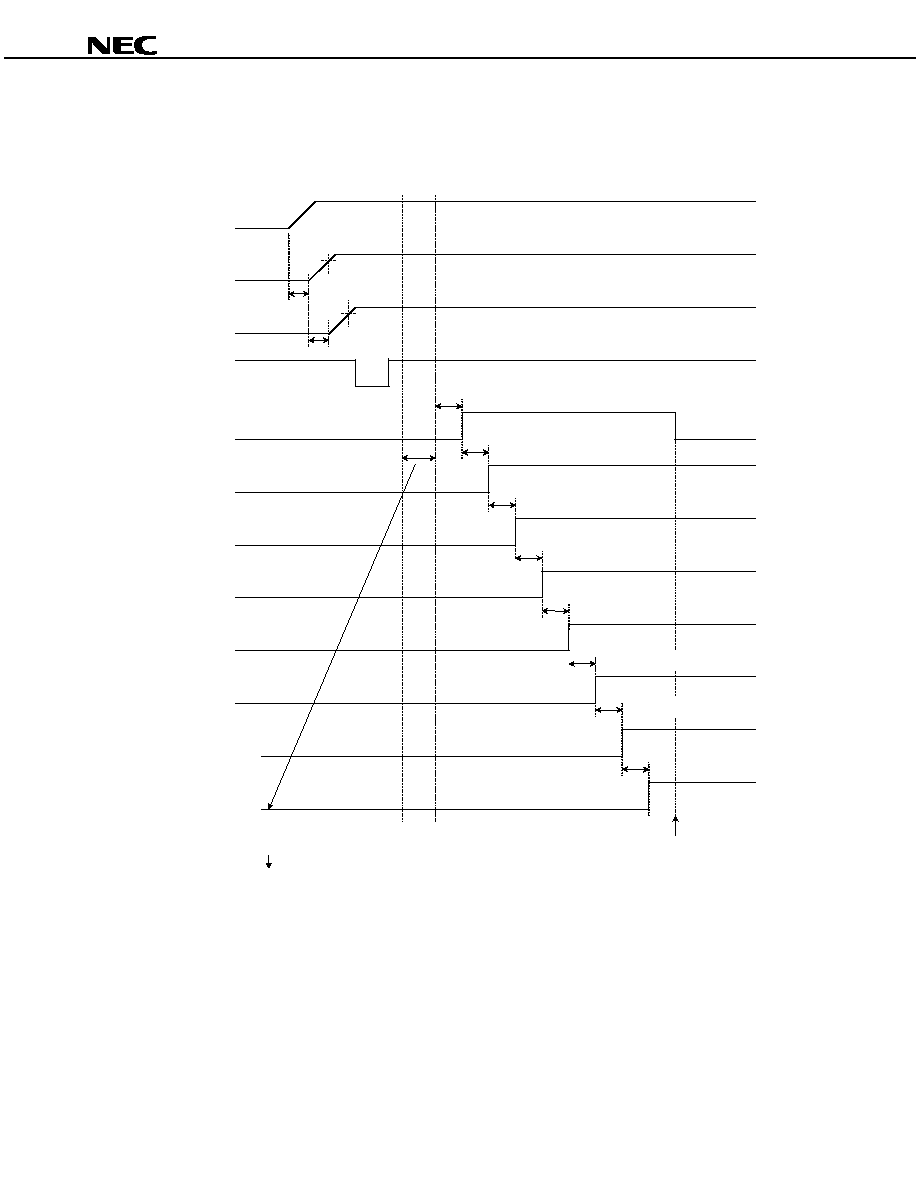

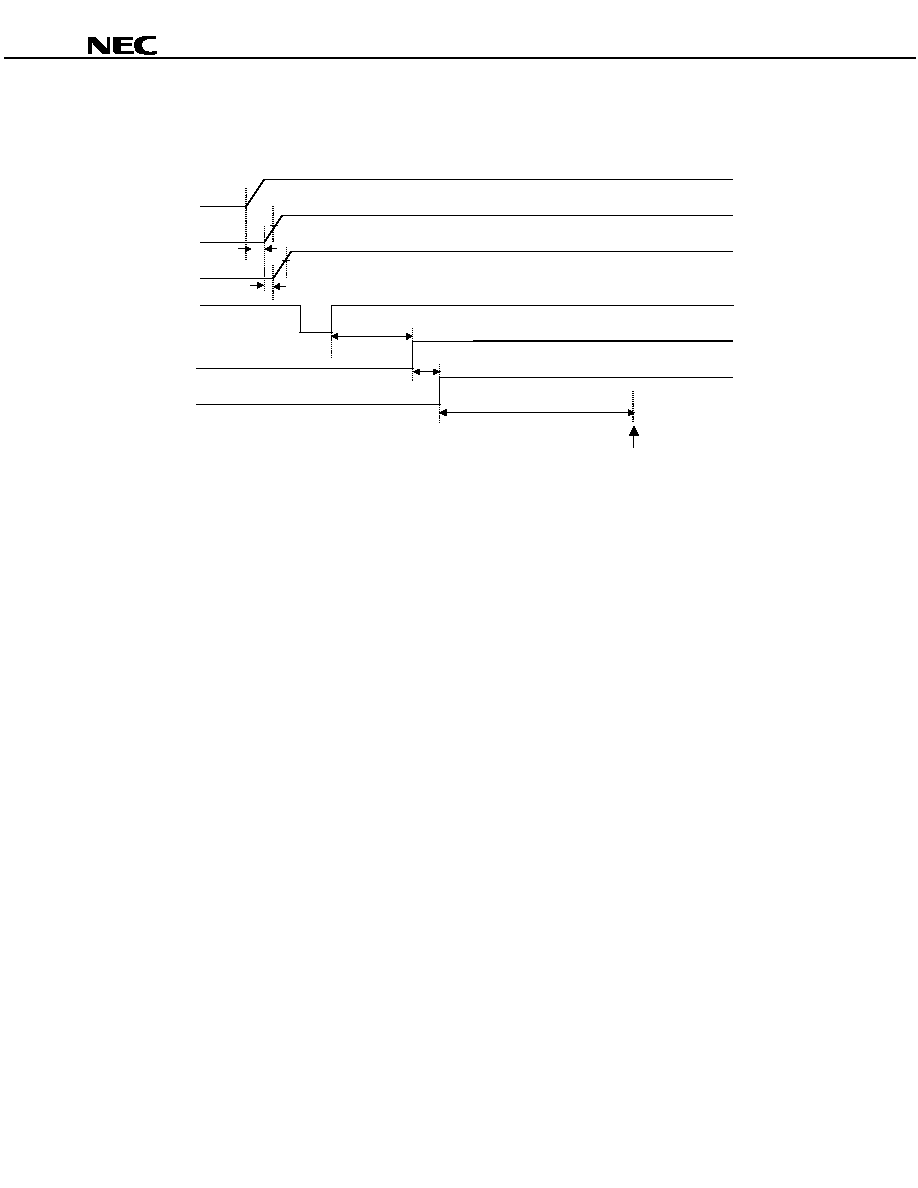

- 12. POWER ON/OFF SEQUENCE

- 12.1 Power ON sequence

- 12.2 Power OFF sequence

- 13. ELECTRICAL SPECIFICATIONS

©

2001

MOS INTEGRATED CIRCUIT

µ

µ

µ

µ

PD161644

241 OUTPUT GATE DRIVER WITH POWER SUPPLY FOR TFT-LCD GATE DRIVER

PRELIMINARY PRODUCT INFORMATION

Document No. S15797EJ1V4PM00 (1st edition)

Date Published October 2002 NS CP(K)

Printed in Japan

The information contained in this document is being issued in advance of the production cycle for the

device. The parameters for the device may change before final production or NEC Corporation, at its own

discretion, may withdraw the device prior to its production.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

The mark

!

shows major revised points.

DESCRIPTION

The

µ

PD161644 is a TFT-LCD gate driver with power supply for TFT-LCD driver. Because this gate driver has a

level shift circuit for logic input, it can output a high gate scanning voltage in response to a CMOS-level input. This

ICs can generate the levels which TFT-LCD driver need, from 2.7 V.

FEATURES

∑

High breakdown voltage output (V

DD1

-V

SS3

= 40 V MAX.)

∑

2.7 V CMOS level input

∑

Number of output: 241 output selectable

∑

To generate 4 levels from single voltage input

∑

To integrate regulator circuit for source driver

∑

Mode setting from source driver: Serial I/F or pin control

∑

On-chip VCOM driver

∑

On-chip gate output low-level selector

ORDERING INFORMATION

Part number

Package

µ

PD161644P

Chip

Remark

Purchasing the above chip entails the exchange of documents such as a separate memorandum or

product quality, so please contact one of our sales representatives.

Preliminary Product Information S15797EJ1V4PM

2

µ

µ

µ

µ

PD161644

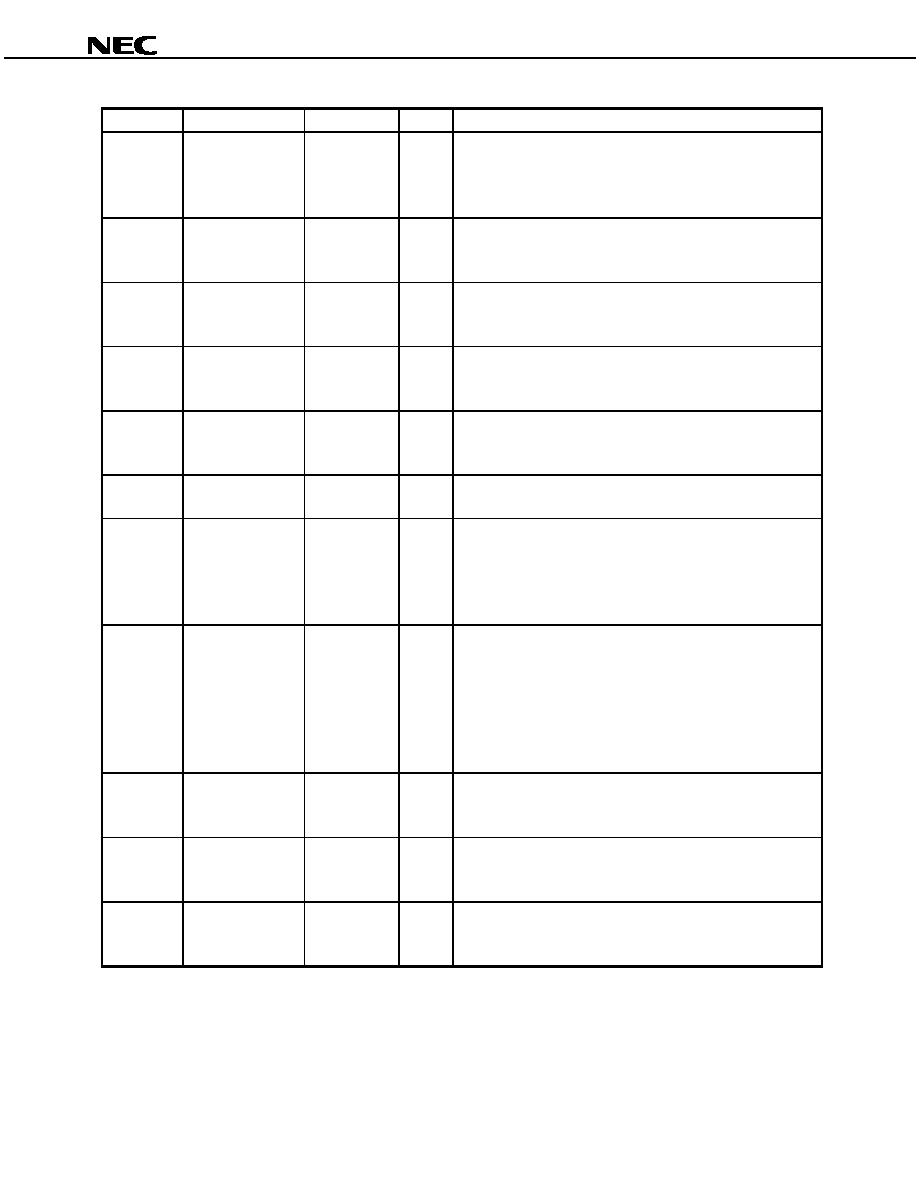

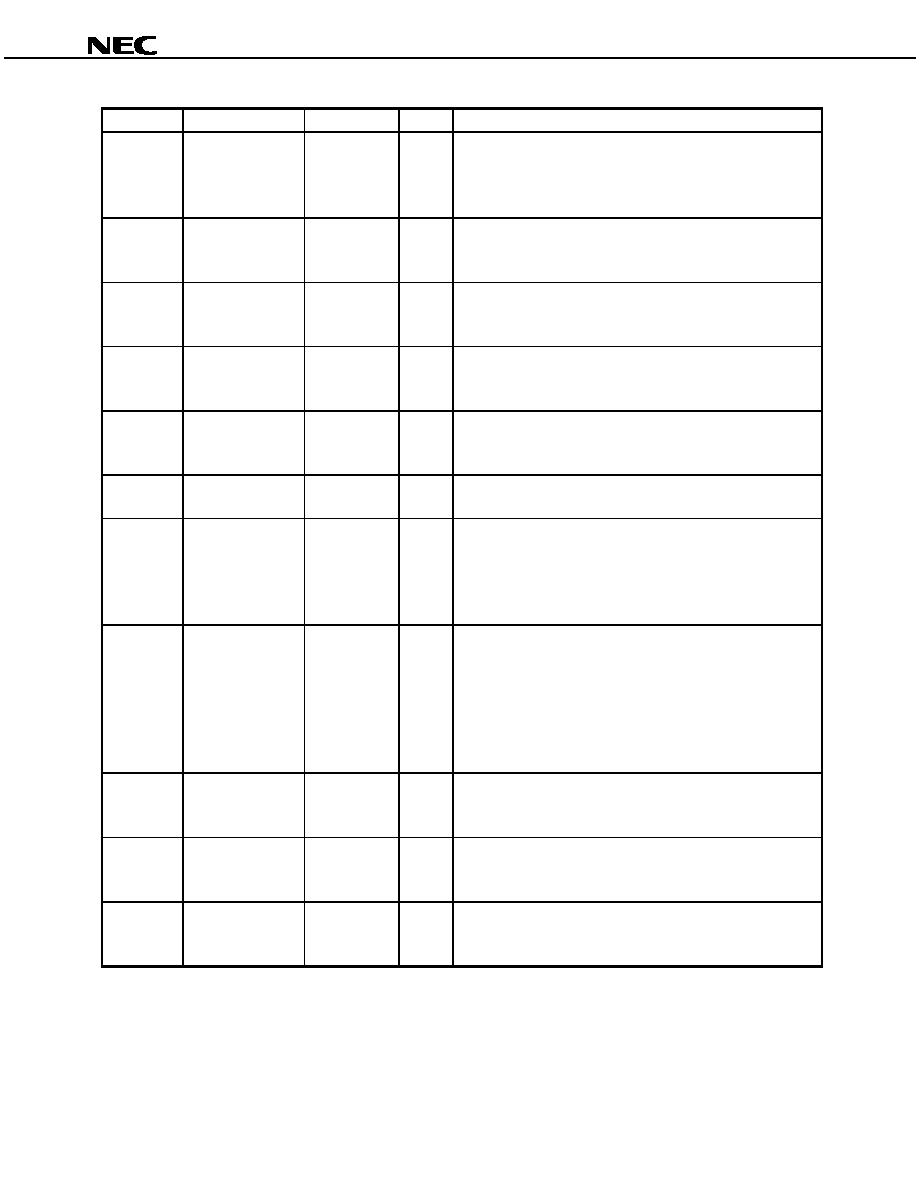

1. BLOCK DIAGRAM/SYSTEM DIAGRAM

SR121 SR122

SR240

SR241

SCN1

SR120

SR119

SR2

SR1

C2

V

DD2

V

DD1

V

SS2

GCS

GCL

V

SS1

IFSEL

MVS

C2

C5

+

C5

-

C2

C4

+

C4

-

C2

C3

+

C3

-

C1

C2

+

C2

-

C1

C1

+

C1

-

V

CC1

V

DC

V

S

5 V

4 V

V

REF

Regurator

V

S

GDA

DC/DC converter

R,/L

CLK

STVR

OE

1

OE

2

MPX

O

1

O

2

O

119

O

120

O

122

O

122

O

240

O

241

STVL

V

B

PV

SS3

PV

CC1

VCIN

VCOM

COMH

COML

V

SS3

DCON

RGONR

VM

VCD2

V

DC

SCN0

/GRESET

C2

C2

C2

C2

C6

+

C6

-

C2

V

SS4

C2

C2

V

DC

D/A

OSC

DCCLK

VSEL

EXRV

CLS0

FS0

FS2

PUPT0

DUPF0

DC/DC converter

DC/DC converter

Common

driver

circuit

Source driver

Serial interface

register

Switch

Level Shifter

Gate output

low level select circuit

ACS0

Source driver

Common

VMS

RGON

SCN2

FRM

VMON

TESTIN1

TESTIN2

TESTOUT1

TESTOUT2

D/A

Regurator

V

R

VGD

V

R

PV

SS1

VCOMIN

C2

C3

Remarks 1./xxx indicates active low signal.

2.Level Shifter (LS): Interfaces between 2.7 V CMOS level and V

DD1

to V

B

level.

Preliminary Product Information S15797EJ1V4PM

3

µ

µ

µ

µ

PD161644

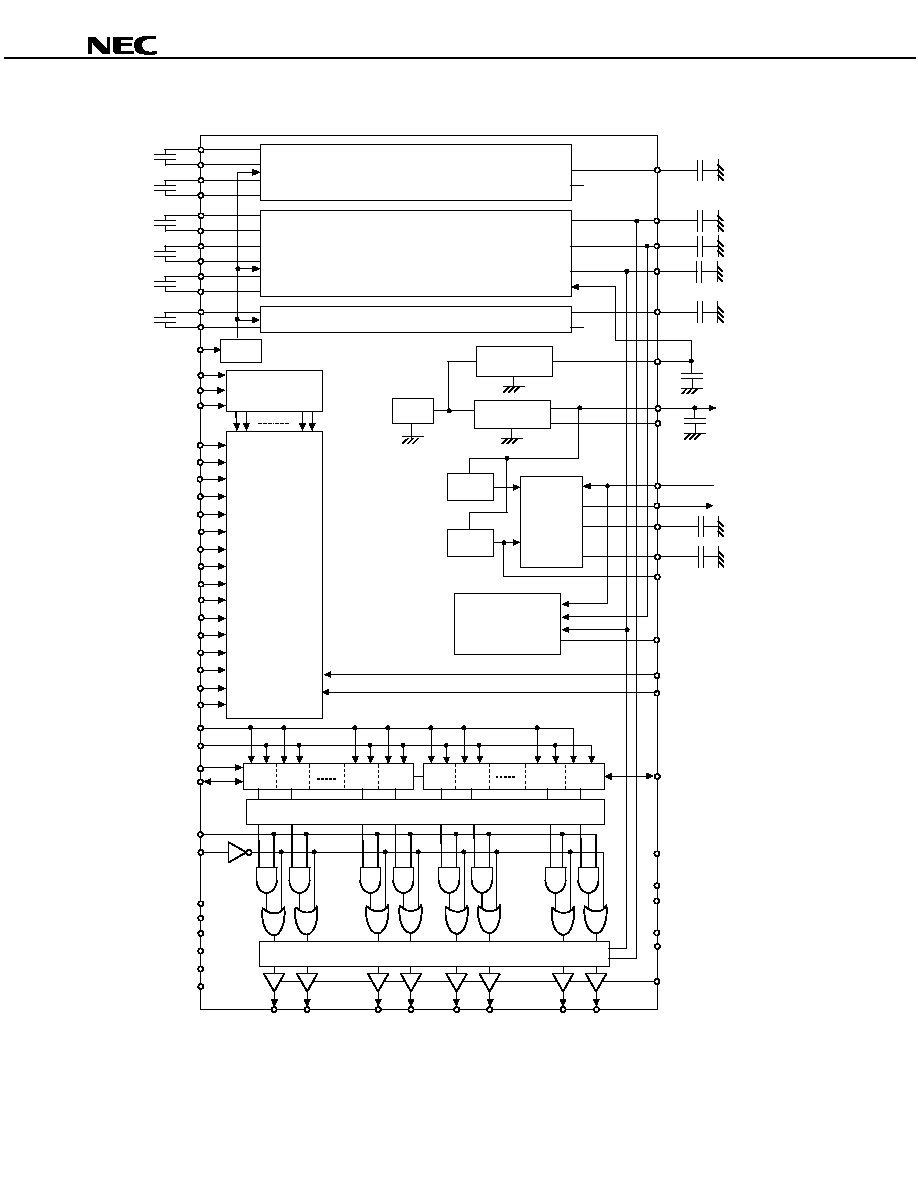

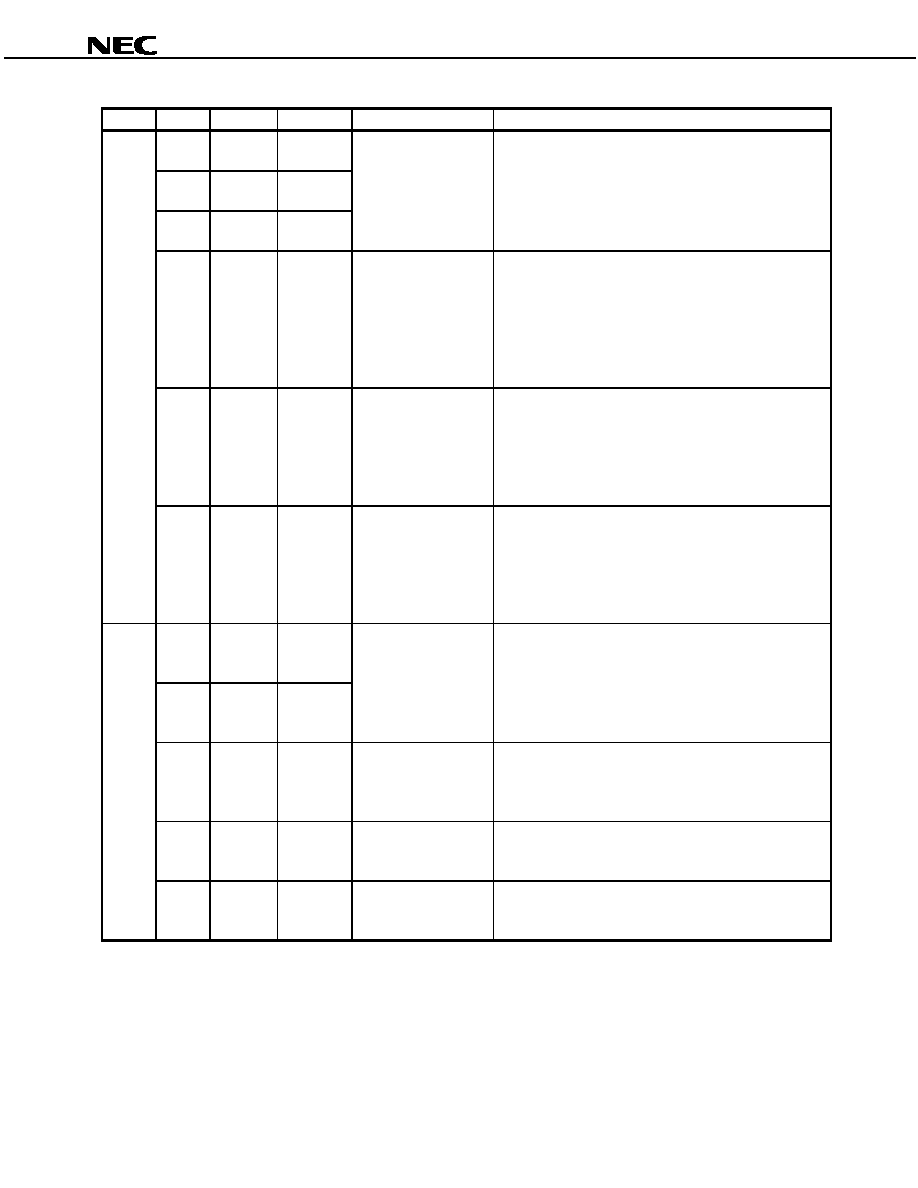

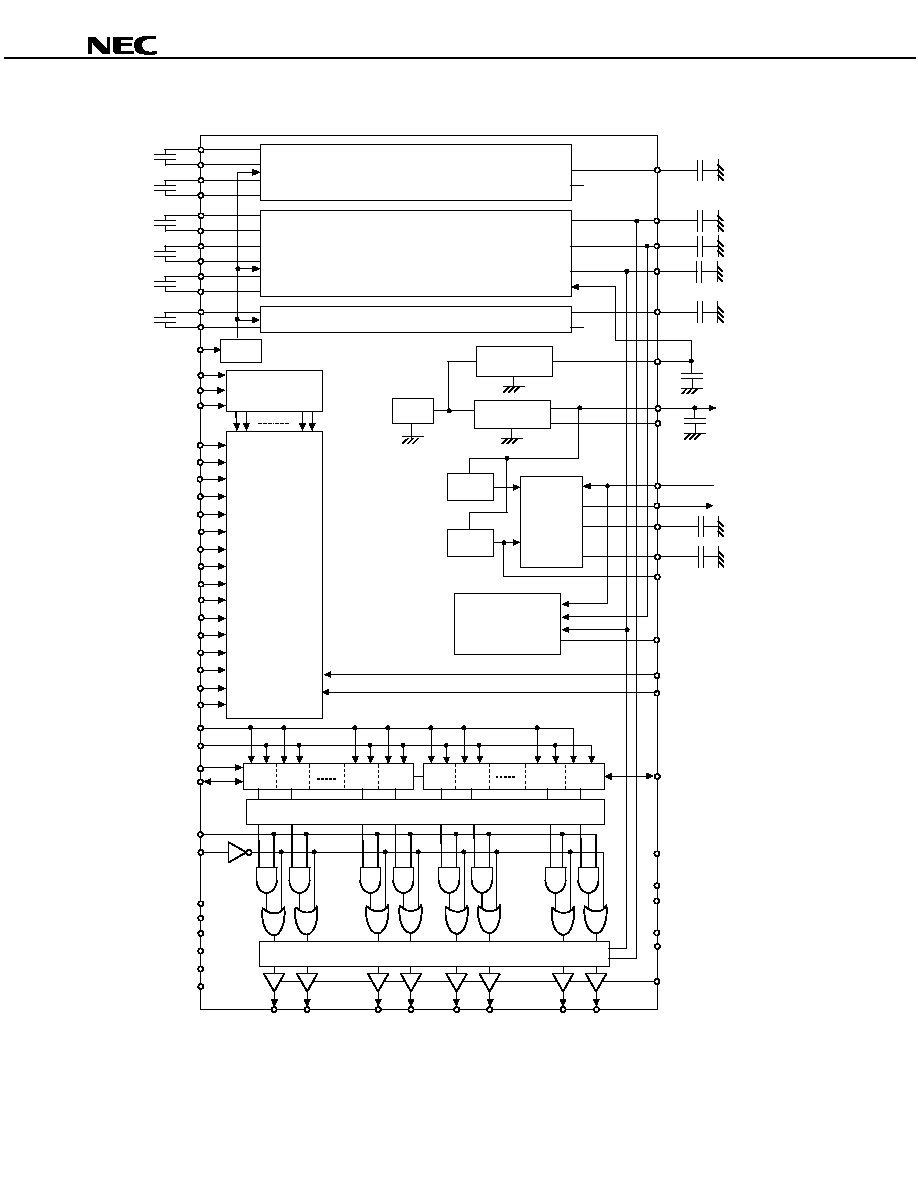

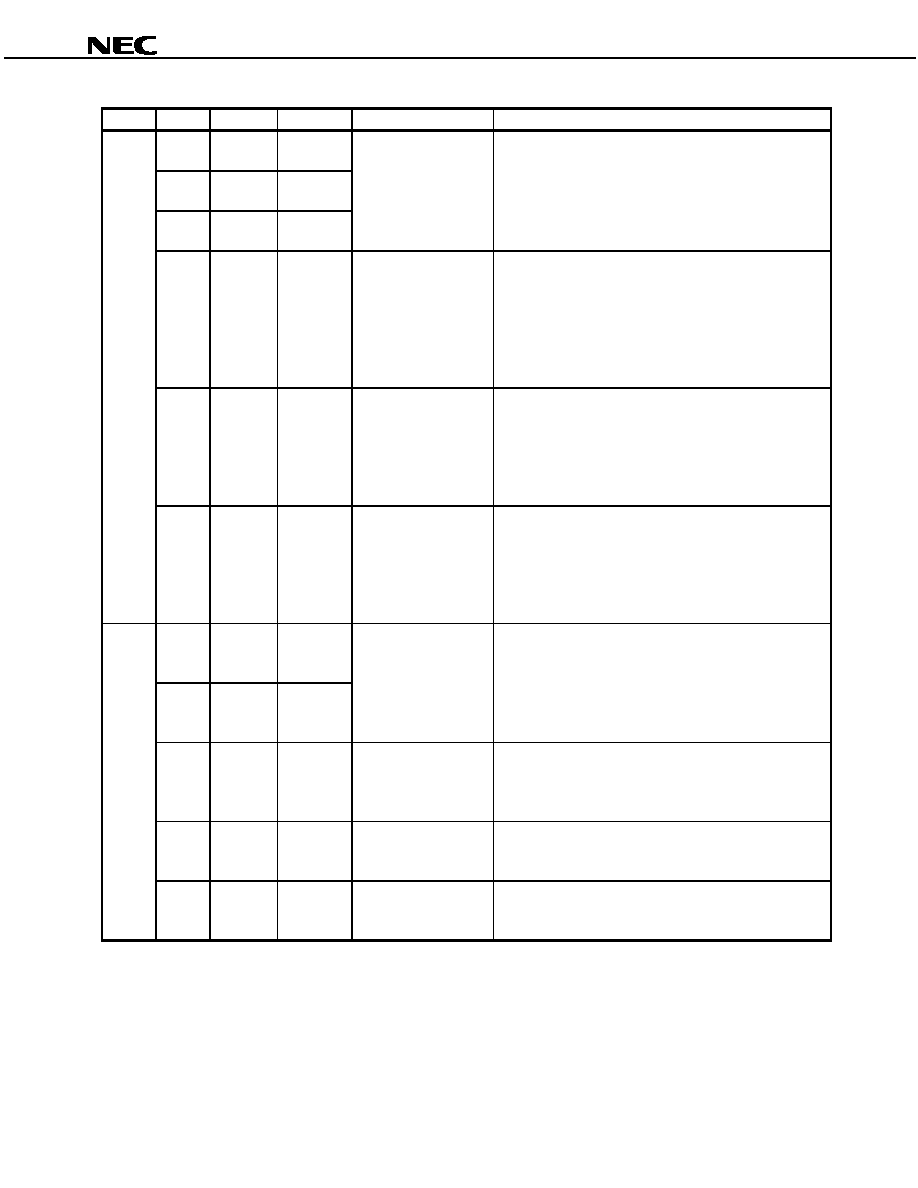

1.1 Boost Voltage Construction

The boost voltage generated in

µ

PD161644 is shown below.

V

DD2

: 5.4 V

V

SS1

: 0 V

V

R

: 5 V

V

DD1

= V

R

x 3

= 15 V

V

DC

: 2.7 V

V

SS2

= V

R

x

-

2

=

-

10 V

V

SS3

= V

R

x

-

3

=

-

15 V

V

DD2

: 5.4 V

V

SS1

: 0 V

V

R

: 5 V

V

DD1

= V

DD2

x 3

= 16.2 V

V

DC

: 2.7 V

V

SS2

= V

DD2

x

-

2

=

-

10.8 V

V

SS3

= V

DD2

x

-

3

=

-

16.2 V

V

SS4

= V

DC

x

-

1

=

-

2.7 V

V

SS4

= V

DC

x

-

1

=

-

2.7 V

VGD = V

R

VGD = V

DD2

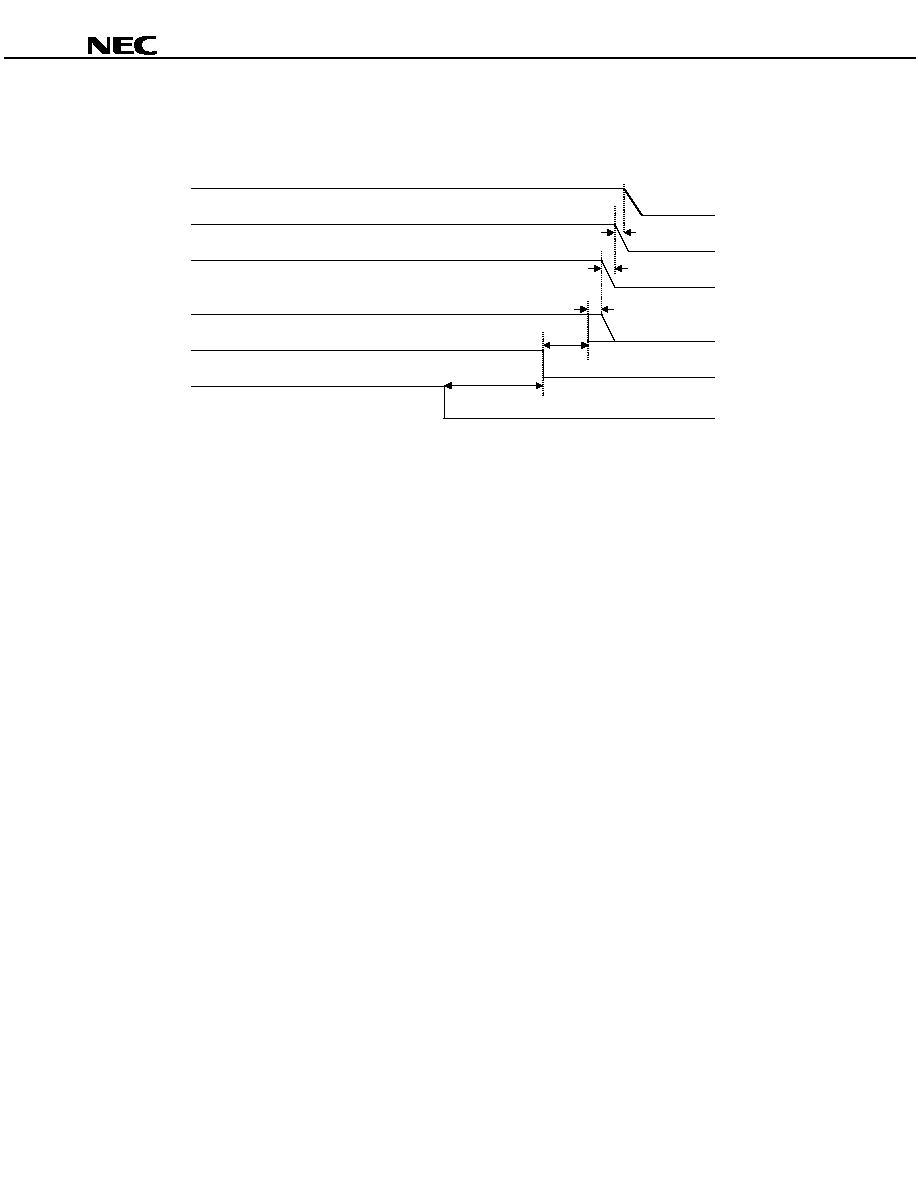

1.2 Boost Voltage Auto Start and Rising Order

DCON

V

DD1

= 3 x V

R

V

SS3

=

-

3 x V

R

V

R

V

DD2

= 3 x V

DC

V

SS1

V

SS2

=

-

2 x V

R

T1

T2

T3

T4

V

SS4

=

-

V

DC

T1, T2, T3, T4: changeable by PUPT0, PUPT01, DUPF0, DUPF1

VGD = V

R

, VCD2 = H

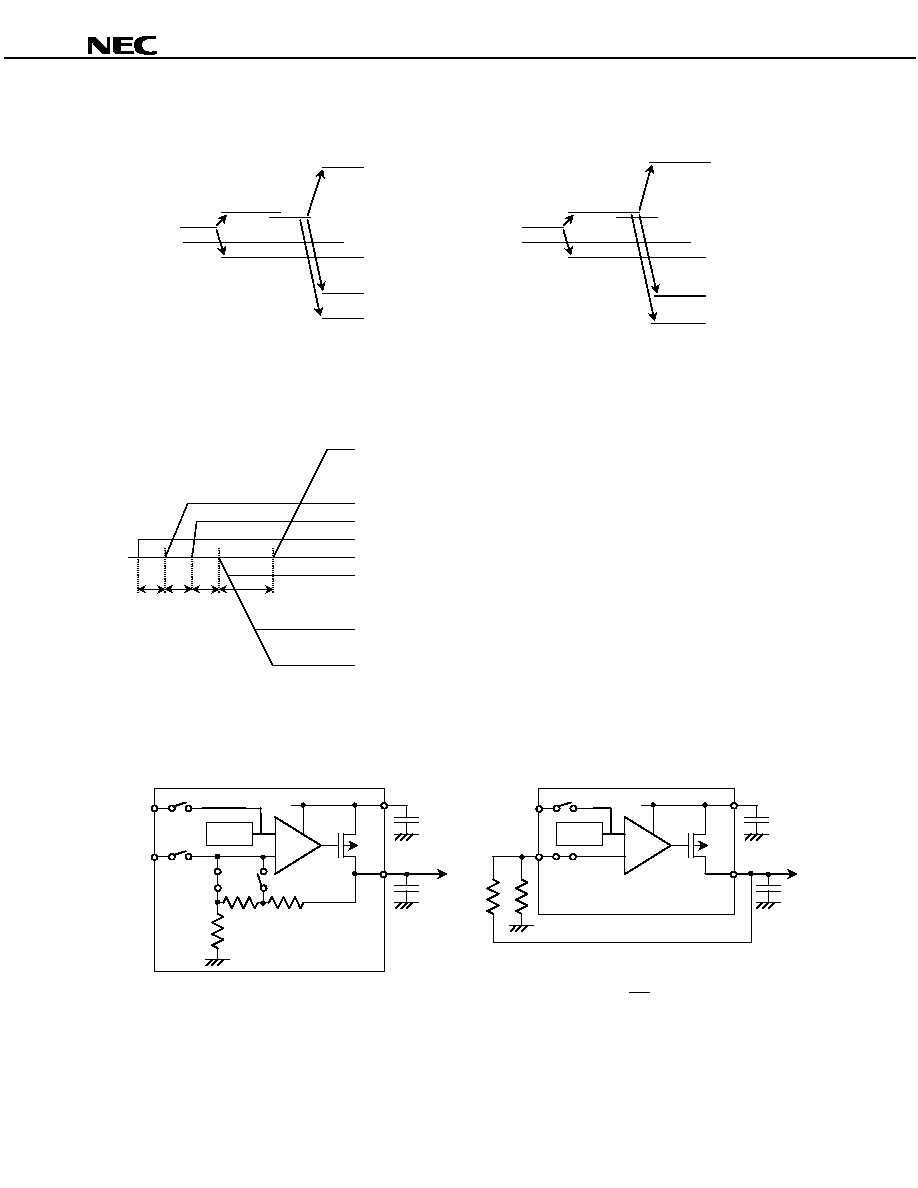

1.3 V

S

_AMP Circuit

V

S

_AMP circuits are shown below.

RbS

RaS

V

S

C3

5 V

4 V

MVS

RcS

V

REF

V

DD2

-

+

C3

V

S

C3

5 V

4 V

MVS

V

REF

V

DD2

-

+

C3

R

bS

R

aS

Internal Resistor Mode

EXRV = L

External Resistor Mode

EXRV = H

V

S

= (1+ )V

REF

R

bS

R

aS

TESTOUT1

TESTOUT1

Preliminary Product Information S15797EJ1V4PM

4

µ

µ

µ

µ

PD161644

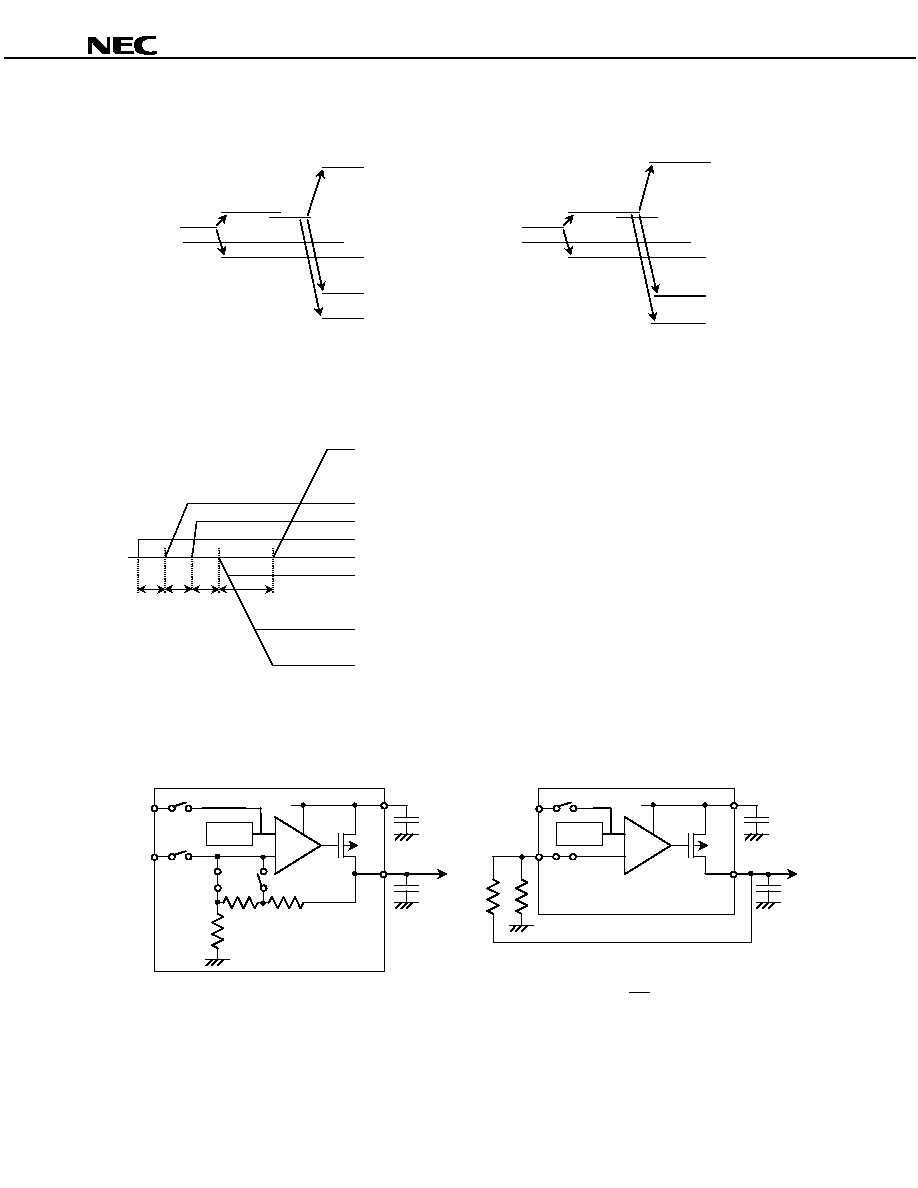

1.4 Common Drive Circuit

The common drive circuit is shown below.

COMH

V

S

VCIN

LS

+

-

COML

C3

VCOM

C3

V

CC1

V

DD2

V

SS4

D/A

CDA

0

CDA

1

CDA

2

CDA

3

CDA

4

CDA

5

CDA

6

CDA

7

+

-

V

S

D/A

DA

0

DA

1

DA

2

DA

3

DA

4

DA

5

DA

6

DA

7

V

S

+

-

V

S

+

-

VCOMIN

Preliminary Product Information S15797EJ1V4PM

5

µ

µ

µ

µ

PD161644

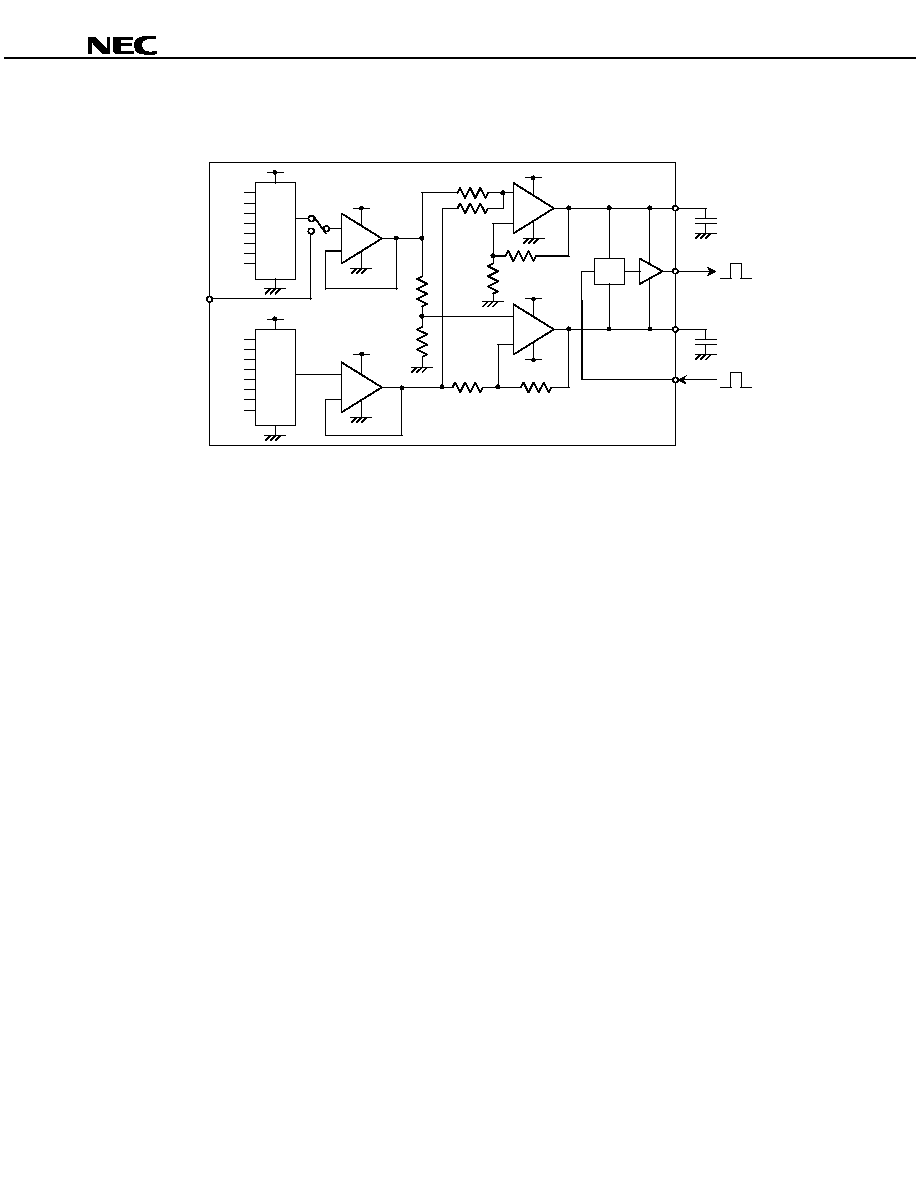

1.5 Variable Boost Steps

The boost steps of V

DD1

, V

SS2

, V

SS3

are selected according to how the external capacitor is connected.

The examples of connection are shown below. V

S

is selected as a boost reference voltage in these examples (short

between the V

S

and VGD pins).

C5+

C5

-

C4+

C4

-

C3+

C3

-

C2+

C2

-

C1+

C1

-

V

DD2

= V

DC

x 3

C2+

C2

-

C1+

C1

-

C2+

C2

-

C1+

C1

-

V

DD1

V

SS2

V

SS3

C5+

C5

-

C4+

C4

-

C3+

C3

-

V

SS2

V

SS3

C5+

C5

-

C4+

C4

-

C3+

C3

-

V

SS2

V

SS3

C5+

C5

-

C4+

C4

-

C3+

C3

-

V

SS2

V

SS3

V

SS4

= V

DC

x

-

1

C6+

C6

-

V

SS4

C6+

C6

-

V

SS4

V

SS4

=

-

V

DD2

= V

DC

x 2

V

DD2

= V

DC

x 2

(dual mode)

V

DD1

= VGD x 3

V

SS2

= VGD x

-

2

V

SS3

= VGD x

-

3

V

DD2

(single mode)

V

DD1

= VGD x 3

V

SS2

=

-

V

SS3

= VGD x

-

2

V

DD1

= VGD x 2

V

SS2

= VGD x

-

1

V

SS3

= VGD x

-

2

V

DD2

V

DD2

V

DD1

= VGD x 2

V

SS2

=

-

V

SS3

= VGD x

-

1

V

DD1

V

DD1

V

DD1

Preliminary Product Information S15797EJ1V4PM

6

µ

µ

µ

µ

PD161644

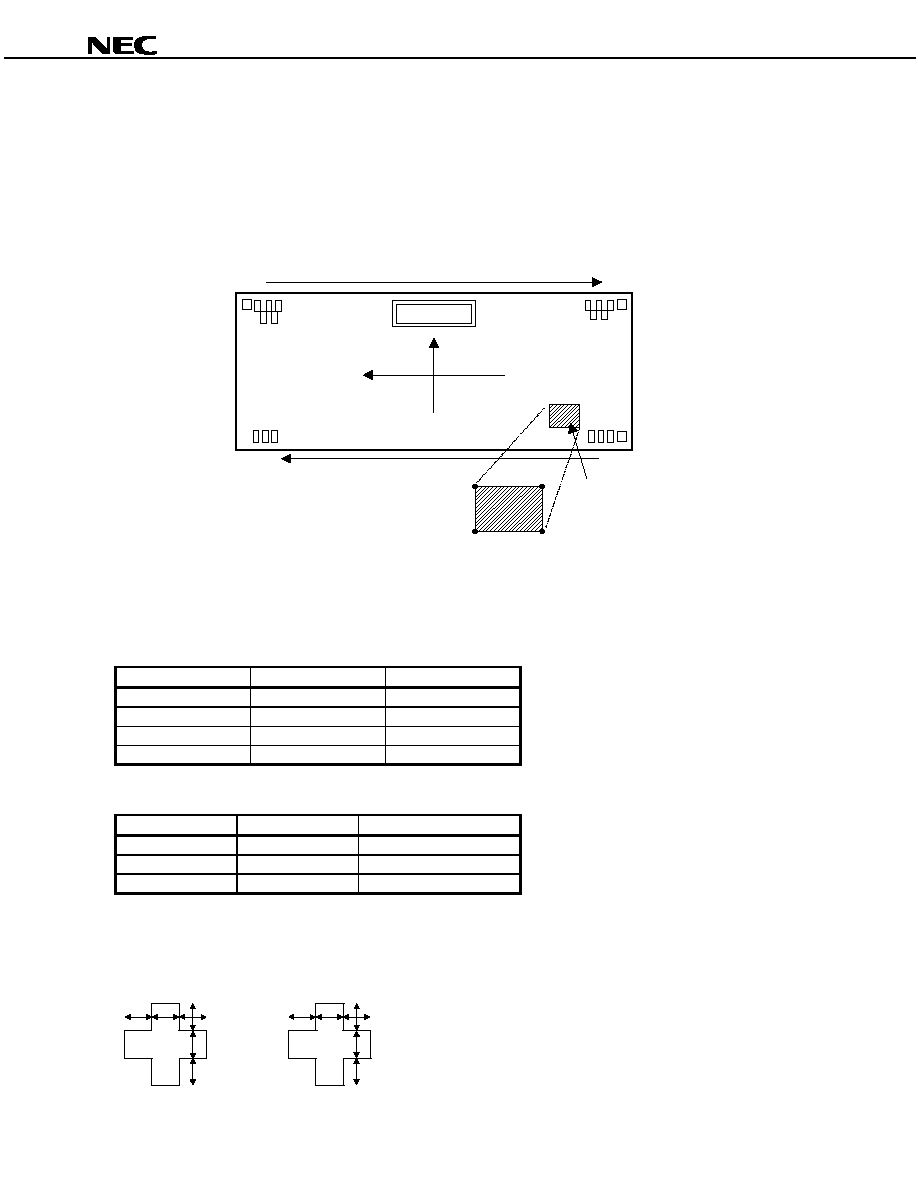

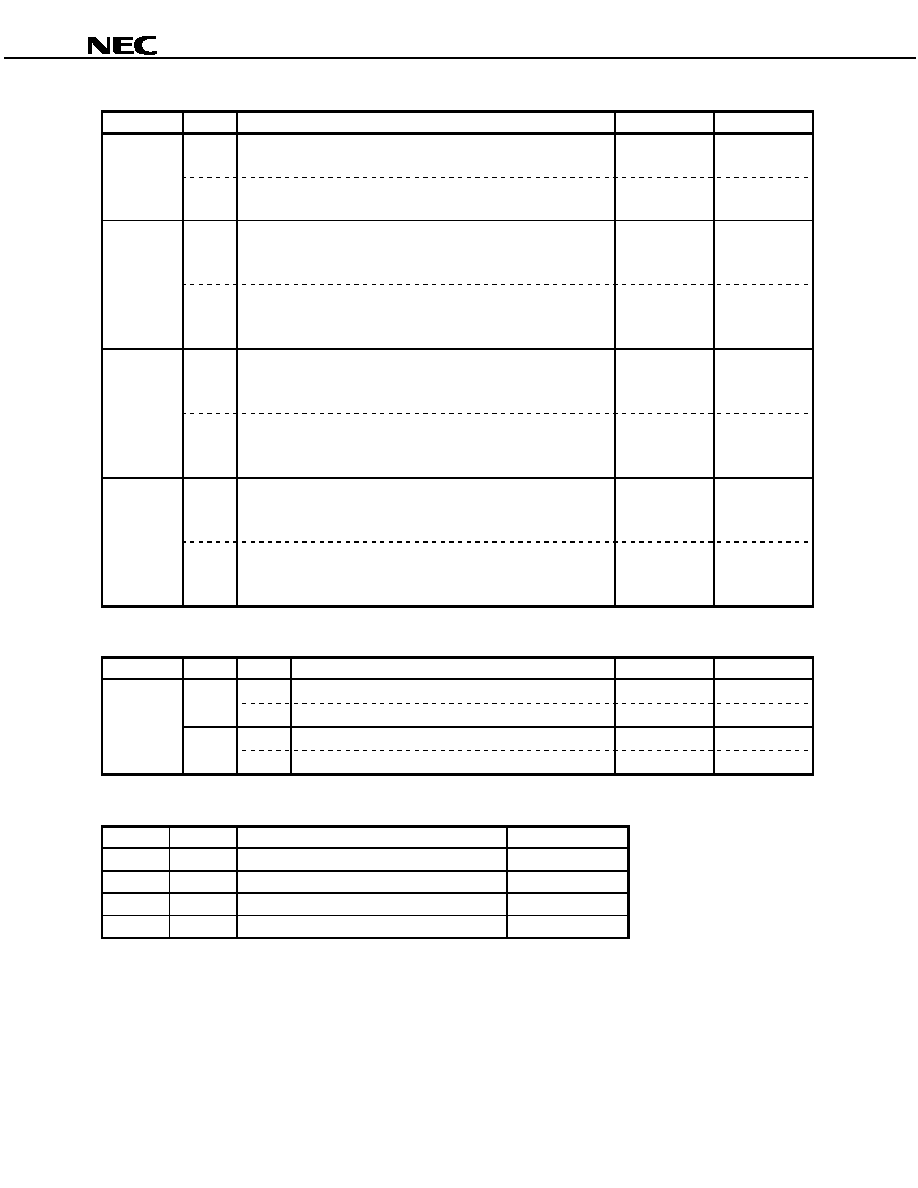

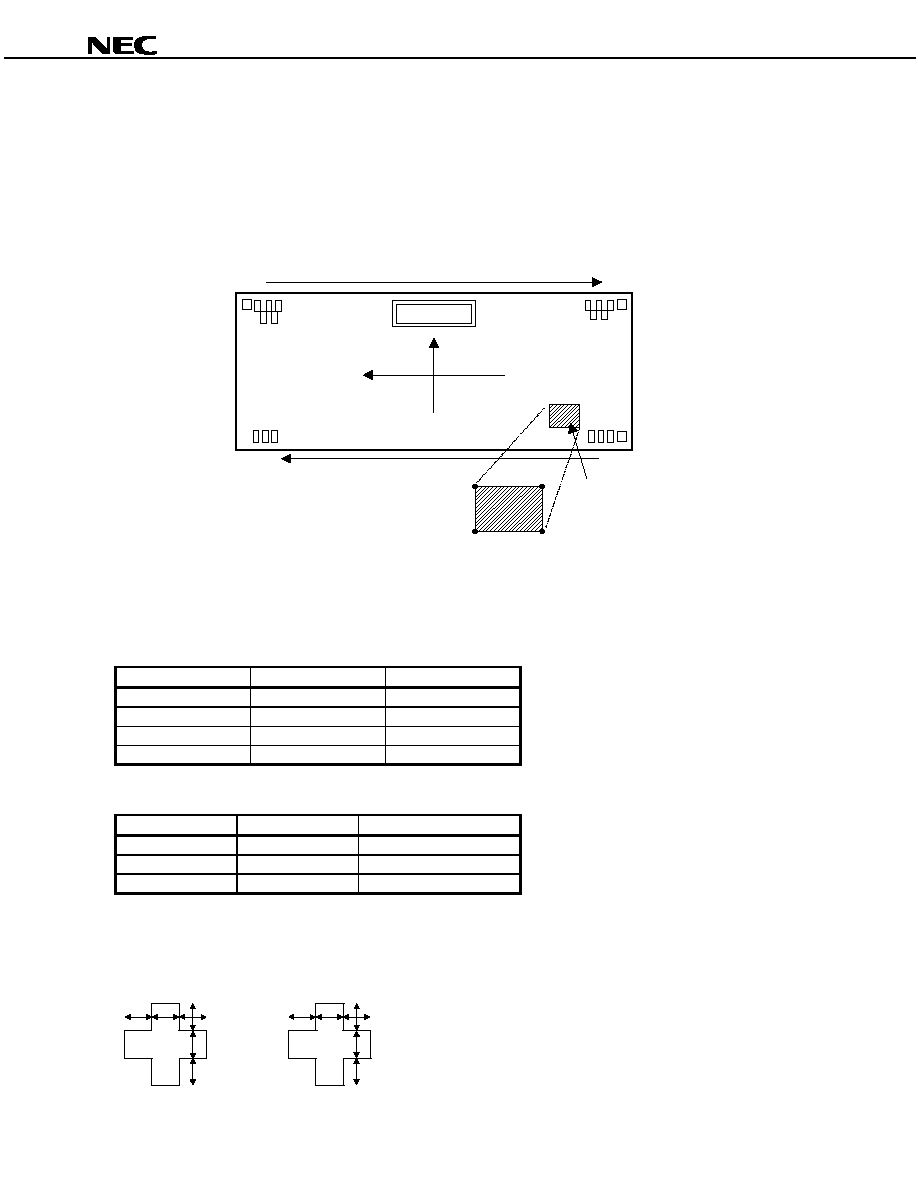

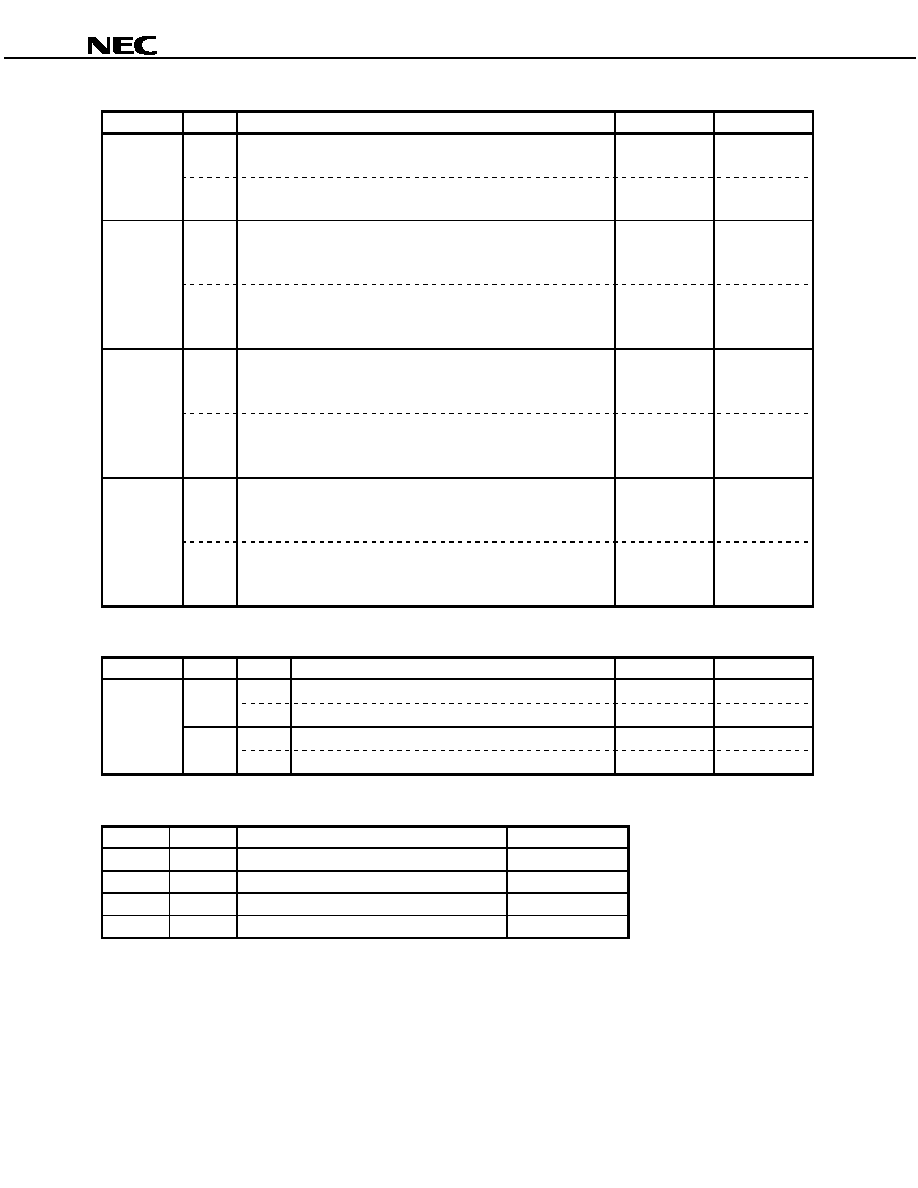

2. PIN CONFIGURATION (Pad Layout)

Chip size: 2.8 x 9.4 mm

2

Bump size

Input/Left/Right (includes DUMMY of input side)

: 100 x 40

µ

m

2

Output (includes DUMMY output side)

: 86 x 35

µ

m

2

Figure 2-1. Chip Schematic

No.145

No.391

No.144

No.1

X

Y

Bump side up

(0,0)

+

+

+

B

D

A

C

Opening in protective film

Note

Note A part of the protective film on the chip surface is absent to enable a transistor check at shipment.

The position of this opening is indicated by the shaded section in the above chip schematic. The specific

coordinates of this opening are as follows.

X (

µ

m)

Y (

µ

m)

A

-

847.74

-

3143.37

B

-

687.75

-

3143.37

C

-

687.75

-

3438.78

D

-

847.74

-

3438.78

Alignment Mark Coordinate (mark center, unit: mm)

X

Y

Shape of Alignment Mark

-

1.125

-

4.5705

Type A

0.9705

4.5495

Type B

0.9705

-

4.5495

Type B

Alignment Mark

Type A Type B

10

µ

m

10

µ

m 10

µ

m

10

µ

m

10

µ

m

10

µ

m

30

µ

m

30

µ

m 30

µ

m

30

µ

m

30

µ

m

30

µ

m

Preliminary Product Information S15797EJ1V4PM

7

µ

µ

µ

µ

PD161644

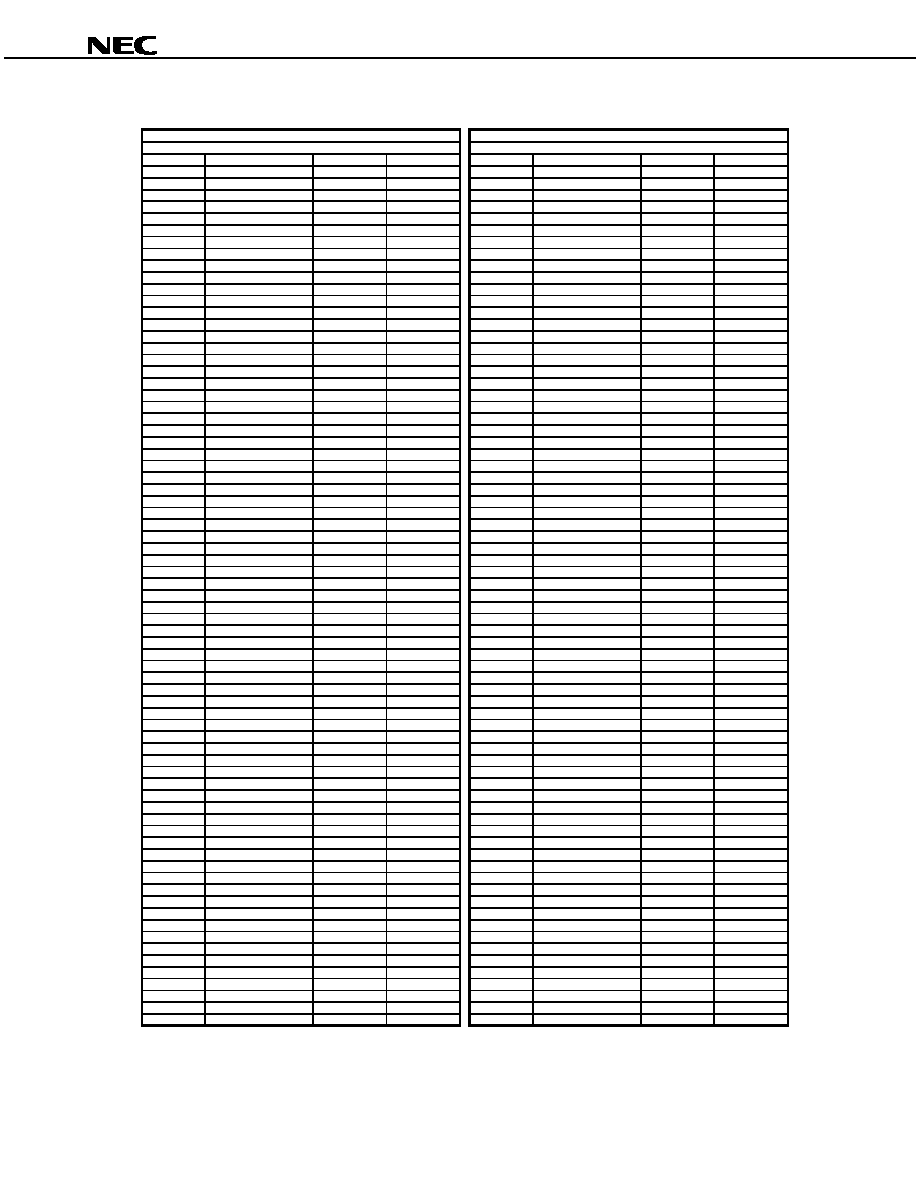

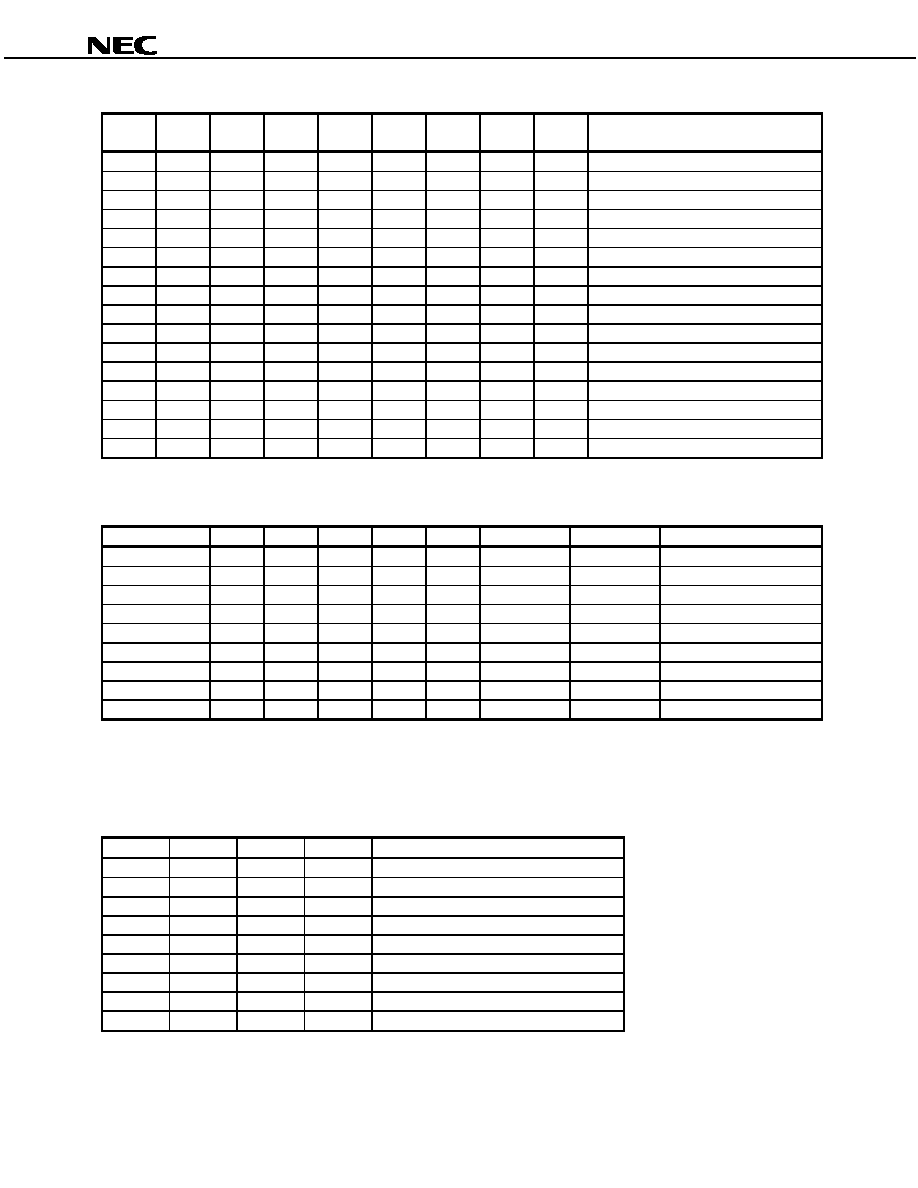

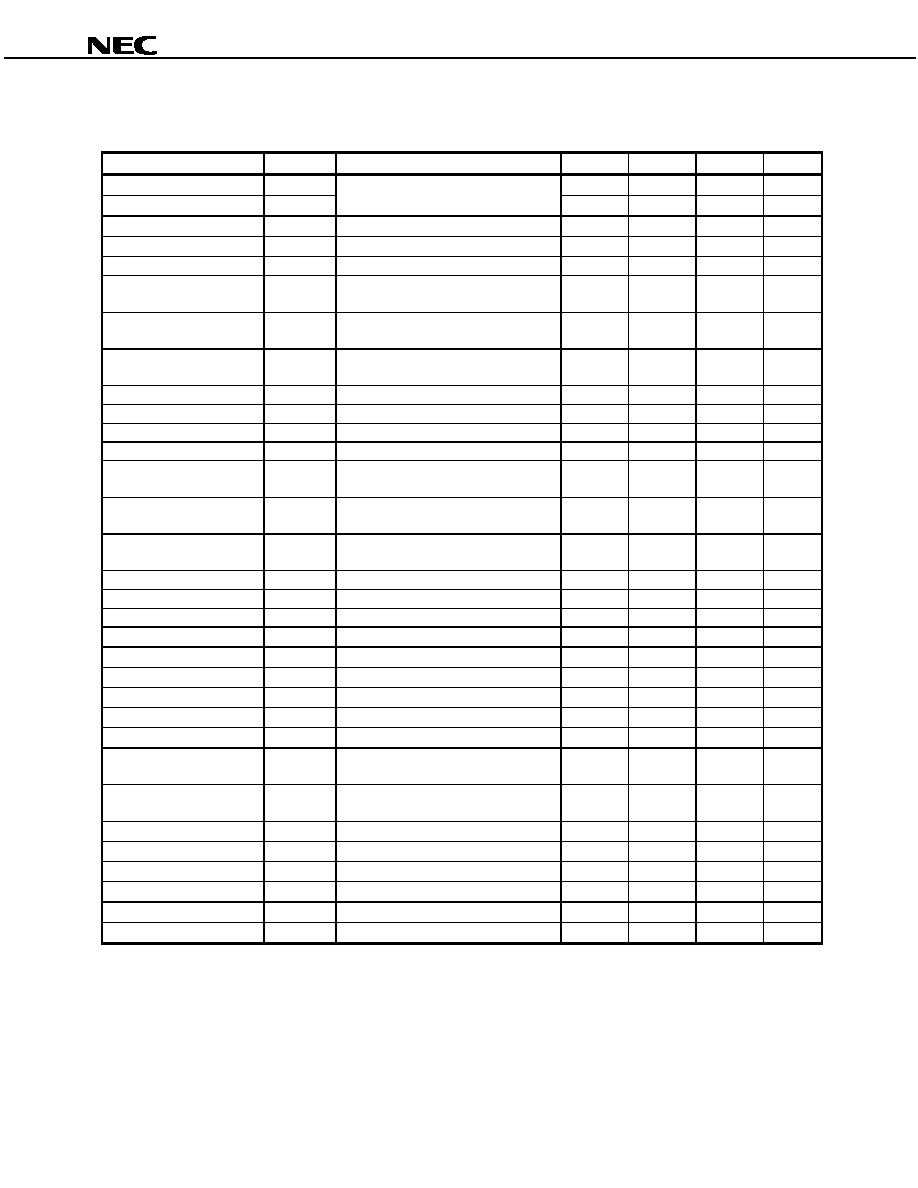

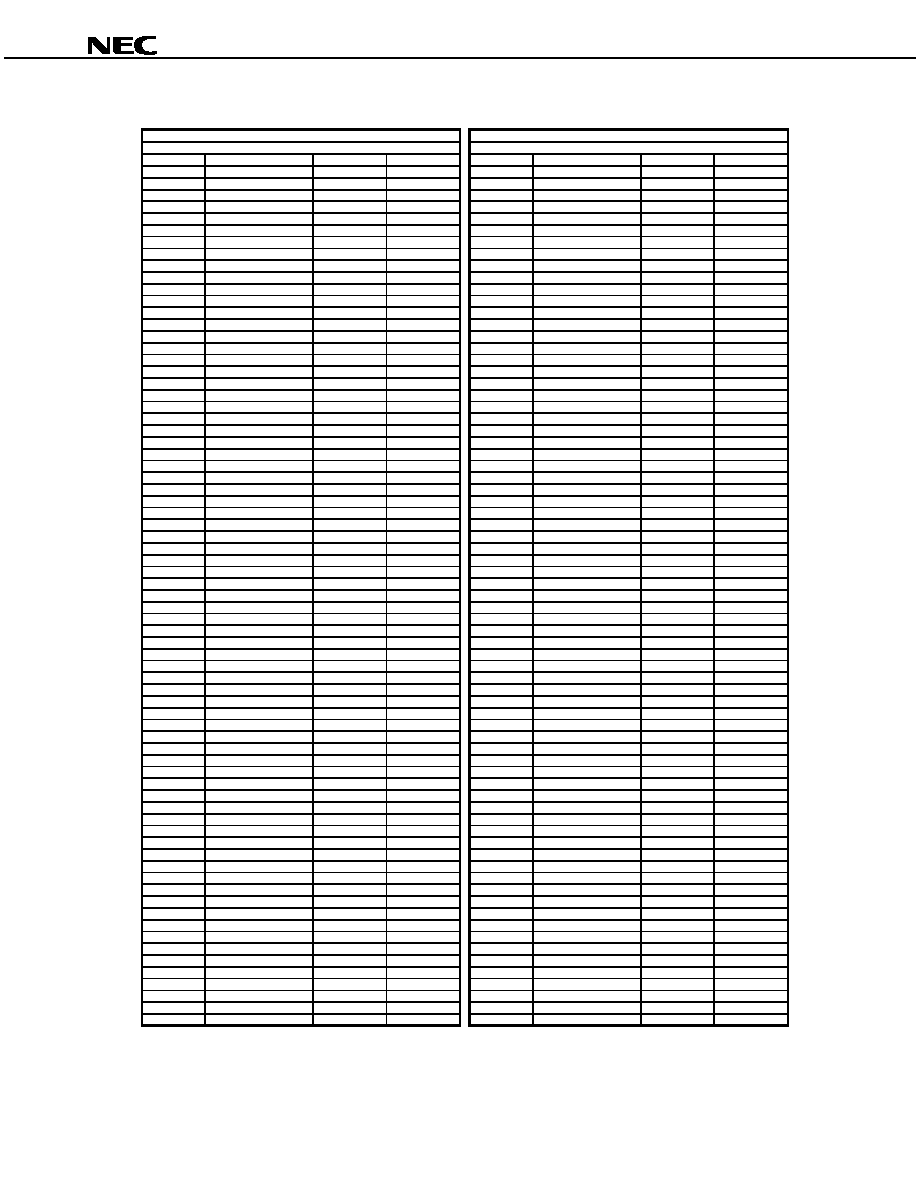

Table 2-1. Pad Layout (1/3)

PADTYPE : BUMP SIZE 100

µ

m x 40

µ

m

PADTYPE : BUMP SIZE 100

µ

m x 40

µ

m

GATE INPUTS

GATE INPUTS

PAD No.

PAD NAME

X [mm]

Y [mm]

PAD No.

PAD NAME

X [mm]

Y [mm]

1

DUMMY

-1.242

-4.5500

73

C2+

-1.242

-0.0300

2

TESTOUT2

-1.242

-4.4900

74

C2+

-1.242

0.0300

3

TESTIN2

-1.242

-4.4300

75

C2+

-1.242

0.0900

4

TESTIN1

-1.242

-4.3700

76

C1-

-1.242

0.1600

5

TESTOUT1

-1.242

-4.3100

77

C1-

-1.242

0.2200

6

PVCC1

-1.242

-4.2500

78

C1-

-1.242

0.2800

7

DUPF0

-1.242

-4.1900

79

C1-

-1.242

0.3400

8

PUPT0

-1.242

-4.1300

80

C1+

-1.242

0.4100

9

SCN2

-1.242

-4.0700

81

C1+

-1.242

0.4700

10

SCN1

-1.242

-4.0100

82

C1+

-1.242

0.5300

11

SCN0

-1.242

-3.9500

83

C1+

-1.242

0.5900

12

ACS0

-1.242

-3.8900

84

VDD2

-1.242

0.6600

13

EXRV

-1.242

-3.8300

85

VDD2

-1.242

0.7200

14

VSEL

-1.242

-3.7700

86

VDD2

-1.242

0.7800

15

CLS0

-1.242

-3.7100

87

VDD2

-1.242

0.8400

16

FS2

-1.242

-3.6500

88

VSS1

-1.242

0.9100

17

FS0

-1.242

-3.5900

89

VSS1

-1.242

0.9700

18

VMS

-1.242

-3.5300

90

VSS1

-1.242

1.0300

19

RGONR

-1.242

-3.4700

91

VSS1

-1.242

1.0900

20

PVSS1

-1.242

-3.4100

92

DUMMY

-1.242

1.1600

21

PVSS3

-1.242

-3.3500

93

VDC

-1.242

1.2300

22

VMON

-1.242

-3.2900

94

VDC

-1.242

1.2900

23

DUMMY

-1.242

-3.2300

95

VDC

-1.242

1.3500

24

PVCC1

-1.242

-3.1700

96

VDC

-1.242

1.4100

25

R,/L

-1.242

-3.1100

97

VDC

-1.242

1.4700

26

IFSEL

-1.242

-3.0500

98

VDC

-1.242

1.5300

27

PVSS1

-1.242

-2.9900

99

VDC

-1.242

1.5900

28

VCOMIN

-1.242

-2.9200

100

VDC

-1.242

1.6500

29

VCOM

-1.242

-2.8500

101

VCC1

-1.242

1.7200

30

VCOM

-1.242

-2.7900

102

VCC1

-1.242

1.7800

31

VCOM

-1.242

-2.7300

103

VCC1

-1.242

1.8400

32

COML

-1.242

-2.6600

104

VCC1

-1.242

1.9000

33

COML

-1.242

-2.6000

105

VSS1

-1.242

1.9700

34

COMH

-1.242

-2.5300

106

VSS1

-1.242

2.0300

35

COMH

-1.242

-2.4700

107

VSS1

-1.242

2.0900

36

VM

-1.242

-2.4000

108

VSS1

-1.242

2.1500

37

VM

-1.242

-2.3400

109

VSS1

-1.242

2.2100

38

VB

-1.242

-2.2700

110

VSS1

-1.242

2.2700

39

VB

-1.242

-2.2100

111

VR

-1.242

2.3400

40

VSS3

-1.242

-2.1400

112

VR

-1.242

2.4000

41

VSS3

-1.242

-2.0800

113

VR

-1.242

2.4600

42

VSS3

-1.242

-2.0200

114

VGD

-1.242

2.5300

43

VSS4

-1.242

-1.9500

115

VGD

-1.242

2.5900

44

VSS4

-1.242

-1.8900

116

VGD

-1.242

2.6500

45

VSS4

-1.242

-1.8300

117

MVS

-1.242

2.7200

46

VSS2

-1.242

-1.7600

118

VS

-1.242

2.7900

47

VSS2

-1.242

-1.7000

119

VS

-1.242

2.8500

48

VSS2

-1.242

-1.6400

120

VS

-1.242

2.9100

49

C6-

-1.242

-1.5700

121

VS

-1.242

2.9700

50

C6-

-1.242

-1.5100

122

VS

-1.242

3.0300

51

C6+

-1.242

-1.4400

123

VS

-1.242

3.0900

52

C6+

-1.242

-1.3800

124

DUMMY

-1.242

3.1600

53

C5-

-1.242

-1.3100

125

PVCC1

-1.242

3.2300

54

C5-

-1.242

-1.2500

126

VCD2

-1.242

3.3000

55

C5+

-1.242

-1.1800

127

RGON

-1.242

3.3700

56

C5+

-1.242

-1.1200

128

DCON

-1.242

3.4400

57

C4-

-1.242

-1.0500

129

FRM

-1.242

3.5100

58

C4-

-1.242

-0.9900

130

VCIN

-1.242

3.5800

59

C4+

-1.242

-0.9200

131

PVSS1

-1.242

3.6500

60

C4+

-1.242

-0.8600

132

/GRESET

-1.242

3.7200

61

C3-

-1.242

-0.7900

133

GCS

-1.242

3.7900

62

C3-

-1.242

-0.7300

134

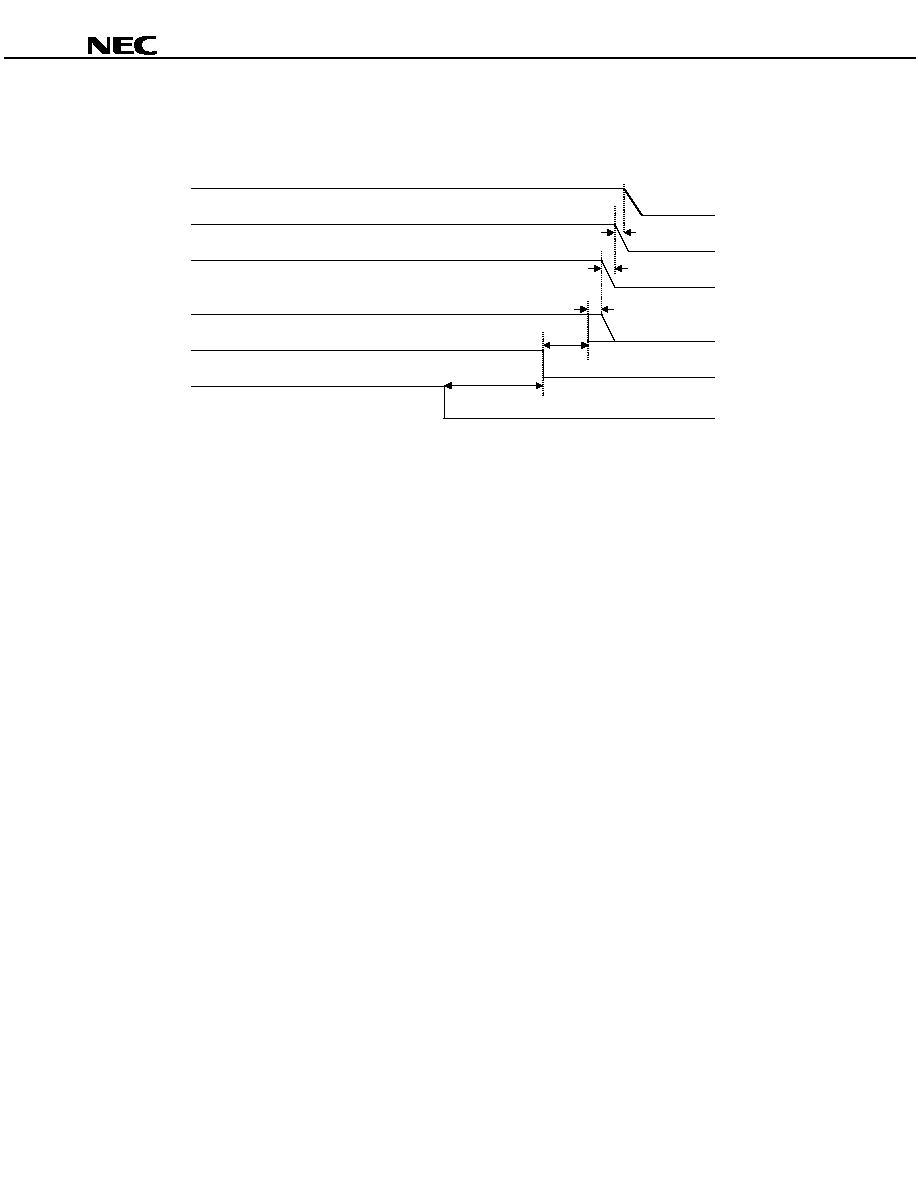

GCL

-1.242

3.8600

63

C3+

-1.242

-0.6600

135

GDA

-1.242

3.9300

64

C3+

-1.242

-0.6000

136

STVR

-1.242

4.0000

65

VDD1

-1.242

-0.5300

137

STVL

-1.242

4.0700

66

VDD1

-1.242

-0.4700

138

DCCLK

-1.242

4.1400

67

VDD1

-1.242

-0.4100

139

CLK

-1.242

4.2100

68

C2-

-1.242

-0.3400

140

OE1

-1.242

4.2800

69

C2-

-1.242

-0.2800

141

OE2

-1.242

4.3500

70

C2-

-1.242

-0.2200

142

DUMMY

-1.242

4.4200

71

C2-

-1.242

-0.1600

143

VSS3

-1.242

4.4900

72

C2+

-1.242

-0.0900

144

DUMMY

-1.242

4.5600

Preliminary Product Information S15797EJ1V4PM

8

µ

µ

µ

µ

PD161644

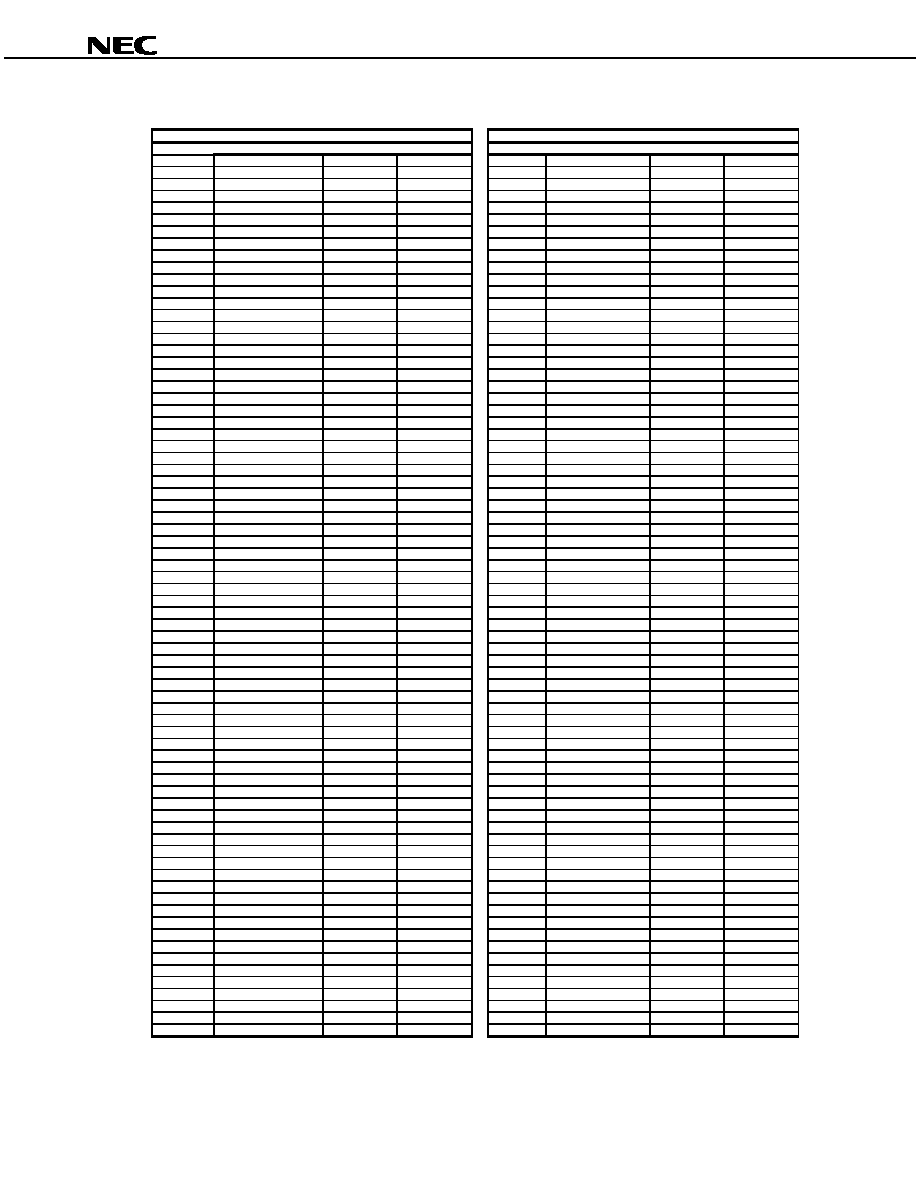

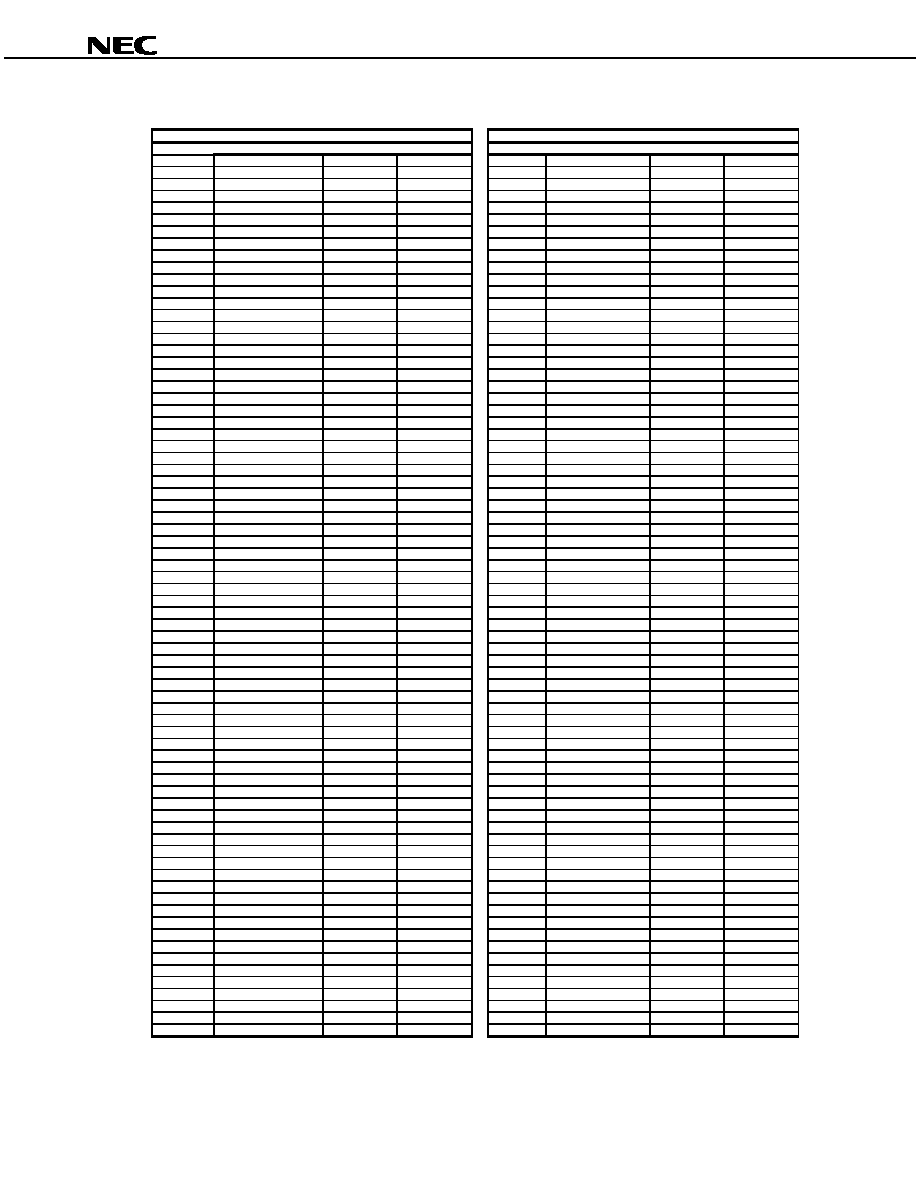

Table 2-1. Pad Layout (2/3)

PADTYPE : BUMP SIZE 86

µ

m x 35

µ

m

PADTYPE : BUMP SIZE 86

µ

m x 35

µ

m

GATE OUTPUTS 35

µ

m pitch

GATE OUTPUTS 35

µ

m pitch

PAD No.

PAD NAME

X [mm]

Y [mm]

PAD No.

PAD NAME

X [mm]

Y [mm]

145

DUMMY

1.249

4.3050

217

O172

1.249

1.7850

146

DUMMY

1.127

4.2700

218

O171

1.127

1.7500

147

DUMMY

1.249

4.2350

219

O170

1.249

1.7150

148

O241

1.127

4.2000

220

O169

1.127

1.6800

149

O240

1.249

4.1650

221

O168

1.249

1.6450

150

O239

1.127

4.1300

222

O167

1.127

1.6100

151

O238

1.249

4.0950

223

O166

1.249

1.5750

152

O237

1.127

4.0600

224

O165

1.127

1.5400

153

O236

1.249

4.0250

225

O164

1.249

1.5050

154

O235

1.127

3.9900

226

O163

1.127

1.4700

155

O234

1.249

3.9550

227

O162

1.249

1.4350

156

O233

1.127

3.9200

228

O161

1.127

1.4000

157

O232

1.249

3.8850

229

O160

1.249

1.3650

158

O231

1.127

3.8500

230

O159

1.127

1.3300

159

O230

1.249

3.8150

231

O158

1.249

1.2950

160

O229

1.127

3.7800

232

O157

1.127

1.2600

161

O228

1.249

3.7450

233

O156

1.249

1.2250

162

O227

1.127

3.7100

234

O155

1.127

1.1900

163

O226

1.249

3.6750

235

O154

1.249

1.1550

164

O225

1.127

3.6400

236

O153

1.127

1.1200

165

O224

1.249

3.6050

237

O152

1.249

1.0850

166

O223

1.127

3.5700

238

O151

1.127

1.0500

167

O222

1.249

3.5350

239

O150

1.249

1.0150

168

O221

1.127

3.5000

240

O149

1.127

0.9800

169

O220

1.249

3.4650

241

O148

1.249

0.9450

170

O219

1.127

3.4300

242

O147

1.127

0.9100

171

O218

1.249

3.3950

243

O146

1.249

0.8750

172

O217

1.127

3.3600

244

O145

1.127

0.8400

173

O216

1.249

3.3250

245

O144

1.249

0.8050

174

O215

1.127

3.2900

246

O143

1.127

0.7700

175

O214

1.249

3.2550

247

O142

1.249

0.7350

176

O213

1.127

3.2200

248

O141

1.127

0.7000

177

O212

1.249

3.1850

249

O140

1.249

0.6650

178

O211

1.127

3.1500

250

O139

1.127

0.6300

179

O210

1.249

3.1150

251

O138

1.249

0.5950

180

O209

1.127

3.0800

252

O137

1.127

0.5600

181

O208

1.249

3.0450

253

O136

1.249

0.5250

182

O207

1.127

3.0100

254

O135

1.127

0.4900

183

O206

1.249

2.9750

255

O134

1.249

0.4550

184

O205

1.127

2.9400

256

O133

1.127

0.4200

185

O204

1.249

2.9050

257

O132

1.249

0.3850

186

O203

1.127

2.8700

258

O131

1.127

0.3500

187

O202

1.249

2.8350

259

O130

1.249

0.3150

188

O201

1.127

2.8000

260

O129

1.127

0.2800

189

O200

1.249

2.7650

261

O128

1.249

0.2450

190

O199

1.127

2.7300

262

O127

1.127

0.2100

191

O198

1.249

2.6950

263

O126

1.249

0.1750

192

O197

1.127

2.6600

264

O125

1.127

0.1400

193

O196

1.249

2.6250

265

O124

1.249

0.1050

194

O195

1.127

2.5900

266

O123

1.127

0.0700

195

O194

1.249

2.5550

267

O122

1.249

0.0350

196

O193

1.127

2.5200

268

O121

1.127

0.0000

197

O192

1.249

2.4850

269

O120

1.249

-0.0350

198

O191

1.127

2.4500

270

O119

1.127

-0.0700

199

O190

1.249

2.4150

271

O118

1.249

-0.1050

200

O189

1.127

2.3800

272

O117

1.127

-0.1400

201

O182

1.249

2.3450

273

O116

1.249

-0.1750

202

O187

1.127

2.3100

274

O115

1.127

-0.2100

203

O186

1.249

2.2750

275

O114

1.249

-0.2450

204

O185

1.127

2.2400

276

O113

1.127

-0.2800

205

O184

1.249

2.2050

277

O112

1.249

-0.3150

206

O183

1.127

2.1700

278

O111

1.127

-0.3500

207

O182

1.249

2.1350

279

O110

1.249

-0.3850

208

O181

1.127

2.1000

280

O109

1.127

-0.4200

209

O180

1.249

2.0650

281

O108

1.249

-0.4550

210

O179

1.127

2.0300

282

O107

1.127

-0.4900

211

O178

1.249

1.9950

283

O106

1.249

-0.5250

212

O177

1.127

1.9600

284

O105

1.127

-0.5600

213

O176

1.249

1.9250

285

O104

1.249

-0.5950

214

O175

1.127

1.8900

286

O103

1.127

-0.6300

215

O174

1.249

1.8550

287

O102

1.249

-0.6650

216

O173

1.127

1.8200

288

O101

1.127

-0.7000

Preliminary Product Information S15797EJ1V4PM

9

µ

µ

µ

µ

PD161644

Table 2-1. Pad Layout (3/3)

PADTYPE : BUMP SIZE 86

µ

m x 35

µ

m

PADTYPE : BUMP SIZE 86

µ

m x 35

µ

m

GATE OUTPUTS 35

µ

m pitch

GATE OUTPUTS 35

µ

m pitch

PAD No.

PAD NAME

X [mm]

Y [mm]

PAD No.

PAD NAME

X [mm]

Y [mm]

289

O100

1.249

-0.7350

361

O28

1.249

-3.2550

290

O99

1.127

-0.7700

362

O27

1.127

-3.2900

291

O98

1.249

-0.8050

363

O26

1.249

-3.3250

292

O97

1.127

-0.8400

364

O25

1.127

-3.3600

293

O96

1.249

-0.8750

365

O24

1.249

-3.3950

294

O95

1.127

-0.9100

366

O23

1.127

-3.4300

295

O94

1.249

-0.9450

367

O22

1.249

-3.4650

296

O93

1.127

-0.9800

368

O21

1.127

-3.5000

297

O92

1.249

-1.0150

369

O20

1.249

-3.5350

298

O91

1.127

-1.0500

370

O19

1.127

-3.5700

299

O90

1.249

-1.0850

371

O18

1.249

-3.6050

300

O89

1.127

-1.1200

372

O17

1.127

-3.6400

301

O88

1.249

-1.1550

373

O16

1.249

-3.6750

302

O87

1.127

-1.1900

374

O15

1.127

-3.7100

303

O86

1.249

-1.2250

375

O14

1.249

-3.7450

304

O85

1.127

-1.2600

376

O13

1.127

-3.7800

305

O84

1.249

-1.2950

377

O12

1.249

-3.8150

306

O83

1.127

-1.3300

378

O11

1.127

-3.8500

307

O82

1.249

-1.3650

379

O10

1.249

-3.8850

308

O81

1.127

-1.4000

380

O9

1.127

-3.9200

309

O80

1.249

-1.4350

381

O8

1.249

-3.9550

310

O79

1.127

-1.4700

382

O7

1.127

-3.9900

311

O78

1.249

-1.5050

383

O6

1.249

-4.0250

312

O77

1.127

-1.5400

384

O5

1.127

-4.0600

313

O76

1.249

-1.5750

385

O4

1.249

-4.0950

314

O75

1.127

-1.6100

386

O3

1.127

-4.1300

315

O74

1.249

-1.6450

387

O2

1.249

-4.1650

316

O73

1.127

-1.6800

388

O1

1.127

-4.2000

317

O72

1.249

-1.7150

389

DUMMY

1.249

-4.2350

318

O71

1.127

-1.7500

390

DUMMY

1.127

-4.2700

319

O70

1.249

-1.7850

391

DUMMY

1.249

-4.3050

320

O69

1.127

-1.8200

321

O68

1.249

-1.8550

322

O67

1.127

-1.8900

323

O66

1.249

-1.9250

324

O65

1.127

-1.9600

325

O64

1.249

-1.9950

326

O63

1.127

-2.0300

327

O62

1.249

-2.0650

328

O61

1.127

-2.1000

329

O60

1.249

-2.1350

330

O59

1.127

-2.1700

331

O58

1.249

-2.2050

332

O57

1.127

-2.2400

333

O56

1.249

-2.2750

334

O55

1.127

-2.3100

335

O54

1.249

-2.3450

336

O53

1.127

-2.3800

337

O52

1.249

-2.4150

338

O51

1.127

-2.4500

339

O50

1.249

-2.4850

340

O49

1.127

-2.5200

341

O48

1.249

-2.5550

342

O47

1.127

-2.5900

343

O46

1.249

-2.6250

344

O45

1.127

-2.6600

345

O44

1.249

-2.6950

346

O43

1.127

-2.7300

347

O42

1.249

-2.7650

348

O41

1.127

-2.8000

349

O40

1.249

-2.8350

350

O39

1.127

-2.8700

351

O38

1.249

-2.9050

352

O37

1.127

-2.9400

353

O36

1.249

-2.9750

354

O35

1.127

-3.0100

355

O34

1.249

-3.0450

356

O33

1.127

-3.0800

357

O32

1.249

-3.1150

358

O31

1.127

-3.1500

359

O30

1.249

-3.1850

360

O29

1.127

-3.2200

Preliminary Product Information S15797EJ1V4PM

10

µ

µ

µ

µ

PD161644

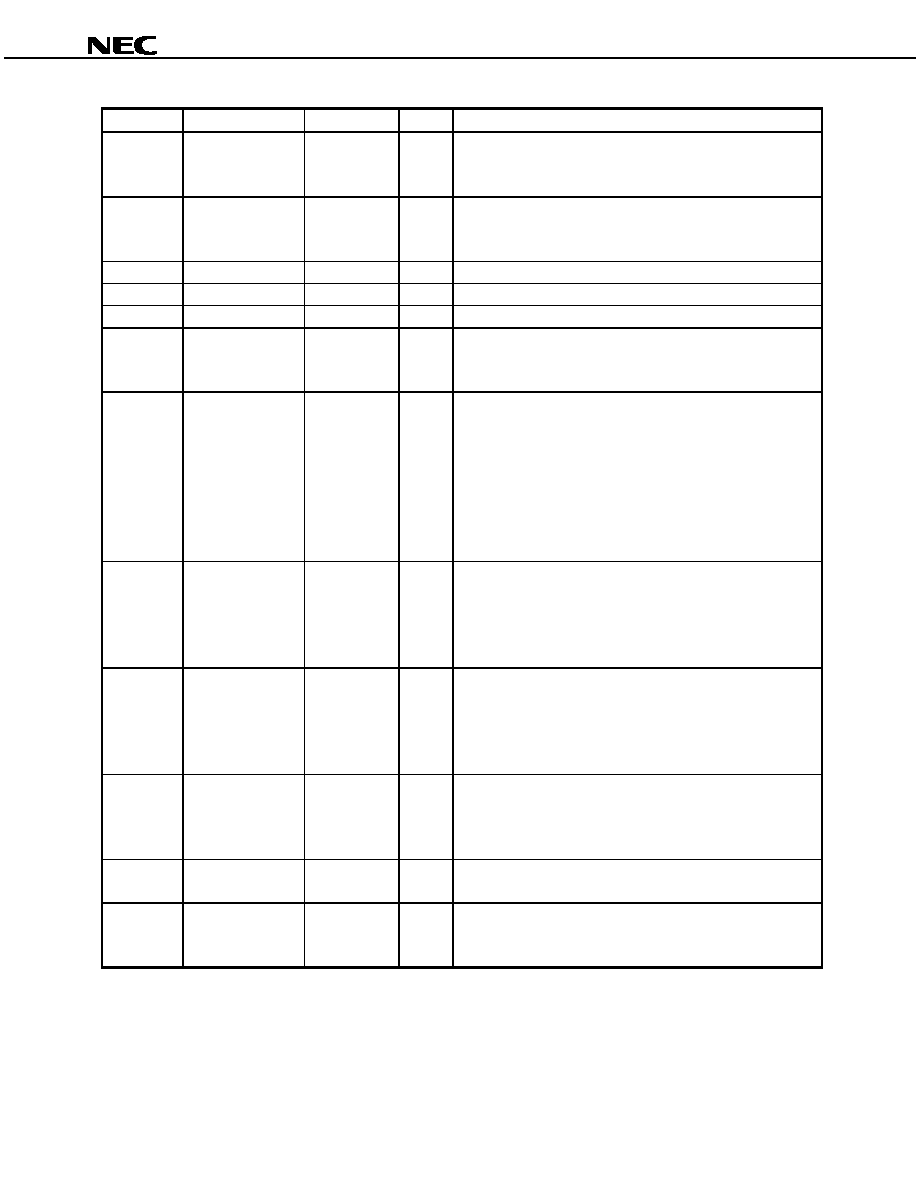

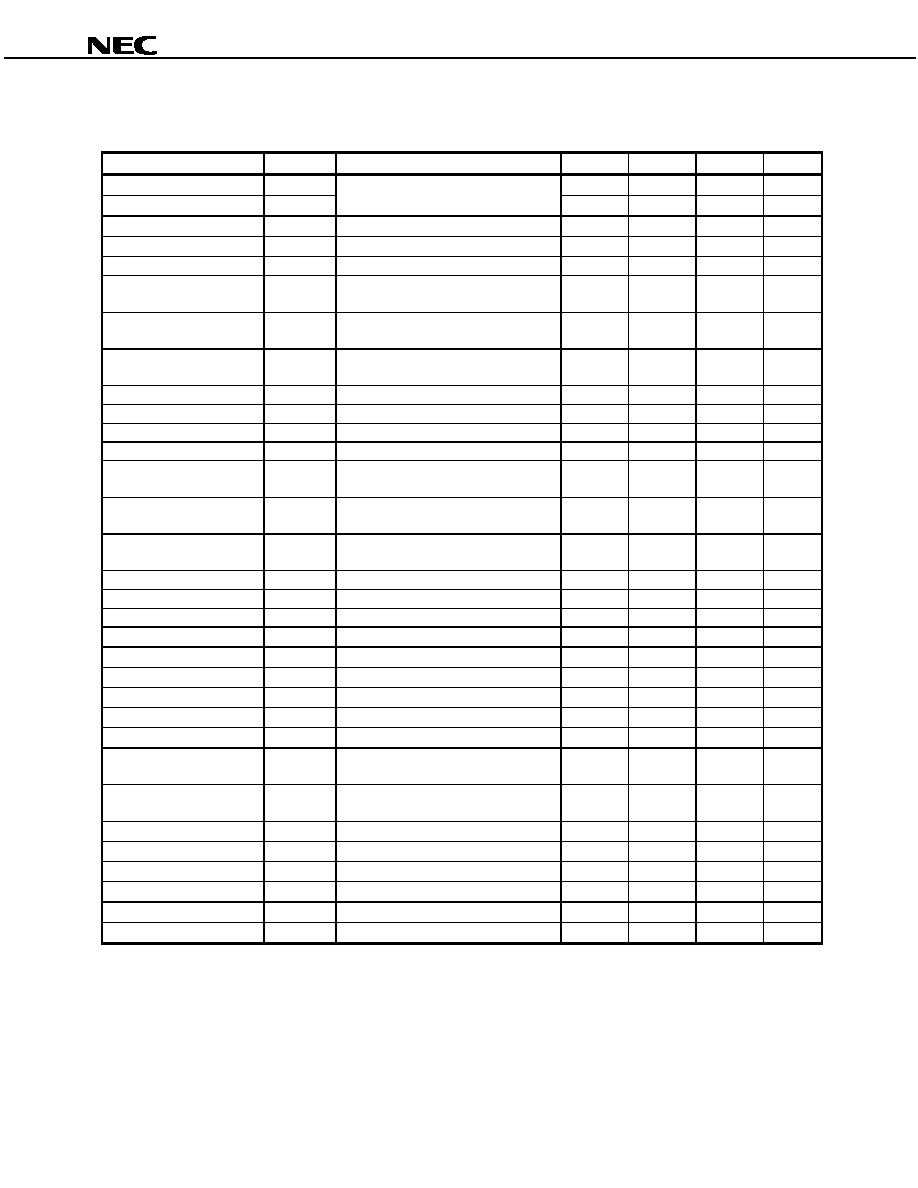

3. PIN FUNCTIONS

(1/5)

Symbol

Pin Name

Pad No.

I/O

Function

V

DC

DC/DC converter

reference voltage

93 to 100

-

Reference voltage input pin for DC/DC converter.

V

CC1

Logic reference

voltage

101 to 104

-

2.5 to 3.3 V LS (level shifter) reference voltage input pin.

V

SS1

Ground

88 to 91,

105 to 110

-

Connect to the system ground.

VGD

Power supply input

for DC/DC converter

114 to 116

Input

Reference voltage input pin for V

DD1

, V

SS1

to V

SS4

boost.

Connect to any of V

DD2,

V

R

or V

S

.

V

DD1

DC/DC converter

output

65 to 67

Output

Boost output voltage of DC/DC converter (VGD x 2 or x 3).

The boost step number of V

DD1

is selected according to how the

external capacitor is connected. The boost reference voltage can

be set using VGD. Refer to the function of VGD pin.

V

DD2

DC/DC converter

output

84 to 87

Output

Boost output voltage of DC/DC converter (V

DC

x 2 or x 3). The

boost step number of V

DD2

can be set using VCD2.

V

SS2

DC/DC converter

output

46 to 48

Output

Boost output voltage of DC/DC converter (VGD x

-

1 or x

-

2).

The boost step number of V

SS2

is selected according to how the

external capacitor is connected. The boost reference voltage can

be set using VGD. Refer to the function of VGD pin.

V

SS3

DC/DC converter

output

40 to 42, 143

Output

Boost output voltage of DC/DC converter (VGD

x

-

2 or x

-

3).

The boost step number of V

SS3

is selected according to how the

external capacitor is connected. The boost reference voltage can

be set using VGD. Refer to VGD pin function.

V

SS4

DC/DC converter

output

43 to 45

Output

Boost output voltage of DC/DC converter (V

DC

x

-

1).

VM

Gate output low

level select voltage

36, 37

Output

The voltage level of V

SS2

or V

SS3

is output synchronized with the

VCIN input.

VCIN = 0: Output the voltage level of V

SS3

VCIN = 1: Output the voltage level of V

SS2

The timing chart is shown in Figure 3-1.

V

B

Driver negative

voltage

38, 39

Input

Negative voltage of output buffer. This is the input pin of the

liquid crystal driver negative voltage. Input the negative power

supply of the gate output. V

B

pin connection examples are

shown in Figure 3-2.

C

1

+

, C

1

-

C

2

+

, C

2

-

C

3

+

, C

3

-

C

4

+

, C

4

-

C

5

+

, C

5

-

C

6

+

, C

6

-

Capacitor connect

pin for boost

80 to 83, 76 to 79,

72 to 75, 68 to 71,

63, 64, 61, 62,

59, 60, 57, 58,

55, 56, 53, 54,

51, 52, 49, 50

Output

To connect booster for DC/DC converter.

For the recommended values of the capacitance and

withstanding voltage of each capacitor, refer to

9. RECOMMENDED CAPACITANCE VALUES OF EXTERNAL

CAPACITOR.

V

R

Power supply

output for DC/DC

converter

111 to 113

Output

Positive power supply voltage output for the DC/DC converter.

The V

R

output voltage can be changed by setting VRSEL0 to

VRSEL2.

Preliminary Product Information S15797EJ1V4PM

11

µ

µ

µ

µ

PD161644

(2/5)

Symbol

Pin Name

Pad No.

I/O

Function

V

S

Positive power

output supply for

driver

118 to 123

Output

Positive power supply voltage output for source driver. The V

S

output voltage can be changed by setting VSEL0 to VSEL2.

MVS

External resistor

input

117

Input

Any output voltage can be set by connecting an external resistor.

<EXRV = 0> Leave open.

<EXRV = 1> Connect to external resistor.

PV

CC1

Pull-up voltage

6, 24, 125

-

Pull-up voltage for mode setting pin.

PV

SS1

Pull-down voltage

20, 27, 131

-

Pull-down voltage for mode setting pin.

PV

SS3

Pull-down voltage

21

-

Pull-down voltage for mode setting pin.

CLK

Shift clock input

139

Input

Shift clock input pin of the internal shift resistor. The contents of

internal shift resistor are shifted at the rising edge of CLK.

Connect to GCLK pin of source driver.

STVR,

STVL

Start pulse

input/output pin

136,

137

I/O

Input/output pin of the internal shift resistor.

Start pulse signal is read at the rising edge of shift clock CLK and a

scan signal is output from the driver output pin.

The valid level of the STVR/STVL pin is determined by the setting

of STVSEL.

When STVSEL = L, the pulse becomes low level at the falling

edge of the 240th shift clock CLK and high level at falling edge of

the 241st clock.

OE

1

Enable input

140

Input

If the level selected by OE1SEL is input, the driver output is fixed to

low level (When OE1SEL = L the driver output is fixed to low level if

a low level is input). However, the shift resistor is not cleared. And,

output enable actuation is asynchronous in the clock.

Connect to GOE

1

pin of source driver.

OE

2

Enable input

141

Input

If the level selected by OE2SEL is input, the driver output is fixed to

high level (When OE2SEL = L the driver output is fixed to low level

if a high level is input). However, the shift resistor is not cleared.

And, output enable actuation is asynchronous in the clock.

Connect to GOE

2

pin of source driver.

R,/L

Shift direction

control

25

Input

The shift direction control pin of shift register. The shift directions

of the shift registers are as follows.

R,/L = H (right shift): STVR input, O

1

O

241

,

STVL output

R,/L = L (left shift) : STVL input, O

241

O

1

,

STVR output

FRM

Frame signal input

129

Input

Input frame reverse signals.

Connect to GFRAME pin of source driver.

DCCLK

Clock input for

DC/DC converter

138

Input

To input the external clock for the DC/DC converter.

This pin is valid only when CLS0 = 1 and CLS1 = 1. In other

settings, leave open.

Preliminary Product Information S15797EJ1V4PM

12

µ

µ

µ

µ

PD161644

(3/5)

Symbol

Pin Name

Pad No.

I/O

Function

O

1

to O

241

Driver output pins

388 to 148

Output

Scan signal output pins that drive the gate electrode of a TFT-

LCD. The status of each output pin changes in synchronization

with the rising edge of shift clock CLK. The output voltage of the

driver is V

DD1

to V

B

.

COMH

Common high level

output

34, 35

Output

<COMON = 1> High level of common voltage is output. The voltage

level changes accordance with DA

0

to DA

7

and CDA

0

to CDA

7

.

<COMON = 0> Leave open when not using it.

COML

Common low level

output

32, 33

Output

<COMON = 1> Low level of common voltage is output. The voltage

level changes accordance with DA

0

to DA

7

and CDA

0

to CDA

7

.

<COMON = 0> Leave open when not using it.

VCOM

Common output

29 to 31

Output

<COMON = 1> The common voltage synchronized with the VCIN

input is output.

Connect to common pin of panel.

<COMON = 0> Leave open when not using it.

VCOMIN

VCOM center

voltage input

28

Input

VCOM center voltage input pin. Leave open when COMSEL = 0.

<COMSEL = 0> Internal D/A is valid.

<COMSEL = 1> VCOMIN input voltage is valid.

VCIN

Common pulse

input

130

Input

To input common pulse. Connect to VCOUT3 pin of source driver.

Fix this pin to low when not using it.

/GRESET

Reset input

132

Input

Reset input pin. Connect to /GRESET pin of source driver.

If /GRESET is made low, the serial interface is initialized (the

register values are not initialized). A reset operation is executed

according to the level of the /GRESET signal. Be sure to execute

a reset using this pin at power application.

IFSEL

Interface selection

26

Input

The serial interface input switching pin.

<IFSEL = 0> Serial interface input.

The DCON, RGONR, VCD2, VMS, FS0, FS2, CLS0, RGON, VSEL,

EXRV, ACS0, SCN0 to SCN2, PUPT0, DUPF0 pins should be left

open.

<IFSEL = 1> Control pin input.

The GCS, GCL, GDA pins should be left open.

GCS

Chip select input

133

Input

<IFSEL = 0> To input chip select signals.

Connect to GCS pin of source driver.

<IFSEL = 1> Leave open.

GCL

Serial clock input

134

Input

<IFSEL = 0> To input serial clock signals.

Connect to GCL pin of source driver.

<IFSEL = 1> Leave open.

GDA

Serial data input

135

Input

<IFSEL = 0> To input serial data signals.

Connect to GDA pin of source driver.

<IFSEL = 1> Leave open.

Preliminary Product Information S15797EJ1V4PM

13

µ

µ

µ

µ

PD161644

(4/5)

Symbol

Pin Name

Pad No.

I/O

Function

DCON

DC/DC converter

control

128

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> The DC/DC converter ON/OFF control signal is input.

Connect to the DCON pin of the source driver.

<DCON = 0> DC/DC converter OFF

<DCON = 1> DC/DC converter ON

RGONR

V

R

regulator control 19

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> The V

R

regulator ON/OFF control signal is input.

<RGONR = 0> V

R

regulator OFF

<RGONR = 1> V

R

regulator ON

VCD2

V

DD2

boost

selection

126

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> The V

DD2

boost step number select pin.

<VCD2 = 0> V

DD2

= V

DC

x 2

<VCD2 = 1> V

DD2

= V

DC

x 3

VMS

V

DD2

boost

selection

18

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> V

DD2

boost mode select pin.

<VMS = 0> V

DD2

: single boost mode

<VMS = 1> V

DD2

: dual boost mode

FS0

V

DD2,

V

SS4

boost

frequency selection

in scan mode

17

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> V

DD2

,

V

SS4

boost frequency select pin in scan mode.

<FS0 = 0 > f

OSC

/2

<FS0 = 1 > f

OSC

/4

FS2

V

DD1

, V

SS2

, V

SS3

boost frequency

selection in scan

mode

16

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> V

DD1

, V

SS2

, V

SS3

boost frequency select pin

in scan

mode.

<FS2 = 0 > f

OSC

/2

<FS2 = 1, > f

OSC

/4

CLS0

DC/DC OSC

frequency selection

15

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> Select pin of the OSC oscillation frequency for DC/DC

converter.

<CLS0 = 0> f

OSC

= 25 kHz, DCCLK: Open

<CLS0 = 1> External CK input mode

RGON

V

S

regulator control 127

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> The V

S

regulator ON/OFF control signal is input.

Connect this pin to the RGON pin of the source driver.

<RGON = 0> V

S

regulator OFF

<RGON = 1> V

S

regulator ON

VSEL

V

S

regulator voltage

selection

14

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> Select pin of output voltage for V

S

regulator.

<VSEL = 1> V

S

= 4 V

<VSEL = 0> V

S

= 5 V

EXRV

V

S

regulating resistor

selection

13

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> Select pin of external resistor for V

S

regulator.

<EXRV = 0> Internal resistor setting mode.

<EXRV = 1> Any output voltage can be set by connecting MVS to

an external resistor.

Preliminary Product Information S15797EJ1V4PM

14

µ

µ

µ

µ

PD161644

(5/5)

Symbol

Pin Name

Pad No.

I/O

Function

ACS0

Amp. current

selection in scan

mode

12

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> Amp. current select pin in scan mode.

<ACS0 = 0> Amp. current = 5

µ

A

<ACS0 = 1> Amp. current = 15

µ

A

SCN0,

SCN1,

SCN2

Gate scan selection

11,

10,

9

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> Select pin of gate scan order.

<SCN0 = 1, SCN1 = 1, SCN2 = 1> MODE1

<SCN0 = 1, SCN1 = 1, SCN2 = 0> MODE2

<SCN0 = 1, SCN1 = 0, SCN2 = 1> MODE3

<SCN0 = 1, SCN1 = 0, SCN2 = 0> MODE4

<SCN0 = 0, SCN1, SCN2 = x> MODE5

PUPT0

Setting pin of

DC/DC converter

power on time

8

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> This pin sets the rising time of V

DD1

, V

DD2

, V

SS2

to

V

SS4

at DC/DC converter power on time.

DUPF0

Operating frequency

setting pin at

DC/DC converter

power on

7

Input

<IFSEL = 0> Leave open (Internal resistors are valid).

<IFSEL = 1> This pin sets the operating frequency at DC/DC

converter power on time.

<DUPT0 = 0> f

OSC

/8

<DUPT0 = 1> f

OSC

/16

VMON

Stand-by current

reduction control

pin

22

Input

The standby current reduction control pin.

<VMON = PV

SS3

> Normal mode.

A quiescent current of about 0.5

µ

A is consumed in standby mode.

When the V

CC1

voltage drops, the driver output pins are fixed to

ALL-High.

<VMON = PV

CC1

> Standby current reduction mode.

Makes the quiescent current consumed in standby mode 0.

When the V

CC1

voltage drops, the driver output pins are undefined.

TESTOUT1

V

REF

reference

voltage output

5

Output

The V

REF

voltage measurement pin. Leave open.

TESTIN1,

TESTIN2

TEST input pin

4,

3

Input

Test input pins. Leave open.

TESTOUT2

TEST output pin

2

Output

Test output pin. Leave open.

DUMMY

Dummy

1, 23, 92, 124,

142, 144 to 147,

389 to 391

-

Dummy data

Preliminary Product Information S15797EJ1V4PM

15

µ

µ

µ

µ

PD161644

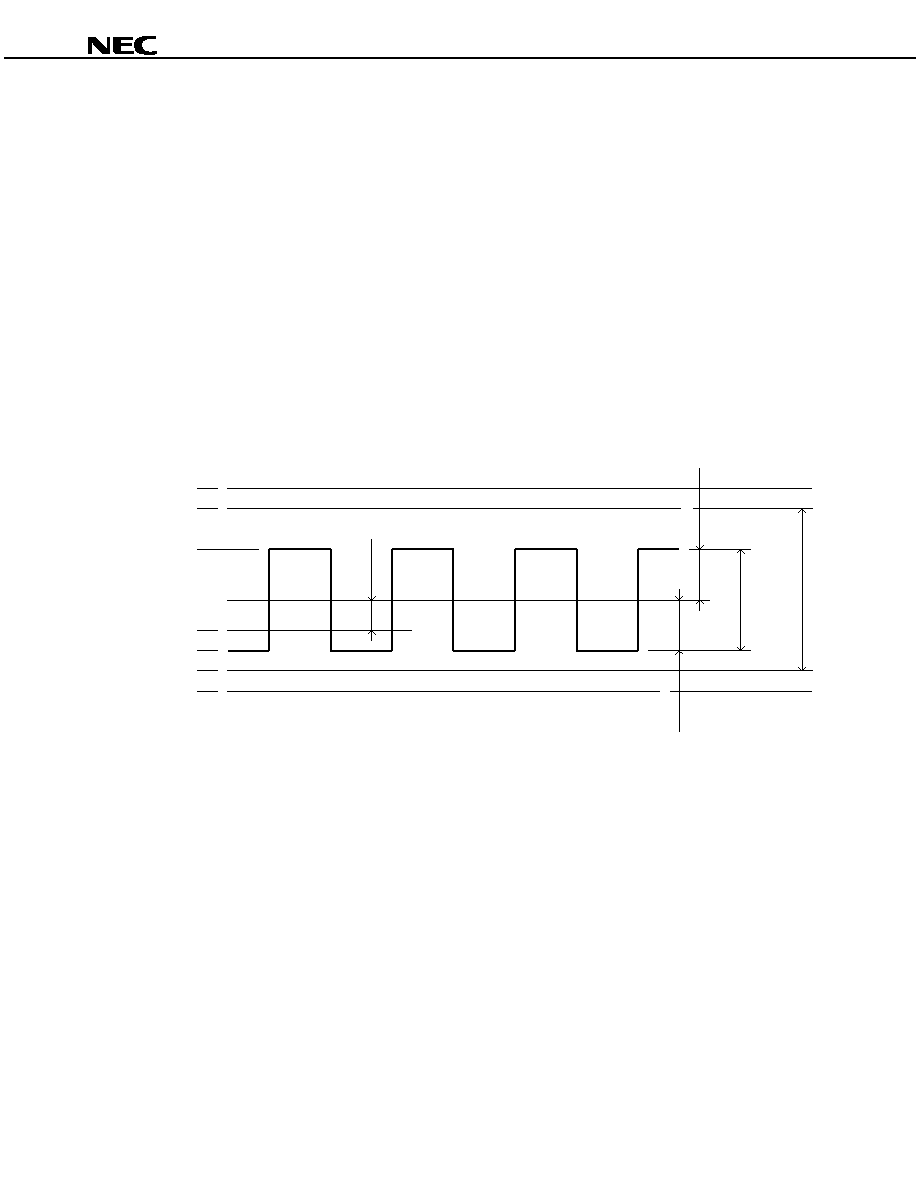

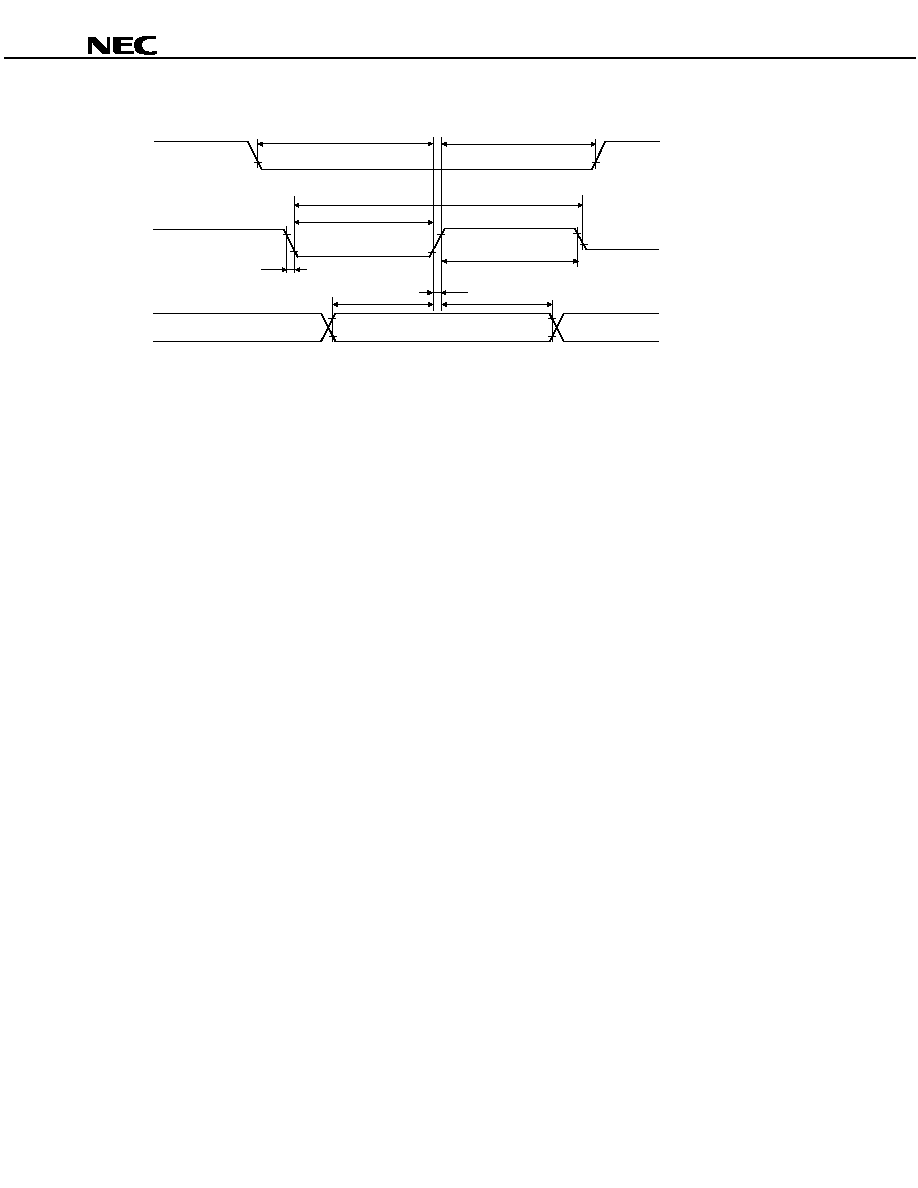

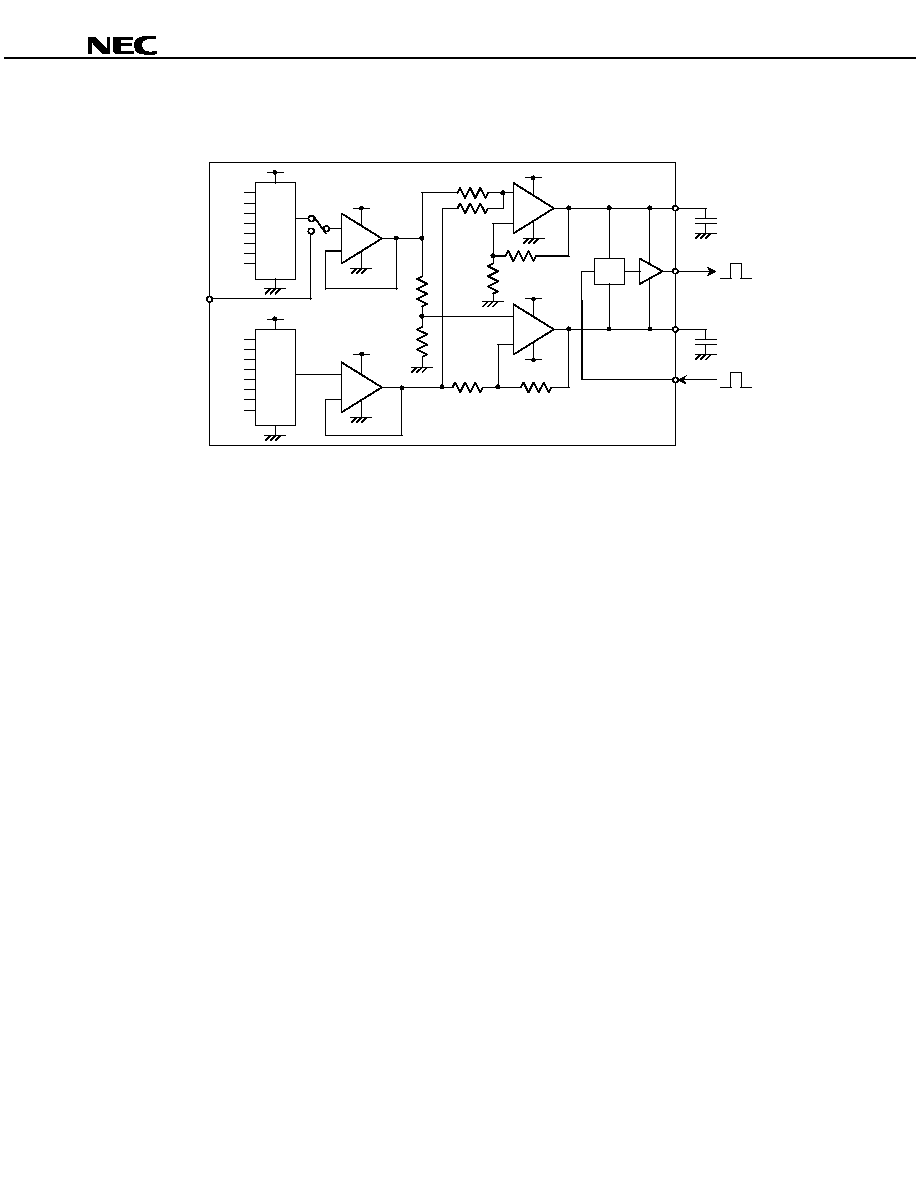

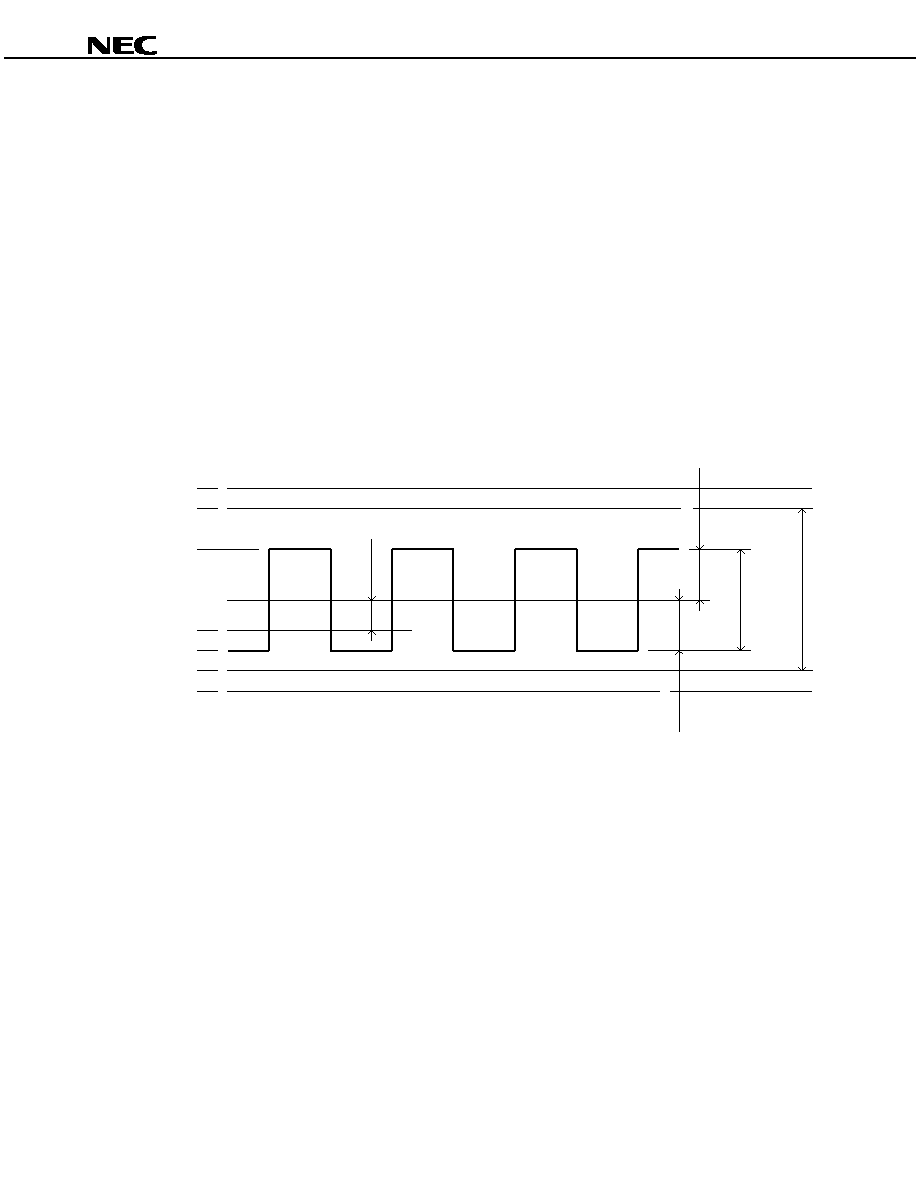

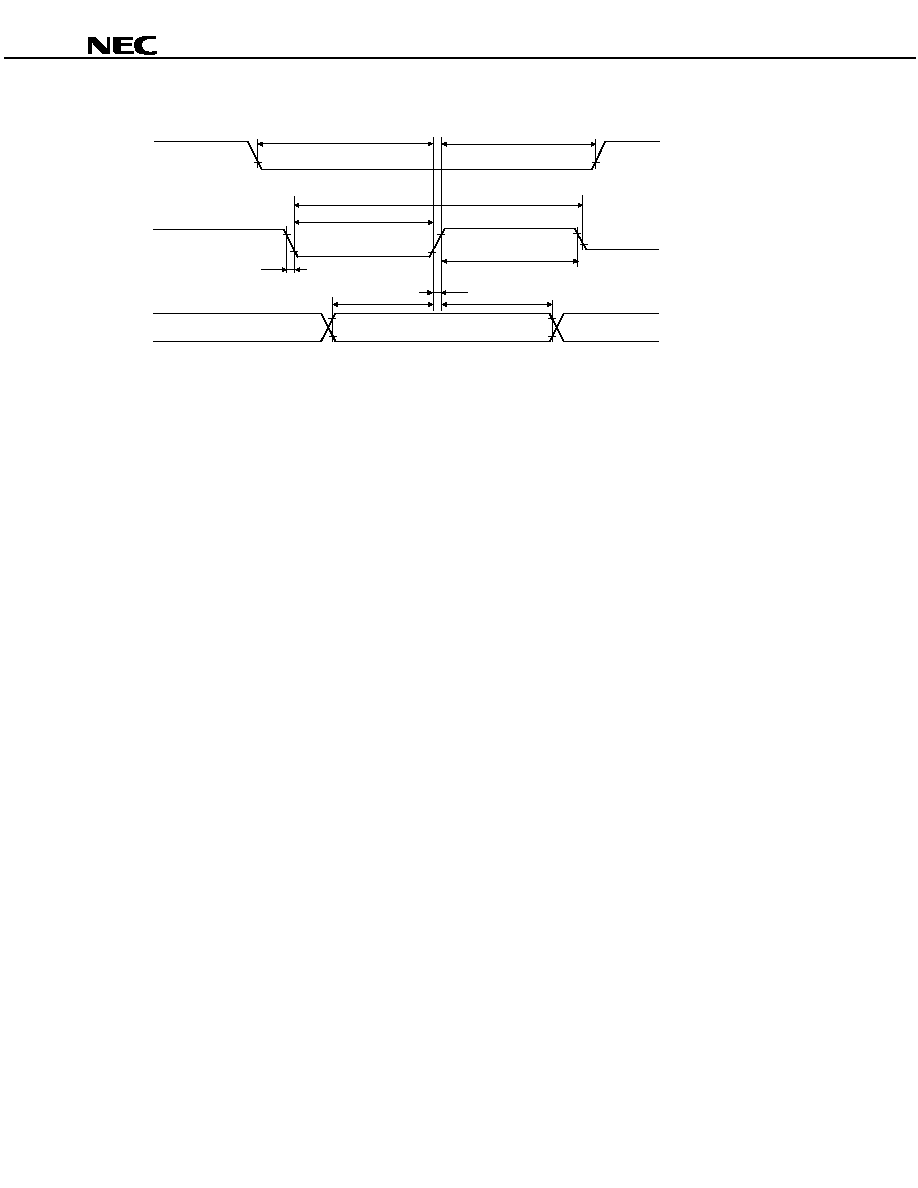

Figure 3-1. VM signal Timing Chart

V

SS

V

CC1

V

SS

V

CC1

V

SS

V

CC1

V

SS

V

CC1

GOE1ON(R59) = "1"

DC/DC converter ON

CLK = "H" + OE

1

= "L" : Hi-Z

CLK = "H": Hi-Z

Output Hi-Z term

V

SS

V

CC1

Remark Hi-Z (High impedance)

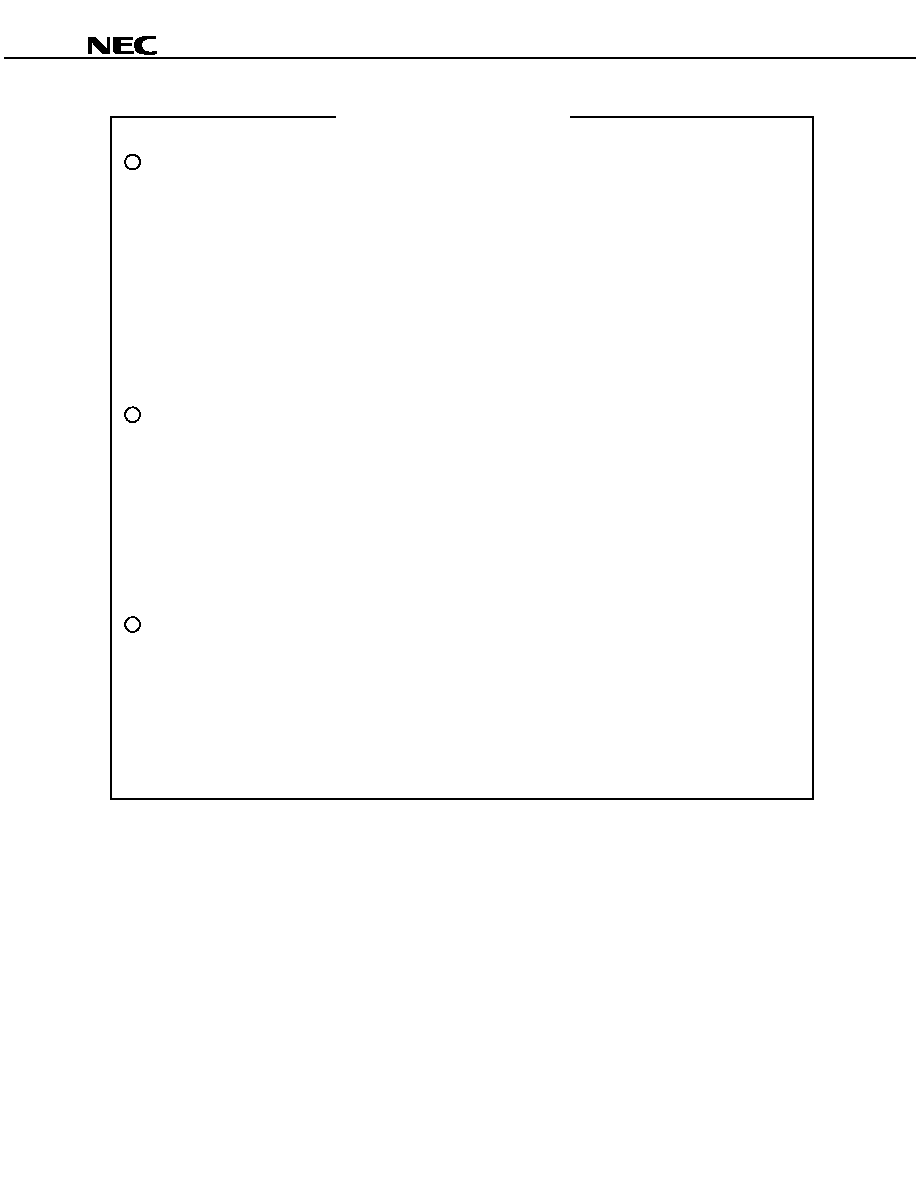

Figure 3-2. Examples of V

B

pin connection

(a) When the negative voltage level of the gate output

is set to V

SS3

Lev

el

s

h

i

f

t

e

r

VCIN

VM

V

B

O

1

O

2

O

241

V

SS2

V

SS3

V

DD1

to Panel gate line

µ

µ

µ

µ

PD161644

DC/DC converter

V

SS2

V

SS3

VGD

V

DD1

open

V

S

or V

R

open

(b) When the negative voltage level of the gate output

is switched between V

SS2

and V

SS3

Lev

el

s

h

i

f

t

e

r

VCIN

VM

V

B

O

1

O

2

O

241

V

SS2

V

SS3

V

DD1

to Panel gate line

µ

µ

µ

µ

PD161644

DC/DC converter

V

SS2

V

SS3

VGD

V

DD1

VCOUT3

V

S

or

V

R

common

driving signal

from

µ

PD161621

Preliminary Product Information S15797EJ1V4PM

16

µ

µ

µ

µ

PD161644

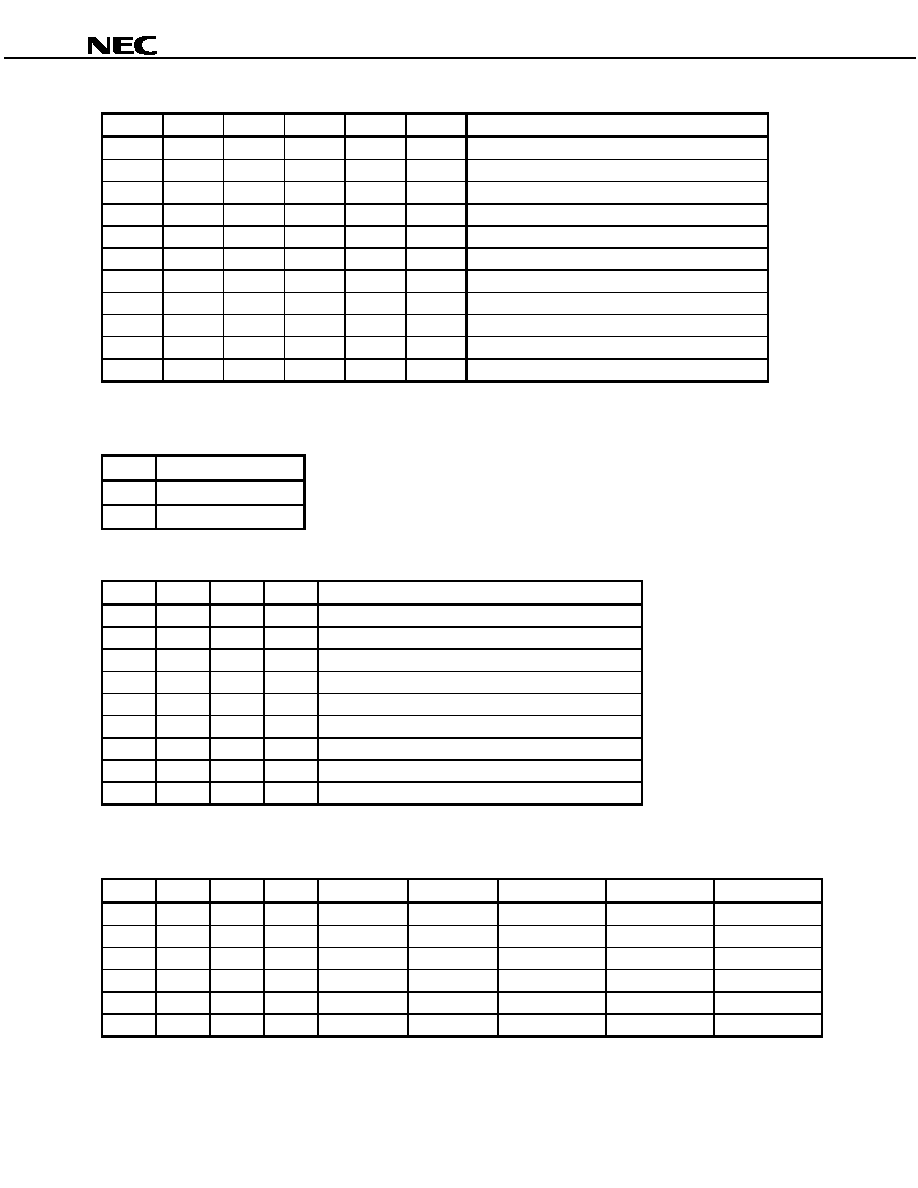

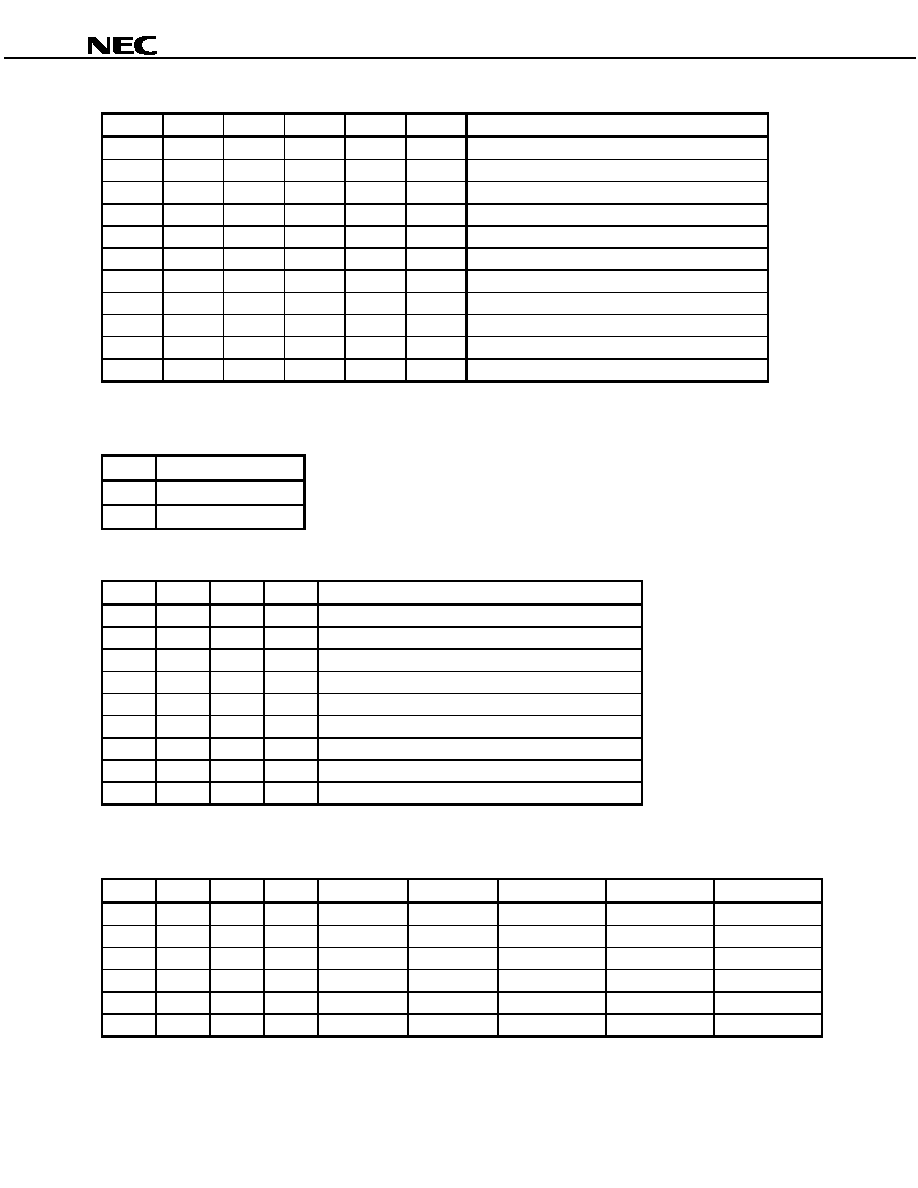

4. COMMAND

4.1 Command List

Data bit

7 6 5 4 3 2 1 0

Rn

Register

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

0 0 0 1 1 0 0 0 R24 DC/DC operation setting

RGONR VS4ON VS3ON VS2ON VD2ON VD1ON DCON

0 0 0 1 1 0 0 1 R25 DC/DC step setting

VRSEL2VRSEL1 VRSEL0 VMS

VCD2

0 0 0 1 1 0 1 0 R26 DC/DC oscillation setting

FUP

CLS1

CLS0

FS3

FS2

FS1

FS0

0 0 0 1 1 0 1 1 R27

Regulator output setting

ACS1

ACS0

EXRV VSEL2

VSEL1 VSEL0 RGON

0 0 0 1 1 1 0 0 R28 LPM setting

LACS1 LACS0

LFS3

LFS2

LFS1

LFS0

LPM

0 0 0 1 1 1 0 1 R29 Gate scan setting

OE2SEL OE1SELSTVSEL SCN2

SCN1

SCN0

0 0 0 1 1 1 1 0 R30 Gate mode setting

COMHI

COMSEL

COMON NLINE2 NLINE1

0 0 0 1 1 1 1 1 R31 Common amplitude setting

DA

7

DA

6

DA

5

DA

4

DA

3

DA

2

DA

1

DA

0

0 0 1 0 0 0 0 0 R32 Common center setting

CDA

7

CDA

6

CDA

5

CDA

4

CDA

3

CDA

2

CDA

1

CDA

0

0 0 1 0 0 0 0 1 R33 DC/DC power on setting

PONM

PON

DUPF1 DUPF0 PUPT1 PUPT0

0 0 1 0 0 0 1 0 R34 Reset

RES

4.2 Command Description

Reset the internal data at power application by inputting a low level to the /GRESET pin.

(1/5)

Resistor

Bit

Symbol

Reset

Function

Description

R24

D

0

DCON

0

DC/DC converter control

Control ON/OFF of DC/DC converter.

<DCON = 0> DC/DC converter OFF

<DCON = 1> DC/DC converter ON

D

1

VD1ON

0

V

DD1

boost control

Control ON/OFF of V

DD1

boost.

<VD1ON = 0> V

DD1

boost OFF

<VD1ON = 1> V

DD1

boost ON

D

2

VD2ON

0

V

DD2

boost control

Control V

DD2

boost ON/OFF.

<VD2ON = 0> V

DD2

boost OFF

<VD2ON = 1> V

DD2

boost ON

D

3

VS2ON

0

V

SS2

boost control

Control

VSS2

boost ON/OFF.

<VS2ON = 0> V

SS2

boost OFF

<VS2ON = 1> V

SS2

boost ON

D

4

VS3ON

0

V

SS3

boost control

Control V

SS3

boost ON/OFF.

<VS3ON = 0> V

SS3

boost OFF

<VS3ON = 1> V

SS3

boost ON

D

5

VS4ON

0

V

SS4

boost control

Control V

SS4

boost ON/OFF.

<VS4ON = 0> V

SS4

boost OFF

<VS4ON = 1> V

SS4

boost ON

D

6

RGONR

0

V

R

regulator control

Control ON/OFF of V

R

regulator.

<RGONR = 0> V

R

regulator OFF

<RGONR = 1> V

R

regulator ON

Preliminary Product Information S15797EJ1V4PM

17

µ

µ

µ

µ

PD161644

(2/5)

Resistor

Bit

Symbol

Reset

Function

Description

R25

D

0

VCD2

0

V

DD2

boost selection

Select the number of V

DD2

boost step (x2/x3).

<VCD2 = 0> V

DD2

= V

DC

x 2

<VCD2 = 1> V

DD2

= V

DC

x 3

D

1

VMS

1

V

DD2

boost mode

selection

Select V

DD2

boost mode.

<VMS = 0> V

DD2

= Single boost mode

<VMS = 1> V

DD2

= Dual boost mode

D

2

VRSEL0

1

D

3

VRSEL1

0

D

4

VRSEL2

1

V

R

regulator output

voltage selection

Select output voltage of V

R

regulator. When IFSEL = 1, V

R

is fixed to 5 V.

<VRSEL0 = 0, VRSEL1 = 0, VRSEL2 = 0> V

R

= 3 V

<VRSEL0 = 1, VRSEL1 = 0, VRSEL2 = 0> V

R

= 3.5 V

<VRSEL0 = 0, VRSEL1 = 1, VRSEL2 = 0> V

R

= 4 V

<VRSEL0 = 1, VRSEL1 = 1, VRSEL2 = 0> V

R

= 4.5 V

<VRSEL0 = 0, VRSEL1 = 0, VRSEL2 = 1> V

R

= 4.75 V

<VRSEL0 = 1, VRSEL1 = 0, VRSEL2 = 1> V

R

= 5 V

<VRSEL0 = 0, VRSEL1 = 1, VRSEL2 = 1> V

R

= 5.25 V

<VRSEL0 = 1, VRSEL1 = 1, VRSEL2 = 1> V

R

= 5.5 V

D

0

FS0

1

R26

D

1

FS1

0

V

DD2

, V

SS4

boost

frequency selection in

scan mode

Select V

DD2,

V

SS4

boost frequency in scan mode. When

IFSEL = 1, FS1 is fixed to 0.

<FS0 = 0, FS1 = 0> f

OSC

/2 <FS0 = 1, FS1 = 0> f

OSC

/4

<FS0 = 0, FS1 = 1> f

OSC

/8 <FS0 = 1, FS1 = 1> f

OSC

/16

D

2

FS2

1

D

3

FS3

0

V

DD1

, V

SS2

, V

SS3

boost frequency

selection in scan mode

Select V

DD1

, V

SS2

, V

SS3

boost frequency in scan mode.

When IFSEL = 1, FS3 is fixed to 0.

<FS2 = 0, FS3 = 0> f

OSC

/2 <FS2 = 1, FS3 = 0> f

OSC

/4

<FS2 = 0, FS3 = 1> f

OSC

/8 <FS2 = 1, FS3 = 1> f

OSC

/16

D

4

CLS0

1

D

5

CLS1

0

DC/DC OSC frequency

selection

Select oscillation frequency of OSC for DC/DC converter.

When IFSEL = 1, CLS1 is fixed to 1.

<CLS0 = 0, CLS1 = 0> f

OSC

= 18 kHz, DCCLK: Open

<CLS0 = 1, CLS1 = 0> f

OSC

= 25 kHz, DCCLK: Open

<CLS0 = 0, CLS1 = 1> f

OSC

= 37 kHz, DCCLK: Open

<CLS0 = 1, CLS1 = 1> External CK input mode

D

6

FUP

0

Switching of DC/DC

OSC frequency

Select oscillation frequency of OSC for DC/DC converter.

When IFSEL = 1, the frequency is fixed to f

OSC

.

<FUP = 0> f

OSC

<FUP = 1> f

OSC

x 2

Preliminary Product Information S15797EJ1V4PM

18

µ

µ

µ

µ

PD161644

(3/5)

Resistor

Bit

Symbol

Reset

Function

Description

R27

D

0

RGON

0

V

S

regulator control

Control ON/OFF of V

S

regulator.

<RGON = 0> V

S

regulator OFF

<RGON = 1> V

S

regulator ON

D

1

VSEL0

1

D

2

VSEL1

0

D

3

VSEL2

1

V

S

regulator output

voltage selection

Select the output voltage of V

S

regulator.

VSEL0 = 0: V

S

= 5 V, VSEL = 1: V

S

= 4 V when IFSEL = 1.

<VSEL0 = 0, VSEL1 = 0, VSEL2 = 0> V

S

= 3 V

<VSEL0 = 1, VSEL1 = 0, VSEL2 = 0> V

S

= 3.5 V

<VSEL0 = 0, VSEL1 = 1, VSEL2 = 0> V

S

= 4 V

<VSEL0 = 1, VSEL1 = 1, VSEL2 = 0> V

S

= 4.5 V

<VSEL0 = 0, VSEL1 = 0, VSEL2 = 1> V

S

= 4.75 V

<VSEL0 = 1, VSEL1 = 0, VSEL2 = 1> V

S

= 5 V

<VSEL0 = 0, VSEL1 = 1, VSEL2 = 1> V

S

= 5.25 V

<VSEL0 = 1, VSEL1 = 1, VSEL2 = 1> V

S

= 5.5 V

D

4

EXRV

0

V

S

regulator resistor

selection

Select external resistor of V

S

regulator.

<EXRV = 0> Internal resistor mode

<EXRV = 1> Connect external resistor to MVS and set any

level of voltage

D

5

ACS0

0

D

6

ACS1

0

Amp. current selection

in scan mode

Select Amp. current of V

R

and V

S

regulators in scan mode.

When IFSEL = 1, ACS1 is fixed to 0.

<ACS0 = 0, ACS1 = 0> Amp. current = 5

µ

A

<ACS0 = 0, ACS1 = 1> Amp. current = 10

µ

A

<ACS0 = 1, ACS1 = 0> Amp. current = 15

µ

A

<ACS0 = 1, ACS1 = 1> Amp. current = 30

µ

A

R28

D

0

LPM

0

Low power mode

control

Control in low power mode. When IFSEL = 1, LPM is fixed

to 0.

<LPM = 0> Scan mode

<LPM = 1> Low power mode

D

1

LFS0

0

D

2

LFS1

0

V

DD2

, V

SS4

boost

frequency selection in

low power mode

Select boost frequency of V

DD2

, V

SS4

in low power mode.

<LFS0 = 0, LFS1 = 0> f

OSC

/8

<LFS0 = 1, LFS1 = 0> f

OSC

/16

<LFS0 = 0, LFS1 = 1> f

OSC

/32

<LFS0 = 1, LFS1 = 1> f

OSC

/64

D

3

LFS2

0

D

4

LFS3

0

V

DD1

, V

SS2

, V

SS3

boost frequency

selection in low power

mode

Select boost frequency of V

DD1,

V

SS2

, V

SS3

in low power

mode.

<LFS2 = 0, LFS3 = 0> f

OSC

/8

<LFS2 = 1, LFS3 = 0> f

OSC

/16

<LFS2 = 0, LFS3 = 1> f

OSC

/32

<LFS2 = 1, LFS3 = 1> f

OSC

/64

D

5

LACS0

0

D

6

LACS1

0

Amp. current selection

in low power mode

Select Amp. current in low power mode.

<LACS0 = 0, LACS1 = 0> Amp. current = 1.25

µ

A

<LACS0 = 0, LACS1 = 1> Amp. current = 2.5

µ

A

<LACS0 = 1, LACS1 = 0> Amp. current = 5

µ

A

<LACS0 = 1, LACS1 = 1> Amp. current = 7.5

µ

A

Preliminary Product Information S15797EJ1V4PM

19

µ

µ

µ

µ

PD161644

(4/5)

Resistor

Bit

Symbol

Reset

Function

Description

D

0

SCN0

1

D

1

SCN1

1

R29

D

2

SCN2

1

Gate scan selection

Select scan order of gate scan.

<SCN0 = 1, SCN1 = 1, SCN2 = 1> MODE1

<SCN0 = 1, SCN1 = 1, SCN2 = 0> MODE2

<SCN0 = 1, SCN1 = 0, SCN2 = 1> MODE3

<SCN0 = 1, SCN1 = 0, SCN2 = 0> MODE4

<SCN0 = 0, SCN1, SCN2 = X> MODE5

D

3

STVSEL

0

Start pulse input/output

valid level selection

Select start pulse input/output valid level to STVR/STVL.

But there is no pin to select start pulse input/output valid

level. When IFSEL = H (When using control pins), low-fixed

is valid. Refer to 4.3 Command Setting Values When

IFSEL = H (When Using Control Pins).

<STVSEL= 0> Low level is valid.

<STVSEL= 1> High level is valid.

D

4

OE1SEL

0

OE

1

valid level selection

Select valid level of OE

1

. But there is no pin to select valid

level of OE

1

. When IFSEL = H (When using control pins),

low-fixed is valid. Refer to 4.3 Command Setting Values

When IFSEL = H (When Using Control Pins).

<OE1SEL = 0> OE

1

= Low, gate output OFF

<OE1SEL = 1> OE

1

= High, gate output OFF

D

5

OE2SEL

0

OE

2

valid level selection

Select valid level of OE

2

. There is no pin to select valid

level of OE

2

. When IFSEL = H (When using control pins),

low-fixed is valid. Refer to 4.3 Command Setting Values

When IFSEL = H (When Using Control Pins).

<OE2SEL = 0> OE

2

= Low, gate output ON

<OE2SEL = 1> OE

2

= High, gate output ON

D

0

NLINE1

1

R30

D

1

NLINE2

1

Gate mode selection

Select 1-line skip, 2-line skip or N frame inversion of a gate

scan. When IFSEL = 1, this is fixed to normal mode.

<NLINE1 = 1, NLINE2 = 1> Normal mode

<NLINE1 = 1, NLINE2 = 0> 1-line skip mode

<NLINE1 = 0, NLINE2 = 1> 2-line skip mode

<NLINE1 = 0, NLINE2 = 0> N frame inversion

D

2

COMON

0

COM output control

Control ON/OFF of COM output. When IFSEL = 1, COMON

is fixed to 0.

<COMON = 0> COM_AMP, COM output OFF

<COMON = 1> COM_AMP, COM output ON

D

3

COMSEL

0

VCOM center input

selection

Select VCOM center voltage input.

<COMSEL = 0> Internal D/A is valid.

<COMSEL = 1> VCOMIN input voltage is valid.

D

4

COMHI

0

VCOM output selection

Select VCOM output.

<COMHI = 0> VCOM = Hi-Z

<COMHI = 1> VCOM = Output

Preliminary Product Information S15797EJ1V4PM

20

µ

µ

µ

µ

PD161644

(5/5)

Resistor

Bit

Symbol

Reset

Function

Description

R31

D

0

to D

7

DA

0

to DA

7

0

COM amplitude control

Control COM output amplitude using 8-bit D/A.

R32

D

0

to D

7

CDA

0

to CDA

7

0

COM center level control

Control COM output center level using 8-bit D/A.

D

0

PUPT0

0

R33

D

1

PUPT1

1

Setting of DC/DC

converter power on time

This pin sets the ON time of V

DD1

and V

DD2

, V

SS2

to V

SS4

,

and RGON when the DC/DC converter is started up. This

setting is valid only when PONM = 1. When IFSEL = 1,

PUPT1 is fixed to 0.

D

2

DUPF0

1

D

3

DUPF1

0

Setting of DC/DC

converter power on

operating frequency

This pin sets the DC/DC operating frequency when the

DC/DC converter is started up. When IFSEL = 1, DUPF1 is

fixed to 0.

<DUPF0 = 0, DUPF1 = 0> f

OSC

/8

<DUPF0 = 1, DUPF1 = 0> f

OSC

/16

<DUPF0 = 0, DUPF1 = 1> f

OSC

/2

<DUPF0 = 1, DUPF1 = 1> f

OSC

/4

D

4

PON

0

Switching DC/DC

converter startup

operating frequency

This pin selects the V

DD1

, V

DD2

, V

SS2

to V

SS4

rising

operating frequency when the DC/DC converter is started

up. This setting is valid only when PONM = 1.

<PON = 0> Normal operation

<PON = 1> Power on operation startup operation

D

5

PONM

1

DC/DC operation startup

operating selection

Select internal/external sequence of DC/DC converter

power on operation.

<PONM = 0> External sequence

<PONM = 1> Internal sequence

R34

D

0

RES

-

Command reset

This is the command reset function. A command reset

must always be executed after power application. All

contents of registers are initialized.

This bit is automatically cleared after command reset

execution (RES = 1). It is therefore not necessary to set

this bit to 0 again by software (to select normal operation).

Also, because this bit changes from 1 to 0 very quickly

following a command reset, it is not necessary to leave any

time before setting the next command after setting a

command reset.

<RES = 0> Normal operation

<RES = 1> Command reset

Preliminary Product Information S15797EJ1V4PM

21

µ

µ

µ

µ

PD161644

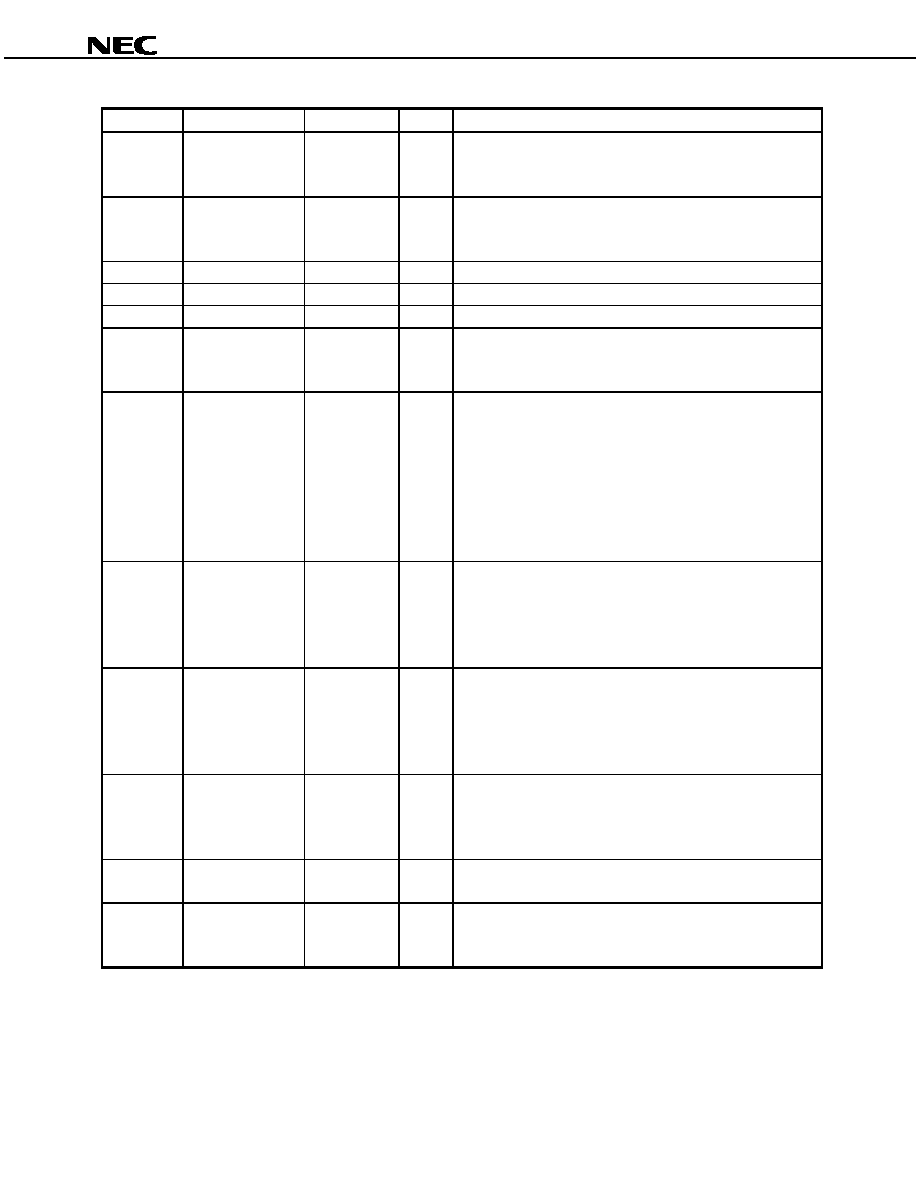

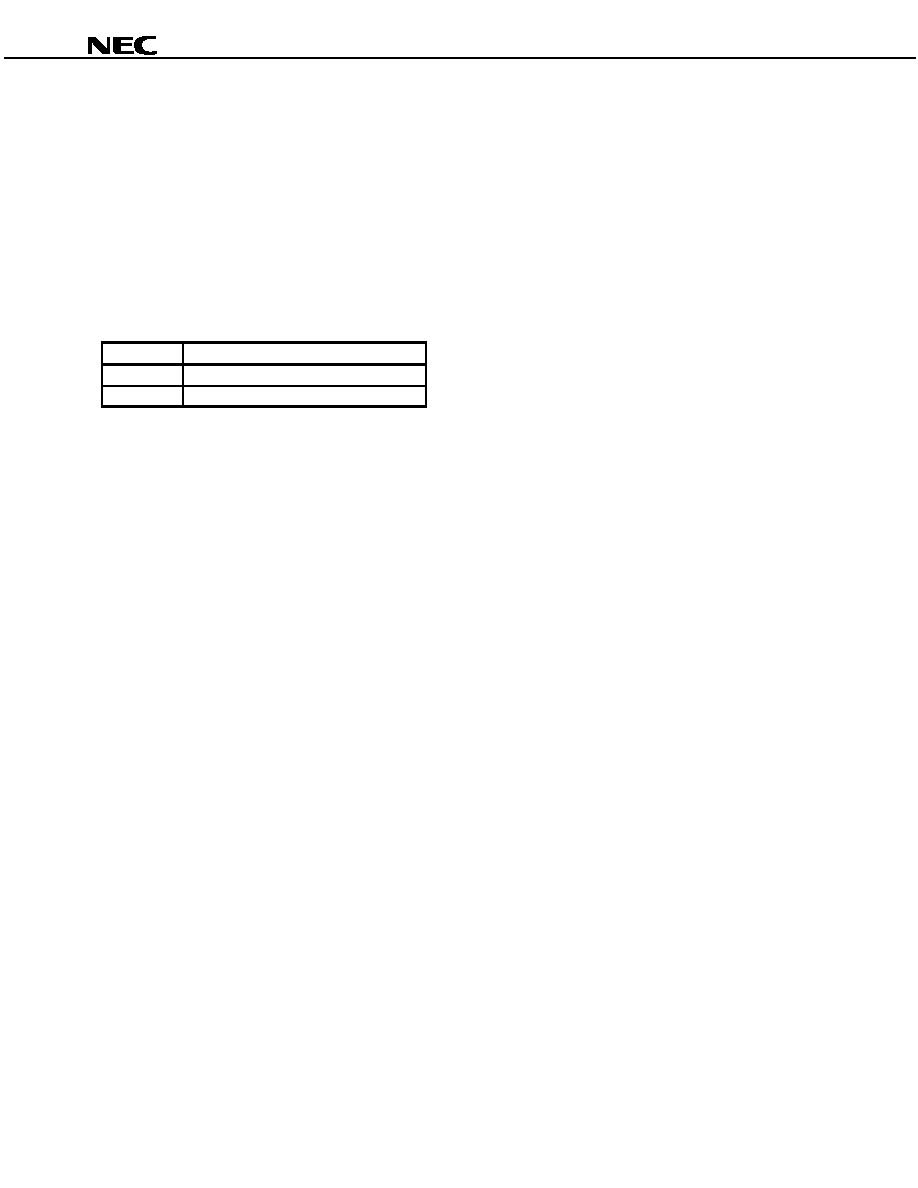

4.3

Command Setting Values When IFSEL = H (When Using Control Pins)

(1/2)

Register

Bit

Symbol

Setting value

Conditions

R24

D

0

DCON

-

DCON control pin is valid.

D

1

VD1ON

1

<VD1ON = 1> V

DD1

boost ON

D

2

VD2ON

1

<VD2ON = 1> V

DD2

boost ON

D

3

VS2ON

1

<VS2ON = 1> V

SS2

boost ON

D

4

VS3ON

1

<VS3ON = 1> V

SS3

boost ON

D

5

VS4ON

0

<VS4ON = 0> V

SS4

boost OFF

D

6

RGONR

-

RGONR control pin is valid.

R25

D

0

VCD2

-

VCD2 control pin is valid.

D

1

VMS

-

VMS control pin is valid.

D

2

VRSEL0

1

D

3

VRSEL1

0

D

4

VRSEL2

1

<VRSEL0 = 1, VRSEL1 = 0, VRSEL2 = 1 > V

R

= 5 V

R26

D

0

FS0

-

FS0 control pin is valid.

D

1

FS1

0

<FS0 = 0> f

OSC

/2, <FS0 = 1> f

OSC

/4

D

2

FS2

-

FS2 control pin is valid.

D

3

FS3

0

<FS2 = 0> f

OSC

/2, <FS2 = 1> f

OSC

/4

D

4

CLS0

-

CLS1 control pin is valid.

D

5

CLS1

1

<CLS0 = 0> f

OSC

= 37 kHz, <CLS0 = 1> External

D

6

FUP

0

<FUP = 0> f

OSC

R27

D

0

RGON

-

RGON control pin is valid.

D

1

VSEL0

-

VSEL control pin is valid.

D

2

VSEL1

-

<VSEL = 0> V

S

= 5 V

D

3

VSEL2

-

<VSEL = 1> V

S

= 4 V

D

4

EXRV

-

EXRV control pin is valid.

D

5

ACS0

-

ACS0 control pin is valid.

D

6

ACS1

0

<ACS0 = 0> Current = 5

µ

A, <ACS0 = 1> Current = 15

µ

A

R28

D

0

LPM

0

<LPM = 0> Scan mode

D

1

, D

2

LFS0, LFS1

0,1

<LFS0 = 0, LFS1 = 1> f

OSC

/32

D

3,

D

4

LFS2, LFS3

0,1

<LFS2 = 0, LFS3 = 1> f

OSC

/32

D

5,

D

6

LACS0, LACS1

0,1

<LACS0 = 0, LACS1 = 1> Amp. current = 2.5

µ

A

R29

D

0

SCN0

-

SCN0 control pin is valid

D

1

SCN1

-

SCN1 control pin is valid

D

2

SCN2

-

SCN2 control pin is valid

D

3

STVSEL

0

<STVSEL = 0> low-level is valid

D

4

OE1SEL

0

<OE1SEL = 0> OE

1

= low-level, gate output OFF

D

5

OE2SEL

0

<OE2SEL = 0> OE

2

= low-level, gate output ON

Remark When IFSEL = H (when using the control pins), the GCS, GCL, and GDA pins are pulled down to low level, so

be sure to leave these pins open.

When IFSEL = L (when using the serial interface), DCON, RGONR, VCD2, VMS, FS0, FS2, CLS0, RGON,

VSEL, EXRV, ACS0, SCN0, SCN1, SCN2, PUPT0, DUPF0 pins should be left open.

Preliminary Product Information S15797EJ1V4PM

22

µ

µ

µ

µ

PD161644

(2/2)

Register

Bit

Symbol

Setting value

Conditions

R30

D

0

NLINE1

1

<NLINE = 1, NLINE2 = 1>

normal mode

D

1

NLINE2

1

D

2

COMON

0

<COMON = 0> COM_AMP, COM output OFF

R31

D

0

to D

7

DA

0

to DA

7

0

<DA

0

to DA

7

> 0

R32

D

0

to D

7

CDA

0

to CDA

7

0

<CDA

0

to CDA

7

> 0

R33

D

0

PUPT0

-

D

1

PUPT1

0

PUPT0 control pin is valid

<PUPT0 = 0> RGONR = 2048/f

OSC

<PUPT0 = 1> RGONR = 256/f

OSC

D

2

DUPF0

-

D

3

DUPF1

0

DUPF0 control pin is valid

<DUPF0 = 0> f

OSC

/8

<DUPF0 = 1> f

OSC

/16

D

4

PON

1

<PON = 1> Internal sequence

D

5

PONM

1

<PONM = 1> Internal sequence

R34

D

0

RES

0

<RES = 0> Normal operation

Remark When IFSEL = H (when using the control pins), the GCS, GCL, and GDA pins are pulled down to low level, so

be sure to leave these pins open.

When IFSEL = L (when using the serial interface), DCON, RGONR, VCD2, VMS, FS0, FS2, CLS0, RGON,

VSEL, EXRV, ACS0, SCN0, SCN1, SCN2, PUPT0, DUPF0 pins should be left open.

Preliminary Product Information S15797EJ1V4PM

23

µ

µ

µ

µ

PD161644

5. MODE DESCRIPTION

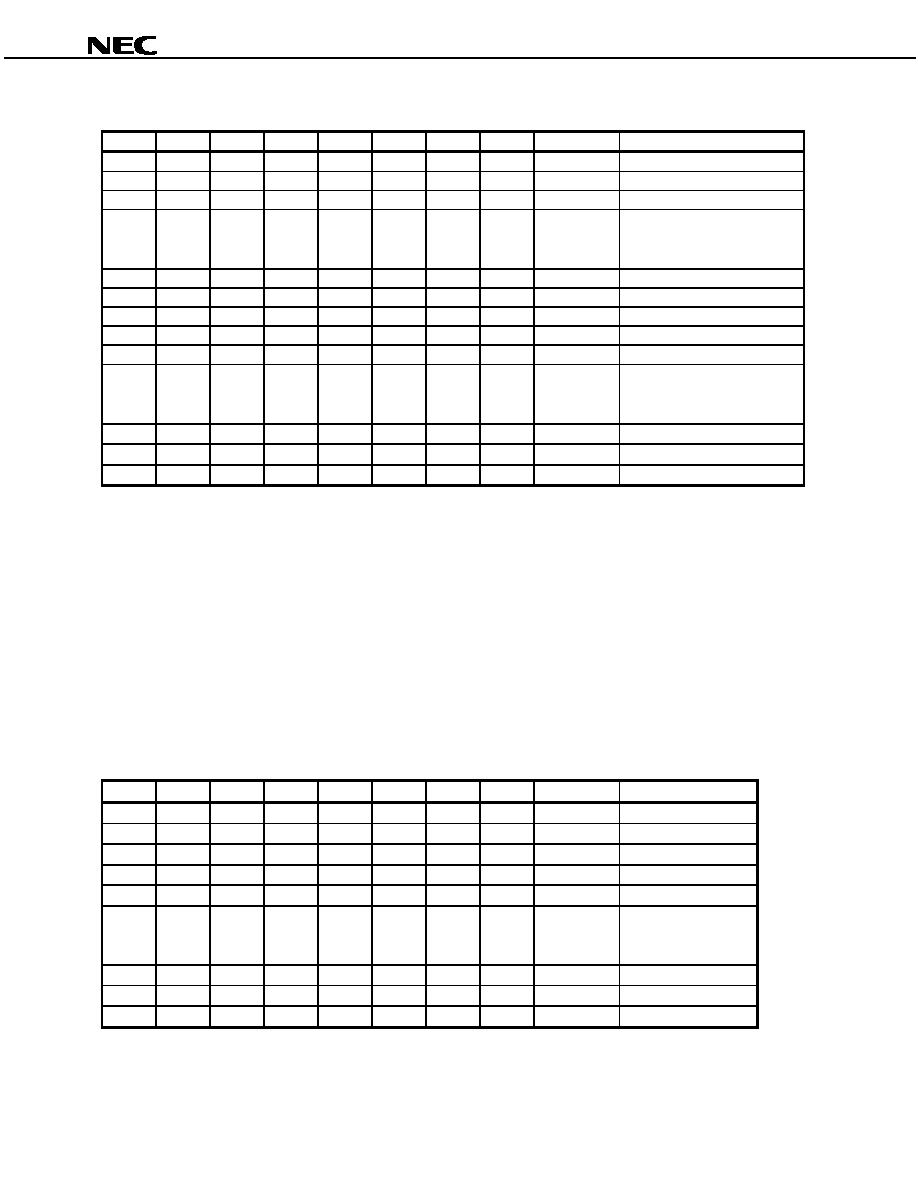

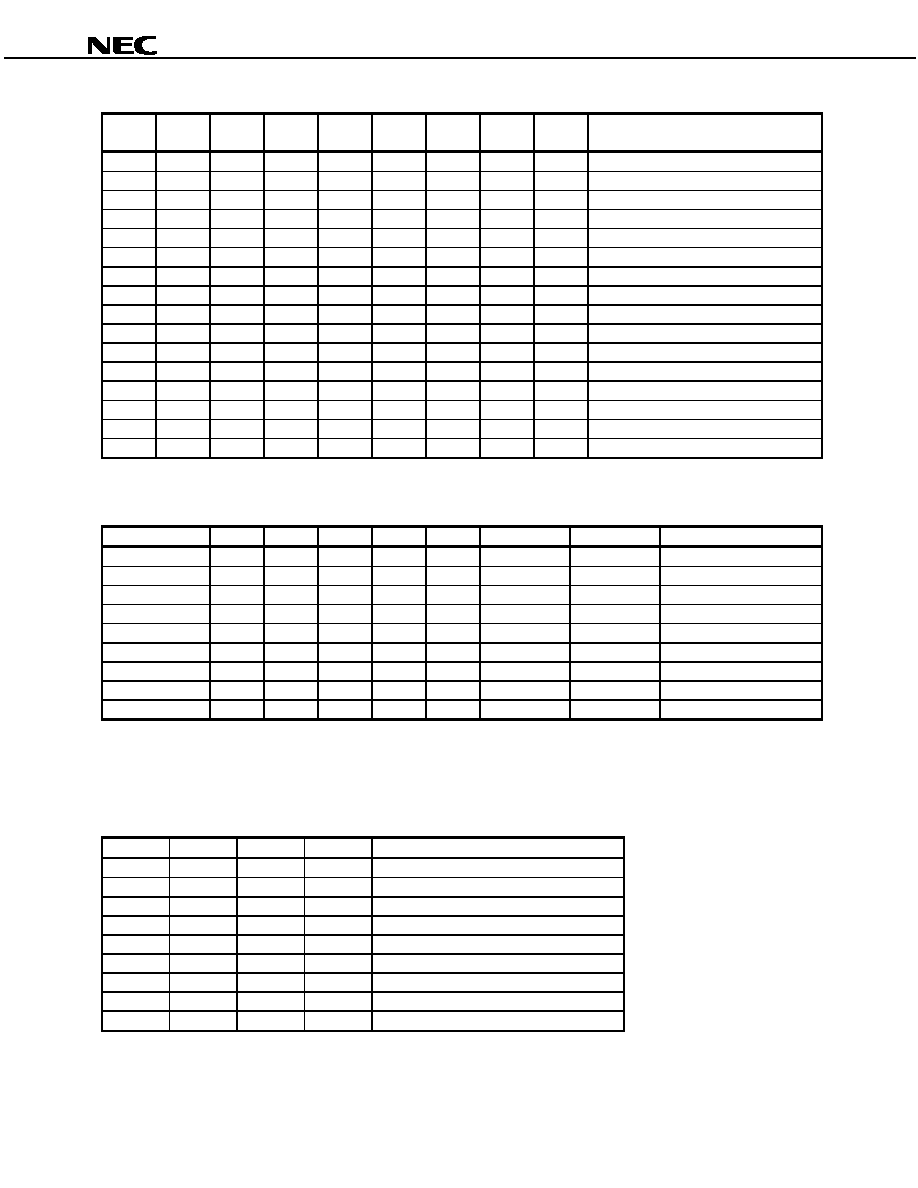

5.1 Output Mode and Gate Scan Selection

Normal mode: NLINE1 =1, NLINE2 = 1

Scan MODE

R,/L

Scan direction

Dummy output

Cascade output

H

1

240, 241

241

240

MODE1

L

241

2,1

1

2

H

1

121

∑

241

123, 122

122

123

MODE2

L

122

241

∑

121

2, 1

1

2

H

1

161

∑

241

163, 162

162

163

MODE3

L

162

241

∑

161

2, 1

1

2

H

1

201, 241

203, 202

202

203

MODE4

L

202

241

∑

201

2, 1

1

2

H

1, 241, 2, 240, 3, 239.....118, 124, 119, 123, 120, 122, 121

121

122

MODE5

L

121, 122, 120, 123, 119, 124.....4, 239, 3, 240, 2, 241, 1

1

241

1-line step mode: NLINE1 =1, NLINE2 = 0

Scan MODE

R,/L

Scan direction

Dummy output

Cascade output

H

1, 3, 5...235, 237, 239, 241

∑

2, 4, 6...236, 238, 240

241

240

MODE1

L

241, 239, 237...7, 5, 3, 1

∑

240, 238, 236...6, 4, 2

1

2

H

1, 3, 5...117, 119, 121

∑

240, 238, 236...128, 126, 124, 122,

∑

2, 4, 6...116, 118, 120

∑

241, 239, 237...127, 125, 123

122

123

MODE2

L

122, 124, 126...236, 238, 240

∑

121, 119, 117...7, 5, 3, 1,

∑

123, 125, 127...237, 239, 241

∑

120, 118, 116...6, 4, 2

1

2

H

1, 3, 5...157, 159, 161

∑

240, 238, 236...168, 166, 164, 162

∑

2, 4, 6...156, 158, 160

∑

241, 239, 237...167, 165, 163

162

163

MODE3

L

162, 164, 166...236, 238, 240

∑

161, 159, 157...7, 5, 3, 1,

∑

163, 165, 167...237, 239, 241

∑

160, 158, 156...6, 4, 2

1

2

H

1, 3, 5...197, 199, 201

∑

240, 238, 236...208, 206, 204, 202,

∑

2, 4, 6...196, 198, 200

∑

241, 239, 237...207, 205, 203

202

203

MODE4

L

202, 204, 206...236, 238, 240

∑

201, 199, 197...7, 5, 3, 1,

∑

203, 205, 207...237, 239, 241

∑

200, 198, 196...6, 4, 2

1

2

Preliminary Product Information S15797EJ1V4PM

24

µ

µ

µ

µ

PD161644

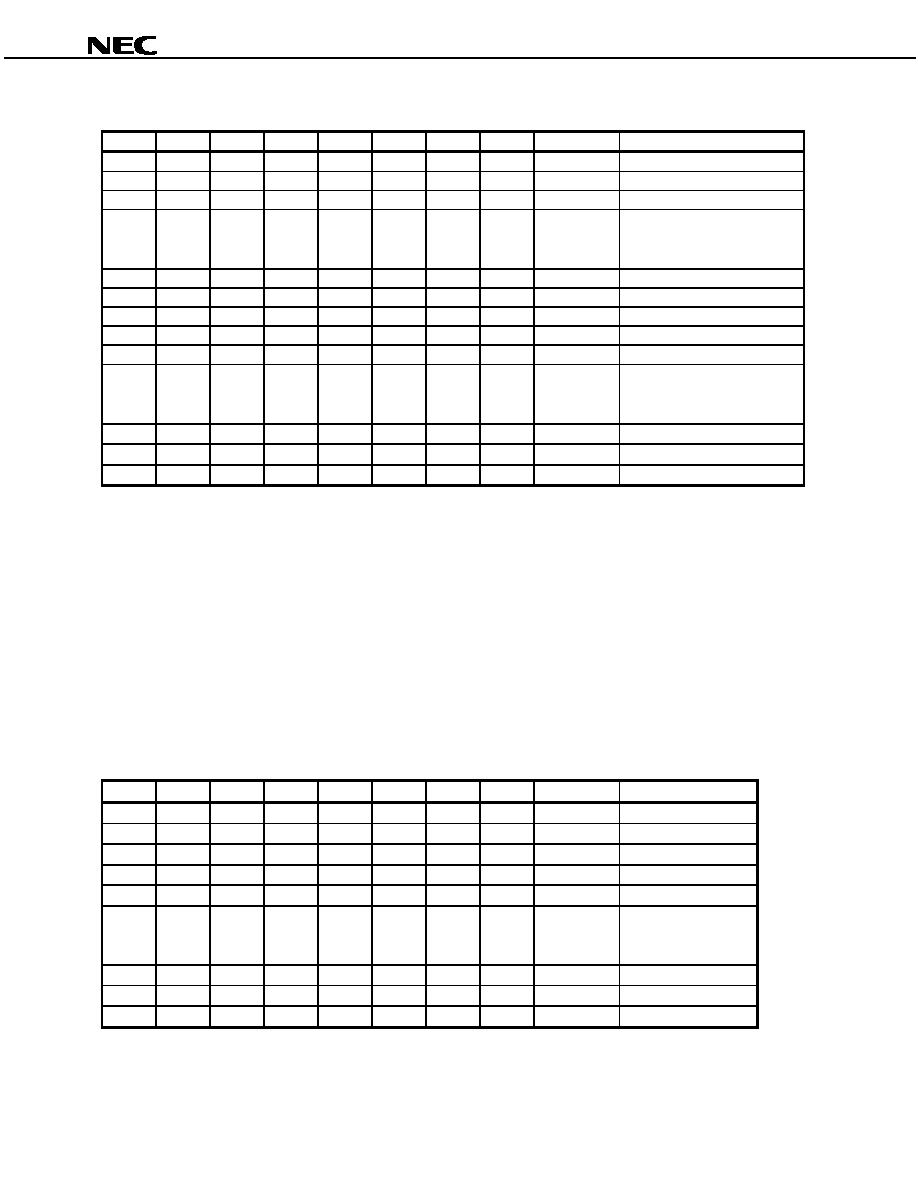

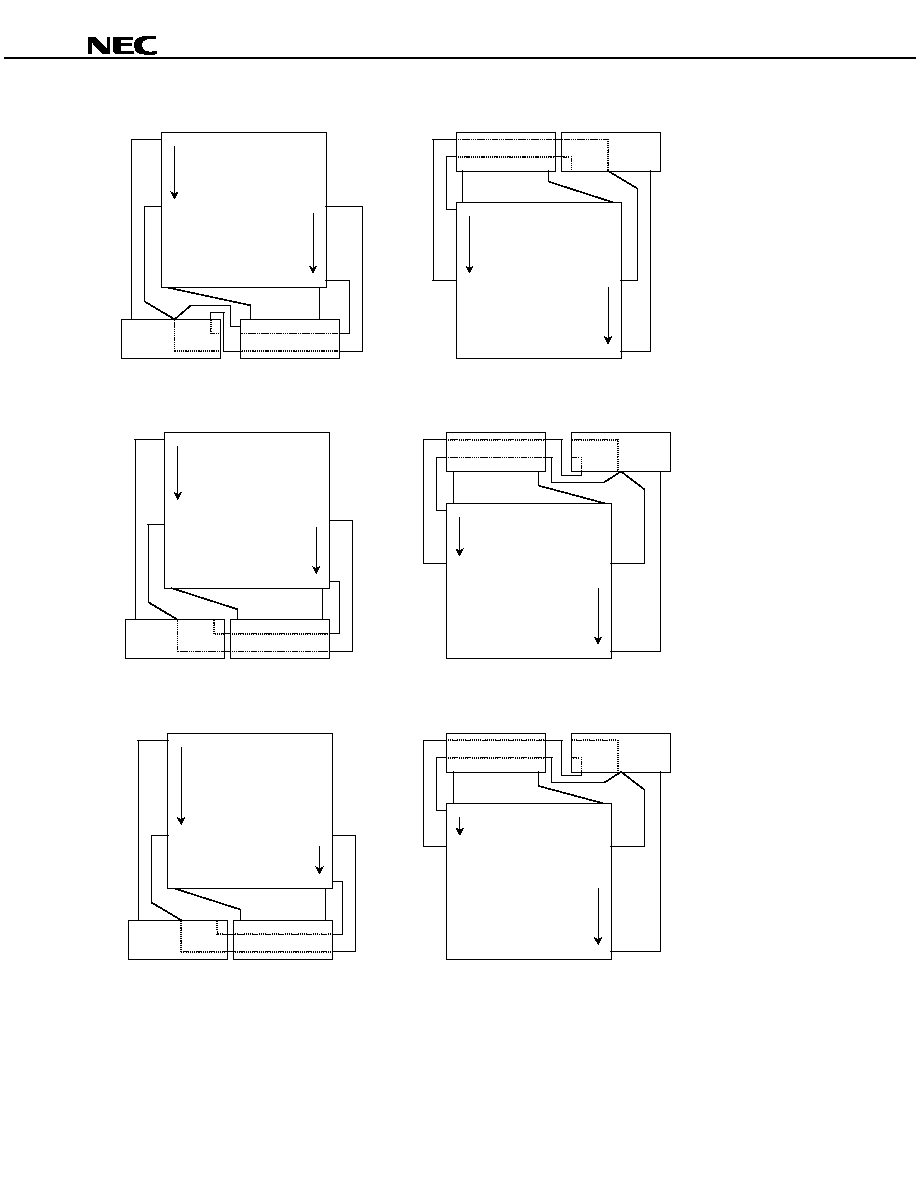

2-line step mode: NLINE1 = 0, NLINE2 = 1

Scan MODE

R,/L

Scan direction

Dummy output

Cascade output

H

1, 4, 7...232, 235, 238, 241

∑

2, 5, 8...233, 236, 239

∑

3, 6, 9...234, 237, 240

241

240

MODE1

L

241, 238, 235...10, 7, 4, 1

∑

240, 237, 234...9, 6, 3

∑

239, 236, 233...8, 5, 2

1

2

H

1, 4, 7...115, 118, 121

∑

239, 236, 233...131, 128, 125, 122,

∑

2, 5, 8...113, 116, 119

∑

241, 238, 235...130, 127, 124

∑

3, 6, 9...114, 117, 120

∑

240, 237, 234,...129, 126, 123

122

123

MODE2

L

122, 125, 128...233, 236, 239

∑

121, 118, 115...10, 7, 4, 1,

∑

123, 126, 129...234, 237, 240

∑

120, 117, 114...9, 6, 3

∑

124, 127, 130...235, 238, 241

∑

119, 116, 113...8, 5, 2

1

2

H

1, 4, 7...154, 157, 160

∑

240, 237, 234...171, 168, 165, 162,

∑

2, 5, 8...155, 158, 161

∑

239, 236, 233...170, 167, 164

∑

3, 6, 9...153, 156, 159

∑

241, 238, 235...169, 166, 163

162

163

MODE3

L

162, 165, 168...234, 237, 240

∑

160, 157, 154...10, 7, 4, 1,

∑

163, 166, 169...235, 238, 241

∑

159, 156, 153...9, 6, 3

∑

164, 167, 170...233, 236, 239

∑

161, 158, 155..8, 5, 2

1

2

H

1, 4, 7...193, 196, 199

∑

241, 238, 235...211, 208, 205, 202,

∑

2, 5, 8...194, 197, 200

∑

240, 237, 234...210, 207, 204

∑

3, 6, 9...195, 198, 201

∑

239, 236, 233...209, 206, 203

202

203

MODE4

L

202, 205, 208...235, 238, 241

∑

199, 196, 193...10, 7, 4, 1,

∑

203, 206, 209...2337, 236, 239

∑

201, 198, 195...9, 6, 3

∑

204, 207, 210...234, 240, 200

∑

197, 194...8, 5, 2

1

2