| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LF11201 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

LF11331/LF13331/LF11332/LF13332/LF11333/

LF13333/LF11201/LF13201/LF11202/LF13202

Quad SPST JFET Analog Switches

General Description

These devices are a monolithic combination of bipolar and

JFET technology producing the industry's first one chip quad

JFET switch. A unique circuit technique is employed to main-

tain a constant resistance over the analog voltage range of

±

10V. The input is designed to operate from minimum TTL

levels,

and

switch

operation

also

ensures

a

break-before-make action.

These devices operate from

±

15V supplies and swing a

±

10V analog signal. The JFET switches are designed for ap-

plications where a dc to medium frequency analog signal

needs to be controlled.

Features

n

Analog signals are not loaded

n

Constant "ON" resistance for signals up to

±

10V and

100 kHz

n

Pin compatible with CMOS switches with the advantage

of blow out free handling

n

Small signal analog signals to 50 MHz

n

Break-before-make action:

t

OFF

<

t

ON

n

High open switch isolation at 1.0 MHz:

-50 dB

n

Low leakage in "OFF" state:

<

1.0 nA

n

TTL, DTL, RTL compatibility

n

Single disable pin opens all switches in package on

LF11331, LF11332, LF11333

n

LF11201 is pin compatible with DG201

Test Circuit and Schematic Diagram

DS005667-2

FIGURE 1. Typical Circuit for One Switch

DS005667-12

FIGURE 2. Schematic Diagram (Normally Open)

January 1995

LF1

1331/LF13331/LF1

1332/LF13332/LF1

1333/LF13333/LF1

1201/LF13201/LF1

1202/LF13202

Quad

SPST

JFET

Analog

Switches

© 1999 National Semiconductor Corporation

DS005667

www.national.com

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

(Note 2)

Supply Voltage (V

CC

-V

EE

)

36V

Reference Voltage

V

EE

V

R

V

CC

Logic Input Voltage

V

R

-4.0V

V

IN

V

R

+6.0V

Analog Voltage

V

EE

V

A

V

CC

+6V;

V

A

V

EE

+36V

Analog Current

|I

A

|

<

20 mA

Power Dissipation (Note 3)

Molded DIP (N Suffix)

500 mW

Cavity DIP (D Suffix)

900 mW

Operating Temperature Range

LF11201, 2 and LF11331, 2, 3

-55∞C to +125∞C

LF13201, 2 and LF13331, 2, 3

0∞C to +70∞C

Storage Temperature

-65∞C to +150∞C

Soldering Information

N and D Package (10 sec.)

300∞C

SO Package:

Vapor Phase (60 sec.)

215∞C

Infrared (15 sec.)

220∞C

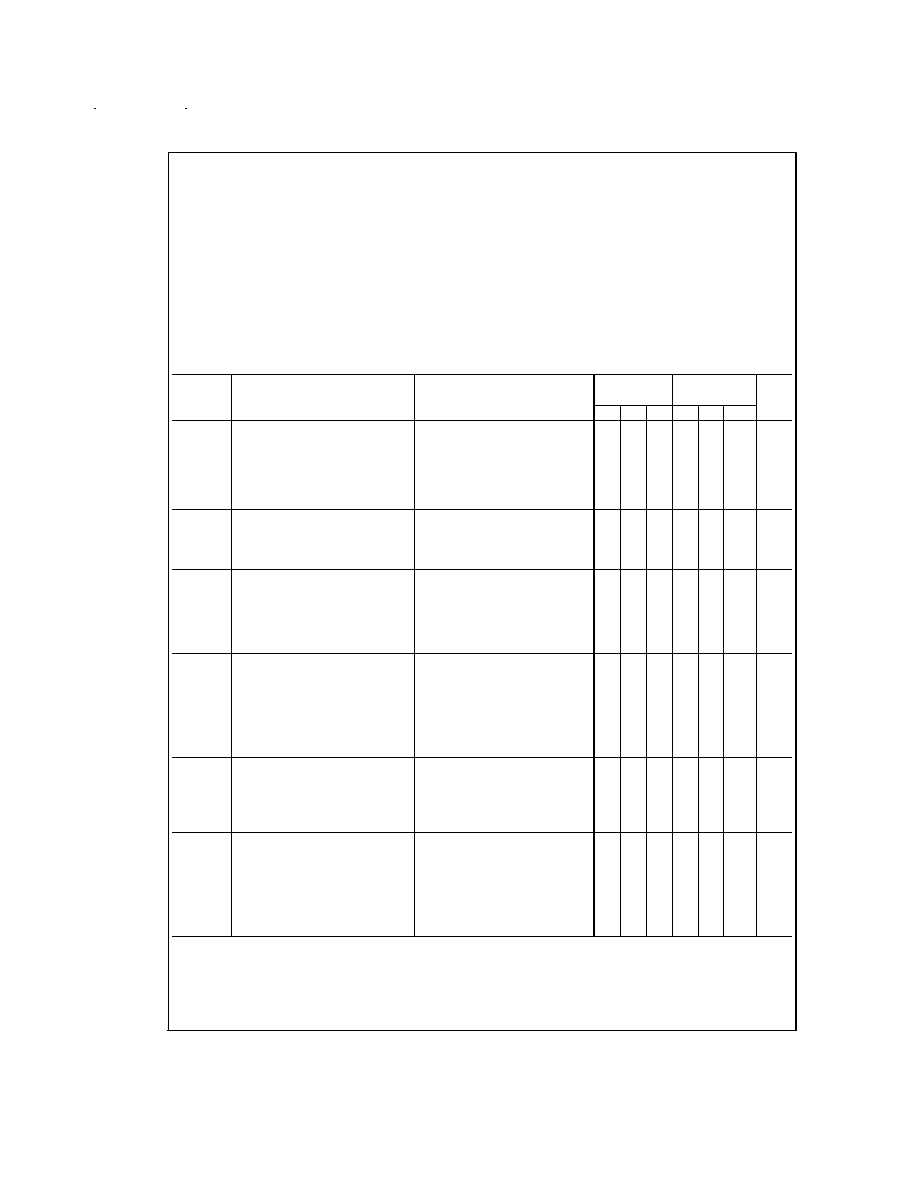

Electrical Characteristics

(Note 4)

LF11331/2/3

LF13331/2/3

Symbol

Parameter

Conditions

LF11201/2

LF13201/2

Units

Min

Typ

Max

Min

Typ

Max

R

ON

"ON" Resistance

V

A

=0, I

D

=1 mA

T

A

=25∞C

150

200

150

250

200

300

200

350

R

ON

Match

"ON" Resistance Matching

T

A

=25∞C

5

20

10

50

V

A

Analog Range

±

10

±

11

±

10

±

11

V

I

S(ON) +

Leakage Current in "ON" Condition

Switch "ON," V

S

=V

D

=

±

10V

T

A

=25∞C

0.3

5

0.3

10

nA

I

D(ON)

3

100

3

30

nA

I

S(OFF)

Source Current in "OFF" Condition

Switch "OFF," V

S

=+10V,

T

A

=25∞C

0.4

5

0.4

10

nA

V

D

=-10V

3

100

3

30

nA

I

D(OFF)

Drain Current in "OFF" Condition

Switch "OFF," V

S

=+10V,

T

A

=25∞C

0.1

5

0.1

10

nA

V

D

=-10V

3

100

3

30

nA

V

INH

Logical "1" Input Voltage

2.0

2.0

V

V

INL

Logical "0" Input Voltage

0.8

0.8

V

I

INH

Logical "1" Input Current

V

IN

=5V

T

A

=25∞C

3.6

10

25

3.6

40

100

µA

I

INL

Logical "0" Input Current

V

IN

=0.8

T

A

=25∞C

0.1

0.1

µA

1

1

µA

t

ON

Delay Time "ON"

V

S

=

±

10V, (

Figure 3

)

T

A

=25∞C

500

500

ns

t

OFF

Delay Time "OFF"

V

S

=

±

10V, (

Figure 3

)

T

A

=25∞C

90

90

ns

t

ON

-t

OFF

Break-Before-Make

V

S

=

±

10V, (

Figure 3

)

T

A

=25∞C

80

80

ns

C

S(OFF)

Source Capacitance

Switch "OFF," V

S

=

±

10V

T

A

=25∞C

4.0

4.0

pF

C

D(OFF)

Drain Capacitance

Switch "OFF," V

D

=

±

10V

T

A

=25∞C

3.0

3.0

pF

C

S(ON) +

Active Source and Drain Capacitance

Switch "ON," V

S

=V

D

=0V

T

A

=25∞C

5.0

5.0

pF

C

D(ON)

I

SO(OFF)

"OFF" Isolation

(

Figure 4

), (Note 5)

T

A

=25∞C

-50

-50

dB

CT

Crosstalk

(

Figure 4

), (Note 5)

T

A

=25∞C

-65

-65

dB

SR

Analog Slew Rate

(Note 6)

T

A

=25∞C

50

50

V/µs

I

DIS

Disable Current

(

Figure 5

), (Note 7)

T

A

=25∞C

0.4

1.0

0.6

1.5

mA

0.6

1.5

0.9

2.3

mA

I

EE

Negative Supply Current

All Switches "OFF," V

S

=

±

10V

T

A

=25∞C

3.0

5.0

4.3

7.0

mA

4.2

7.5

6.0

10.5

mA

I

R

Reference Supply Current

All Switches "OFF," V

S

=

±

10V

T

A

=25∞C

2.0

4.0

2.7

5.0

mA

2.8

6.0

3.8

7.5

mA

I

CC

Positive Supply Current

All Switches "OFF," V

S

=

±

10V

T

A

=25∞C

4.5

6.0

7.0

9.0

mA

6.3

9.0

9.8

13.5

mA

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits.

Note 2: Refer to RETSF11201X, RETSF11331X, RETSF11332X and RETSF11333X for military specifications.

Note 3: For operating at high temperature the molded DIP products must be derated based on a +100∞C maximum junction temperature and a thermal resistance

of +150∞C/W, devices in the cavity DIP are based on a +150∞C maximum junction temperature and are derated at

±

100∞C/W.

www.national.com

2

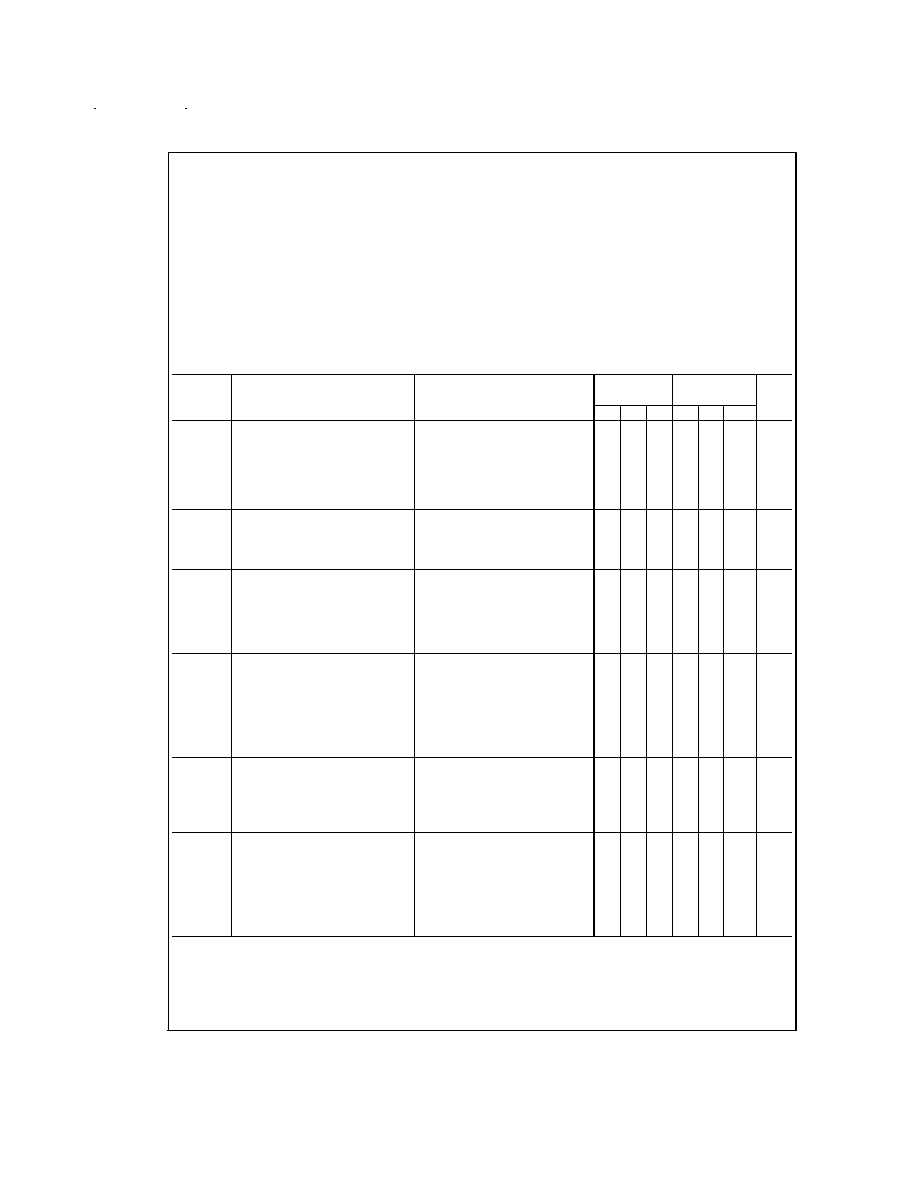

Electrical Characteristics

(Note 4) (Continued)

Note 4: Unless otherwise specified, V

CC

=+15V, V

EE

=-15V, V

R

=0V, and limits apply for -55∞C

T

A

+125∞C for the LF11331/2/3 and the LF11201/2,

-25∞C

T

A

+85∞C for the LF13331/2/3 and the LF13201/2.

Note 5: These parameters are limited by the pin to pin capacitance of the package.

Note 6: This is the analog signal slew rate above which the signal is distorted as a result of finite internal slew rates.

Note 7: All switches in the device are turned "OFF" by saturating a transistor at the disable node as shown in

Figure 5. The delay time will be approximately equal

to the t

ON

or t

OFF

plus the delay introduced by the external transistor.

Note 8: This graph indicates the analog current at which 1% of the analog current is lost when the drain is positive with respect to the source.

Note 9:

JA

(Typical) Thermal Resistance

Molded DIP (N)

85∞C/W

Cavity DIP (D)

100∞C/W

Small Outline (M)

105∞C/W

Connection Diagrams

(Top View for SO and Dual-In-Line Packages) (All Switches Shown are For Logical "0")

LF11331/LF13331

DS005667-1

LF11332/LF13332

DS005667-13

LF11333/LF13333

DS005667-14

LF11201/LF13201

DS005667-15

www.national.com

3

Connection Diagrams

(Top View for SO and Dual-In-Line Packages) (All Switches Shown are For Logical

"0") (Continued)

LF11202/LF13202

DS005667-16

Order Number LF13201D, LF11201D, LF11201D/883, LF13202D, LF11202D, LF11202D/883, LF13331D, LF11331D,

LF11331D/883, LF13332D, LF11332D, LF11332D/883, LF13333D, LF11333D or LH11333D/883

See NS Package Number D16C

Order Number LF13201M, LF13202M, LF13331M, LF13332M or LF13333M

See NS Package Number M16A

Order Number LF13201N, LF13202N, LF13331N, LF13332N or LF13333N

See NS Package Number N16A

www.national.com

4

Test Circuit and Typical Performance Curves

Delay Time, Rise Time, Settling Time, and

Switching Transients

DS005667-17

DS005667-18

DS005667-19

DS005667-20

DS005667-21

DS005667-22

www.national.com

5