1/18

° Semiconductor

MSM82C84A-2RS/GS/JS

GENERAL DESCRIPTION

The MSM82C84A-2RS/GS is a clock generator designed to generate MSM80C86A-10 and

MSM80C88A-10 system clocks of 8MHz.

Due to the use of silicon gate CMOS technology, standby current is only 40 mA (MAX.), and the

power consumption is very low with 16 mA (MAX.) when a 8 MHz clock is generated.

FEATURES

∑ Operating frequency of 6 to 24 MHz (CLK output 2 to 8 MHz)

∑ 3 m silicon gate CMOS technology for low power consumption

∑ Built-in crystal oscillator circuit

∑ 3 V to 6 V single power supply

∑ Built-in synchronized circuit for MSM80C86A-10 and MSM80C88A-10 READY and RESET

∑ TTL compatible

∑ Built-in Schmitt trigger circuit (RES input)

∑ 18-pin Plastic DIP (DIP18-P-300-2.54): (Product name: MSM82C84A-2RS)

∑ 20-pin Plastic QFJ (QFJ20-P-S350-1.27): (Product name: MSM82C84A-2JS)

∑ 24-pin Plastic SOP (SOP24-P-430-1.27-K): (Product name: MSM82C84A-2GS-K)

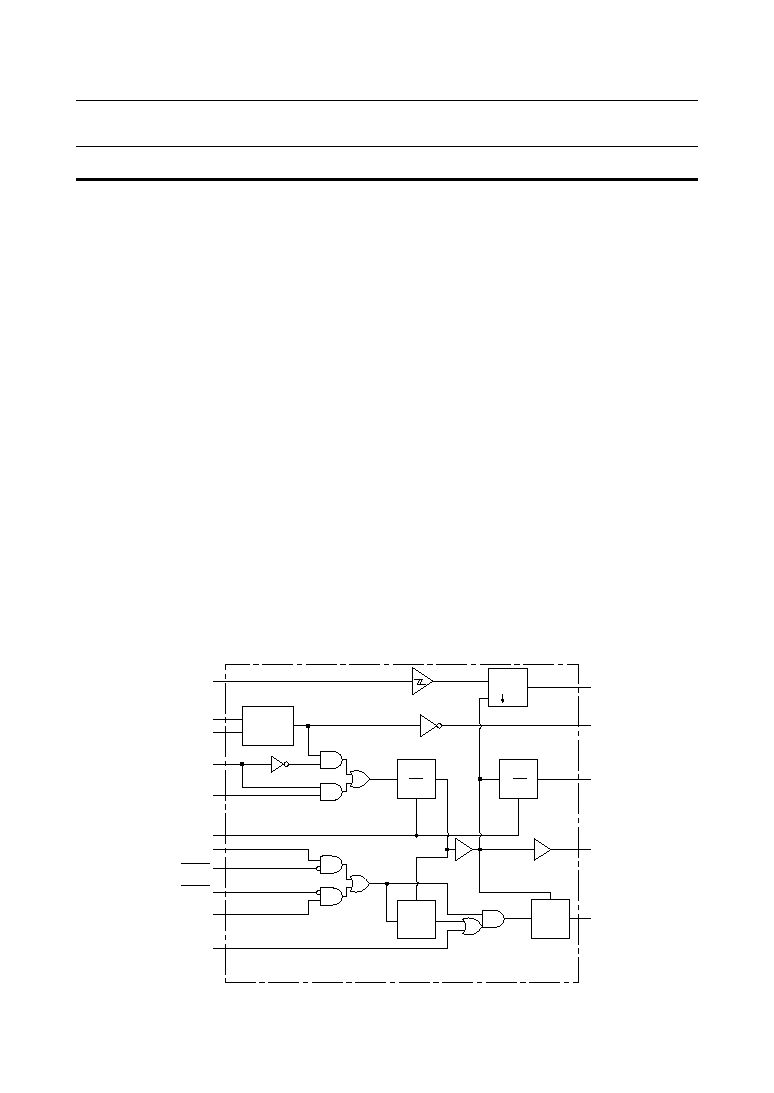

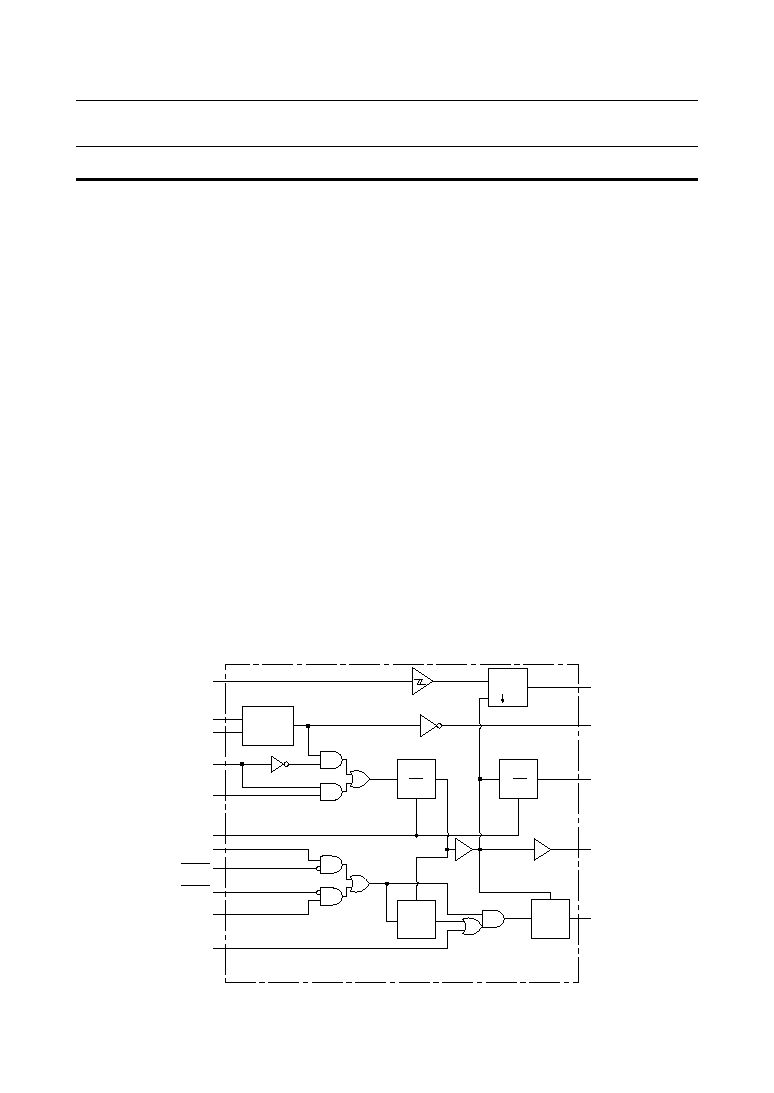

FUNCTIONAL BLOCK DIAGRAM

° Semiconductor

MSM82C84A-2RS/GS/JS

CLOCK GENERATOR AND DRIVER

RESET

OSC

PCLK

CLK

READY

D

C

Q

1

2

1

3

S

Y

N

C

S

Y

N

C

D

C

ÿ

Q

(F2)

D

C

Q

(F1)

RES

x

1

x

2

F/C

EFI

CSYNC

RDY

1

AEN

1

AEN

2

ASYNC

RDY

2

Crystal

Oscillator

E2O0012-27-X2

This version: Jan. 1998

Previous version: Aug. 1996

2/18

° Semiconductor

MSM82C84A-2RS/GS/JS

PIN CONFIGURATION (TOP VIEW)

18 pin Plastic DIP

24 pin Plastic SOP

20 pin Plastic QFJ

18

17

16

15

14

RDY

2

AEN

2

RDY

1

READY

NC

9

10

11

12

13

CLK

GND

RESET

RES

OSC

3

2

1

20

19

AEN

1

PCLK

CSYNC

X

1

4

5

6

7

8

V

CC

ASYNC

EFI

F/C

NC

X

2

X

2

NC

ASYNC

EFI

NC

F/C

OSC

NC

X

1

RES

RESET

NC

AEN

1

RDY

1

READY

NC

RDY2

AEN

2

NC

CSYNC

PCLK

CLK

GND

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Vcc

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

ASYNC

EFI

F/C

OSC

X

2

X

1

RES

RESET

AEN

1

RDY

1

READY

RDY

2

AEN

2

CSYNC

PCLK

CLK

GND

V

CC

(NC not connected)

3/18

° Semiconductor

MSM82C84A-2RS/GS/JS

ABSOLUTE MAXIMUM RATINGS

≠55 to +150

MSM82C84A-2RS/JS

Supply Voltage

V

CC

≠0.5 to +7

V

Input Voltage

V

IN

≠0.5 to V

CC

+0.5

V

Output Voltage

V

OUT

≠0.5 to V

CC

+0.5

V

Storage Temperature

T

STG

∞C

Power Dissipation

P

D

W

Parameter

Unit

Symbol

Respect

to GND

--

Ta = 25∞C

Condition

Rating

MSM82C84A-2GS

0.7

0.8

OPERATING RANGES

Range

Supply Voltage

V

CC

3 to 6

V

Operating Temperature

T

op

≠40 to +85

∞C

Parameter

Unit

Symbol

RECOMMENDED OPERATING CONDITIONS

DC CHARACTERISTICS

Max.

"L" Level Output Voltage (CLK)

V

OL

0.4

V

"H" Output Voltage (CLK)

V

OL

0.4

V

Parameter

Unit

Symbol

Min.

--

--

V

CC

≠0.4

I

OL

= 4 mA

I

OL

= 2.5 mA

I

OH

= ≠4 mA

Condition

"H" Output Voltage (Others)

V

OH

--

V

V

CC

≠0.4

I

OH

= ≠1 mA

RES Input Hysteresis

V

IHR

-V

ILR

--

V

0.2*V

CC

Input Leak Current

(Except ASYNC)

I

LI

+1

mA

≠1

0 £ V

IN

£ V

CC

Input Current (ASYNC)

I

LIA

+10

mA

≠100

0 £ V

IN

£ V

CC

Standby Supply Current

I

CCS

40

mA

--

Note 1

Input Capacitance

C

IN

7

pF

f =1 MHz

--

"L" Level Output Voltage (Others)

Operating Supply Current

--

V

OH

--

V

I

CC

16

mA

f = 24 MHz, C

L

= O

P

F

(V

CC

= 5 V ± 10%, Ta = ≠40 to 85∞C)

Note:

1. X1

V

CC

≠ 0.2 V, X2 £ 0.2 V

F/C

V

CC

≠ 0.2 V, ASYNC = V

CC

or open

VIH

V

CC

≠ 0.2 V, VIL £ 0.2 V

Typ.

Supply Voltage

V

CC

5

V

T

op

+25

"L" Level Input Voltage

V

IL

V

IH

--

"H" Level Input Voltage (except RES)

--

Min.

4.5

≠40

≠0.5

2.2

Max.

5.5

+85

+0.8

V

CC

+0.5

Parameter

Unit

Symbol

∞C

V

V

0.6*V

CC

Operating Temperature

"H" Level Input Voltage (RES)

4/18

° Semiconductor

MSM82C84A-2RS/GS/JS

AC CHARACTERISTICS

(1)

Parameter

Symbol

Min.

Max.

Unit

EFI "H" Pulse Width

EFI "L" Pulse Width

Crystal Oscillator Frequency

Set up Time of RDY

1

or RDY

2

to

CLK Falling Edge (Active)

EFI Cycle Time

Conditions

Set up Time of RDY

1

or RDY

2

to

CLK Rising Edge (Active)

Set up Time of RDY

1

or RDY

2

to

CLK Falling Edge (Inactive)

Hold Time of RDY

1

or RDY

2

to

CLK Falling Edge

Set up Time of ASYNC to CLK

Falling Edge

Hold Time of ASYNC to

CLK Falling Edge

Set up Time of AEN

1

(AEN

2

) to

RDY

1

(RDY

2

) Rising Edge

Hold Time of AEN

1

(AEN

2

) to

CLK Falling Edge

Set up Time of CSYNC to EFI

Rising Edge

Hold Time of CSYNC to EFI

Rising Edge

CSYNC Pulse Width

Set up Time of RES to CLK Falling

Edge

Hold Time of RES to CLK Falling

Edge

Input Rising Edge Time

Input Falling Edge Time

t

EHEL

t

ELEH

t

ELEL

t

R1VCL

t

R1VCH

t

R1VCL

t

CLR1X

t

AYVCL

t

CLAYX

t

A1R1V

t

CLA1X

t

YHEH

t

YHYL

t

I1HCL

t

CLI1H

t

ILIH

t

IHIL

t

EHYL

--

13

17

36

6

35

35

35

0

50

0

15

0

20

10

2 •

t

ELEL

65

20

--

--

24

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

15

15

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

ns

ns

ns

ns

ns

90% to 90%

10% to 10%

--

--

ASYNC

= High

ASYNC

= Low

--

--

--

--

--

--

--

--

--

--

--

--

--

Output Load

Capacitance

CLK output

C

L

= 100 pF

Others 30 pF

(V

CC

= 5 V ± 10%, Ta = ≠40 to 85∞C)

Note: Parameters where timing has not been indicated in the above table are measured at

V

L

= 1.5 V and V

H

= 1.5 V for both inputs and outputs.

5/18

° Semiconductor

MSM82C84A-2RS/GS/JS

AC CHARACTERISTICS

(2)

Parameter

Symbol

Min.

Max.

Unit

CLK Cycle Time

CLK "H" Pulse Width

CLK Rising and Falling Edge

Times

CLK "L" Pulse Width

Conditions

PCLK "H" Pulse Width

Time from READY Falling Edge

to CLK Falling Edge

Time from READY Rising Edge

to CLK Rising Edge

Delay from CLK Falling Edge

to RESET Falling Edge

Delay from CLK Falling Edge

to PCLK Rising Edge

Delay from CLK Falling Edge

to PCLK Falling Edge

Delay from OSC Falling Edge

to CLK Falling Edge

Output Rising Edge Time

(Except CLK)

Output Falling Edge Time

(Except CLK)

t

CLCL

t

CHCL

t

CLCH

t

CH1CH2

t

PHPL

t

RYLCL

t

RYHCH

t

CLIL

t

CLPH

t

CLPL

t

OLCL

t

OLOH

t

OHOL

125

--

T

CLCL

≠20

-8

--

--

--

2

--

--

10

--

--

--

40

22

22

35

--

--

--

15

15

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

--

Output Load

Capacitance

CLK Output

C

L

= 100 pF

Others 30 pF

(V

CC

= 5 V ± 10%, Ta = -40 to 85∞C)

PCLK "L" Pulse Width

t

CL2CL1

t

PLPH

Delay from OSC Falling Edge

to CLK Rising Edge

t

OLCH

1

3

T

CLCL

+ 2

2

3

T

CLCL

≠15

T

CLCL

≠20

2

3

T

CLCL

≠15

≠5

--

22

ns

--

--

1.0 V to 3.5 V

--

--

--

--

--

--

--

--

--

0.8 V to 2.2 V

2.2 V to 0.8 V

Note: Parameters where timing has not been indicated in the above table are measured at

V

L

= 1.5 V and V

H

= 1.5 V for both inputs and outputs.