1999 Sep 23

2

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset;

positive-edge trigger

74AHC74; 74AHCT74

FEATURES

∑

ESD protection:

HBM EIA/JESD22-A114-A

exceeds 2000 V

MM EIA/JESD22-A115-A

exceeds 200 V

∑

Balanced propagation delays

∑

Inputs accepts voltages higher than

V

CC

∑

For AHC only:

operates with CMOS input levels

∑

For AHCT only:

operates with TTL input levels

∑

Output capability: standard

∑

I

CC

category: flip-flops

∑

Specified from

-

40 to +85 and +125

∞

C.

DESCRIPTION

The 74AHC/AHCT74 are high-speed

Si-gate CMOS devices and are pin

compatible with low power Schottky

TTL (LSTTL). They are specified in

compliance with JEDEC standard

No. 7A.

The 74AHC/AHCT74 dual

positive-edge triggered, D-type

flip-flops with individual data (D)

inputs, clock (CP) inputs, set (S

D

) and

reset (R

D

) inputs; also

complementary Q and Q outputs.

The set and reset are asynchronous

active LOW inputs and operate

independently of the clock input.

Information on the data input is

transferred to the Q output on the

LOW-to-HIGH transition of the clock

pulse. The D inputs must be stable

one set-up time prior to the

LOW-to-HIGH clock transition for

predictable operation.

Schmitt-trigger action in the clock

input makes the circuit highly tolerant

to slower clock rise and fall times.

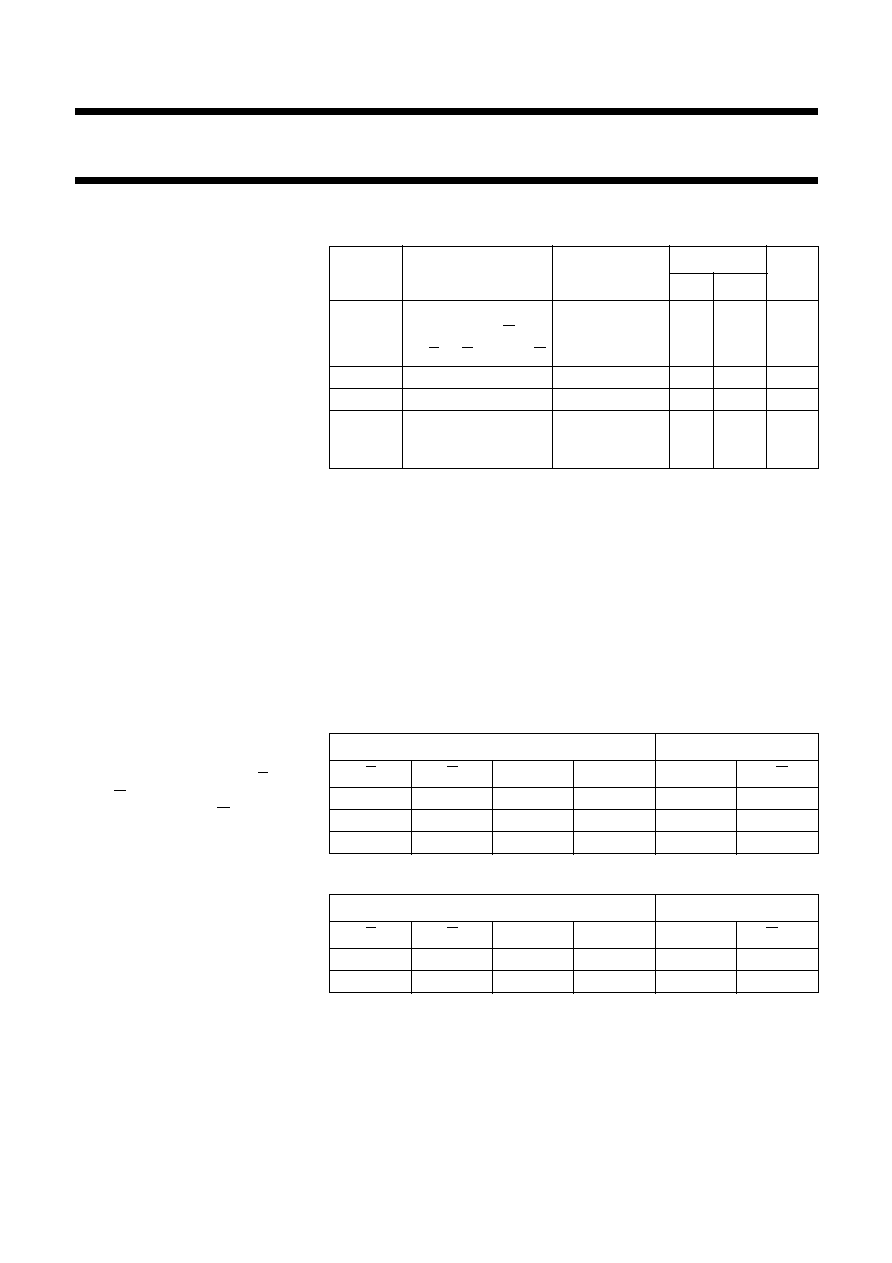

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

∞

C; t

r

= t

f

3.0 ns.

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

µ

W).

P

D

= C

PD

◊

V

CC

2

◊

f

i

+

(C

L

◊

V

CC

2

◊

f

o

) where:

f

i

= input frequency in MHz; f

o

= output frequency in MHz;

(C

L

◊

V

CC

2

◊

f

o

) = sum of outputs;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in Volts.

2. The condition is V

I

= GND to V

CC

.

FUNCTION TABLES

Table 1

See note 1

Table 2

See note 1

Note to Tables 1 and 2

1. H = HIGH voltage level;

L = LOW voltage level;

X = don't care;

= LOW-to-HIGH CP transition;

Q

n+1

= state after the next LOW-to-HIGH CP transition.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

AHC

AHCT

t

PHL

/t

PLH

propagation delay

C

L

= 15 pF;

V

CC

= 5 V

nCP to nQ, nQ

3.7

3.3

ns

nS

D

, nR

D

to nQ, nQ

3.7

3.7

ns

f

max

max. clock frequency

130

100

MHz

C

I

input capacitance

V

I

= V

CC

or GND 4.0

4.0

pF

C

PD

power dissipation

capacitance

C

L

= 50 pF;

f = 1 MHz;

notes 1 and 2

12

16

pF

INPUT

OUTPUT

nS

D

nR

D

nCP

nD

nQ

nQ

L

H

X

X

H

L

H

L

X

X

L

H

L

L

X

X

H

H

INPUT

OUTPUT

nS

D

nR

D

nCP

nD

nQ

n+1

nQ

n+1

H

H

L

L

H

H

H

H

H

L

1999 Sep 23

3

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset;

positive-edge trigger

74AHC74; 74AHCT74

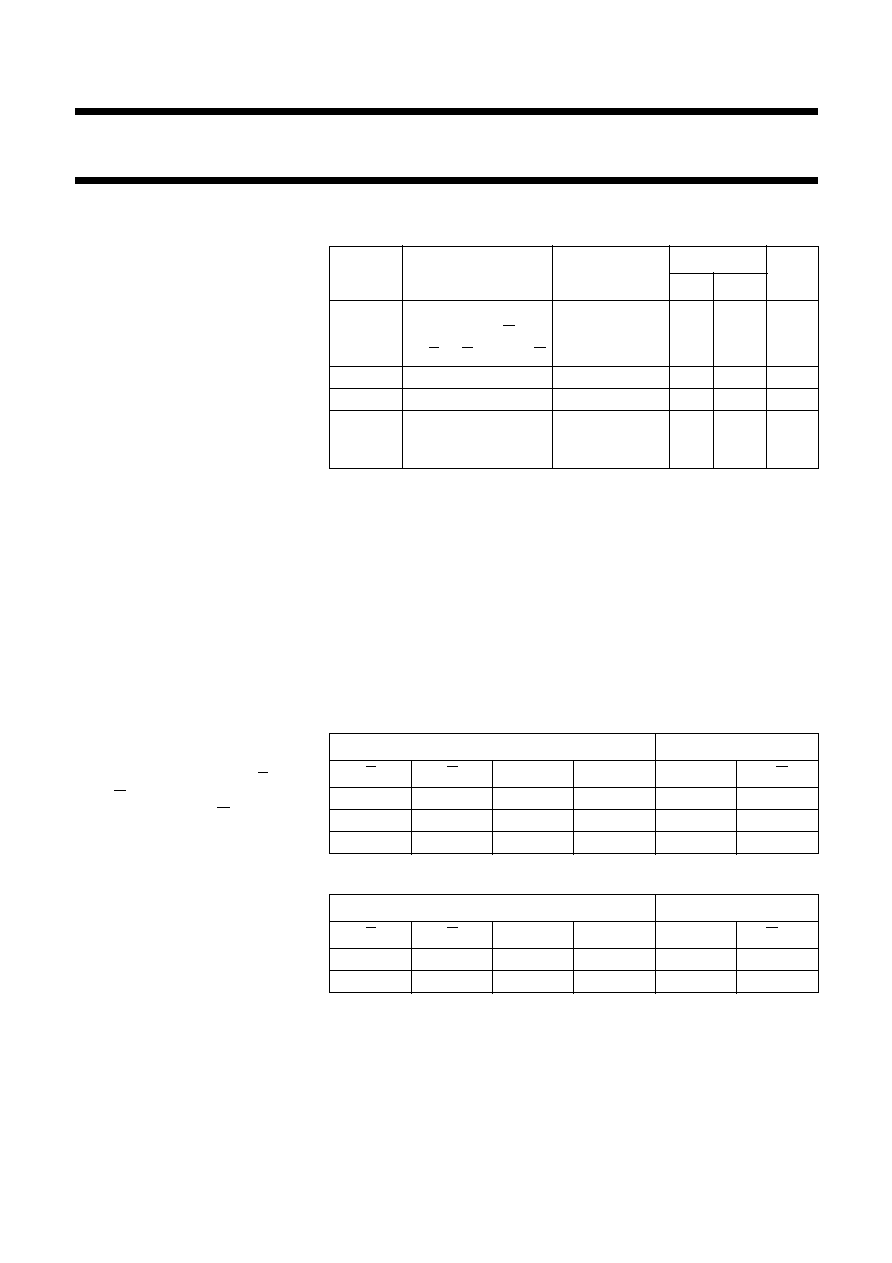

ORDERING INFORMATION

PINNING

OUTSIDE

NORTH

AMERICA

NORTH AMERICA

PACKAGE

TEMPERATURE

RANGE

PINS

PACKAGE

MATERIAL

CODE

74AHC74D

74AHC74D

-

40 to +85

∞

C

14

SO

plastic

SOT108-1

74AHC74PW

74AHC74PW DH

14

TSSOP

plastic

SOT402-1

74AHCT74D

74AHCT74D

14

SO

plastic

SOT108-1

74AHCT74PW

74AHCT74PW DH

14

TSSOP

plastic

SOT402-1

PIN

SYMBOL

DESCRIPTION

1 and 13

1R

D

and 2R

D

asynchronous reset-direct input (active LOW)

2 and 12

1D and 2D

data inputs

3 and 11

1CP and 2CP

clock input (LOW-to-HIGH, edge-triggered)

4 and 10

1S

D

and 2S

D

asynchronous set-direct input (active LOW)

5 and 9

1Q and 2Q

true flip-flop outputs

6 and 8

1Q and 2Q

complement flip-flop outputs

7

GND

ground (0 V)

14

V

CC

DC supply voltage

Fig.1 Pin configuration.

handbook, halfpage

MNA417

74

1

2

3

4

5

6

7

8

14

13

12

11

10

9

1RD

1D

1CP

1SD

1Q

1Q

GND

2Q

2Q

2SD

2CP

2D

2RD

VCC

Fig.2 Logic diagram.

MNA418

handbook, halfpage

RD

FF

SD

4 10

Q

1Q

2Q

1Q

2Q

5

9

2

12

3

11

6

8

Q

1SD

CP

2CP

1CP

2D

1D

D

2SD

1 13

1RD 2RD

1999 Sep 23

5

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset;

positive-edge trigger

74AHC74; 74AHCT74

RECOMMENDED OPERATING CONDITIONS

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134); voltages are referenced to GND (ground = 0 V).

Notes

1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. For SO packages: above 70

∞

C the value of P

D

derates linearly with 8 mW/K.

For TSSOP packages: above 60

∞

C the value of P

D

derates linearly with 5.5 mW/K.

SYMBOL

PARAMETER

CONDITIONS

74AHC

74AHCT

UNIT

MIN.

TYP.

MAX.

MIN.

TYP.

MAX.

V

CC

DC supply voltage

2.0

5.0

5.5

4.5

5.0

5.5

V

V

I

input voltage

0

-

5.5

0

-

5.5

V

V

O

output voltage

0

-

V

CC

0

-

V

CC

V

T

amb

operating ambient temperature

see DC and AC

characteristics per

device

-

40

+25

+85

-

40

+25

+85

∞

C

-

40

+25

+125

-

40

+25

+125

∞

C

t

r

,t

f

(

t/

f) input rise and fall rates

V

CC

= 3.3 V

±

0.3 V

-

-

100

-

-

-

ns/V

V

CC

= 5 V

±

0.5 V

-

-

20

-

-

20

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX. UNIT

V

CC

DC supply voltage

-

0.5

+7.0

V

V

I

input voltage

-

0.5

+7.0

V

I

IK

DC input diode current

V

I

<

-

0.5 V; note 1

-

-

20

mA

I

OK

DC output diode current

V

O

<

-

0.5 V or V

O

> V

CC

+ 0.5 V; note 1

-

±

20

mA

I

O

DC output source or sink current

-

0.5 V < V

O

< V

CC

+ 0.5 V

-

±

25

mA

I

CC

DC V

CC

or GND current

-

±

75

mA

T

stg

storage temperature

-

65

+150

∞

C

P

D

power dissipation per package

for temperature range:

-

40 to +85

∞

C; note 2

-

500

mW