| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: BSH102 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DATA SHEET

Product specification

Supersedes data of 1997 Jun 19

File under Discrete Semiconductors, SC13b

1997 Dec 08

DISCRETE SEMICONDUCTORS

BSH102

N-channel enhancement mode

MOS transistor

andbook, halfpage

M3D088

1997 Dec 08

2

Philips Semiconductors

Product specification

N-channel enhancement mode

MOS transistor

BSH102

FEATURES

∑

Very low threshold

∑

High-speed switching

∑

No secondary breakdown

∑

Direct interface to C-MOS, TTL etc.

APPLICATIONS

∑

Power management

∑

DC to DC converters

∑

Battery powered applications

∑

`Glue-logic'; interface between logic blocks and/or

periphery

∑

General purpose switch.

DESCRIPTION

N-channel enhancement mode MOS transistor in a SOT23

SMD package.

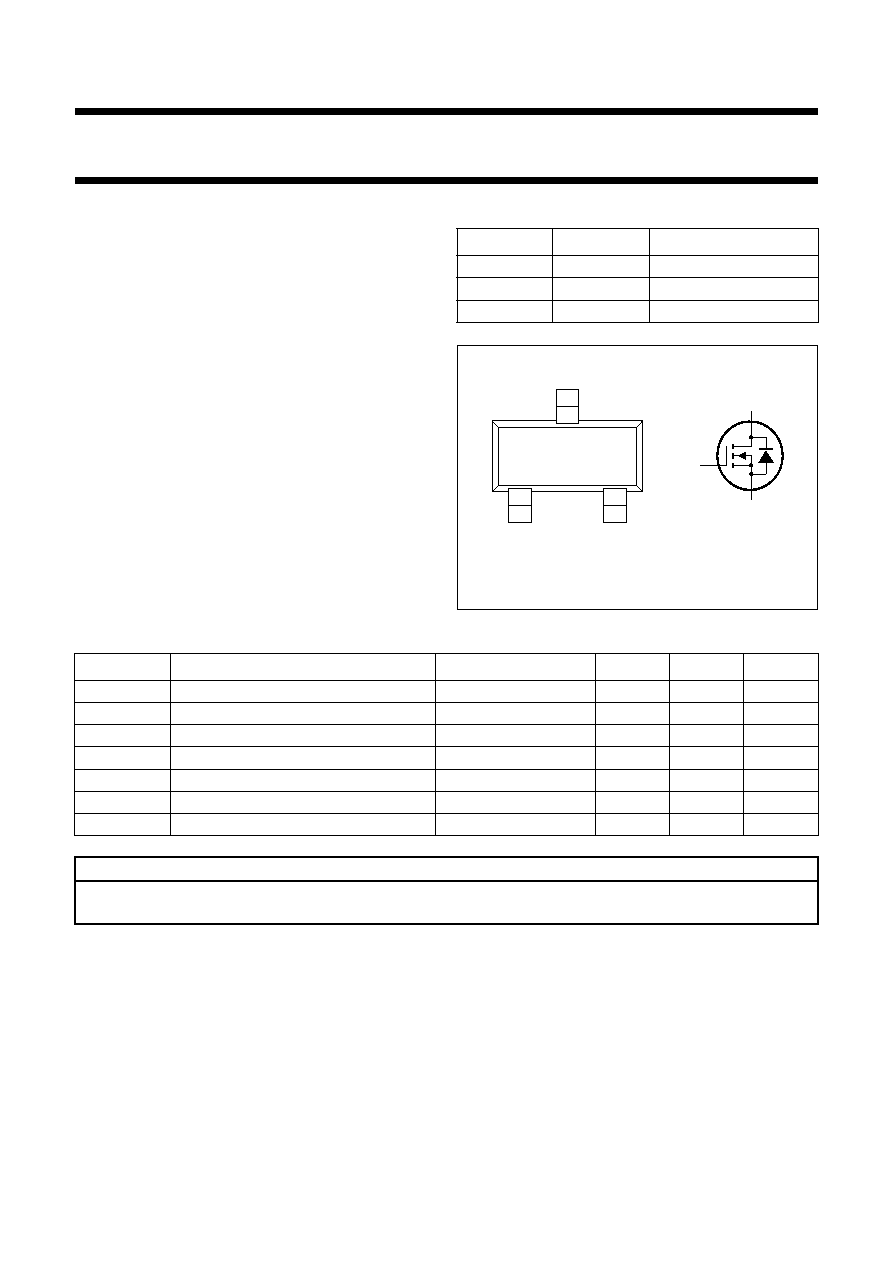

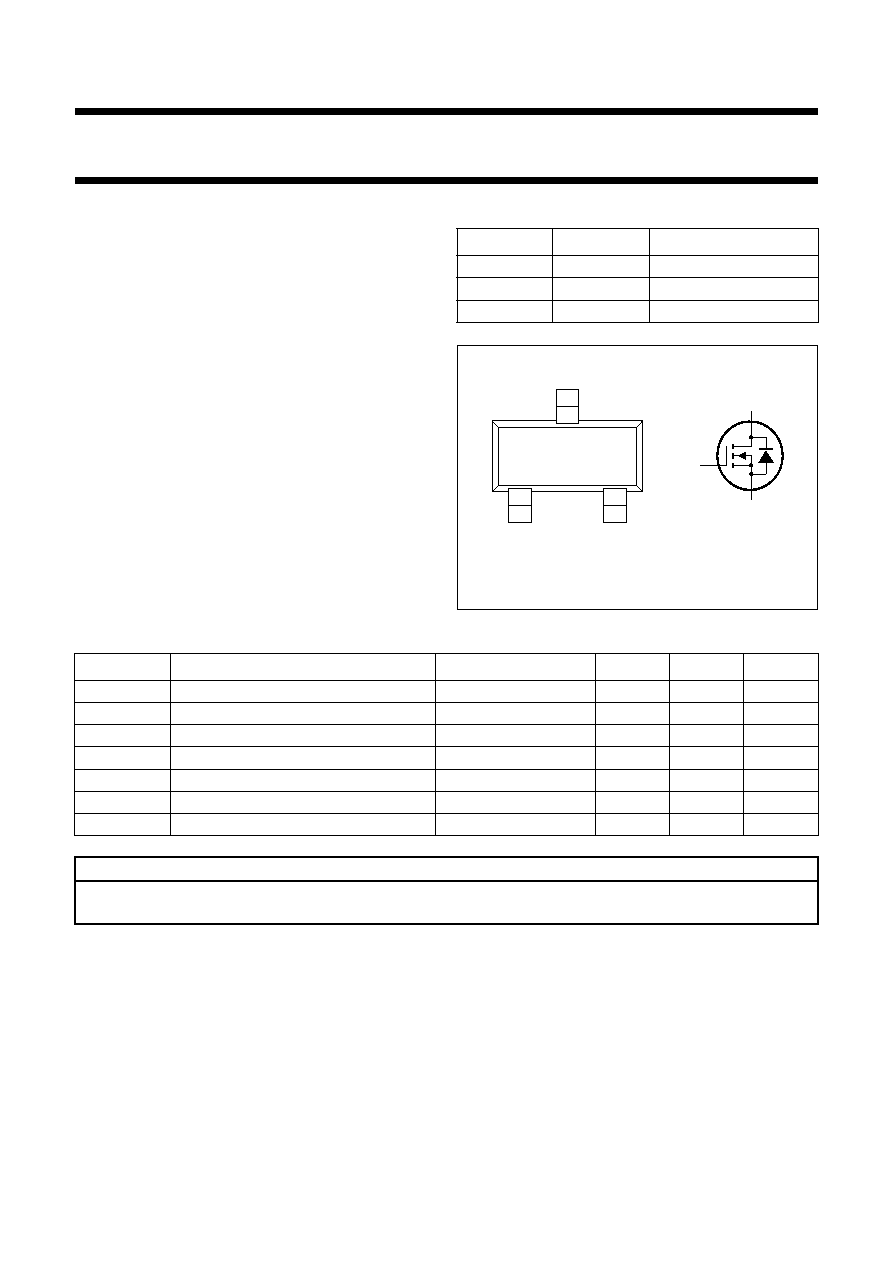

PINNING - SOT23

PIN

SYMBOL

DESCRIPTION

1

g

gate

2

s

source

3

d

drain

Fig.1 Simplified outline and symbol.

handbook, halfpage

s

d

g

MAM273

2

1

3

Top view

QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

V

DS

drain-source voltage (DC)

-

30

V

V

SD

source-drain diode forward voltage

V

GD

= 0; I

S

= 0.5 A

-

1

V

V

GS

gate-source voltage (DC)

-

±

20

V

V

GSth

gate-source threshold voltage

V

DS

= V

GS

; I

D

= 1 mA

1

-

V

I

D

drain current (DC)

T

s

= 80

∞

C

-

0.85

A

R

DSon

drain-source on-state resistance

V

GS

= 10 V; I

D

= 0.5 A

-

0.4

P

tot

total power dissipation

T

s

= 80

∞

C

-

0.5

W

CAUTION

This product is supplied in anti-static packing to prevent damage caused by electrostatic discharge during transport

and handling. For further information, refer to Philips specs.: SNW-EQ-608, SNW-FQ-302A and SNW-FQ-302B.

1997 Dec 08

3

Philips Semiconductors

Product specification

N-channel enhancement mode

MOS transistor

BSH102

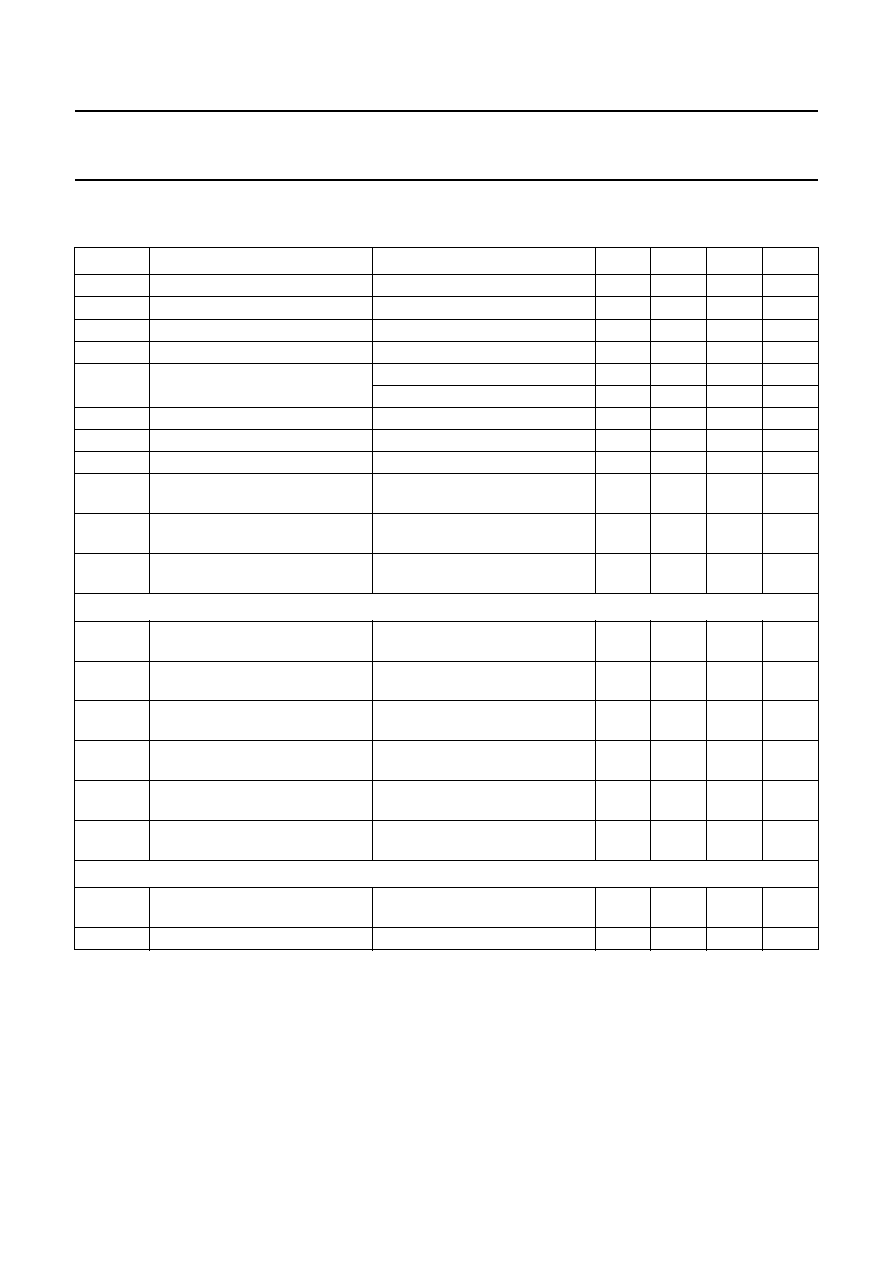

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

Notes

1. T

s

is the temperature at the soldering point of the drain lead.

2. Pulse width and duty cycle limited by maximum junction temperature.

3. Device mounted on printed-circuit board with an R

th a-tp

(ambient to tie-point) of 27.5 K/W.

4. Device mounted on printed-circuit board with an R

th a-tp

(ambient to tie-point) of 90 K/W.

SYMBOL

PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

V

DS

drain-source voltage (DC)

-

30

V

V

GS

gate-source voltage (DC)

-

±

20

V

I

D

drain current (DC)

T

s

= 80

∞

C; note 1

-

0.85

A

I

DM

peak drain current

note 2

-

3.4

A

P

tot

total power dissipation

T

s

= 80

∞

C

-

0.5

W

T

amb

= 25

∞

C; note 3

-

0.75

W

T

amb

= 25

∞

C; note 4

-

0.54

W

T

stg

storage temperature

-

55

+150

∞

C

T

j

operating junction temperature

-

55

+150

∞

C

Source-drain diode

I

S

source current (DC)

T

s

= 80

∞

C

-

0.5

A

I

SM

peak pulsed source current

note 2

-

2

A

Fig.2 Power derating curve.

handbook, halfpage

0

40

80

160

0.6

0.2

0

0.4

MGM190

120

Ptot

(W)

TS (

∞

C)

Fig.3 SOAR.

= 0.01; T

s

= 80

∞

C.

(1) R

DSon

limitation.

handbook, halfpage

MGM210

10

1

1

10

10

-

3

10

-

2

10

-

1

10

2

10

-

1

VDS (V)

IDS

(A)

t p

T

P

t

t p

T

=

DC

(1)

1997 Dec 08

4

Philips Semiconductors

Product specification

N-channel enhancement mode

MOS transistor

BSH102

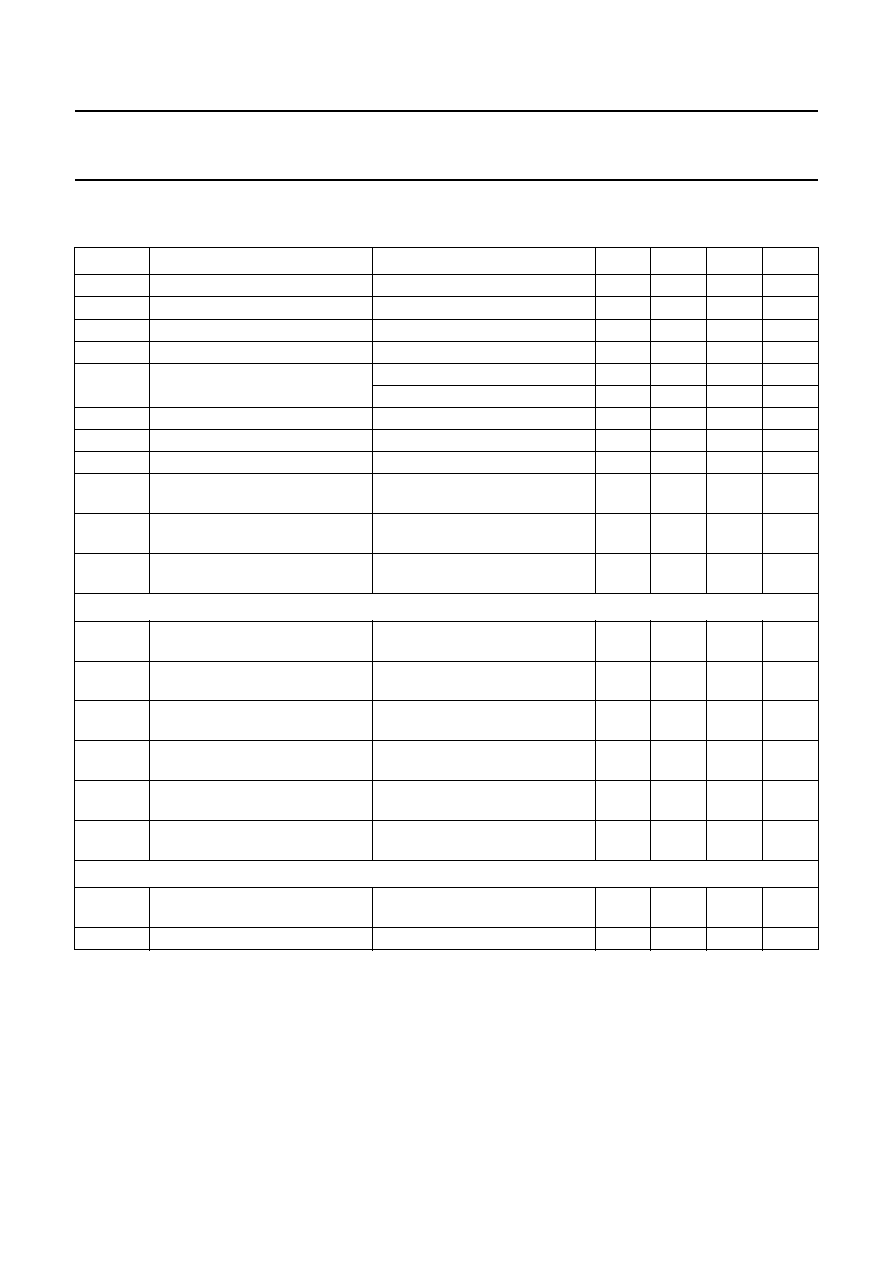

THERMAL CHARACTERISTICS

SYMBOL

PARAMETER

VALUE

UNIT

R

th j-s

thermal resistance from junction to soldering point

140

K/W

Fig.4 Transient thermal resistance from junction to soldering point as a function of pulse time; typical values.

(1)

= 1.

(2)

= 0.75.

(3)

= 0.5.

(4)

= 0.33.

(5)

= 0.2.

(6)

= 0.1.

(7)

= 0.05.

(8)

= 0.02.

(9)

= 0.01.

(10)

= 0.

handbook, full pagewidth

10

3

10

2

10

1

10

-

6

10

-

5

10

-

4

10

-

3

10

-

2

10

-

1

1

MGM201

Rth j-s

(K/W)

tp (s)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

tp

tp

T

P

t

T

=

1997 Dec 08

5

Philips Semiconductors

Product specification

N-channel enhancement mode

MOS transistor

BSH102

CHARACTERISTICS

T

j

= 25

∞

C unless otherwise specified.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

V

(BR)DSS

drain-source breakdown voltage

V

GS

= 0; I

D

= 10

µ

A

30

-

-

V

V

GSth

gate-source threshold voltage

V

GS

= V

DS

; I

D

= 1 mA

1

-

-

V

I

DSS

drain-source leakage current

V

GS

= 0; V

DS

= 24 V

-

-

100

nA

I

GSS

gate leakage current

V

GS

=

±

20 V; V

DS

= 0

-

-

±

100

nA

R

DSon

drain-source on-state resistance

V

GS

= 10 V; I

D

= 0.5 A

-

-

0.4

V

GS

= 4.5 V; I

D

= 0.25 A

-

-

0.6

C

iss

input capacitance

V

GS

= 0; V

DS

= 24 V; f = 1 MHz

-

67

-

pF

C

oss

output capacitance

V

GS

= 0; V

DS

= 24 V; f = 1 MHz

-

27

-

pF

C

rss

reverse transfer capacitance

V

GS

= 0; V

DS

= 24 V; f = 1 MHz

-

13

-

pF

Q

G

total gate charge

V

GS

= 10 V; V

DD

= 15 V;

I

D

= 0.5 A; T

amb

= 25

∞

C

-

2290

-

pC

Q

GS

gate-source charge

V

DD

= 15 V; I

D

= 0.5 A;

T

amb

= 25

∞

C

-

150

-

pC

Q

GD

gate-drain charge

V

DD

= 15 V; I

D

= 0.5 A;

T

amb

= 25

∞

C

-

780

-

pC

Switching times

t

d(on)

turn-on delay time

V

GS

= 0 to 10 V; V

DD

= 15 V;

I

D

= 0.5 A; R

gen

= 6

-

3.5

-

ns

t

f

fall time

V

GS

= 0 to 10 V; V

DD

= 15 V;

I

D

= 0.5 A; R

gen

= 6

-

4

-

ns

t

on

turn-on switching time

V

GS

= 0 to 10 V; V

DD

= 15 V;

I

D

= 0.5 A; R

gen

= 6

-

7.5

-

ns

t

d(off)

turn-off delay time

V

GS

= 10 to 0 V; V

DD

= 15 V;

I

D

= 0.5 A; R

gen

= 6

-

8

-

ns

t

r

rise time

V

GS

= 10 to 0 V; V

DD

= 15 V;

I

D

= 0.5 A; R

gen

= 6

-

3

-

ns

t

off

turn-off switching time

V

GS

= 10 to 0 V; V

DD

= 15 V;

I

D

= 0.5 A; R

gen

= 6

-

11

-

ns

Source-drain diode

V

SD

source-drain diode forward

voltage

V

GD

= 0; I

S

= 0.5 A

-

-

1

V

t

rr

reverse recovery time

I

S

= 0.5 A; di/dt =

-

100 A/

µ

s

-

25

-

ns