Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

BUK7516-55A; BUK7616-55A

TrenchMOSTM standard level FET

Rev. 01 -- 18 January 2001

Product specification

c

c

1.

Description

N-channel enhancement mode field-effect power transistor in a plastic package using

TrenchMOSTM technology, featuring very low on-state resistance.

Product availability:

BUK7516-55A in SOT78 (TO-220AB)

BUK7616-55A in SOT404

(D

2

-PAK).

2.

Features

s

TrenchMOSTM technology

s

Q101 compliant

s

175

°

C rated

s

Standard level compatible.

3.

Applications

s

Automotive and general purpose power switching:

x

12 V and 24 V loads

x

Motors, lamps and solenoids.

4.

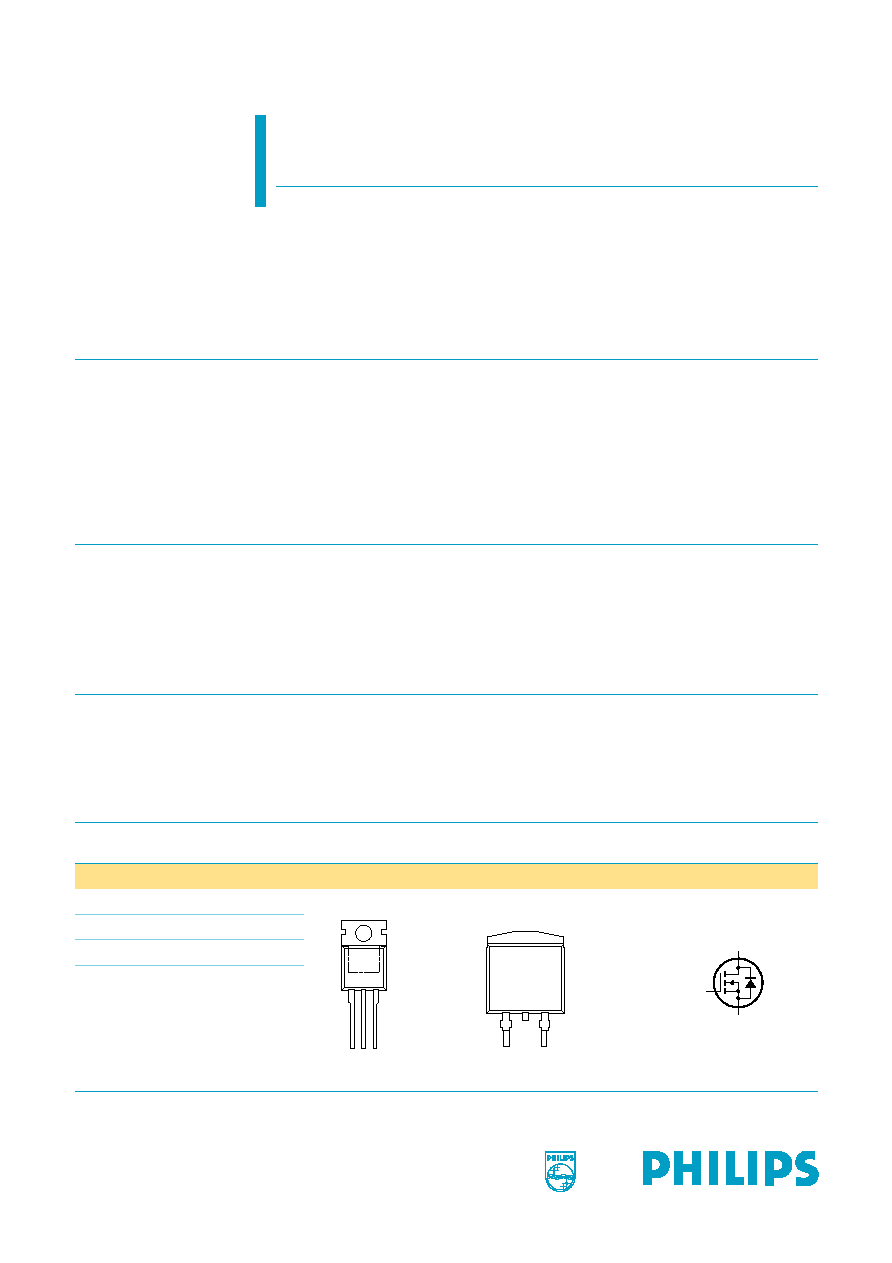

Pinning information

Table 1:

Pinning - SOT78, SOT404, simplified outline and symbol

Pin

Description

Simplified outline

Symbol

1

gate (g)

SOT78 (TO-220AB)

SOT404 (D

2

-PAK)

2

drain (d)

3

source (s)

mb

mounting base;

connected to drain (d)

MBK106

1 2

mb

3

1

3

2

MBK116

mb

s

d

g

MBB076

Philips Semiconductors

BUK7516-55A; BUK7616-55A

TrenchMOSTM standard level FET

Product specification

Rev. 01 -- 18 January 2001

2 of 15

9397 750 07682

© Philips Electronics N.V. 2001. All rights reserved.

5.

Quick reference data

6.

Limiting values

Table 2:

Quick reference data

Symbol Parameter

Conditions

Typ

Max

Unit

V

DS

drain-source voltage (DC)

-

55

V

I

D

drain current (DC)

T

mb

= 25

°

C; V

GS

= 10 V

-

65.7

A

P

tot

total power dissipation

T

mb

= 25

°

C

-

138

W

T

j

junction temperature

-

175

°

C

R

DSon

drain-source on-state resistance

V

GS

= 10 V; I

D

= 25 A

T

j

= 25

°

C

13

16

m

T

j

= 175

°

C

-

32

m

Table 3:

Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter

Conditions

Min

Max

Unit

V

DS

drain-source voltage (DC)

-

55

V

V

DGR

drain-gate voltage (DC)

R

GS

= 20 k

-

55

V

V

GS

gate-source voltage (DC)

-

±

20

V

I

D

drain current (DC)

T

mb

= 25

°

C; V

GS

= 10 V;

Figure 2

and

3

-

65.7

A

T

mb

= 100

°

C; V

GS

= 10 V;

Figure 2

-

46.5

A

I

DM

peak drain current

T

mb

= 25

°

C; pulsed; t

p

10

µ

s;

Figure 3

-

263

A

P

tot

total power dissipation

T

mb

= 25

°

C;

Figure 1

-

138

W

T

stg

storage temperature

-

55

+175

°

C

T

j

operating junction temperature

-

55

+175

°

C

Source-drain diode

I

DR

reverse drain current (DC)

T

mb

= 25

°

C

-

65.7

A

I

DRM

pulsed reverse drain current

T

mb

= 25

°

C; pulsed; t

p

10

µ

s

-

263

A

Avalanche ruggedness

W

DSS

non-repetitive avalanche energy

unclamped inductive load; I

D

= 49 A;

V

DS

55 V; V

GS

= 10 V; R

GS

= 50

;

starting T

mb

= 25

°

C

-

120

mJ

Philips Semiconductors

BUK7516-55A; BUK7616-55A

TrenchMOSTM standard level FET

Product specification

Rev. 01 -- 18 January 2001

3 of 15

9397 750 07682

© Philips Electronics N.V. 2001. All rights reserved.

V

GS

4.5 V

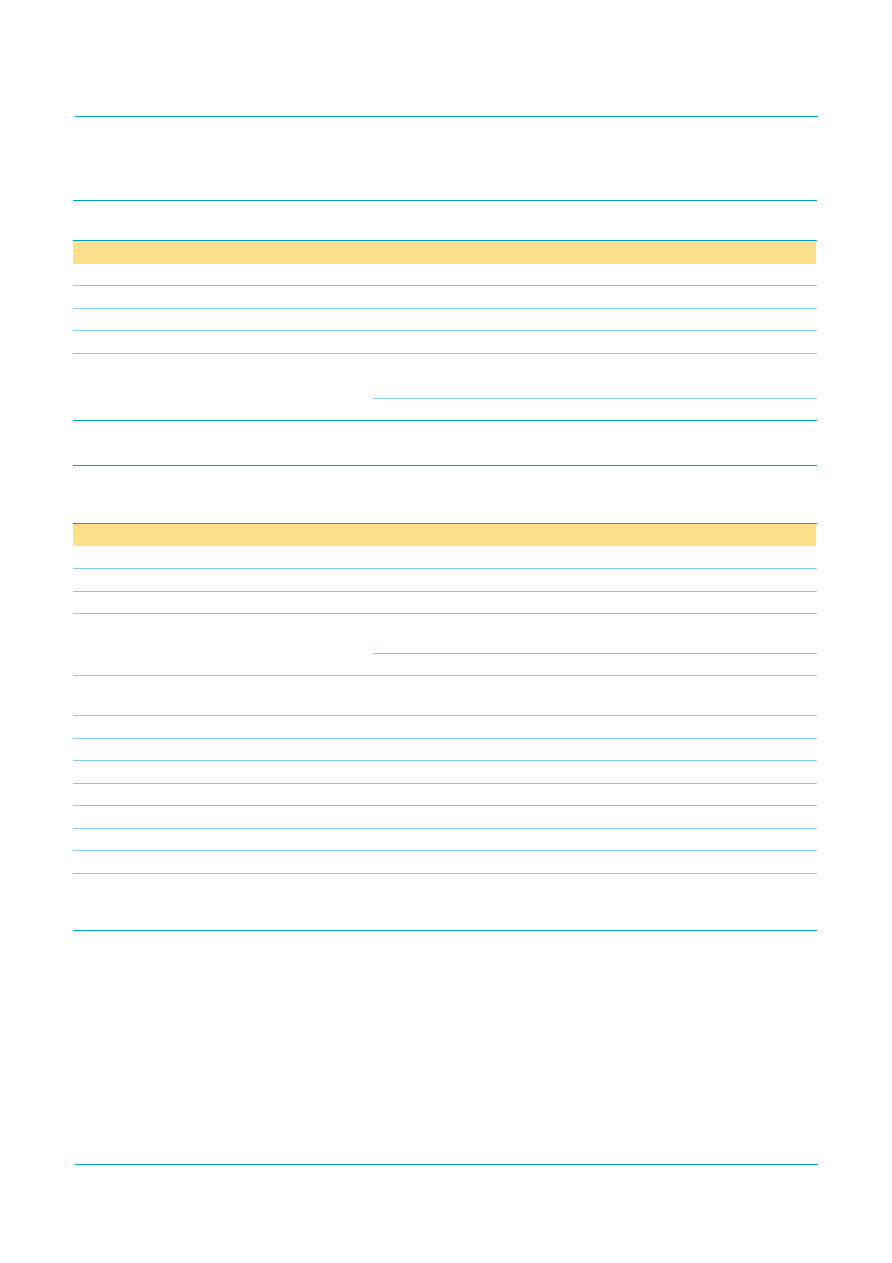

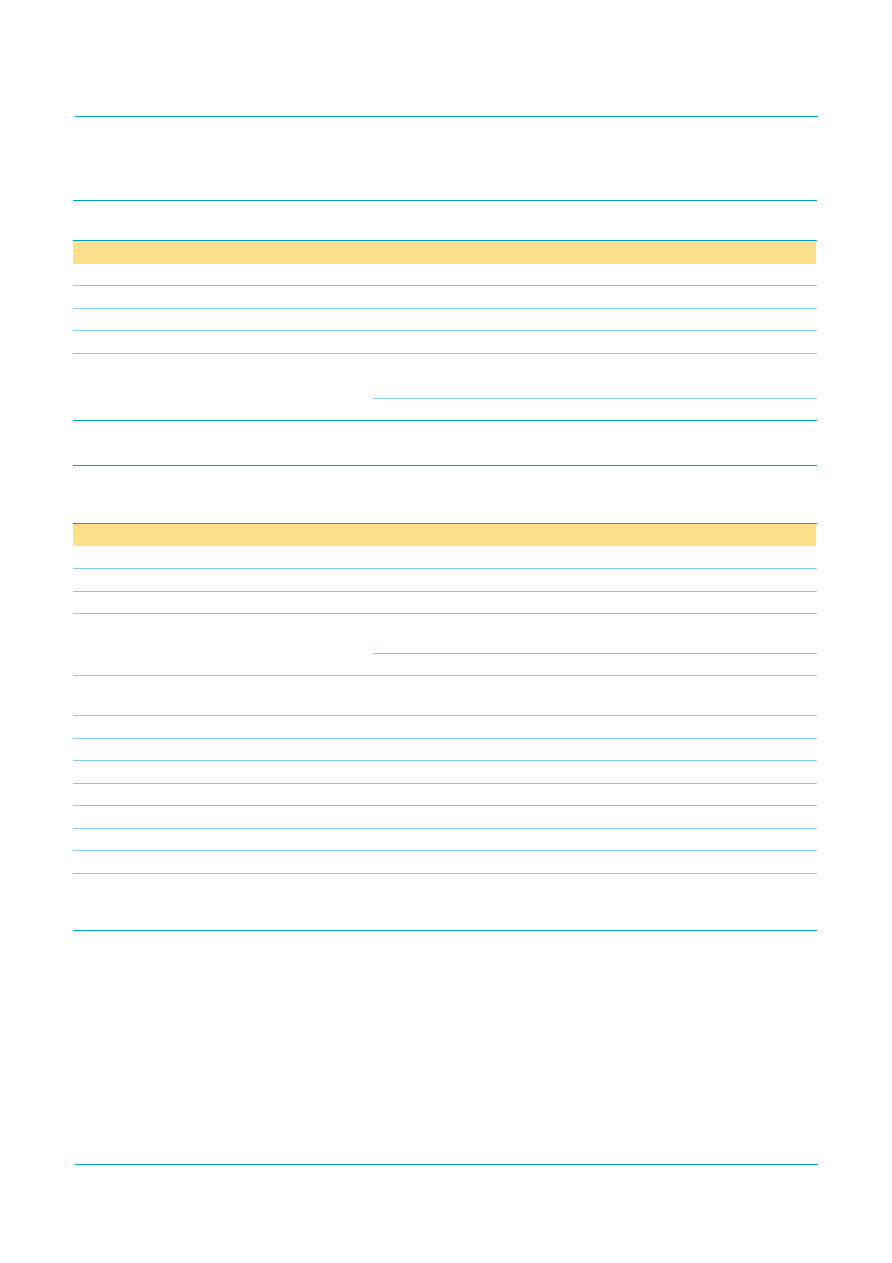

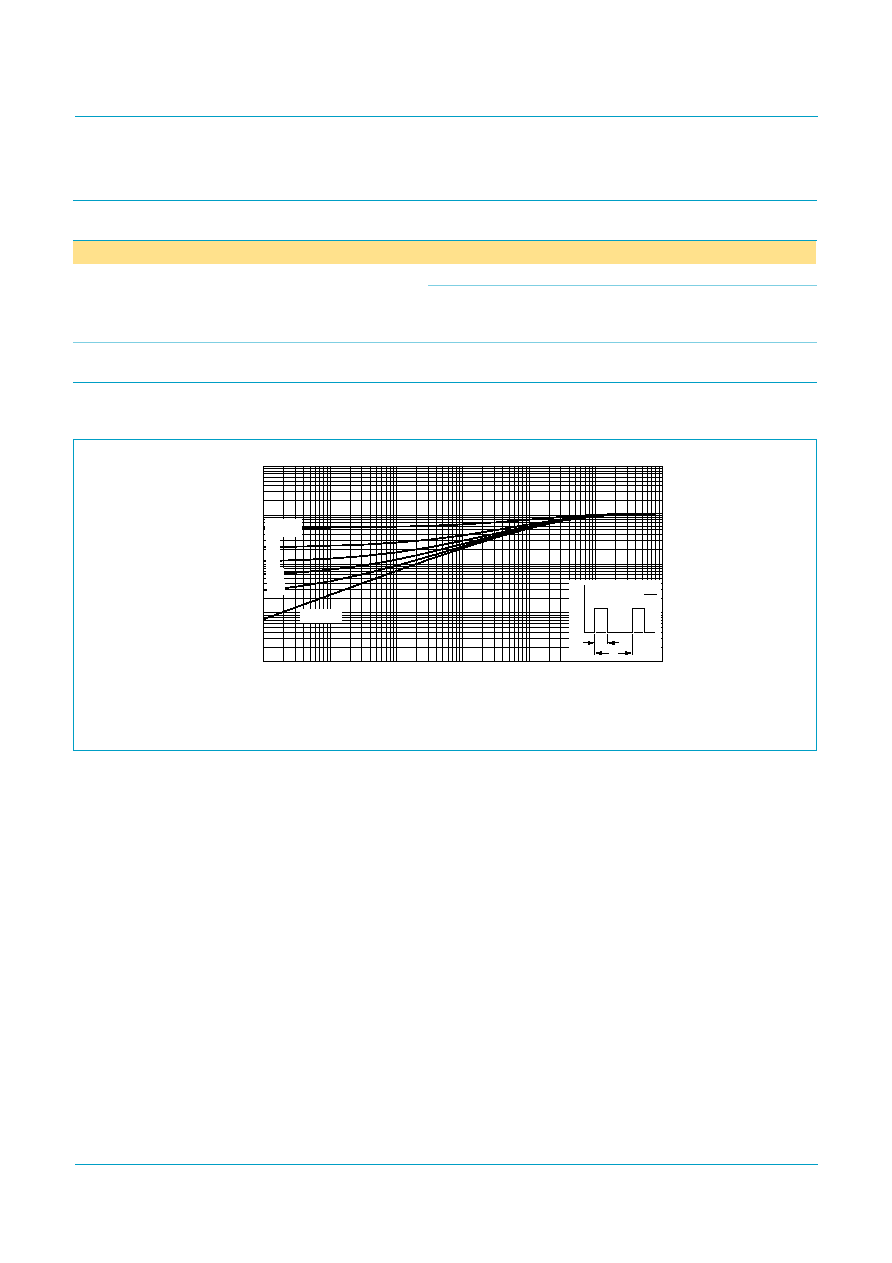

Fig 1.

Normalized total power dissipation as a

function of mounting base temperature.

Fig 2.

Normalized continuous drain current as a

function of mounting base temperature.

T

mb

= 25

°

C; I

DM

single pulse.

Fig 3.

Safe operating area; continuous and peak drain currents as a function of drain-source voltage.

03na19

0

20

40

60

80

100

120

0

25

50

75

100

125

150

175

200

P

der

(%)

Tmb (

o

C)

03aa24

0

20

40

60

80

100

120

0

25

50

75

100

125

150

175

200

I

der

(%)

T

mb

(

o

C)

P

der

P

tot

P

tot 25 C

°

(

)

----------------------

100%

×

=

I

der

I

D

I

D 25 C

°

(

)

-------------------

100%

×

=

03nc01

1

10

102

103

1

10

102

VDS (V)

ID

(A)

D.C.

100 ms

10 ms

RDSon = VDS/ ID

1 ms

tp = 10 us

100 us

tp

tp

T

P

t

T

=

Philips Semiconductors

BUK7516-55A; BUK7616-55A

TrenchMOSTM standard level FET

Product specification

Rev. 01 -- 18 January 2001

4 of 15

9397 750 07682

© Philips Electronics N.V. 2001. All rights reserved.

7.

Thermal characteristics

7.1 Transient thermal impedance

Table 4:

Thermal characteristics

Symbol

Parameter

Conditions

Value

Unit

R

th(j-a)

thermal resistance from junction to ambient

vertical in still air; SOT78 package

60

K/W

mounted on printed circuit board;

minimum footprint; SOT404

package

50

K/W

R

th(j-mb)

thermal resistance from junction to mounting

base

Figure 4

1.1

K/W

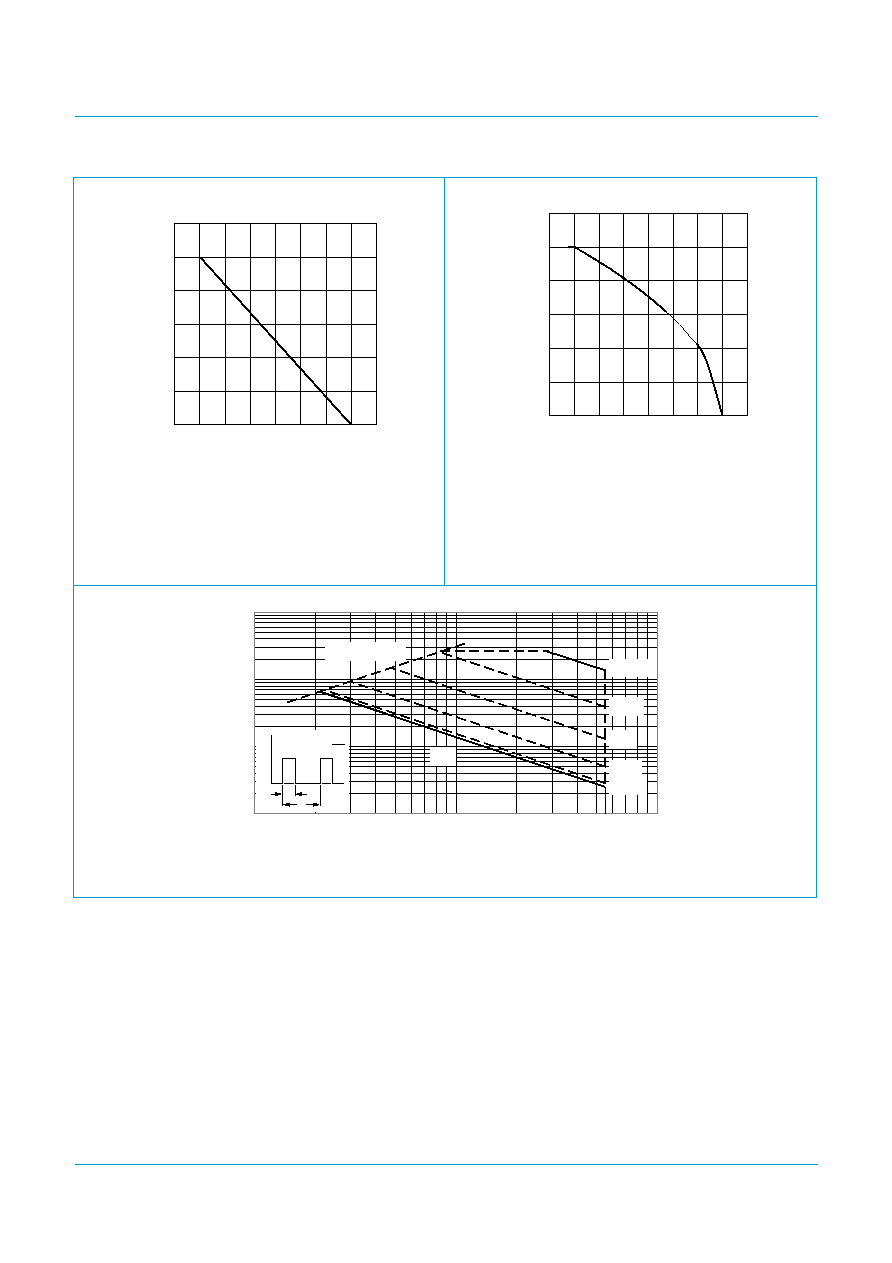

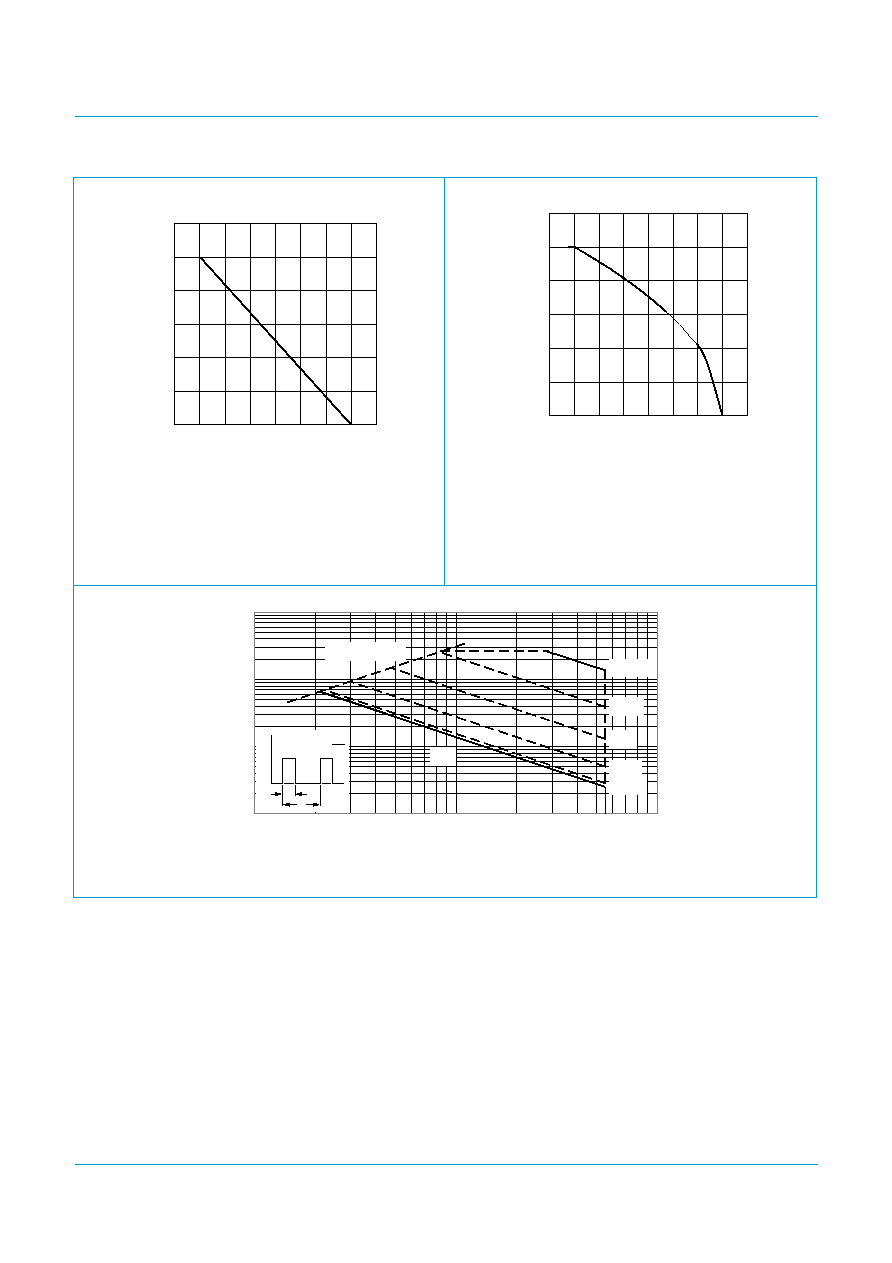

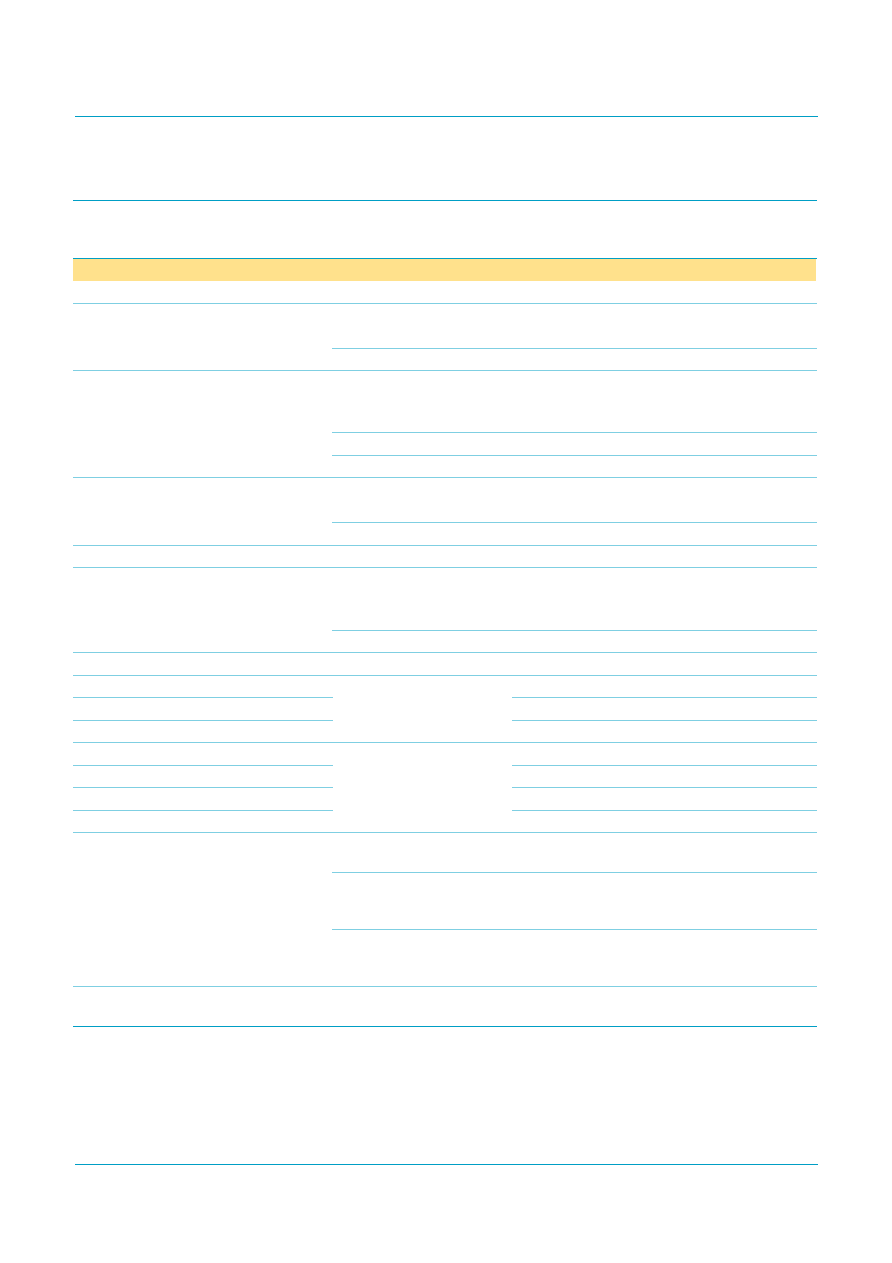

Fig 4.

Transient thermal impedance from junction to mounting base as a function of pulse duration.

03nc00

Single Shot

0.2

0.1

0.05

0.02

10-3

10-2

10-1

1

10

10-6

10-5

10-4

10-3

10-2

10-1

1

tp (s)

Zth(j-mb)

(K/W)

= 0.5

tp

tp

T

P

t

T

=

Philips Semiconductors

BUK7516-55A; BUK7616-55A

TrenchMOSTM standard level FET

Product specification

Rev. 01 -- 18 January 2001

5 of 15

9397 750 07682

© Philips Electronics N.V. 2001. All rights reserved.

8.

Characteristics

Table 5:

Characteristics

T

j

= 25

°

C unless otherwise specified

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Static characteristics

V

(BR)DSS

drain-source breakdown

voltage

I

D

= 0.25 mA; V

GS

= 0 V

T

j

= 25

°

C

55

-

-

V

T

j

=

-

55

°

C

50

-

-

V

V

GS(th)

gate-source threshold voltage I

D

= 1 mA; V

DS

= V

GS

;

Figure 9

T

j

= 25

°

C

2

3

4

V

T

j

= 175

°

C

1

-

-

V

T

j

=

-

55

°

C

-

-

4.4

V

I

DSS

drain-source leakage current

V

DS

= 55 V; V

GS

= 0 V

T

j

= 25

°

C

-

0.05

10

µ

A

T

j

= 175

°

C

-

-

500

µ

A

I

GSS

gate-source leakage current

V

GS

=

±

20 V; V

DS

= 0 V

-

2

100

nA

R

DSon

drain-source on-state

resistance

V

GS

= 10 V; I

D

= 25 A;

Figure 7

and

8

T

j

= 25

°

C

-

13

16

m

T

j

= 175

°

C

-

-

32

m

Dynamic characteristics

C

iss

input capacitance

V

GS

= 0 V; V

DS

= 25 V;

f = 1 MHz;

Figure 12

-

1580

2245

pF

C

oss

output capacitance

-

370

423

pF

C

rss

reverse transfer capacitance

-

220

312

pF

t

d(on)

turn-on delay time

V

DD

= 30 V; R

L

= 1.2

;

V

GS

= 10 V; R

G

= 10

;

-

16

-

ns

t

r

rise time

-

70

-

ns

t

d(off)

turn-off delay time

-

57

-

ns

t

f

fall time

-

41

-

ns

L

d

internal drain inductance

from drain lead 6mm from

package to centre of die

-

4.5

-

nH

from contact screw on

mounting base to centre of

die SOT78

-

3.5

-

nH

from upper edge of drain

mounting base to centre of

die SOT404

-

2.5

-

nH

L

s

internal source inductance

from source lead to source

bond pad

-

7.5

-

nH

Document Outline