DATA SHEET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4502B

buffers

Strobed hex inverter/buffer

For a complete data sheet, please also download:

∑

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

∑

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

January 1995

2

Philips Semiconductors

Product specification

Strobed hex inverter/buffer

HEF4502B

buffers

DESCRIPTION

The HEF4502B consists of six inverter/buffers with 3-state

outputs. When the output enable input (EO) is HIGH all six

outputs (O

1

to O

6

) are in the high impedance OFF-state.

When the enable input (E) is HIGH all six outputs are

switched to LOW. The outputs have a 2-TTL load drive

capability.

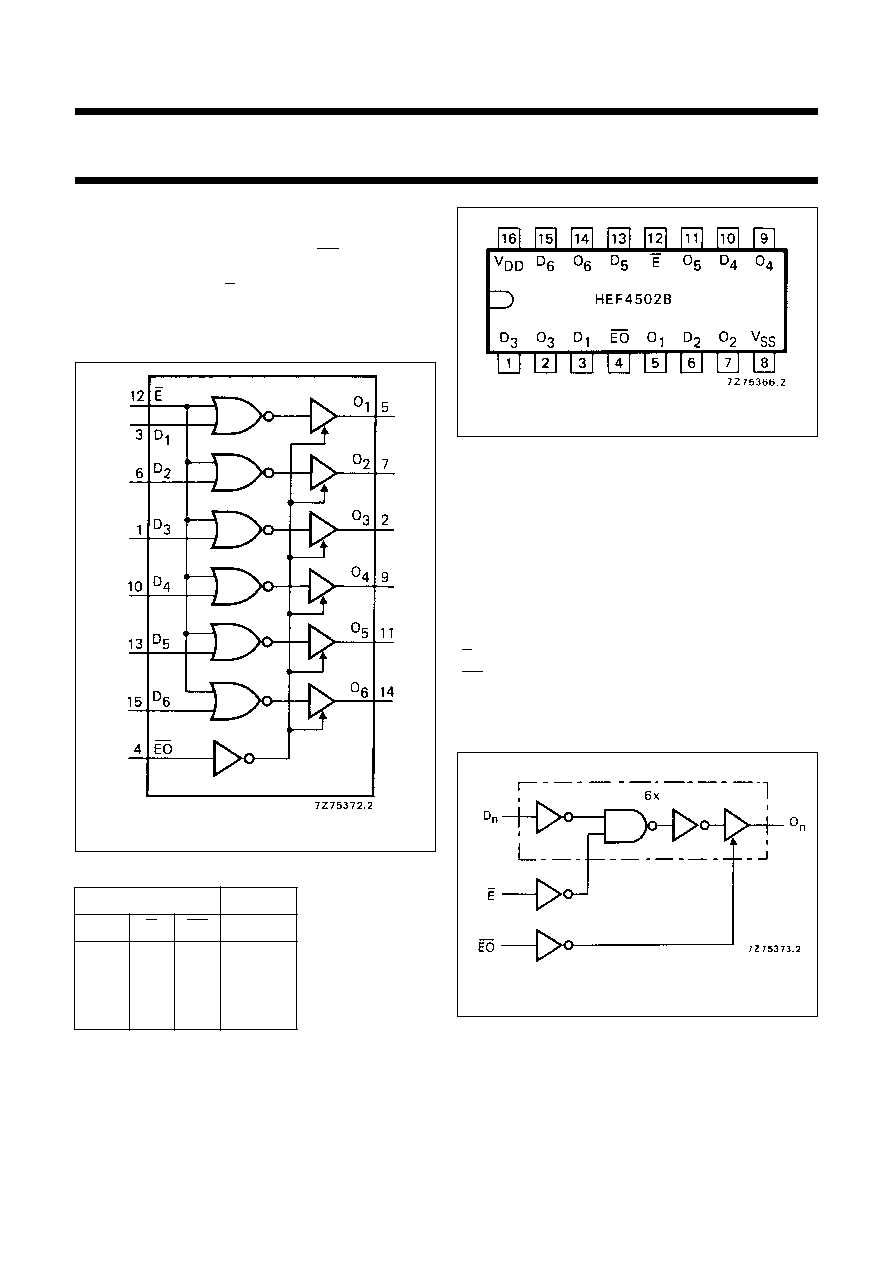

Fig.1 Functional diagram.

PINNING

HEF4502BP(N):

16-lead DIL; plastic (SOT38-1)

HEF4502BD(F):

16-lead DIL; ceramic (cerdip) (SOT74)

HEF4502BT(D):

16-lead SO; plastic (SOT109-1)

( ): Package Designator North America

D

1

to D

6

data inputs

E

enable input

EO

output enable input

O

1

to O

6

3-state outputs

Fig.2 Pinning diagram.

TRUTH TABLE

Notes

1. H = HIGH state (the more pos. voltage)

L = LOW state (the less pos. voltage)

X = state is immaterial

Z = high impedance off state

INPUTS

OUTPUT

D

n

E

EO

O

n

L

L

L

H

H

L

L

L

X

H

L

L

X

X

H

Z

FAMILY DATA, I

DD

LIMITS category BUFFERS

See Family Specifications

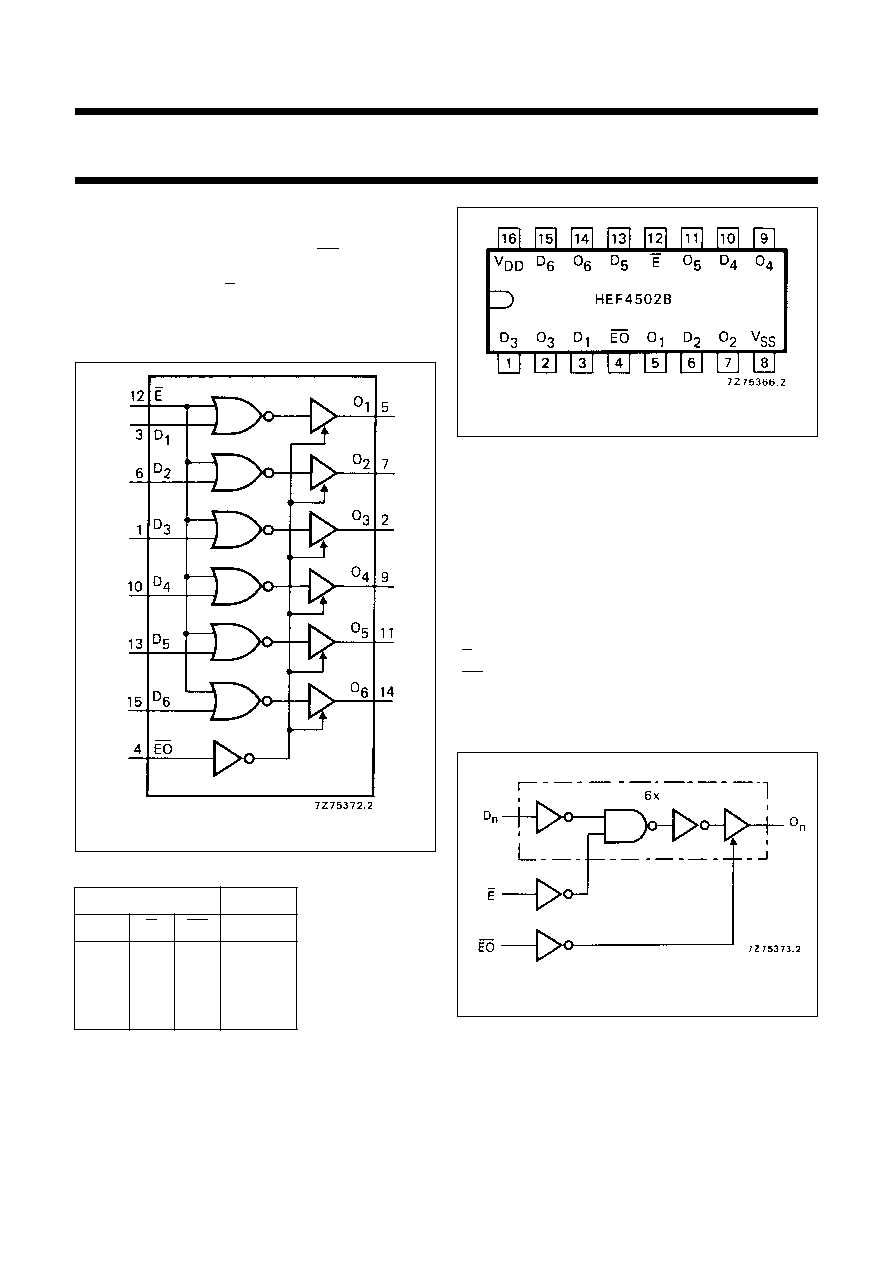

Fig.3 Logic diagram.

January 1995

4

Philips Semiconductors

Product specification

Strobed hex inverter/buffer

HEF4502B

buffers

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

= 25

∞

C; C

L

= 50 pF; input transition times

20 ns

V

DD

V

SYMBOL

TYP.

MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

D

n

, E

O

n

5

85

170 ns

77 ns

+

(0,17 ns/pF) C

L

HIGH to LOW

10

t

PHL

40

80 ns

37 ns

+

(0,06 ns/pF) C

L

15

35

70 ns

33 ns

+

(0,04 ns/pF) C

L

5

80

160 ns

66 ns

+

(0,28 ns/pF) C

L

LOW to HIGH

10

t

PLH

35

70 ns

28 ns

+

(0,13 ns/pF) C

L

15

30

60 ns

25 ns

+

(0,10 ns/pF) C

L

Output transition times

5

25

50 ns

10 ns

+

(0,30 ns/pF) C

L

HIGH to LOW

10

t

THL

12

24 ns

7 ns

+

(0,11 ns/pF) C

L

15

8

15 ns

5 ns

+

(0,07 ns/pF) C

L

5

30

60 ns

5 ns

+

(0,50 ns/pF) C

L

LOW to HIGH

10

t

TLH

15

30 ns

3 ns

+

(0,24 ns/pF) C

L

15

12

24 ns

3 ns

+

(0,18 ns/pF) C

L

3-state propagation delays

Output disable times

EO

O

n

5

60

160 ns

HIGH

10

t

PHZ

55

140 ns

15

55

140 ns

5

50

100 ns

LOW

10

t

PLZ

35

70 ns

15

30

60 ns

Output enable times

EO

O

n

5

60

120 ns

HIGH

10

t

PZH

35

70 ns

15

30

60 ns

5

55

110 ns

LOW

10

t

PZL

25

50 ns

15

20

40 ns