LH6V4256

CMOS 1M (256K

◊

4) Dynamic RAM

FUNCTION

∑∑

262,144 words

◊

4 bit

∑∑

Access time: 100 ns (MAX)

∑∑

Cycle time: 190 ns (MIN)

∑∑

Fast page mode cycle time: 60 ns (MIN)

∑∑

Power supply: +3.3 V

±

0.3 V

∑∑

Power consumption (MAX):

Operating: 126 mW

Standby: 0.54 mW

∑∑

Built-in latch circuit for row-address,

column-address, and input data

∑∑

OE = Don't care in early write operation

∑∑

RAS only refresh, hidden refresh, and

CAS before RAS refresh capability

∑∑

On-chip refresh counter

∑∑

512 refresh cycle/8 ms

∑∑

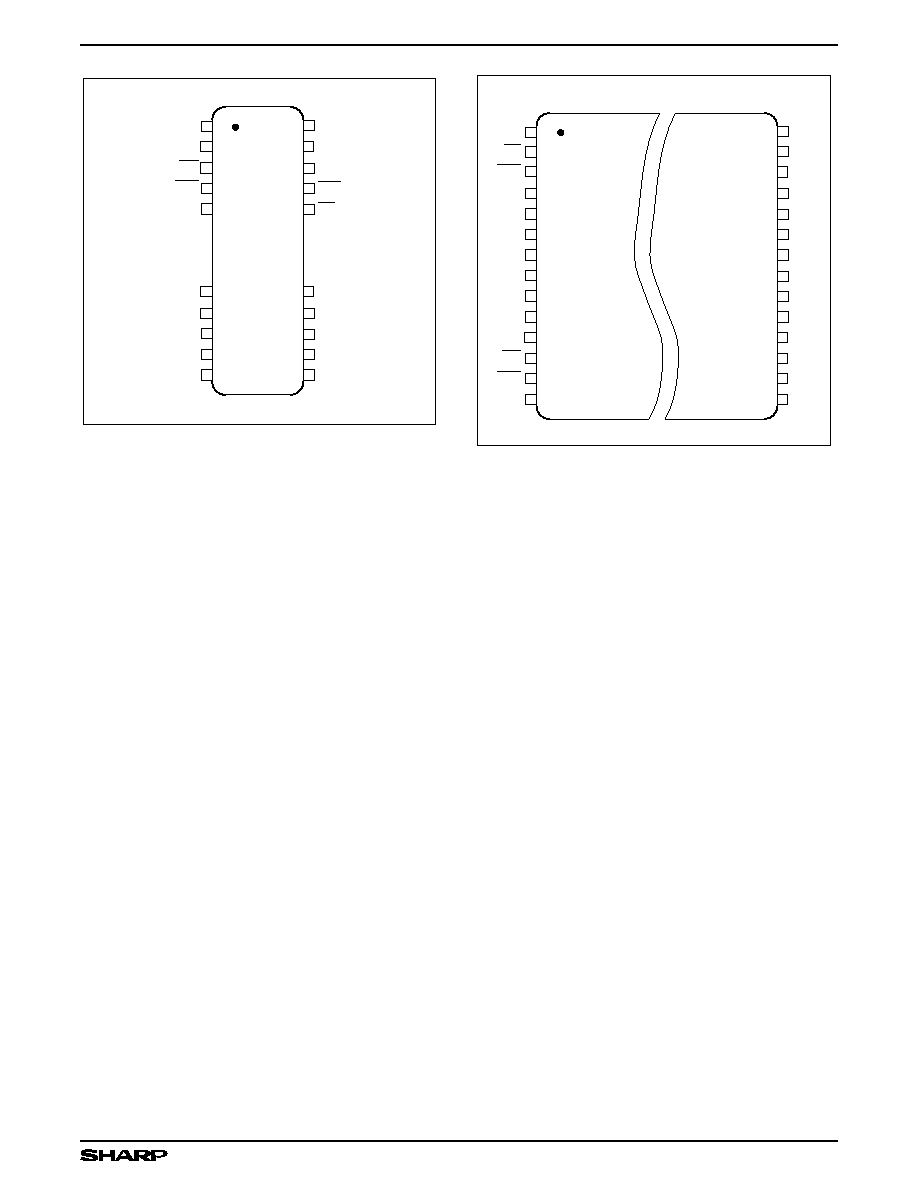

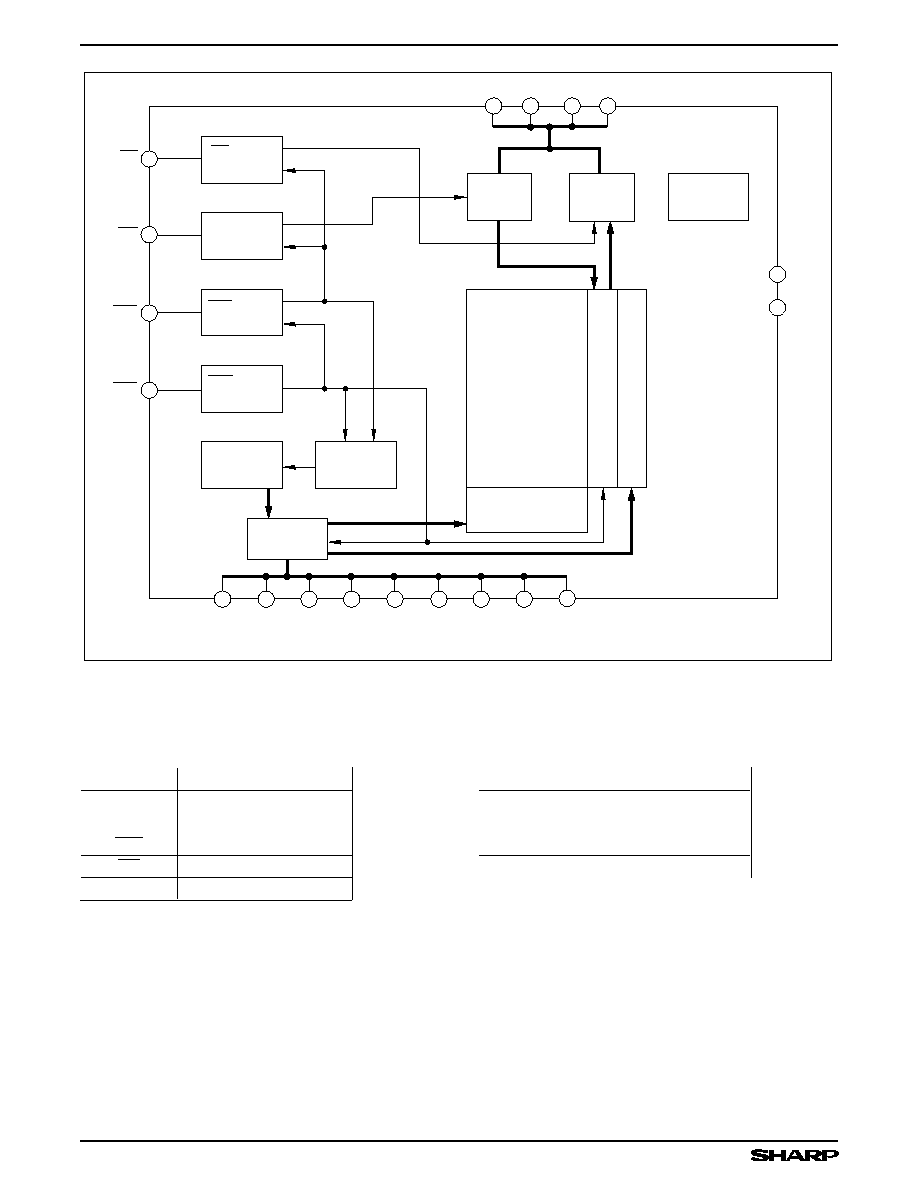

Packages:

20-pin, 300-mil DIP

26-pin, 300-mil SOJ

28-pin, 8

◊

13 mm

2

TSOP (Type I)

DESCRIPTION

The LH6V4256 is a 262,144 word

◊

4-bit dynamic

RAM which allows fast page mode access. The

LH6V4256 is fabricated on SHARP's advanced CMOS

double-level polysilicon gate technology. With its input

multiplexed and packaged in the standard 20-pin DIP,

26-pin SOJ, or 28-pin TSOP (I) packages, it is easy to

realize memory systems with low power dissipation and

large memory capacity. The LH6V4256 operates on a

single +3.3 V power supply and the built-in biasing

voltage generator circuit.

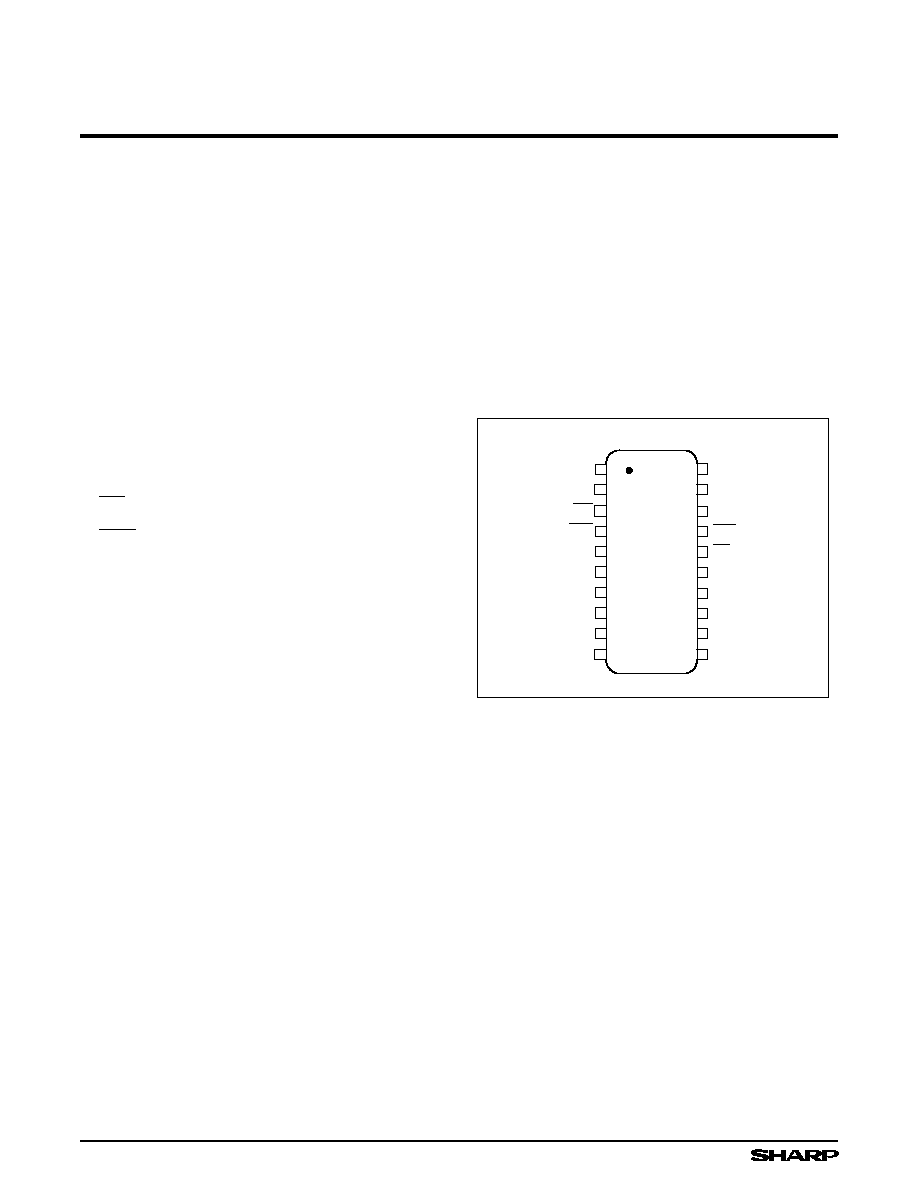

PIN CONNECTIONS

6V4256-1

TOP VIEW

1

2

3

4

7

8

A

2

NC

18

17

16

15

14

13

WE

RAS

5

6

A

1

A

0

12

11

CAS

A

8

9

10

20

19

I/O

4

A

3

V

SS

V

CC

OE

20-PIN DIP

I/O

3

A

7

A

6

A

5

A

4

I/O

2

I/O

1

Figure 1. Pin Connections for DIP Package

2-14

ABSOLUTE MAXIMUM RATINGS

PARAMETER

RATING

UNIT

NOTE

Applied voltage on all pins

≠ 0.5 to +5.5

V

1

Output short circuit current

50

mA

Power dissipation

1.0

W

Operating temperature

0 to +70

∞

C

Storage temperature

≠ 65 to +150

∞

C

NOTE:

1.

The maximum applicable voltage on any pin with respect to V

SS

.

RECOMMENDED OPERATING CONDITIONS (T

A

= 0 to +70

∞

C)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

Supply voltage

V

CC

3.0

3.3

3.6

V

V

SS

0

0

0

V

Input voltage

V

IH

2. 3

V

CC

+ 0.3

V

V

IL

≠ 0.3

0.6

V

CAPACITANCE (T

A

= 0 to +70

∞

C, f = 1 MHz, V

CC

= 3.3 V

±

0.3 V)

PARAMETER

CONDITIONS

SYMBOL

MIN.

MAX.

UNIT

Input capacitance

A

0

≠ A

8

C

IN1

6

pF

RAS, OE, CAS, WE

C

IN2

7

pF

Input/output capacitance

I/O

1

≠ I/O

4

C

OUT1

7

pF

DC ELECTRICAL CHARACTERISTICS (T

A

= 0 to +70

∞

C, V

CC

= 3.3 V

±

0.3 V)

PARAMETER

CONDITIONS

SYMBOL

MIN.

MAX.

UNIT

NOTE

Average supply current in normal operation

I

CC1

35

mA

1, 2, 3

Supply current in

standby mode

RAS = CAS

V

CC

≠ 0.2 V

I

CC2

0.15

mA

1

Average supply current in fast page mode

I

CC3

30

mA

1, 2

Average supply current in CAS before RAS refresh cycle

I

CC4

35

mA

1, 2, 3

Average supply current in RAS only refresh cycle

I

CC5

35

mA

1, 2, 3

Input leakage current

0 V

V

IN

4.8 V

0 V except on test pins

I

LI

≠10

10

µ

A

Output leakage current

0 V

V

OUT

4.8 V

Output in high-impedance state

I

LO

≠10

10

µ

A

Output `High' Voltage

I

OUT

= ≠ 2 0 0

µ

A

V

OH

2.15

V

Output `Low' Voltage

I

OUT

= 1 mA

V

OL

0.4

V

NOTES:

1.

Specified values are with outputs open.

2.

I

CC1

, I

CC3

, I

CC4

, and I

CC5

depend on cycle time.

3.

Cycle time is 190 ns. Address transition is once at RAS = V

IH

and once at RAS = V

IL

.

LH6V4256

CMOS 1M (256K

◊

4) Dynamic RAM

2-18