| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 74V1G125 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

74V1G125

SINGLE BUS BUFFER (3-STATE)

October 1999

s

HIGH SPEED: t

PD

= 3.8 ns (TYP.) at V

CC

= 5V

s

LOW POWER DISSIPATION:

I

CC

= 1

µ

A (MAX.) at T

A

= 25

o

C

s

HIGH NOISE IMMUNITY:

V

NIH

= V

NIL

= 28% V

CC

(MIN.)

s

POWER DOWN PROTECTION ON INPUTS

s

SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = I

OL

= 8 mA (MIN)

s

BALANCED PROPAGATION DELAYS:

t

PLH

t

PHL

s

OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 2V to 5.5V

s

IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The 74V1G125 is an advanced high-speed

CMOS SINGLE BUS BUFFER fabricated with

sub-micron silicon gate and double-layer metal

wiring C

2

MOS technology.

3-STATE control input G has to be set high to

place the output into the high impedance state.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage. This device can be

used to interface 5V to 3V.

PIN CONNECTION AND IEC LOGIC SYMBOLS

Æ

S

(SOT23-5L)

C

(SC-70)

ORDER CODE:

74V1G125S

1/8

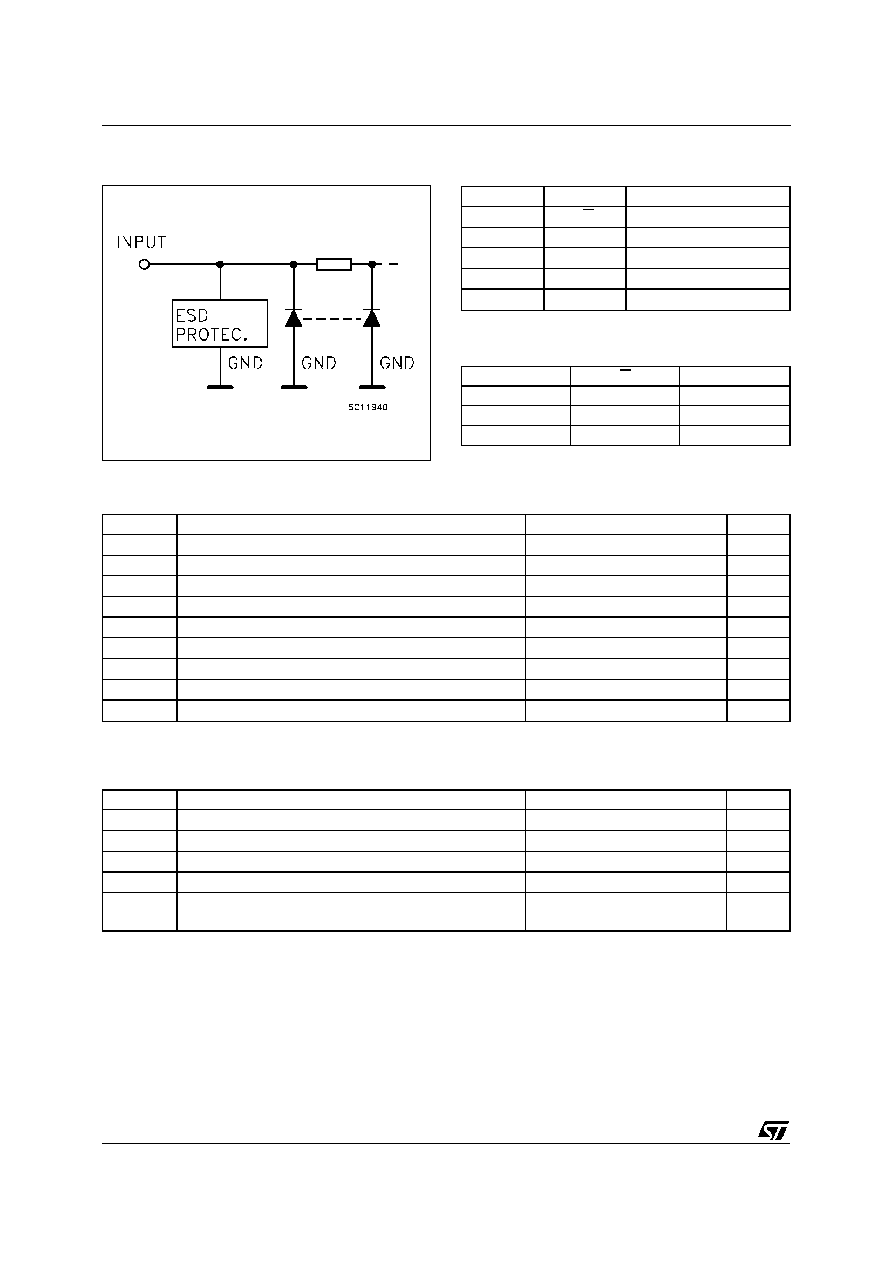

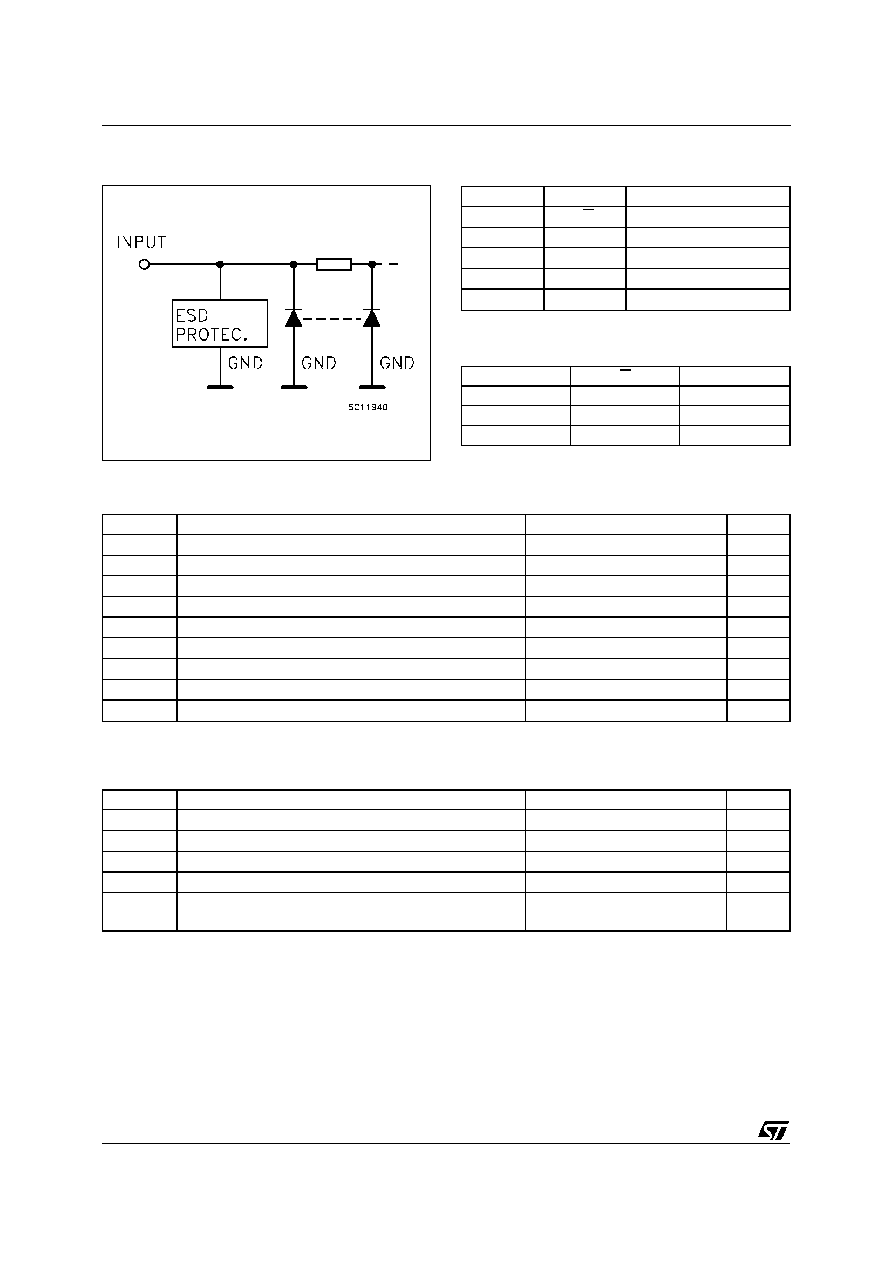

INPUT EQUIVALENT CIRCUIT

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Val ue

Unit

V

CC

Supply Voltage

-0.5 to +7.0

V

V

I

DC Input Voltage

-0.5 to +7.0

V

V

O

DC Output Voltage

-0.5 to V

CC

+ 0.5

V

I

IK

DC Input Diode Current

- 20

mA

I

OK

DC Output Diode Current

±

20

mA

I

O

DC Output Current

±

25

mA

I

CC

or I

GND

DC V

CC

or Ground Current

±

50

mA

T

stg

Storage Temperature

-65 to +150

o

C

T

L

Lead Temperature (10 sec)

260

o

C

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

TRUTH TABLE

A

G

Y

X

H

Z

L

L

L

H

L

H

X:"H" or "L" Z:High Impadance

PIN DESCRIPTION

PI N No

SYMBOL

NAME AND FUNCT ION

1

1G

Output Enable Input

2

1A

Data Input

4

1Y

Data Output

3

GND

Ground (0V)

5

V

CC

Positive Supply Voltage

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Valu e

Uni t

V

CC

Supply Voltage

2.0 to 5.5

V

V

I

Input Voltage

0 to 5.5

V

V

O

Output Voltage

0 to V

CC

V

T

op

Operating Temperature

-40 to +85

o

C

dt/dv

Input Rise and Fall Time (see note 1) (V

CC

= 3.3

±

0.3V)

(V

CC

= 5.0

±

0.5V)

0 to 100

0 to 20

ns/V

ns/V

1) V

IN

from 30% to70%of V

CC

74V1G125

2/8

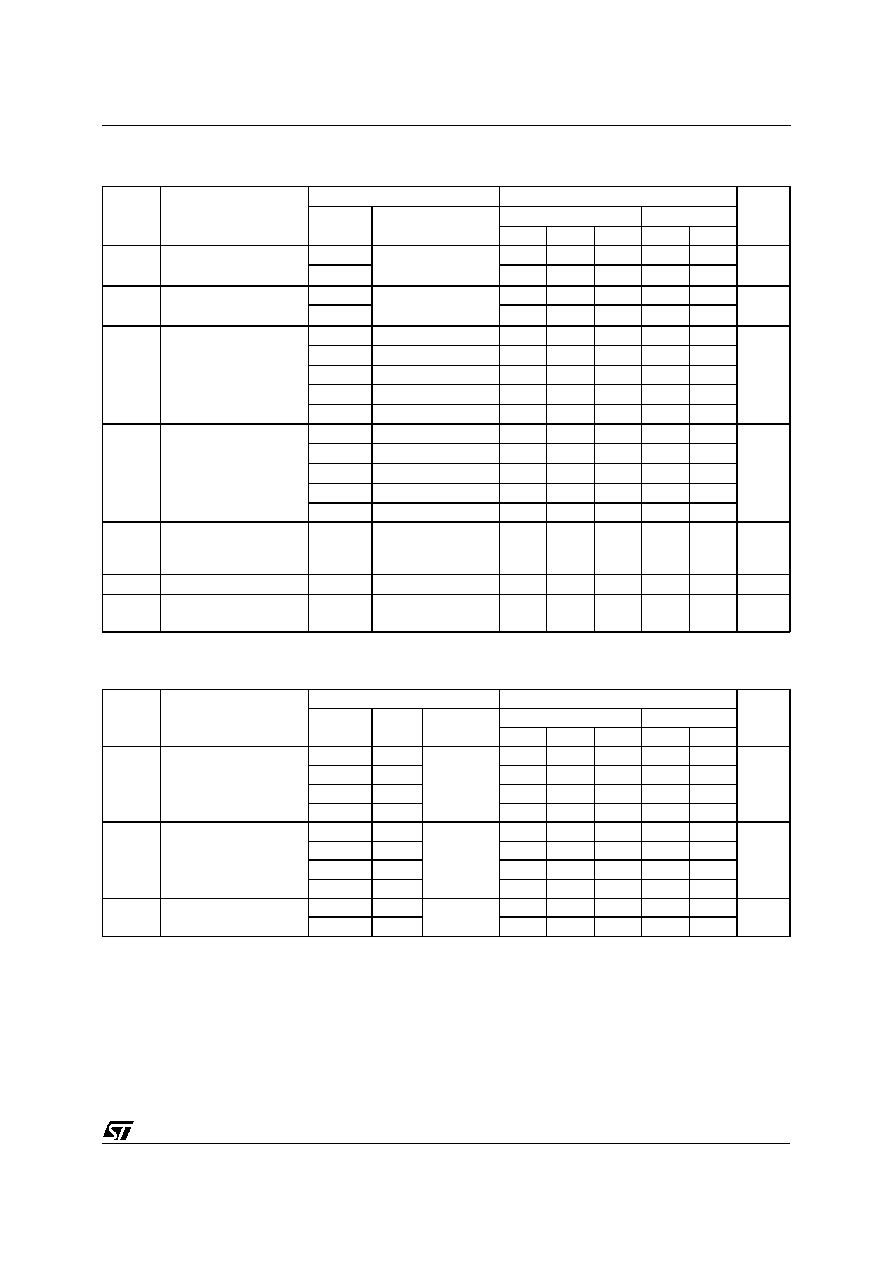

DC SPECIFICATIONS

Symb ol

Parameter

T est Cond ition s

Val ue

Un it

V

CC

(V)

T

A

= 25

o

C

-40 to 85

o

C

Min.

Typ .

Max.

Min .

Max.

V

IH

High Level Input

Voltage

2.0

1.5

1.5

V

3.0 to 5.5

0.7V

CC

0.7V

CC

V

IL

Low Level Input

Voltage

2.0

0.5

0.5

V

3.0 to 5.5

0.3V

CC

0.3V

CC

V

OH

High Level Output

Voltage

2.0

I

O

=-50

µ

A

1.9

2.0

1.9

V

3.0

I

O

=-50

µ

A

2.9

3.0

2.9

4.5

I

O

=-50

µ

A

4.4

4.5

4.4

3.0

I

O

=-4 mA

2.58

2.48

4.5

I

O

=-8 mA

3.94

3.8

V

OL

Low Level Output

Voltage

2.0

I

O

=50

µ

A

0.0

0.1

0.1

V

3.0

I

O

=50

µ

A

0.0

0.1

0.1

4.5

I

O

=50

µ

A

0.0

0.1

0.1

3.0

I

O

=4 mA

0.36

0.44

4.5

I

O

=8 mA

0.36

0.44

I

OZ

High Impedance

Output Leakage

Current

5.5

V

I

= V

IH

or V

IL

V

O

= V

CC

or GND

±

0.25

±

2.5

µ

A

I

I

Input Leakage Current

0 to 5.5

V

I

= 5.5V or GND

±

0.1

±

1.0

µ

A

I

CC

Quiescent Supply

Current

5.5

V

I

= V

CC

or GND

1

10

µ

A

AC ELECTRICAL CHARACTERISTICS (Input t

r

= t

f

=3 ns)

Symb ol

Parameter

Test Co nditi on

Val ue

Un it

V

CC

(V)

C

L

(pF )

T

A

= 25

o

C

-40 to 85

o

C

Min.

Typ .

Max.

Min .

Max.

t

PLH

t

PHL

Propagation Delay

Time

3.3

(*)

15

5.6

8.0

1.0

9.5

ns

3.3

(*)

50

8.1

11.5

1.0

13.0

5.0

(**)

15

3.8

5.5

1.0

6.5

5.0

(**)

50

5.3

7.5

1.0

8.5

t

PLZ

t

PHZ

Output Disable Time

3.3

(*)

15

R

L

= 1K

5.4

8.0

1.0

9.5

ns

3.3

(*)

50

7.9

11.5

1.0

13.0

5.0

(**)

15

3.6

5.0

1.0

6.0

5.0

(**)

50

5.1

7.0

1.0

8.0

t

PZL

t

PZH

Output Enable Time

3.3

(*)

50

R

L

= 1K

9.5

13.0

1.0

15.0

ns

5.0

(**)

50

6.1

8.5

1.0

10.0

(*) Voltage range is 3.3V

±

0.3V

(**) Voltage range is 5V

±

0.5V

74V1G125

3/8

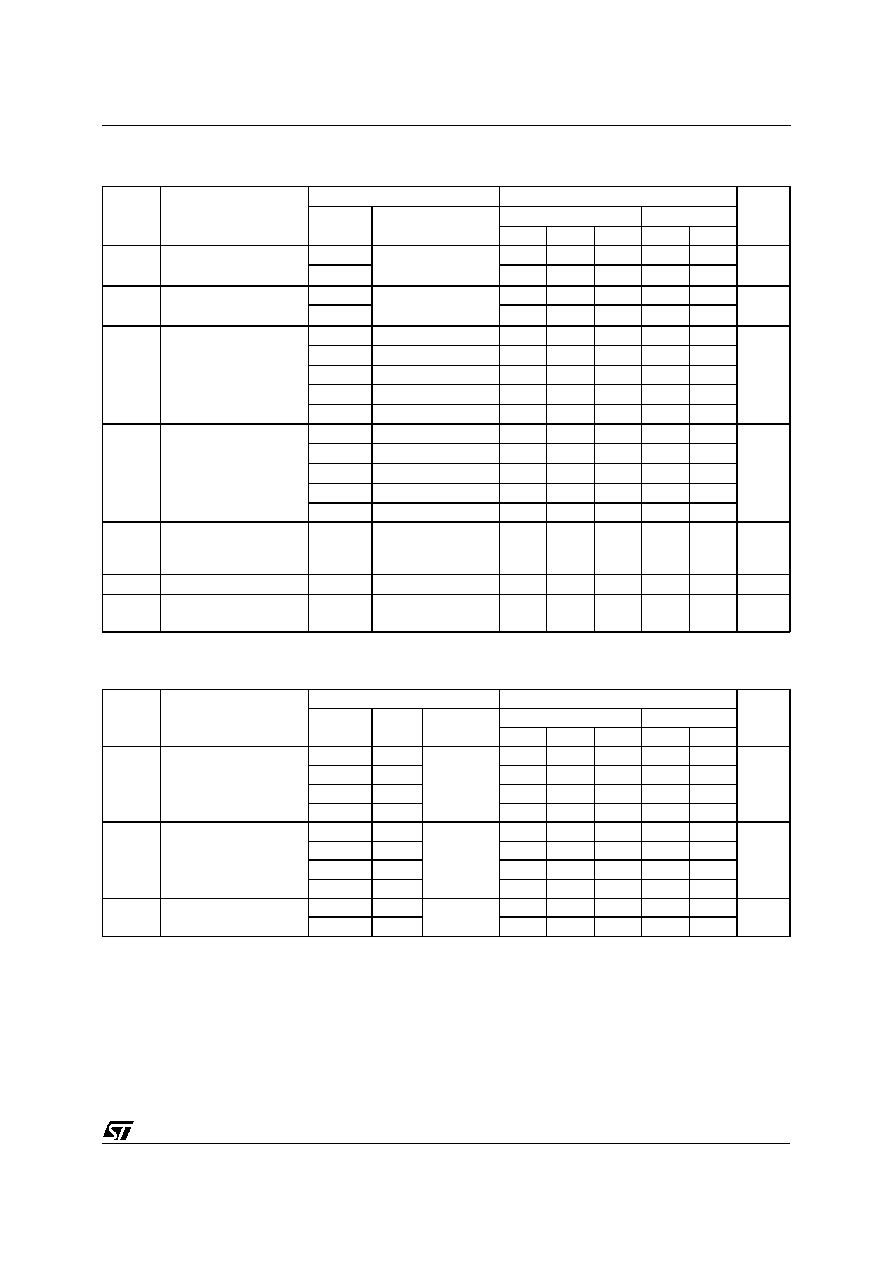

CAPACITIVE CHARACTERISTICS

Symb ol

Parameter

Test Co nditi ons

Valu e

Un it

T

A

= 25

o

C

-40 to 85

o

C

Min.

T yp.

Max.

Mi n.

Max.

C

IN

Input Capacitance

4

pF

C

OUT

Output Capacitance

6

10

10

pF

C

PD

Power Dissipation

Capacitance (note 1)

14

pF

1) C

PD

isdefined as the value of the IC'sinternal equivalent capacitance which is calculated fromthe operating current consumption without load. (Referto

Test Circuit).Average operting current can be obtained by the following equation. I

CC

(opr) = C

PD

∑

V

CC

∑

f

IN

+ I

CC

TEST CIRCUIT

T EST

SW IT CH

t

PLH

, t

PHL

Open

t

PZL

, t

PLZ

V

CC

t

PZH

, t

PHZ

GND

C

L

= 15/50 pF or equivalent (includes jig and probe capacitance)

R

L

= R

1

= 1K

orequivalent

R

T

= Z

OUT

of pulse generator (typically 50

)

74V1G125

4/8

WAVEFORM 1: PROPAGATION DELAYS (f=1MHz; 50% duty cycle)

WAVEFORM 2: OUTPUT ENABLE AND DISABLE TIME (f=1MHz; 50% duty cycle)

74V1G125

5/8