M54HC4024

M74HC4024

October 1992

7 STAGE BINARY COUNTER

B1R

(Plastic Package)

ORDER CODES :

M54HC4024F1R

M74HC4024M1R

M74HC4024B1R

M74HC4024C1R

F1R

(Ceramic Package)

M1R

(Micro Package)

C1R

(Chip Carrier)

PIN CONNECTIONS (top view)

NC =

No Internal

Connection

DESCRIPTION

.

HIGH SPEED

t

PD

= 13 ns (TYP.) AT V

CC

= 5 V

.

LOW POWER DISSIPATION

I

CC

= 4

µ

A (MAX.) AT T

A

= 25

∞

C

.

HIGH NOISE IMMUNITY

V

NIH

= V

NIL

= 28 % V

CC

(MIN.)

.

OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.

SYMMETRICAL OUTPUT IMPEDANCE

|I

OH

|= I

OL

= 4 mA (MIN.)

.

BALANCED PROPAGATION DELAYS

t

PLH

= t

PHL

.

WIDE OPERATING VOLTAGE RANGE

V

CC

(OPR) = 2 V TO 6 V

.

PIN AND FUNCTION COMPATIBLE

WITH 4024B

The M54/74HC4024 is a high speed CMOS 7-

STAGE BINARY COUNTER fabricated in silicon

gate C

2

MOS technology. It has the same high

speed performance of LSTTL combined with true

CMOS low power consumption. The HC4024 is a 7

stage Counter. This devices is incremented on the

falling edge (negative transition) of the input clock,

and all its outputs are reset to a low level by applying

a logical high on their reset input. All inputs are

equipped with protection circuits against static dis-

charge and transient excess voltage.

1/11

INPUT AND OUTPUT EQUIVALENT CIRCUIT

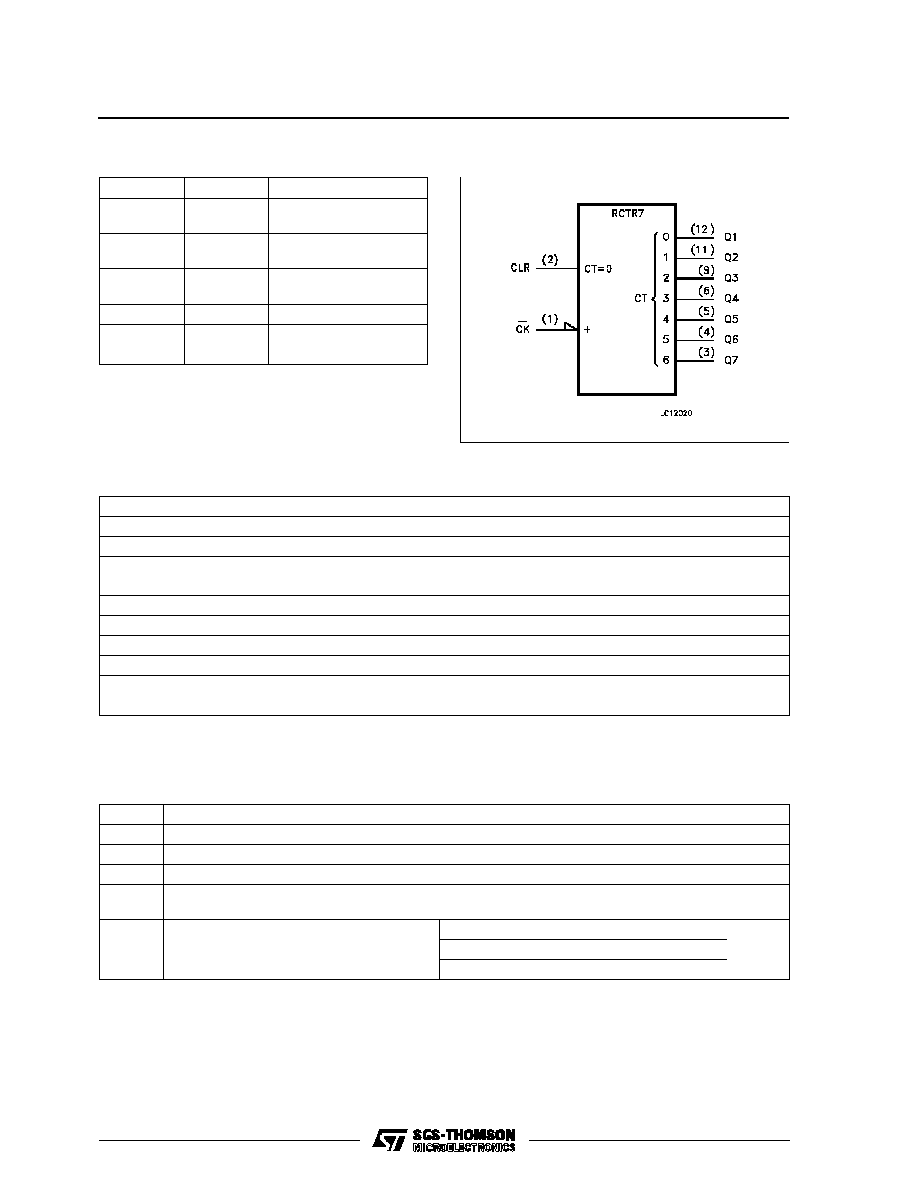

TRUTH TABLE

CLOCK

CLEAR

OUTPUT STATE

X

H

ALL OUTPUTS = "L"

L

NO CHANGE

L

ADVANCE TO NEXT STATE

X: DON'T CARE

LOGIC DIAGRAM

M54/M74HC4024

2/11

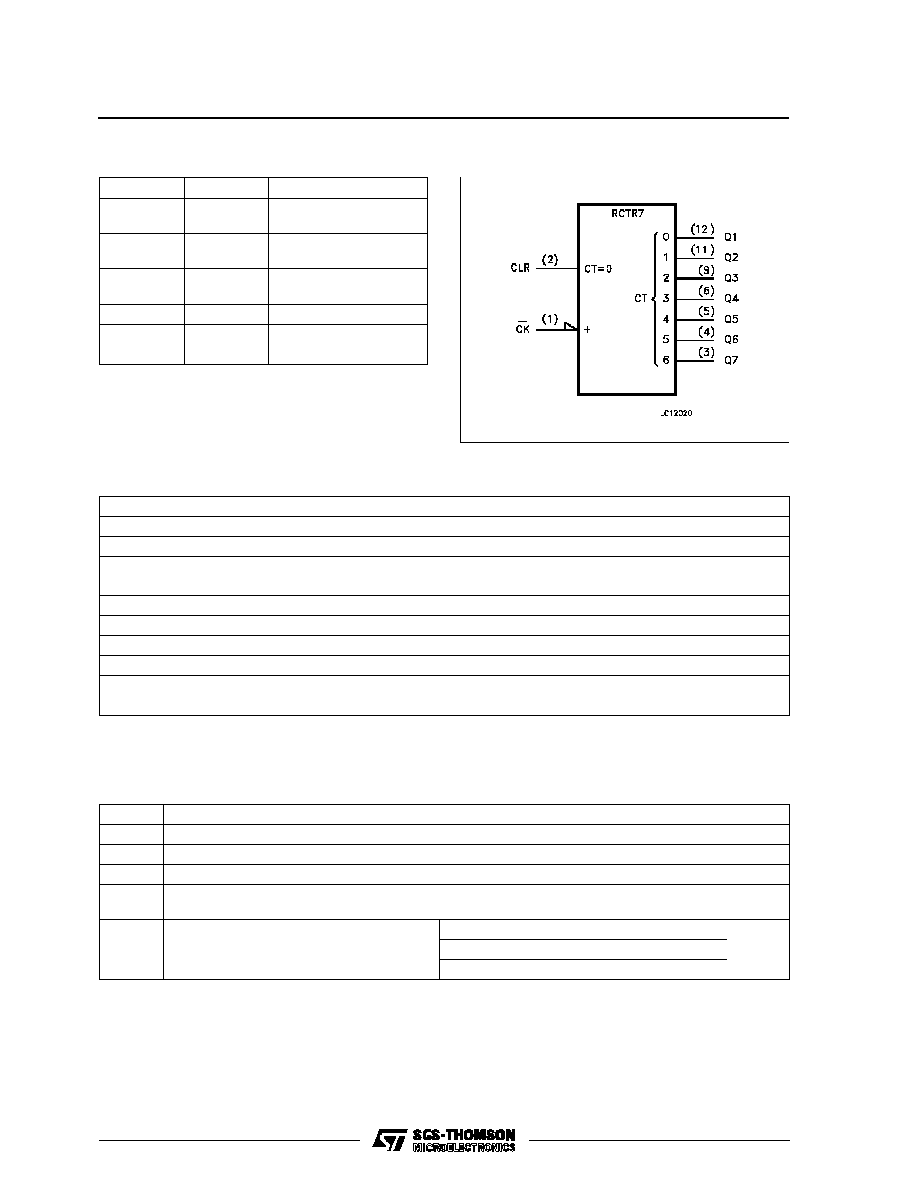

PIN DESCRIPTION

PIN No

SYMBOL

NAME AND FUNCTION

1

CLOCK

Clock Input (HIGH to

LOW, Edge-triggered)

2

RESET

Reset Input (Active

HIGH)

12, 11, 9, 6,

5, 4, 3

Q1 to Q7

Parallel Outputs

8, 10, 13

NC

Not Connected

7

GND

Ground (0V)

14

V

CC

Positive Supply Voltage

IEC LOGIC SYMBOL

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

CC

Supply Voltage

-0.5 to +7

V

V

I

DC Input Voltage

-0.5 to V

CC

+ 0.5

V

V

O

DC Output Voltage

-0.5 to V

CC

+ 0.5

V

I

IK

DC Input Diode Current

±

20

mA

I

OK

DC Output Diode Current

±

20

mA

I

O

DC Output Source Sink Current Per Output Pin

±

25

mA

I

CC

or I

GND

DC V

CC

or Ground Current

±

50

mA

P

D

Power Dissipation

500 (*)

mW

T

stg

Storage Temperature

-65 to +150

o

C

T

L

Lead Temperature (10 sec)

300

o

C

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

(*) 500 mW:

65

o

C derate to 300 mW by 10mW/

o

C: 65

o

C to 85

o

C

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Value

Unit

V

CC

Supply Voltage

2 to 6

V

V

I

Input Voltage

0 to V

CC

V

V

O

Output Voltage

0 to V

CC

V

T

op

Operating Temperature: M54HC Series

M74HC Series

-55 to +125

-40 to +85

o

C

o

C

t

r

, t

f

Input Rise and Fall Time

V

CC

= 2 V

0 to 1000

ns

V

CC

= 4.5 V

0 to 500

V

CC

= 6 V

0 to 400

M54/ M74HC4024

3/11

DC SPECIFICATIONS

Symbol

Parameter

Test Conditions

Value

Unit

V

CC

(V)

T

A

= 25

o

C

54HC and 74HC

-40 to 85

o

C

74HC

-55 to 125

o

C

54HC

Min.

Typ.

Max.

Min.

Max.

Min.

Max.

V

IH

High Level Input

Voltage

2.0

1.5

1.5

1.5

V

4.5

3.15

3.15

3.15

6.0

4.2

4.2

4.2

V

IL

Low Level Input

Voltage

2.0

0.5

0.5

0.5

V

4.5

1.35

1.35

1.35

6.0

1.8

1.8

1.8

V

OH

High Level

Output Voltage

2.0

V

I

=

V

IH

or

V

IL

I

O

=-20

µ

A

1.9

2.0

1.9

1.9

V

4.5

4.4

4.5

4.4

4.4

6.0

5.9

6.0

5.9

5.9

4.5

I

O

=-4.0 mA

4.18

4.31

4.13

4.10

6.0

I

O

=-5.2 mA

5.68

5.8

5.63

5.60

V

OL

Low Level Output

Voltage

2.0

V

I

=

V

IH

or

V

IL

I

O

= 20

µ

A

0.0

0.1

0.1

0.1

V

4.5

0.0

0.1

0.1

0.1

6.0

0.0

0.1

0.1

0.1

4.5

I

O

= 4.0 mA

0.17

0.26

0.33

0.40

6.0

I

O

= 5.2 mA

0.18

0.26

0.33

0.40

I

I

Input Leakage

Current

6.0

V

I

= V

CC

or GND

±

0.1

±

1

±

1

µ

A

I

CC

Quiescent Supply

Current

6.0

V

I

= V

CC

or GND

4

40

80

µ

A

M54/M74HC4024

4/11

AC ELECTRICAL CHARACTERISTICS (C

L

= 50 pF, Input t

r

= t

f

= 6 ns)

Symbol

Parameter

Test Conditions

Value

Unit

V

CC

(V)

T

A

= 25

o

C

54HC and 74HC

-40 to 85

o

C

74HC

-55 to 125

o

C

54HC

Min.

Typ.

Max.

Min.

Max.

Min.

Max.

t

TLH

t

THL

Output Transition

Time

2.0

30

75

95

110

ns

4.5

8

15

19

22

6.0

7

13

16

19

t

PLH

t

PHL

Propagation

Delay Time

(Qn - Qn + 1)

2.0

24

60

75

90

ns

4.5

6

12

15

18

6.0

5

10

13

15

t

PLH

t

PHL

Propagation

Delay Time

Clock - Q1

2.0

60

120

150

180

ns

4.5

15

24

30

36

6.0

13

20

26

31

t

PHL

Propagation

Delay Time

(CLEAR - Qn)

2.0

60

120

150

180

ns

4.5

15

24

30

36

6.0

13

20

26

31

f

MAX

Maximum Clock

Frequency

2.0

8

17

7

5.6

ns

4.5

42

67

34

28

6.0

49

79

40

34

t

W(H)

t

W(L)

Minimum Pulse

Width (CLOCK)

2.0

24

75

95

110

ns

4.5

6

15

19

22

6.0

5

13

16

19

t

W(H)

Minimum Pulse

Width (CLEAR)

2.0

32

75

95

110

ns

4.5

8

15

19

22

6.0

7

13

16

19

t

REM

Minimum

Removal Time

2.0

25

30

40

ns

4.5

5

6

8

6.0

5

5

7

C

IN

Input Capacitance

5

10

10

10

pF

C

PD

(*)

Power Dissipation

Capacitance

34

pF

(*) C

PD

is defined as the value of the IC's internal equivalent capacitance which is calculated from the operating current consumption without load.

(Refer to Test Circuit). Average operting current can be obtained by the following equation. I

CC

(opr) = C

PD

∑

V

CC

∑

f

IN

+ I

CC

M54/ M74HC4024

5/11