1/12

July 2001

s

HIGH SPEED:

t

PD

= 13ns (TYP.) at V

CC

= 6V

s

LOW POWER DISSIPATION:

I

CC

= 4

µ

A(MAX.) at T

A

=25∞C

s

HIGH NOISE IMMUNITY:

V

NIH

= V

NIL

= 28 % V

CC

(MIN.)

s

SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = I

OL

= 6mA (MIN)

s

BALANCED PROPAGATION DELAYS:

t

PLH

t

PHL

s

WIDE OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 2V to 6V

s

PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 573

DESCRIPTION

The M74HC573 is an high speed CMOS OCTAL

LATCH WITH 3-STATE OUTPUTS fabricated

with silicon gate C

2

MOS technology.

This 8-BIT D-Type latches is controlled by a latch

enable input (LE) and output enable input (OE).

While the LE input is held at a high level, the Q

outputs will follow the data input precisely. When

LE is taken low, the Q outputs will be latched

precisely at the logic level of D input data.

While the OE input is at low level, the eight outputs

will be in a normal logic state (high or low logic

level) and while is at high level the outputs will be

in a high impedance state.

The 3-State output configuration and the wide

choice of outline make bus organized system

simple.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

M74HC573

OCTAL D-TYPE LATCH

WITH 3 STATE OUTPUT NON INVERTING

PIN CONNECTION AND IEC LOGIC SYMBOLS

ORDER CODES

PACKAGE

TUBE

T & R

DIP

M74HC573B1R

SOP

M74HC573M1R

M74HC573RM13TR

TSSOP

M74HC573TTR

TSSOP

DIP

SOP

M74HC573

2/12

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

TRUTH TABLE

X: Don't Care

Z: High Impedance

(*): Q Outputs are latched at the time when the LE input is taken low logic level.

LOGIC DIAGRAM

PIN No

SYMBOL

NAME AND FUNCTION

1

OE

3 State Output Enable

Input (Active LOW)

2, 3, 4, 5, 6,

7, 8, 9

D0 to D7

Data Inputs

12, 13, 14,

15, 16, 17,

18, 19

Q0 to Q7

3 State Latch Outputs

11

LE

Latch Enable Input

10

GND

Ground (0V)

20

V

CC

Positive Supply Voltage

INPUTS

OUTPUTS

OE

LE

D

Q

H

X

X

Z

L

L

X

NO CHANGE (*)

L

H

L

L

L

H

H

H

M74HC573

3/12

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied

(*) 500mW at 65

∞

C; derate to 300mW by 10mW/

∞

C from 65

∞

C to 85

∞

C

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Value

Unit

V

CC

Supply Voltage

-0.5 to +7

V

V

I

DC Input Voltage

-0.5 to V

CC

+ 0.5

V

V

O

DC Output Voltage

-0.5 to V

CC

+ 0.5

V

I

IK

DC Input Diode Current

±

20

mA

I

OK

DC Output Diode Current

±

20

mA

I

O

DC Output Current

±

35

mA

I

CC

or I

GND

DC V

CC

or Ground Current

±

70

mA

P

D

Power Dissipation

500(*)

mW

T

stg

Storage Temperature

-65 to +150

∞C

T

L

Lead Temperature (10 sec)

300

∞C

Symbol

Parameter

Value

Unit

V

CC

Supply Voltage

2 to 6

V

V

I

Input Voltage

0 to V

CC

V

V

O

Output Voltage

0 to V

CC

V

T

op

Operating Temperature

-55 to 125

∞C

t

r

, t

f

Input Rise and Fall Time

V

CC

= 2.0V

0 to 1000

ns

V

CC

= 4.5V

0 to 500

ns

V

CC

= 6.0V

0 to 400

ns

M74HC573

5/12

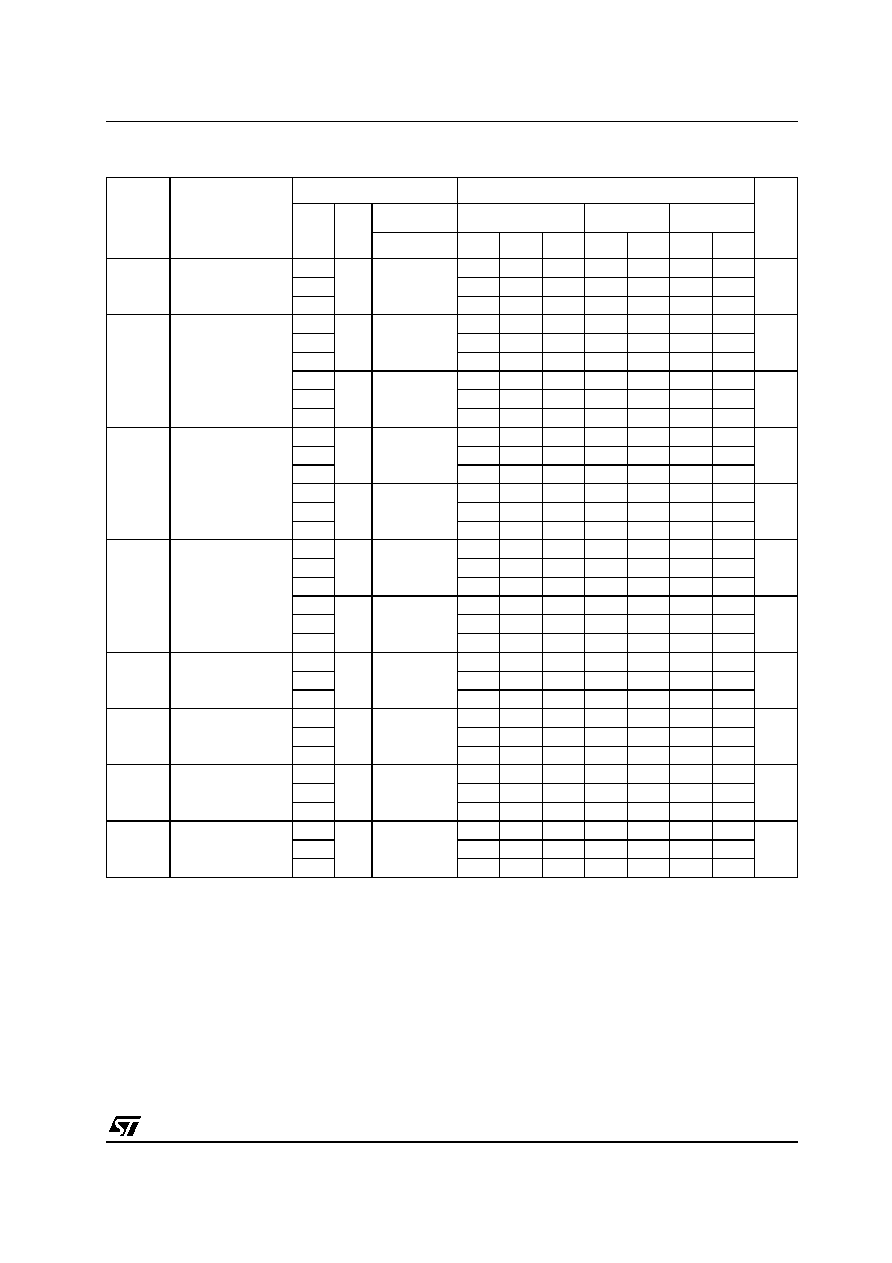

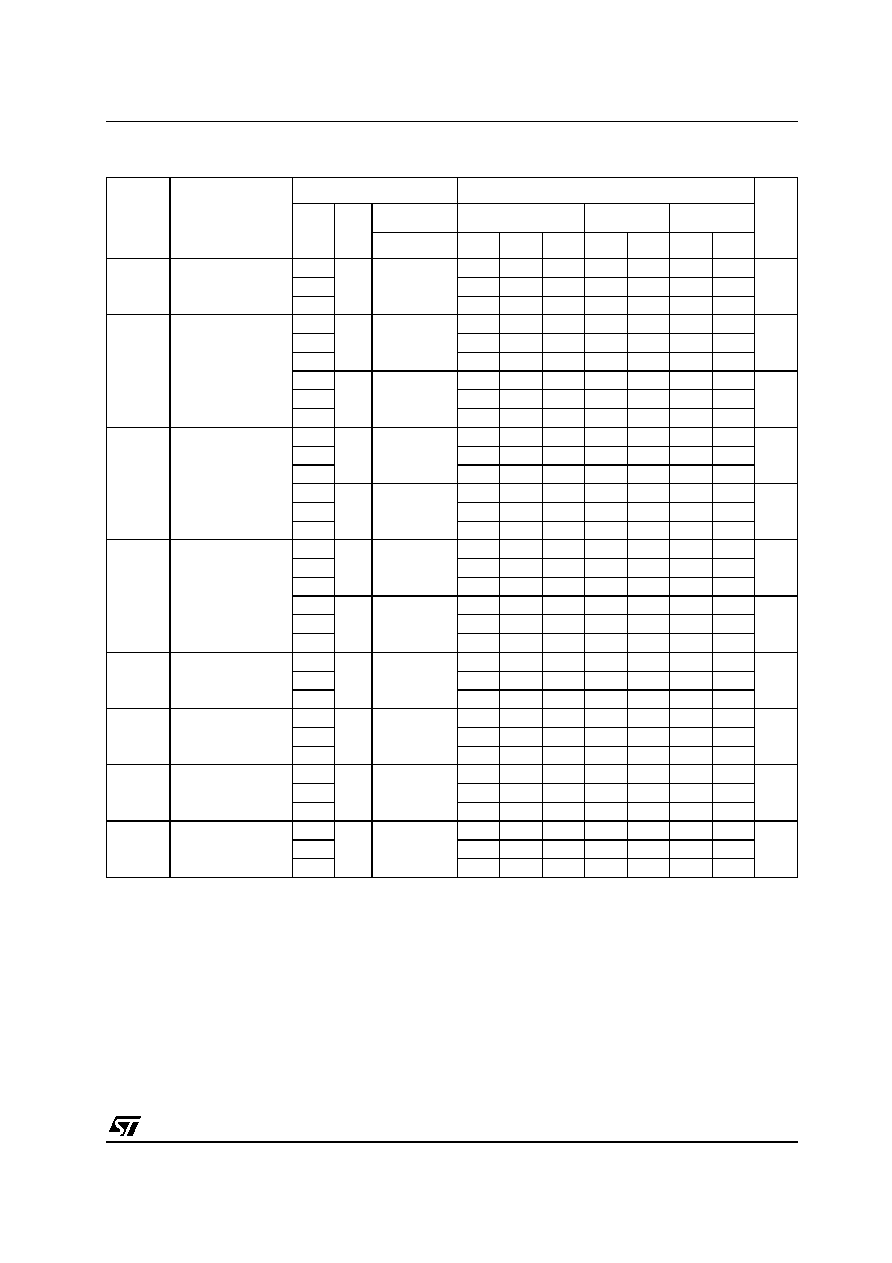

AC ELECTRICAL CHARACTERISTICS (C

L

= 50 pF, Input t

r

= t

f

= 6ns)

Symbol

Parameter

Test Condition

Value

Unit

V

CC

(V)

C

L

(pF)

T

A

= 25∞C

-40 to 85∞C

-55 to 125∞C

Min.

Typ.

Max.

Min.

Max.

Min.

Max.

t

TLH

t

THL

Output Transition

Time

2.0

50

25

60

75

90

ns

4.5

7

12

15

18

6.0

6

10

13

15

t

PLH

t

PHL

Propagation Delay

Time

(LE - Q)

2.0

50

50

115

145

175

ns

4.5

15

23

29

35

6.0

13

20

25

30

2.0

150

60

155

195

235

ns

4.5

20

31

39

47

6.0

17

26

33

40

t

PLH

t

PHL

Propagation Delay

Time

(D - Q)

2.0

50

42

110

140

165

ns

4.5

14

22

28

33

6.0

12

19

24

28

2.0

150

57

150

190

225

ns

4.5

19

30

38

45

6.0

16

26

32

38

t

PZL

t

PZH

High Impedance

Output Enable

Time

2.0

50

R

L

= 1 K

55

140

175

210

ns

4.5

17

28

35

42

6.0

14

24

30

36

2.0

150

R

L

= 1 K

66

180

225

270

ns

4.5

22

36

45

54

6.0

19

31

38

46

t

PLZ

t

PHZ

High Impedance

Output Disable

Time

2.0

50

R

L

= 1 K

40

125

155

190

ns

4.5

17

25

31

38

6.0

15

21

26

32

t

W(L)

t

W(H)

Minimum Pulse

Width

2.0

50

40

75

95

110

ns

4.5

8

15

19

22

6.0

7

13

16

19

t

s

Minimum Set-up

Time

2.0

50

16

50

65

75

ns

4.5

5

10

13

15

6.0

3

9

11

13

t

h

Minimum Hold

Time

2.0

50

5

5

5

ns

4.5

5

5

5

6.0

5

5

5