Document Outline

- FEATURES SUMMARY

- SUMMARY DESCRIPTION

- MEMORY ARRAY ORGANIZATION

- SIGNAL DESCRIPTIONS

- BUS OPERATIONS

- COMMAND SET

- DEVICE OPERATIONS

- DATA PROTECTION

- SOFTWARE ALGORITHMS

- PROGRAM AND ERASE TIMES AND ENDURANCE CYCLES

- MAXIMUM RATING

- DC AND AC PARAMETERS

- PACKAGE MECHANICAL

- Figure 38. TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20 mm, Package Outline

- Table 26. TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20 mm, Package Mechanical Data

- Figure 39. VFBGA63 9.5x12mm - 6x8 active ball array, 0.80mm pitch, Package Outline

- Table 27. VFBGA63 9.5x12mm - 6x8 active ball array, 0.80mm pitch, Package Mechanical Data

- Figure 40. TFBGA63 9.5x12mm - 6x8 active ball array, 0.80mm pitch, Package Outline

- Table 28. TFBGA63 9.5x12mm - 6x8 active ball array, 0.80mm pitch, Package Mechanical Data

- PART NUMBERING

- REVISION HISTORY

1/57

PRELIMINARY DATA

October 2005

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

NAND01G-B, NAND02G-B,

NAND04G-B, NAND08G-B

1 Gbit, 2 Gbit, 4 Gbit, 8 Gbit

2112 Byte/1056 Word Page, 1.8V/3V, NAND Flash Memory

FEATURES SUMMARY

HIGH DENSITY NAND FLASH MEMORIES

�

Up to 8 Gbit memory array

�

Up to 64Mbit spare area

�

Cost effective solutions for mass storage

applications

NAND INTERFACE

�

x8 or x16 bus width

�

Multiplexed Address/ Data

�

Pinout compatibility for all densities

SUPPLY VOLTAGE

�

1.8V device: V

DD

= 1.7 to 1.95V

�

3.0V device: V

DD

= 2.7 to 3.6V

PAGE SIZE

�

x8 device: (2048 + 64 spare) Bytes

�

x16 device: (1024 + 32 spare) Words

BLOCK SIZE

�

x8 device: (128K + 4K spare) Bytes

�

x16 device: (64K + 2K spare) Words

PAGE READ / PROGRAM

�

Random access: 25�s (max)

�

Sequential access: 50ns (min)

�

Page program time: 300�s (typ)

COPY BACK PROGRAM MODE

�

Fast page copy without external buffering

CACHE PROGRAM AND CACHE READ

MODES

�

Internal Cache Register to improve the

program and read throughputs

FAST BLOCK ERASE

�

Block erase time: 2ms (typ)

STATUS REGISTER

ELECTRONIC SIGNATURE

CHIP ENABLE `DON'T CARE'

�

for simple interface with microcontroller

SERIAL NUMBER OPTION

Figure 1. Packages

DATA PROTECTION

�

Hardware and Software Block Locking

�

Hardware Program/Erase locked during

Power transitions

DATA INTEGRITY

�

100,000 Program/Erase cycles

�

10 years Data Retention

RoHS COMPLIANCE

�

Lead-Free Components are Compliant

with the RoHS Directive

DEVELOPMENT TOOLS

�

Error Correction Code software and

hardware models

�

Bad Blocks Management and Wear

Leveling algorithms

�

PC Demo board with simulation software

�

File System OS Native reference software

�

Hardware simulation models

TSOP48 12 x 20mm

VFBGA63 9.5 x 12 x 1mm

TFBGA63 9.5 x 12 x 1.2mm

FBGA

NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

2/57

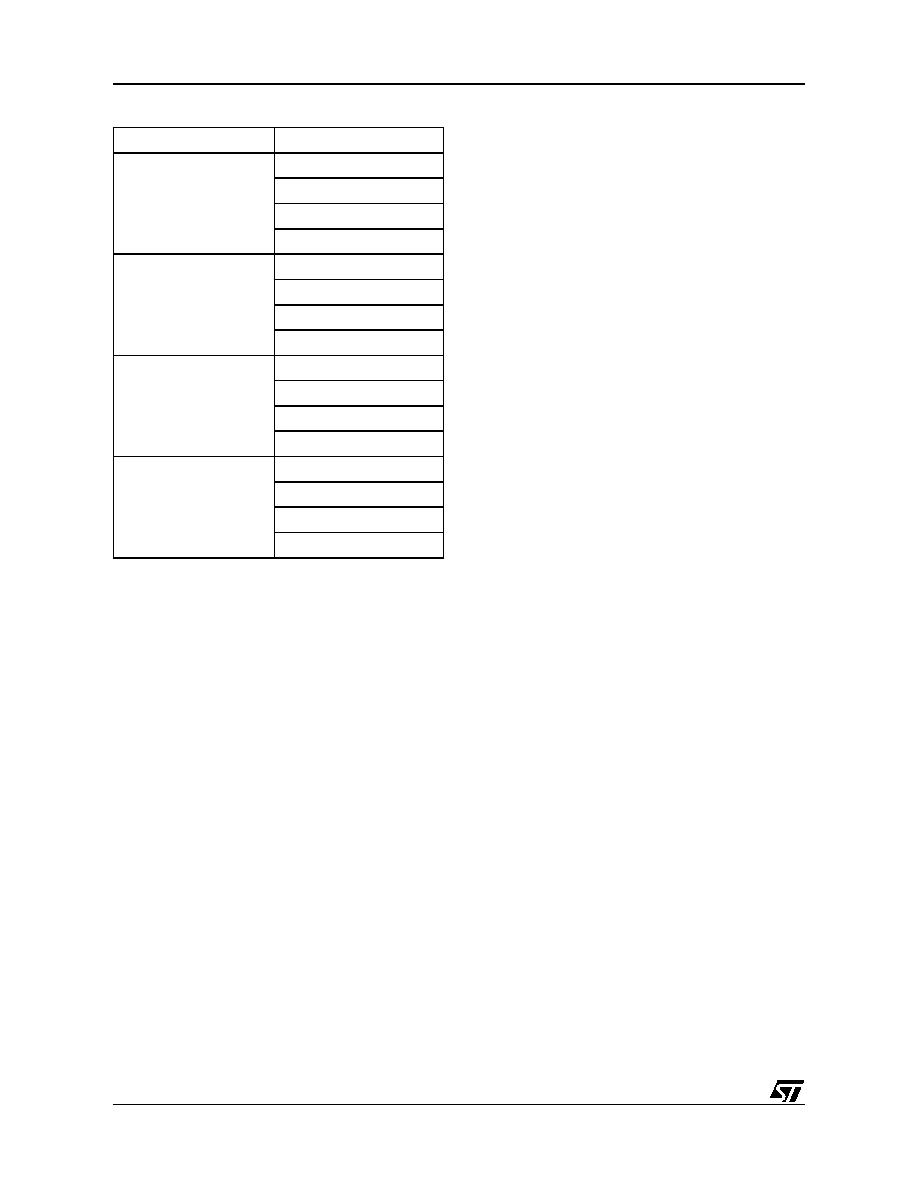

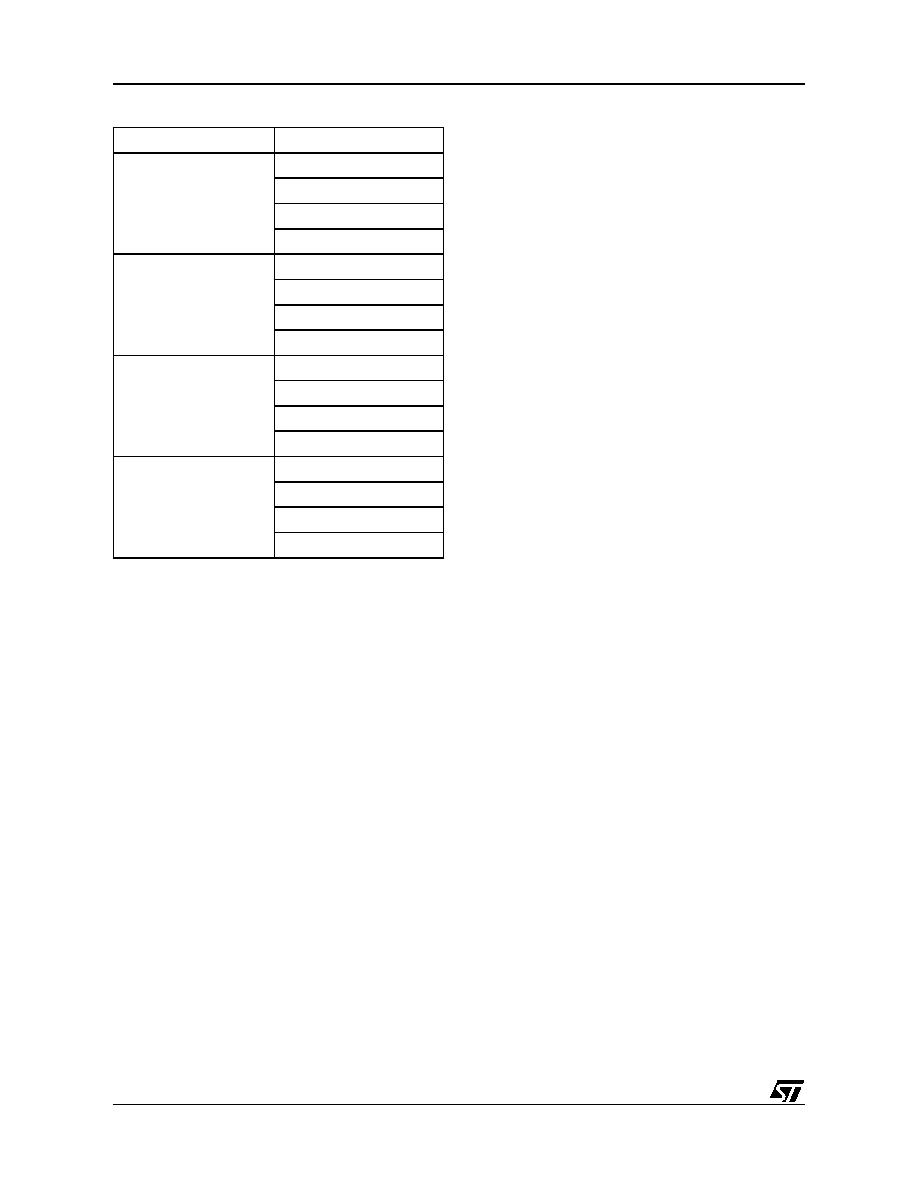

Table 1. Product List

Note: x16 organization only available for MCP

Reference

Part Number

NAND01G-B

NAND01GR3B

NAND01GW3B

NAND01GR4B

NAND01GW4B

NAND02G-B

NAND02GR3B

NAND02GW3B

NAND02GR4B

NAND02GW4B

NAND04G-B

NAND04GR3B

NAND04GW3B

NAND04GR4B

NAND04GW4B

NAND08G-B

NAND08GR3B

NAND08GW3B

NAND08GR4B

NAND08GW4B

3/57

NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 1. Product List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

SUMMARY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. Product Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 2. Logic Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 3. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 3. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 4. TSOP48 Connections, x8 devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 5. FBGA63 Connections, x8 devices (Top view through package) . . . . . . . . . . . . . . . . . . . 11

Figure 6. FBGA63 Connections, x16 devices (Top view through package) . . . . . . . . . . . . . . . . . . 12

MEMORY ARRAY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Bad Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 4. Valid Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. Memory Array Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Inputs/Outputs (I/O0-I/O7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Inputs/Outputs (I/O8-I/O15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Address Latch Enable (AL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Command Latch Enable (CL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Read Enable (R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Power-Up Read Enable, Lock/Unlock Enable (PRL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Write Enable (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Write Protect (WP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Ready/Busy (RB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

V

DD

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

V

SS

Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Command Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Address Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Data Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Data Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Write Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 5. Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 6. Address Insertion, x8 Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 7. Address Insertion, x16 Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 8. Address Definitions, x8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

4/57

Table 9. Address Definitions, x16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

COMMAND SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 10. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

DEVICE OPERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Read Memory Array. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Random Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Page Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 8. Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 9. Random Data Output During Sequential Data Output. . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Cache Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 10.Cache Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Page Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Sequential Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Random Data Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 11.Page Program Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 12.Random Data Input During Sequential Data Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Copy Back Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 11. Copy Back Program x8 Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 12. Copy Back Program x16 Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 13.Copy Back Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 14.Page Copy Back Program with Random Data Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Cache Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 15.Cache Program Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Block Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 16.Block Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Read Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Write Protection Bit (SR7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

P/E/R Controller and Cache Ready/Busy Bit (SR6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

P/E/R Controller Bit (SR5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Cache Program Error Bit (SR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Error Bit (SR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

SR4, SR3 and SR2 are Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 13. Status Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Read Electronic Signature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 14. Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 15. Electronic Signature Byte/Word 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

DATA PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Blocks Lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Blocks Unlock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 17.Blocks Unlock Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Blocks Lock-Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Block Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5/57

NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

Figure 18.Read Block Lock Status Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 16. Block Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 19.Block Protection State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

SOFTWARE ALGORITHMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Bad Block Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Block Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 17. Block Failure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 20.Bad Block Management Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 21.Garbage Collection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Garbage Collection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Wear-leveling Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Error Correction Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 22.Error Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Hardware Simulation Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Behavioral simulation models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

IBIS simulations models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

PROGRAM AND ERASE TIMES AND ENDURANCE CYCLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 18. Program, Erase Times and Program Erase Endurance Cycles . . . . . . . . . . . . . . . . . . . 38

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 19. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 20. Operating and AC Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 21. Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 22. DC Characteristics, 1.8V Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 23.Equivalent Testing Circuit for AC Characteristics Measurement. . . . . . . . . . . . . . . . . . . 40

Table 23. DC Characteristics, 3V Devices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 24. AC Characteristics for Command, Address, Data Input . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 25. AC Characteristics for Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 24.Command Latch AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 25.Address Latch AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 26.Data Input Latch AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 27.Sequential Data Output after Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 28.Read Status Register AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 29.Read Electronic Signature AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 30.Page Read Operation AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 31.Page Program AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 32.Block Erase AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 33.Reset AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Ready/Busy Signal Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 34.Ready/Busy AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 35.Ready/Busy Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 36.Resistor Value Versus Waveform Timings For Ready/Busy Signal . . . . . . . . . . . . . . . . 50