1/8

PRELIMINARY DATA

June 2001

SD56120

RF POWER TRANSISTORS

The

LdmoST FAMILY

N-CHANNEL ENHANCEMENT-MODE LATERAL

MOSFETs

∑ EXCELLENT THERMAL STABILITY

∑ COMMON SOURCE CONFIGURATION,

PUSH-PULL

∑ P

OUT

= 100 W WITH 14 dB GAIN @ 860 MHz

∑ BeO FREE PACKAGE

DESCRIPTION

The SD56120 is a common source N-Channel en-

hancement-mode lateral Field-Effect RF power

transistor designed for broadband commercial and

industrial applications at frequencies up to 1.0 GHz.

The SD56120 is designed for high gain and broad-

band performance operating in common source

mode at 28 V. It is ideal for broadcast applications

from 470 to 860 MHz requiring high linearity.

ABSOLUTE MAXIMUM RATINGS (T

CASE

= 25

∞

C)

Symbol

Parameter

Value

Unit

V

(BR)DSS

Drain-Source Voltage

65

V

V

GS

Gate-Source Voltage

±

20

V

I

D

Drain Current

14

A

P

DISS

Power Dissipation (@ Tc = 70∞C)

217

W

Tj

Max. Operating Junction Temperature

200

∞C

T

STG

Storage Temperature

-65 to +150

∞C

THERMAL DATA

R

th(j-c)

Junction -Case Thermal Resistance

0.6

∞C/W

PIN CONNECTION

1-2 Drain

4-5 Gate

3 Source

1

2

4

5

3

M246

epoxy sealed

ORDER CODE

SD56120

BRANDING

TSD56120

5/8

SD56120

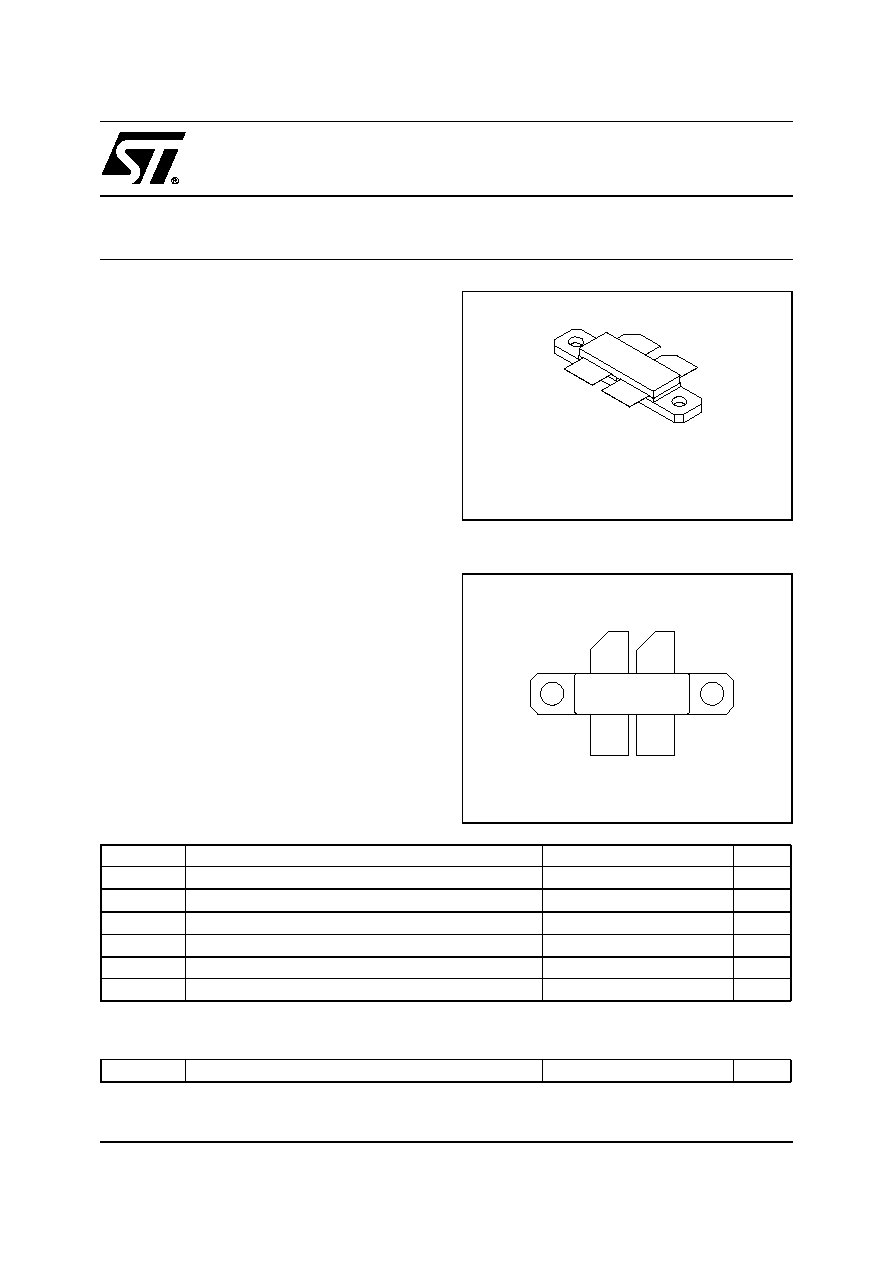

860 MHz TEST CIRCUIT SCHEMATIC

860 MHz TEST CIRCUIT COMPONENT PART LIST

COMPONENT

DESCRIPTION

C32

.6 - 4.5 pF VARIABLE CAPACITOR

C31, C28

.01

µ

F ATC 200B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C29, C30

62 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C27, C22

270 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C26, C21

1200 pF ATC 700B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C25 ,C20

0.1

µ

F 500V SURFACE MOUNT CERAMIC CHIP CAPACITOR

C24, C19, C17, C16

10

µ

F 50V ALUMINUM ELECTROLYTIC RADIAL LEAD SURFACE MOUNT

CAPACITOR

C23, C18

100

µ

F 63V ALUMINUM ELECTROLYTIC RADIAL LEAD CAPACITOR

C15, C14, C13, C12

47 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C11

0.8 - 8 pF GIGATRIM VARIABLE CAPACITOR

C10

3.0 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C9, C8

4.3 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C7, C6, C5

10 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C4

2.0 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C3, C2

20 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

C1

1.3 pF ATC 100B SURFACE MOUNT CERAMIC CHIP CAPACITOR

R7, R8

100 OHM 1/4 W SURFACE MOUNT CHIP RESISTOR

R6, R3

22 OHM 1/4 W CARBON LEADED RESISTOR

R5, R2

4.7 OHM 1/4 W CARBON LEADED RESISTOR

R4, R1

82 OHM 1/4 W CARBON LEADED RESISTOR

B2, B1

BALUN, 50 OHM SUCOFORM, OD 0.141 2.37 LG COAXIAL CABLE OR

EQUIVALENT

L2, L1

INDUCTOR, 6 TURN AIR-WOUND #18AWG ID=0.130[3,30] MAGNET WIRE

FB2, FB1

SURFACE MOUNT EMI SHIELD BEAD

PCB

ULTRALAM 2000. 0.030" THK

r = 2.55, 2 Oz ED CU BOTH SIDES

C18

C19

C20

C21

C7

BALUN1

+

VGG

INPUT

RF

C2

C3

R1

R1

R3

VDD

OUTPUT

L2

C26

FB2

C25

C24

C23

C5

D.U.T.

C9

C8

C10

C22

C6

L1

C15

C11

RF

BALUN2

C12

+

VGG

VDD

FB1

C4

C1

C17

R4

R5

R6

C13

C14

C27

C16

C28

C29

R2

R7

R8

C31

C30

DIMENSION TABLE

DIM IN MM

W X L W X L

Z1,Z12 0.215 X TYP 5,46 X TYP

Z2,Z3 0.215 X 0.850 5,46 X 21,59

Z4,Z5 0.344 X 1.000 8,73 X 25,40

Z6,Z7 0.344 X 0.440 8,73 X 11,17

Z8,Z9 0.700 X 0.870 17,78 X 22,10

Z10,Z11 0.215 X 0.670 5,46 X 17,02

TL1 & TL2 0.100 X 2.37 2,54 X 60,20

DIMENSION OF MCROSTRIP

= 1/2 PRINTED BALUN ONLY.

TRANSMISSON LINE DIMENSIONS

Z1

Z2

Z4

Z6

TL1

Z3

Z5

Z7

Z12

Z8

Z10

Z9

Z11

TL2

REF. 7223940A

NOTES:

1. DIMENSIONS AT COMPONENT SYMBOLS ARE REFERENCE FOR COMPONENT PLACEMENT.

2. GAP BETWEEN GROUND & TRANSMISSION LINE = 0.056 [1.42] +0.002 [0.05] -0.000 [0.00] TYP.

3. DIMENSIONS OF INPUT AND OUTPUT COMPONENT FROM EDGE OF TRANSMISSION LINES.