1/11

February 2005

STP120NF04

N-CHANNEL 40V - 0.0047

- 120A TO-220

STripFETTMII MOSFET

Table 1: General Features

s

TYPICAL R

DS

(on) = 0.0047

s

STANDARD THRESHOLD DRIVE

s

100% AVALANCHE TESTED

DESCRIPTION

This MOSFET is the latest development of STMi-

croelectronics unique "Single Feature Size

TM"

strip-based process. The resulting transistor

shows extremely high packing density for low on-

resistance, rugged avalanche characteristics and

less critical alignment steps therefore a remark-

able manufacturing reproducibility.

APPLICATIONS

s

HIGH CURRENT, HIGH SWITCHING SPEED

Table 2: Order Codes

Figure 1: Package

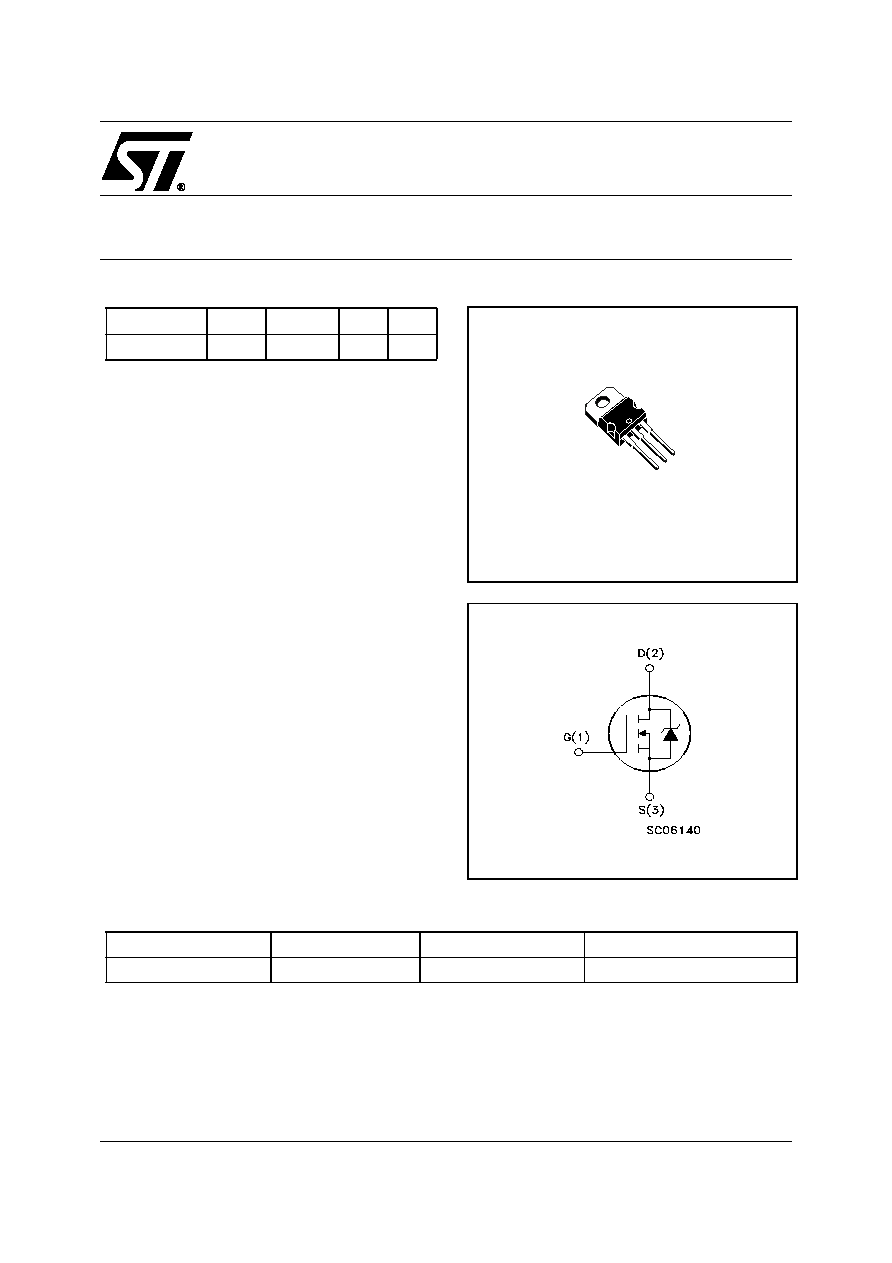

Figure 2: Internal Schematic Diagram

TYPE

V

DSS

R

DS(on)

I

D

(1)

Pw

STP120NF04

40 V

< 0.0050

120 A

300 W

1

2

3

TO-220

Part Number

Marking

Package

Packaging

STP120NF04

P120NF04

TO-220

TUBE

Rev. 1

STP120NF04

2/11

Table 3: Absolute Maximum ratings

( ) Pulse width limited by safe operating area

(1) I

SD

120A, di/dt

300A/µs, V

DD

V

(BR)DSS

, T

j

T

JMAX.

(2) Starting T

j

= 25∞C, I

d

= 60A, V

DD

=30 V

(#) Current Limited by Package

Table 4: Thermal Data

ELECTRICAL CHARACTERISTICS (T

CASE

=25∞C UNLESS OTHERWISE SPECIFIED)

Table 5: On /Off

Table 6: Dynamic

Symbol

Parameter

Value

Unit

V

DS

Drain-source Voltage (V

GS

= 0)

40

V

V

DGR

Drain-gate Voltage (R

GS

= 20 k

)

40

V

V

GS

Gate- source Voltage

± 20

V

I

D

(#)

Drain Current (continuos) at T

C

= 25∞C

120

A

I

D

Drain Current (continuos) at T

C

= 100∞C

120

A

I

DM

( )

Drain Current (pulsed)

480

A

P

TOT

Total Dissipation at T

C

= 25∞C

300

W

Derating Factor

2

W/∞C

dv/dt (1)

Peak Diode Recovery voltage slope

6

V/ns

E

AS

(2)

Single Pulse Avalanche Energy

1.2

J

T

j

T

stg

Operating Junction Temperature

Storage Temperature

-55 to 175

∞C

Rthj-case

Thermal Resistance Junction-case Max

0.5

∞C/W

Rthj-pcb

Thermal Resistance Junction-pcb Max

See Curve on page 6

∞C/W

Rthj-amb

Thermal Resistance Junction-ambient (Free air) Max

62.5

∞C/W

T

l

Maximum Lead Temperature For Soldering Purpose

300

∞C

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250 µA, V

GS

= 0

40

V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating,

T

C

= 125 ∞C

1

10

µA

µA

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= ± 20V

±100

nA

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

, I

D

= 250µA

2.8

4.5

V

R

DS(on)

Static Drain-source On

Resistance

V

GS

= 10V, I

D

= 50 A

0.0047

0.0050

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

g

fs

(1)

Forward Transconductance

V

DS

> =15 V

,

I

D

=50 A

150

S

C

iss

Input Capacitance

V

DS

= 25 V, f = 1 MHz,

V

GS

= 0

5100

pF

C

oss

Output Capacitance

1300

pF

C

rss

Reverse Transfer

Capacitance

160

pF

3/11

STP120NF04

ELECTRICAL CHARACTERISTICS (CONTINUED)

Table 7: Switching On

Table 8: Switching

Table 9: Source Drain Diode

(1) Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %.

(2) Pulse width limited by safe operating area.

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

t

d(on)

t

r

Turn-on Delay Time

Rise Time

V

DD

= 20 V, I

D

= 60 A

R

G

= 4.7

V

GS

= 10 V

(see, Figure 20)

35

220

ns

ns

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

= 32V, I

D

= 120 A,

V

GS

= 10V

(see, Figure 22)

110

35

35

150

nC

nC

nC

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

t

d(off)

t

f

Turn-off Delay Time

Fall Time

V

DD

= 20 V, I

D

= 60 A

R

G

= 4.7

V

GS

= 10 V

( see Figure 20 )

80

50

ns

ns

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

I

SD

I

SDM

(2)

Source-drain Current

Source-drain Current (pulsed)

120

480

A

A

V

SD

(1)

Forward On Voltage

I

SD

= 120 A, V

GS

= 0

1.3

V

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

SD

= 120 A, di/dt = 100A/µs

V

DD

= 20V, T

j

= 150∞C

(see test circuit, Figure 21)

75

185

5

ns

nC

A

STP120NF04

4/11

Figure 3: Safe Operating Area

Figure 4: Output Characteristics

Figure 5: Transconductance

Figure 6: Thermal Impedance

Figure 7: Transfer Characteristics

Figure 8: Static Drain-source On Resistance

5/11

STP120NF04

Figure 9: Gate Charge vs Gate-source Voltage

Figure 10: Normalized Gate Thereshold Volt-

age vs Temperature

Figure 11: Normalized On Resistance vs Tem-

perature

Figure 12: Capacitance Variation

Figure 13: Normalized BVDSS vs Temperature

Figure 14: Source-Drain Diode Forward Char-

acteristics