TDA7332

RDS FILTER

HIGH PERFORMANCE, STABLE 57KHz FIL-

TER

HIGH SELECTIVITY

FLAT GROUP DELAY

HIGH PERFORMANCE LIMITER

VERY FEW EXTERNAL COMPONENTS

4.332MHz CLOCK OSCILLATOR

(8.664MHz OPTIONAL)

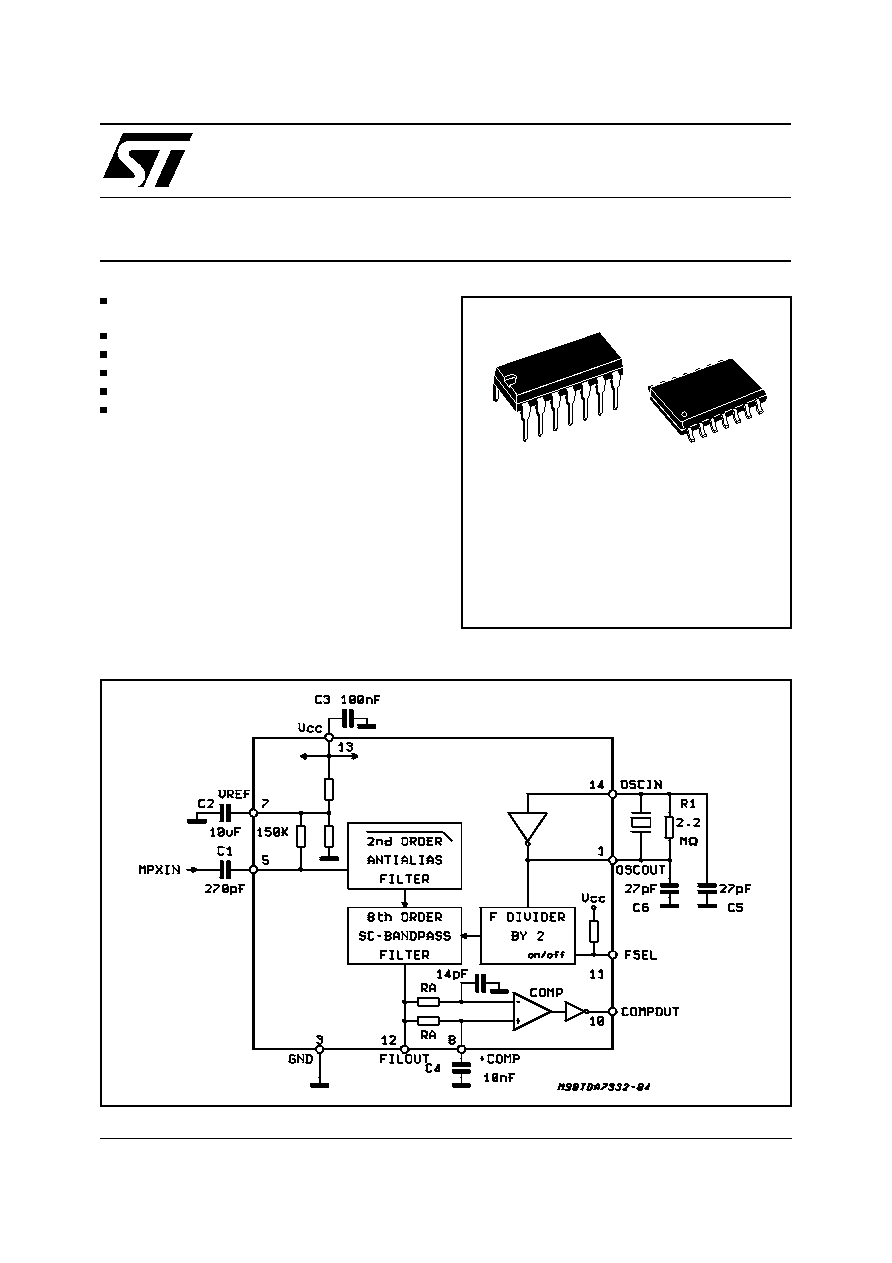

DESCRIPTION

The TDA7332 is an RDS filter, realized in

switched capacitor technique.

The 4 biquad stage architecture is working with

4.332MHz clock.

Optionally a 8.664MHz xtal can be used.

The filter has a center frequency of 57KHz and a

bandwidth of 3KHz. Input 2

nd

order antialiasing fil-

ter and output smoothing filter are provided.

November 1999

®

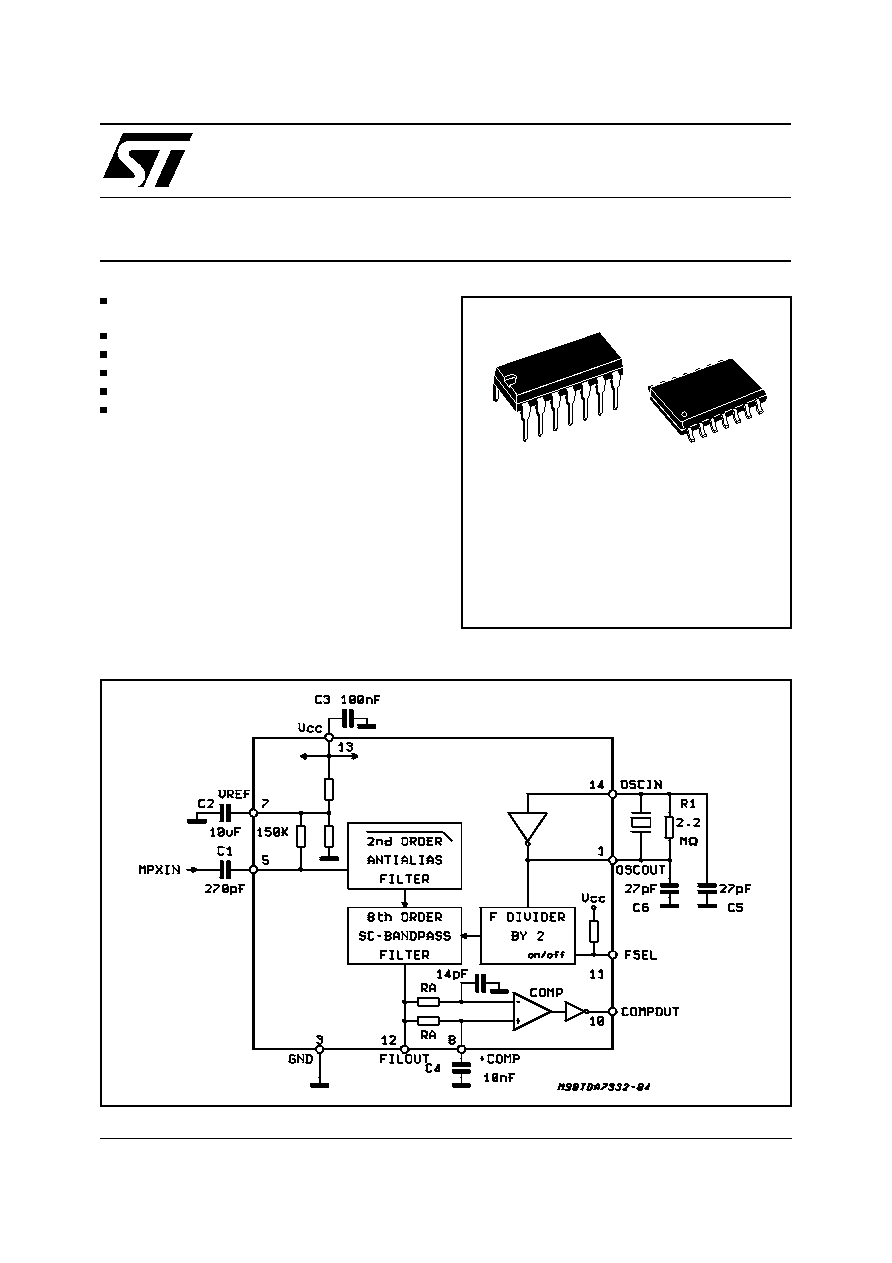

TEST CIRCUIT

DIP14 SO14

ORDERING NUMBERS:

TDA7332 TDA7332D

TDA7332DIE1 (Chip on wafer)

1/6

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

S

Supply Voltage

7

V

T

op

Operating Temperature Range

-40 to 85

°

C

T

stg

Storage Temperature

-40 to 150

°

C

THERMAL DATA

Symbol

Description

DIP14

SO14

Unit

R

th j-case

Thermal Resistance Junction-case Typ.

100

200

°

C/W

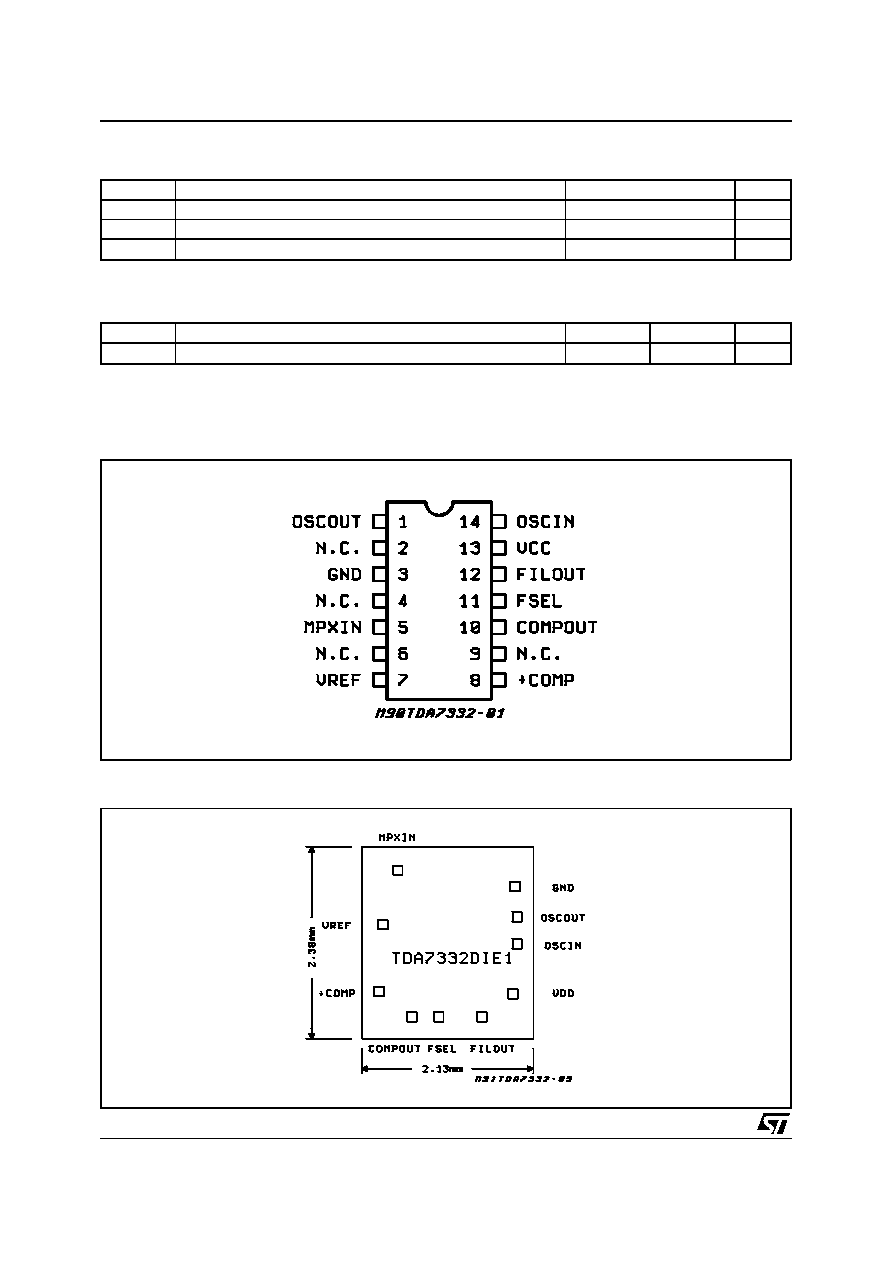

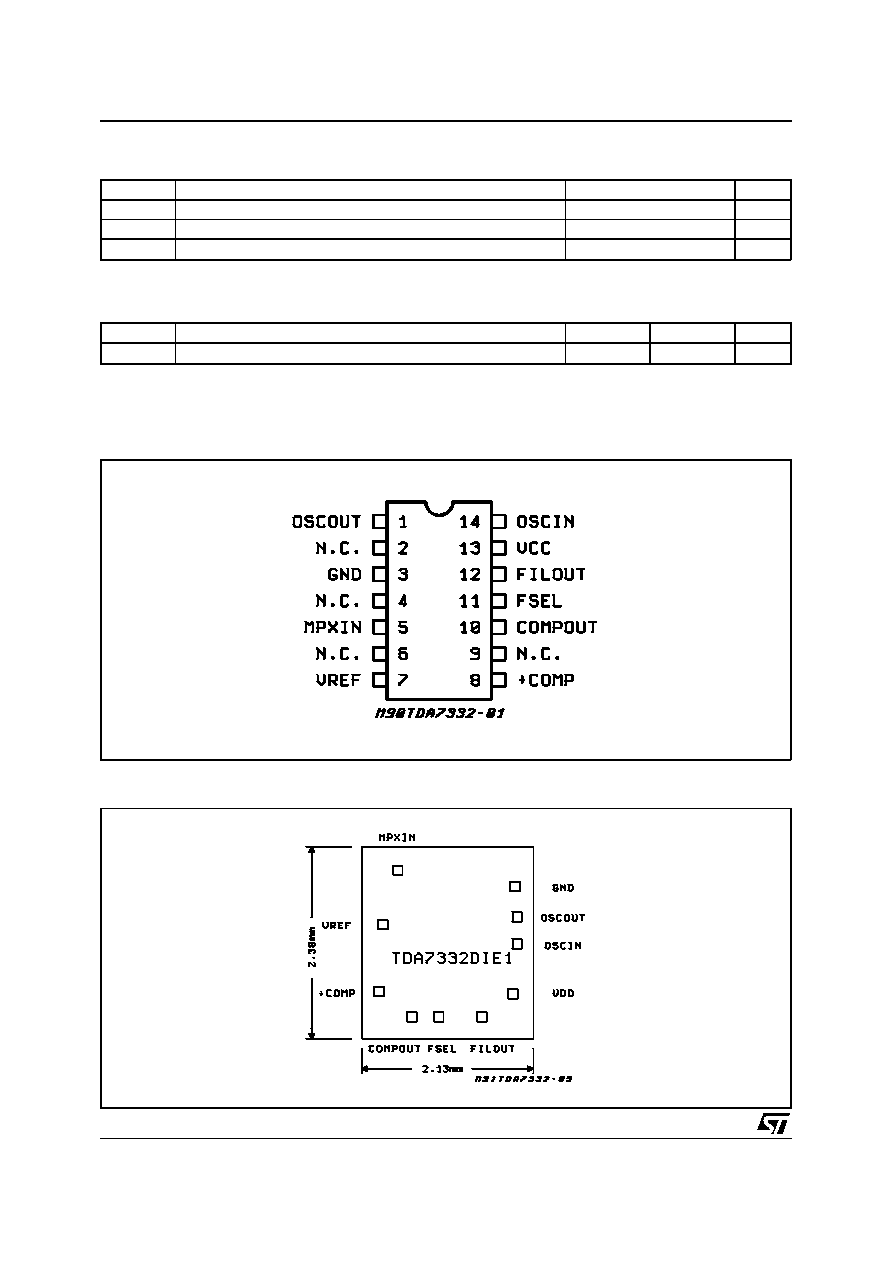

PIN CONNECTION (Top view)

BONDING PAD LOCATIONS (Top view)

TDA7332

2/6

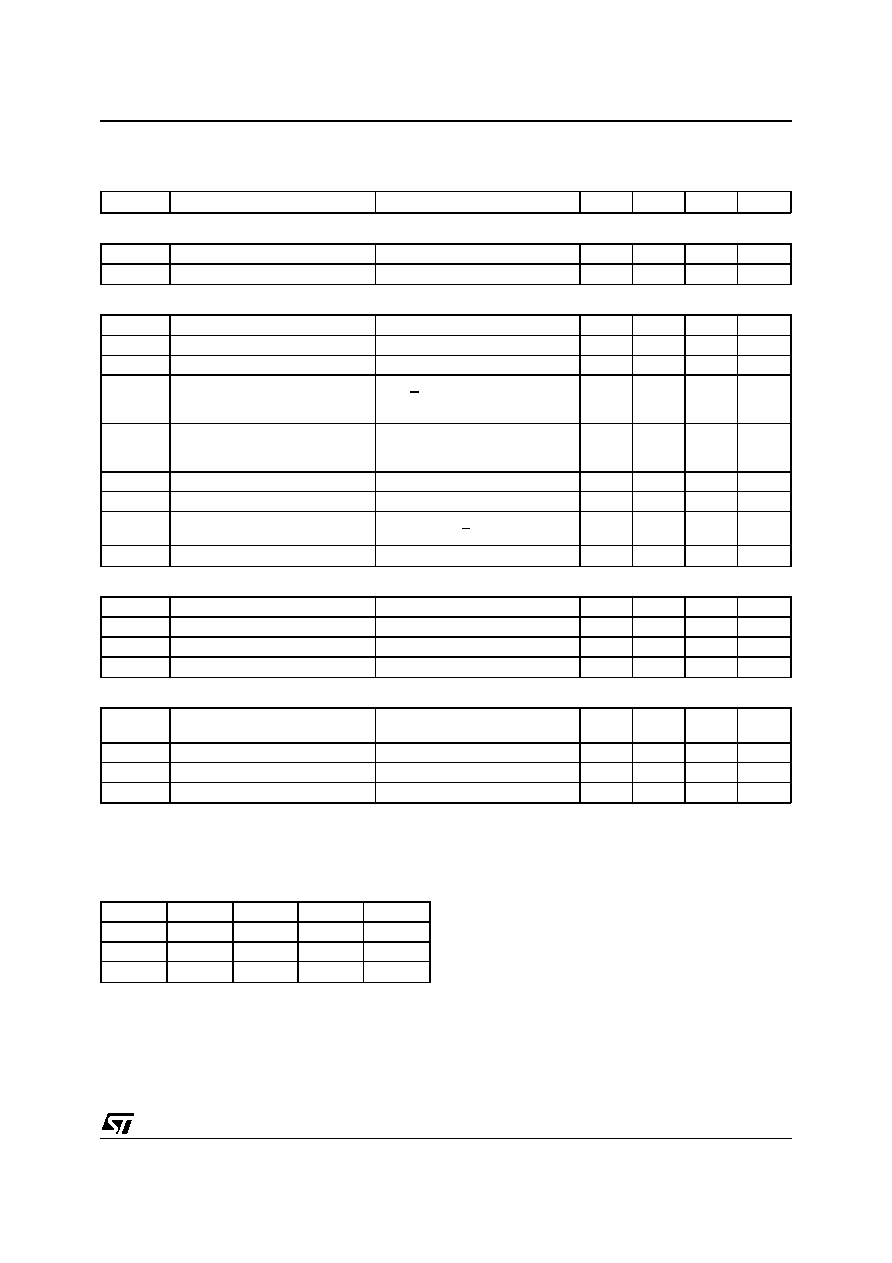

ELECTRICAL CHARACTERISTICS (V

CC

= 5V, Tamb = 25

°

C; fosc = 4.332MHz; V

IN

= 20mVrms unless

otherwise specified)

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

SUPPLY SECTION

V

CC

Supply Voltage

4.5

5

5.5

V

I

S

Supply Current

6

9

14

mA

FILTER

F

C

Center Frequency

56.5

57

57.5

KHz

BW

3dB Bandwidth

2.5

3

3.5

KHz

G

Gain

f = 57KHz

18

20

22

dB

A

Attenuation

f = +4KHz

f = 38KHz; V

i

= 500mVrms

f = 67KHz; V

i

= 250mVrms

18

50

35

22

80

50

dB

dB

dB

Ph

Phase non linearity

A (see note1)

B (see note1)

C (see note1)

0.5

1

2

5

7.5

10

DEG

DEG

DEG

R

i

Input Impedance

100

160

200

K

S/N

Signal to Noise Ratio

V

i

= 3mVrms

30

40

dB

V

i

Input Signal

f = 19KHz; T3 < 40dB (see note2)

f = 57KHz (RDS + ARI)

1

50

Vrms

mVrms

R

L

Load Impedance

Pin 12

100

K

LIMITER

RA

Resistance pin 8-12

15

21

28

K

V

OL

Comp. Output LOW

I

O

= +0.5mA

1

V

V

OH

Comp. Output HIGH

IO = 0.5mA

4

V

Duty Cycle

V

i

= 1mVrms

50

%

OSCILLATOR

F

OSC

Oscillator Frequency

F

SEL

= Open

F

SEL

= Closed to Ground

4.332

8.664

MHz

MHz

Output Amplitude

5

V

PP

V

CLL

Clock Input Level LOW

1

V

V

OLH

Clock Input Level HIGH

4

V

CRYSTAL TYPE = EURO QUARTZ

Note (1):

The phase non linearity is defined as:

Ph = | -2

f2 +

f1 +

f3 |

where

fx is the input-output phase difference at the frequency fx (x = 1,2,3)

Measure

f1 (KHz)

f2 (KHz)

f3 (KHz)

Ph max

A

56.5

57

57.5

<5

°

B

56

57

58

<7.5

°

C

55.5

57

58.5

<10

°

Note (2): The 3th harmonic (57KHz) at the output (pin12) must be less than -40dB in respect to the input signal plus gain.

TDA7332

3/6