| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: BQ3285LC | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Features

Æ Direct clock/calendar replace-

ment for IBM

Æ

AT-compatible

computers and other applications

Æ 2.7≠5.5V operation (bq3285LC);

4.5≠5.5V operation (bq3285EC)

Æ 242 bytes of general nonvolatile

storage

Æ Dedicated 32.768kHz output pin

Æ System wake-up capability--

alarm interrupt output active in

battery-backup mode

Æ Less than 0.5

µ

A load under bat-

tery operation

Æ Selectable Intel or Motorola bus

timing

Æ 24-pin plastic SOIC or SSOP

General Description

The CMOS bq3285EC/LC is a low-

power microprocessor peripheral pro-

viding a time-of-day clock and 100-

year calendar with alarm features

and battery operation. The architec-

ture is based on the bq3285/7 RTC

with added features: low-voltage op-

eration, 32.768kHz output, and an

extra 128 bytes of CMOS.

A 32.768kHz output is available for

sustaining power-management ac-

tivities. The bq3285EC 32kHz out-

put is always on whenever V

CC

is

valid. For the bq3285LC, the output

is on when the oscillator is turned

on.

In V

C C

standby mode, the

32kHz is active, and the bq3285LC

typically draws 100

µ

A while the

bq3285EC typically draws 300

µ

A.

Wake-up capability is provided by

an alarm interrupt, which is active

in battery-backup mode. In battery

backup mode, current drain is less

than 500nA.

The bq3285EC/LC write-protects the

clock, calendar, and storage registers

during power failure.

A backup

battery then maintains data and oper-

ates the clock and calendar.

The bq3285EC/LC is a fully com-

patible real-time clock for IBM AT-

compatible computers and other ap-

plications. The only external compo-

nents are a 32.768kHz crystal and a

backup battery.

The bq3285EC is intended for use in

5V systems.

The bq3285LC is in-

tended for use in 3V systems; the

bq3285LC, however, may also oper-

ate at 5V and then go into a 3V

power-down state, write-protecting

as if in a 3V system.

1

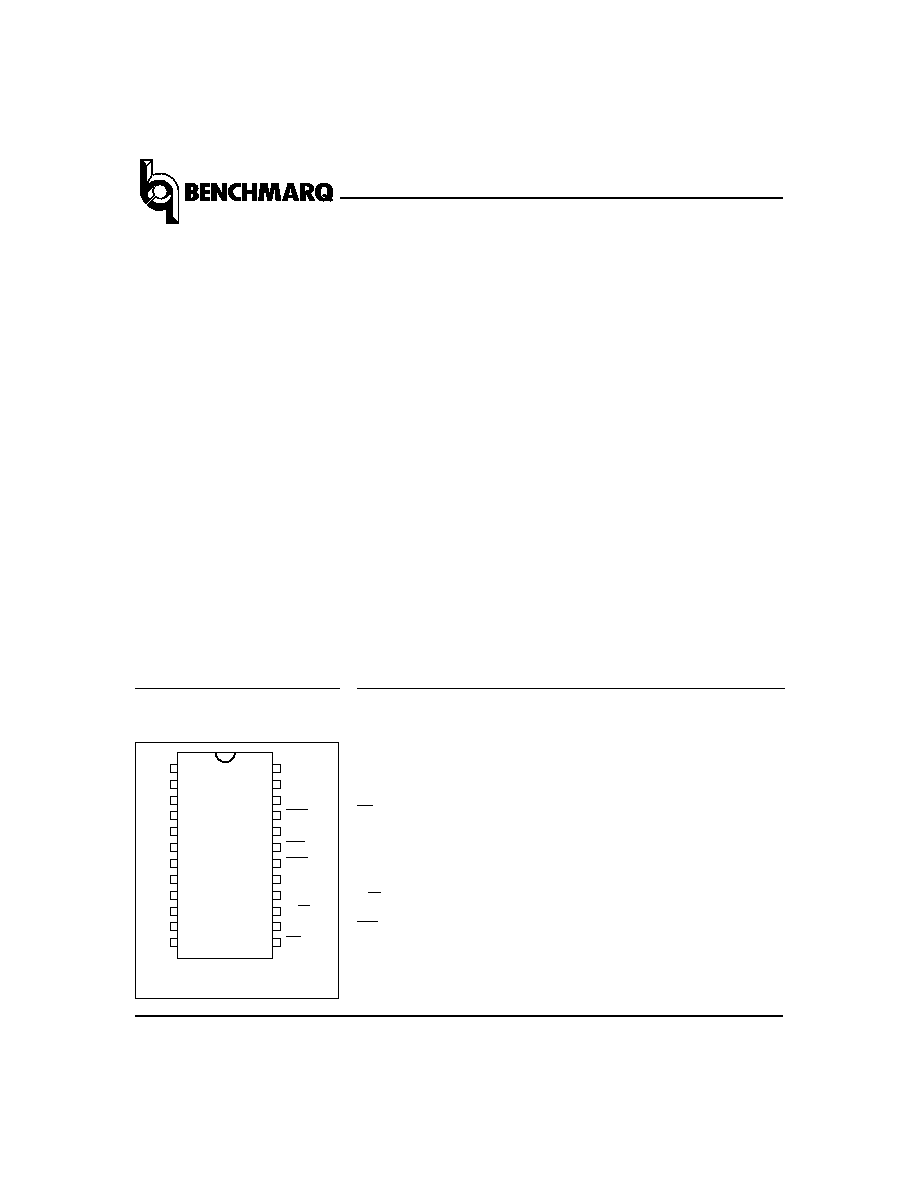

1

PN3285EC.eps

24-Pin SSOP

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

9

10

16

15

11

12

14

13

VCC

32k

EXTRAM

BC

INT

RST

DS

VSS

R/W

AS

CS

MOT

X1

X2

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

VSS

RCL

bq3285EC/LC

Pin Connections

Pin Names

July 1996

AD

0

≠AD

7

Multiplexed address/

data input/output

MOT

Bus type select input

CS

Chip select input

AS

Address strobe input

DS

Data strobe input

R/W

Read/write input

INT

Interrupt request output

RST

Reset input

32K

32.768kHz output

EXTRAM

Extended RAM enable

RCL

RAM clear input

BC

3V backup cell input

X1≠X2

Crystal inputs

V

CC

Power supply

V

SS

Ground

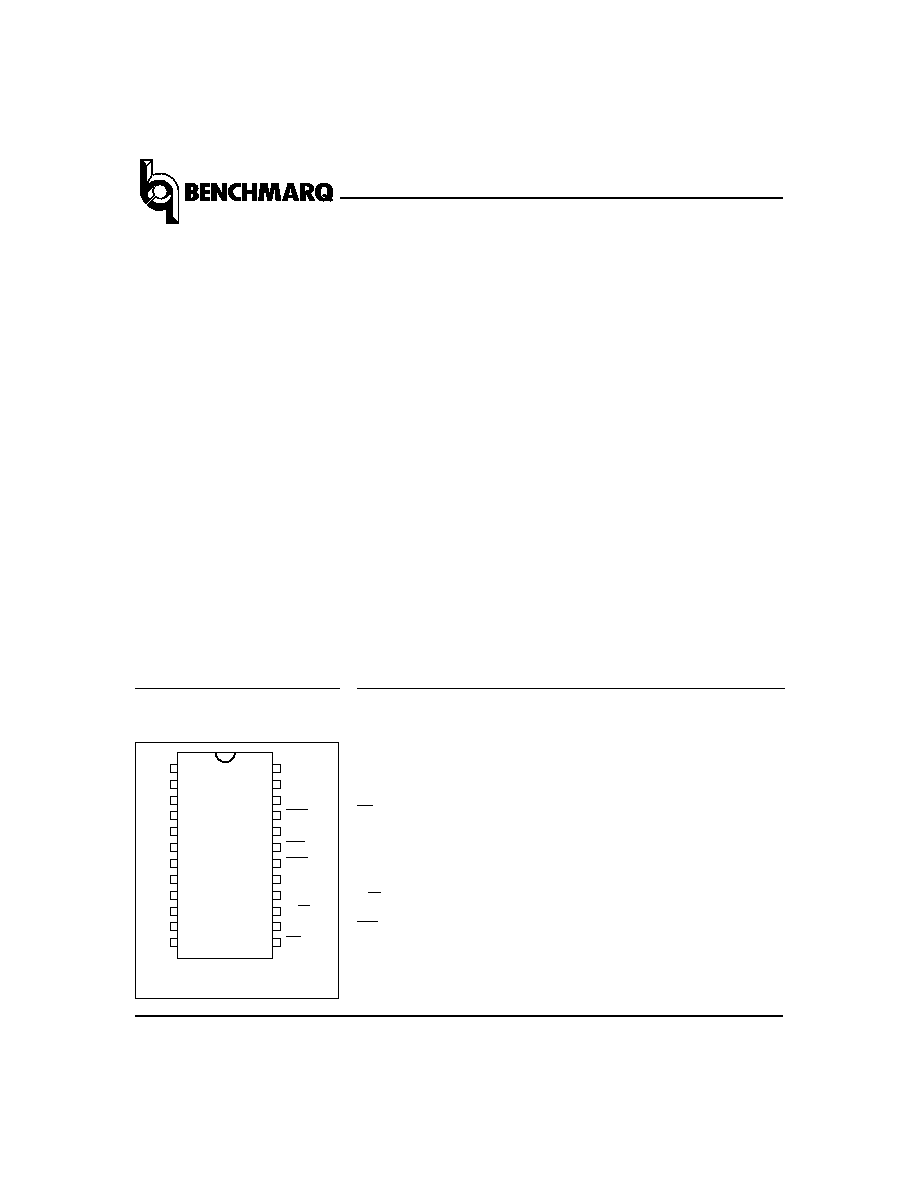

Real-Time Clock (RTC)

Block Diagram

Pin Descriptions

MOT

Bus type select input

MOT selects bus timing for either Motorola

or Intel architecture.

This pin should be

tied to V

CC

for Motorola timing or to V

SS

for

Intel timing (see Table 1).

The setting

should not be changed during system opera-

tion. MOT is internally pulled low by a 30K

resistor.

AD

0

≠AD

7

Multiplexed address/data

input/output

The bq3285EC/LC bus cycle consists of two

phases: the address phase and the data-

transfer phase.

The address phase pre-

cedes the data-transfer phase. During the

address phase, an address placed on

AD

0

≠AD

7

and EXTRAM is latched into the

bq3285EC/LC on the falling edge of the AS

signal. During the data-transfer phase of

the bus cycle, the AD

0

≠AD

7

pins serve as a

bidirectional data bus.

AS

Address strobe input

AS serves to demultiplex the address/data

bus. The falling edge of AS latches the ad-

dress on AD

0

≠AD

7

and EXTRAM. This de-

multiplexing process is independent of the

CS signal.

For DIP and SOIC packages

with MOT = V

SS

, the AS input is provided a

signal similar to ALE in an Intel-based sys-

tem.

2

bq3285EC/LC

Bus

Type

MOT

Level

DS

Equivalent

R/W

Equivalent

AS

Equivalent

Motorola

V

CC

DS, E, or

2

R/W

AS

Intel

V

SS

RD,

MEMR, or

I/OR

WR,

MEMW, or

I/OW

ALE

Table 1. Bus Setup

BD328501.eps

P

Bus

I/F

µ

Power-

Fail

Control

Storage Registers

(114 Bytes)

User Buffer

(14 Bytes)

VOUT

Clock/Calendar, Alarm

and Control Bytes

Time-

Base

Oscillator

Control/Status

Registers

˜ 8

˜ 64

˜ 64

16 1 MUX

:

Interupt

Generator

Control/Calendar

Update

VCC

DS

AD0≠AD7

CS

MOT

32K

INT

X1

X2

3

4

RST

R/W

AS

Storage Registers

(128 Bytes)

RCL

EXTRAM

Write

Protect

CS

BC

32K

Driver

July 1996

DS

Data strobe input

When MOT = V

CC

, DS controls data trans-

fer during a bq3285EC/LC bus cycle. Dur-

ing a read cycle, the bq3285EC/LC drives

the bus after the rising edge on DS. During

a write cycle, the falling edge on DS is used

to latch write data into the chip.

When MOT = V

SS

, the DS input is provided

a signal similar to RD, MEMR, or I/OR in

an Intel-based system. The falling edge on

DS is used to enable the outputs during a

read cycle.

R/W

Read/write input

When MOT = V

CC

, the level on R/W identi-

fies the direction of data transfer. A high

level on R/W indicates a read bus cycle,

whereas a low on this pin indicates a write

bus cycle.

When MOT = V

SS

, R/W is provided a signal

similar to WR, MEMW, or I/OW in an Intel-

based system.

The rising edge on R/W

latches data into the bq3285EC/LC.

CS

Chip select input

CS should be driven low and held stable

during the data-transfer phase of a bus cy-

cle accessing the bq3285EC/LC.

INT

Interrupt request output

INT is an open-drain output. This allows

alarm INT to be valid in battery-backup

mode. To use this feature, connect INT

through a resistor to a power supply other

than V

CC

. INT is asserted low when any

event flag is set and the corresponding

event enable bit is also set. INT becomes

high-impedance whenever register C is read

(see the Control/Status Registers section).

32K

32.768 kHz output

32K provides a buffered 32.768 kHz output.

The frequency remains on and fixed at

32.768kHz as long as V

CC

is valid.

EXTRAM

Extended RAM enable

Enables 128 bytes of additional nonvolatile

SRAM. It is connected internally to a 30k

pull-down resistor. To access the RTC regis-

ters, EXTRAM must be low.

RCL

RAM clear input

A low level on the RCL pin causes the con-

tents of each of the 242 storage bytes to be

set to FF(hex). The contents of the clock

and control registers are unaffected. This

pin should be used as a user-interface input

(pushbutton to ground) and not connected

to the output of any active component. RCL

input is only recognized when held low for

at least 125ms in the presence of V

CC

. Us-

ing RAM clear does not affect the battery

load. This pin is connected internally to a

30k

pull-up resistor.

BC

3V backup cell input

BC should be connected to a 3V backup cell

for RTC operation and storage register non-

volatility in the absence of system power.

When V

CC

slews down past V

BC

(3V typi-

cal), the integral control circuitry switches

the power source to BC. When V

CC

returns

above V

BC

, the power source is switched to

V

CC

.

Upon power-up, a voltage within the V

BC

range must be present on the BC pin for

the oscillator to start up.

RST

Reset input

The bq3285EC/LC is reset when RST is

pulled low. When reset, INT becomes high

impedance, and the bq3285EC/LC is not ac-

cessible. Table 4 in the Control/Status Reg-

isters section lists the register bits that are

cleared by a reset.

Reset may be disabled by connecting RST

to V

CC

. This allows the control bits to re-

t a i n

t h e i r

s t a t e s

t h r o u g h

p o w e r-

down/power-up cycles.

X1≠X2

Crystal inputs

The X1≠X2 inputs are provided for an ex-

ternal 32.768kHz quartz crystal, Daiwa

DT-26 or equivalent, with 6pF load capaci-

tance. A trimming capacitor may be neces-

sary for extremely precise time-base gen-

eration.

In the absence of a crystal, a 32.768kHz

waveform can be fed into the X1 input.

3

bq3285EC/LC

July 1996

Functional Description

Address Map

The bq3285EC/LC provides 14 bytes of clock and con-

trol/status registers and 242 bytes of general nonvolatile

storage.

Figure 1 illustrates the address map for the

bq3285EC/LC.

Update Period

The update period for the bq3285EC/LC is one second.

The bq3285EC/LC updates the contents of the clock and

calendar locations during the update cycle at the end of

each update period (see Figure 2). The alarm flag bit

may also be set during the update cycle.

The bq3285EC/LC copies the local register updates into

the user buffer accessed by the host processor. When a 1

is written to the update transfer inhibit bit (UTI) in reg-

ister B, the user copy of the clock and calendar bytes re-

mains unchanged, while the local copy of the same bytes

continues to be updated every second.

The update-in-progress bit (UIP) in register A is set

t

BUC

time before the beginning of an update cycle (see

Figure 2). This bit is cleared and the update-complete

flag (UF) is set at the end of the update cycle.

4

Figure 1. Address Map

Figure 2. Update Period Timing and UIP

bq3285EC/LC

July 1996

Programming the RTC

The time-of-day, alarm, and calendar bytes can be writ-

ten in either the BCD or binary format (see Table 2).

These steps may be followed to program the time, alarm,

and calendar:

1.

Modify the contents of register B:

a.

Write a 1 to the UTI bit to prevent trans-

fers between RTC bytes and user buffer.

b.

Write the appropriate value to the data

format (DF) bit to select BCD or binary

format for all time, alarm, and calendar

bytes.

c.

Write the appropriate value to the hour

format (HF) bit.

2.

Write new values to all the time, alarm, and

calendar locations.

3.

Clear the UTI bit to allow update transfers.

On the next update cycle, the RTC updates all 10 bytes

in the selected format.

5

bq3285EC/LC

Address

RTC Bytes

Range

Decimal

Binary

Binary-Coded

Decimal

0

Seconds

0≠59

00H≠3BH

00H≠59H

1

Seconds alarm

0≠59

00H≠3BH

00H≠59H

2

Minutes

0≠59

00H≠3BH

00H≠59H

3

Minutes alarm

0≠59

00H≠3BH

00H≠59H

4

Hours, 12-hour format

1≠12

01H≠OCH AM;

81H≠8CH PM

01H≠12H AM;

81H≠92H PM

Hours, 24-hour format

0≠23

00H≠17H

00H≠23H

5

Hours alarm, 12-hour format

1≠12

01H≠OCH AM;

81H≠8CH PM

01H≠12H AM;

81H≠92H PM

Hours alarm, 24-hour format

0≠23

00H≠17H

00H≠23H

6

Day of week (1=Sunday)

1≠7

01H≠07H

01H≠07H

7

Day of month

1≠31

01H≠1FH

01H≠31H

8

Month

1≠12

01H≠0CH

01H≠12H

9

Year

0≠99

00H≠63H

00H≠99H

Table 2. Time, Alarm, and Calendar Formats

July 1996