Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

MSP430C11x1, MSP430F11x1A

MIXED SIGNAL MICROCONTROLLER

SLAS241H - SEPTEMBER 1999 - REVISED SEPTEMBER 2004

1

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

D

Low Supply Voltage Range 1.8 V to 3.6 V

D

Ultralow-Power Consumption

- Active Mode: 160

µ

A at 1 MHz, 2.2 V

- Standby Mode: 0.7

µ

A

- Off Mode (RAM Retention): 0.1

µ

A

D

Wake-Up From Standby Mode in less

than 6

µ

s

D

16-Bit RISC Architecture, 125 ns

Instruction Cycle Time

D

Basic Clock Module Configurations:

- Various Internal Resistors

- Single External Resistor

- 32-kHz Crystal

- High-Frequency Crystal

- Resonator

- External Clock Source

D

16-Bit Timer_A With Three

Capture/Compare Registers

D

On-Chip Comparator for Analog Signal

Compare Function or Slope A/D

Conversion

D

Serial Onboard Programming,

No External Programming Voltage Needed

Programmable Code Protection by

Security Fuse

D

Family Members Include:

MSP430C1101: 1KB ROM, 128B RAM

MSP430C1111: 2KB ROM, 128B RAM

MSP430C1121: 4KB ROM, 256B RAM

MSP430F1101A: 1KB + 128B Flash Memory

128B RAM

MSP430F1111A: 2KB + 256B Flash Memory

128B RAM

MSP430F1121A: 4KB + 256B Flash Memory

256B RAM

D

Available in a 20-Pin Plastic Small-Outline

Wide Body (SOWB) Package, 20-Pin Plastic

Small-Outline Thin Package, 20-Pin TVSOP

(F11x1A only) and 24-Pin QFN

D

For Complete Module Descriptions, Refer

to the MSP430x1xx Family User's Guide,

Literature Number SLAU049

description

The Texas Instruments MSP430 family of ultralow power microcontrollers consist of several devices featuring

different sets of peripherals targeted for various applications. The architecture, combined with five low power

modes is optimized to achieve extended battery life in portable measurement applications. The device features

a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that attribute to maximum code efficiency.

The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 6

µ

s.

The MSP430x11x1(A) series is an ultralow-power mixed signal microcontroller with a built-in 16-bit timer,

versatile analog comparator and fourteen I/O pins.

Typical applications include sensor systems that capture analog signals, convert them to digital values, and then

process the data for display or for transmission to a host system. Stand alone RF sensor front end is another

area of application. The I/O port inputs provide single slope A/D conversion capability on resistive sensors.

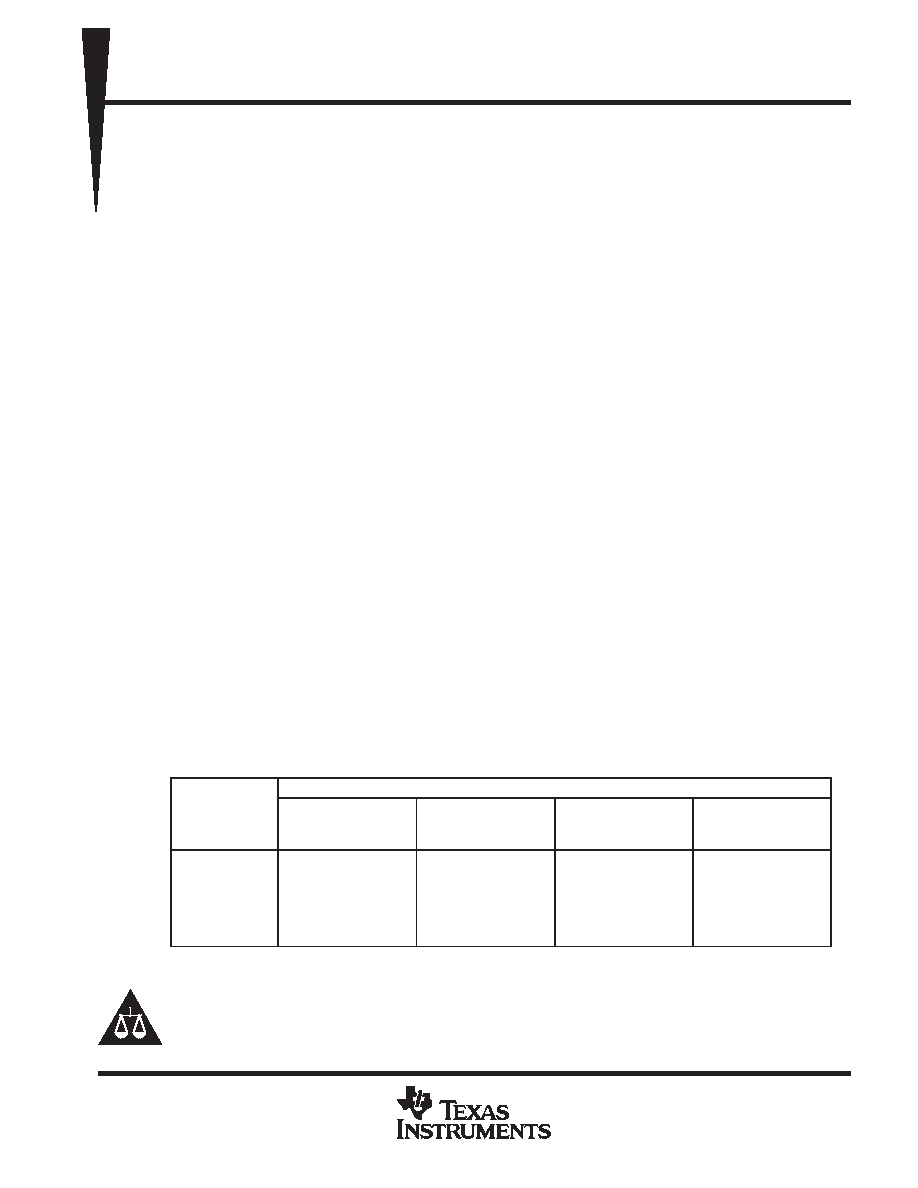

AVAILABLE OPTIONS

PACKAGED DEVICES

TA

PLASTIC

20-PIN SOWB

(DW)

PLASTIC

20-PIN TSSOP

(PW)

PLASTIC

20-PIN TVSOP

(DGV)

PLASTIC

24-PIN QFN

(RGE)

- 40

°

C to 85

°

C

MSP430C1101IDW

MSP430C1111IDW

MSP430C1121IDW

MSP430C1101IPW

MSP430C1111IPW

MSP430C1121IPW

MSP430F1101AIDGV

MSP430F1111AIDGV

MSP430C1101IRGE

MSP430C1111IRGE

MSP430C1121IRGE

- 40

°

C to 85

°

C

MSP430C1121IDW

MSP430F1101AIDW

MSP430F1111AIDW

MSP430F1121AIDW

MSP430C1121IPW

MSP430F1101AIPW

MSP430F1111AIPW

MSP430F1121AIPW

MSP430F1111AIDGV

MSP430F1121AIDGV

MSP430C1121IRGE

MSP430F1101AIRGE

MSP430F1111AIRGE

MSP430F1121AIRGE

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright

1999 - 2004 Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

MSP430C11x1, MSP430F11x1A

MIXED SIGNAL MICROCONTROLLER

SLAS241H - SEPTEMBER 1999 - REVISED SEPTEMBER 2004

2

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

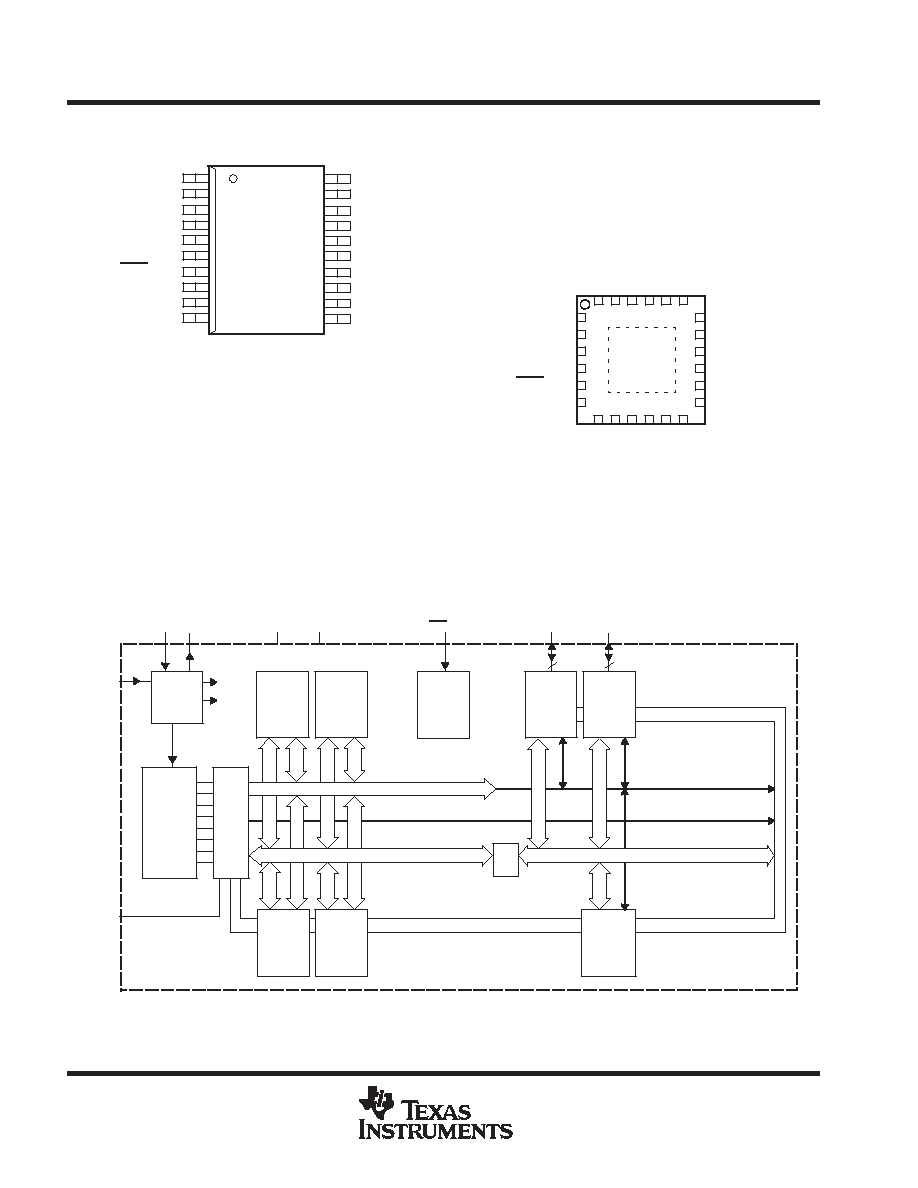

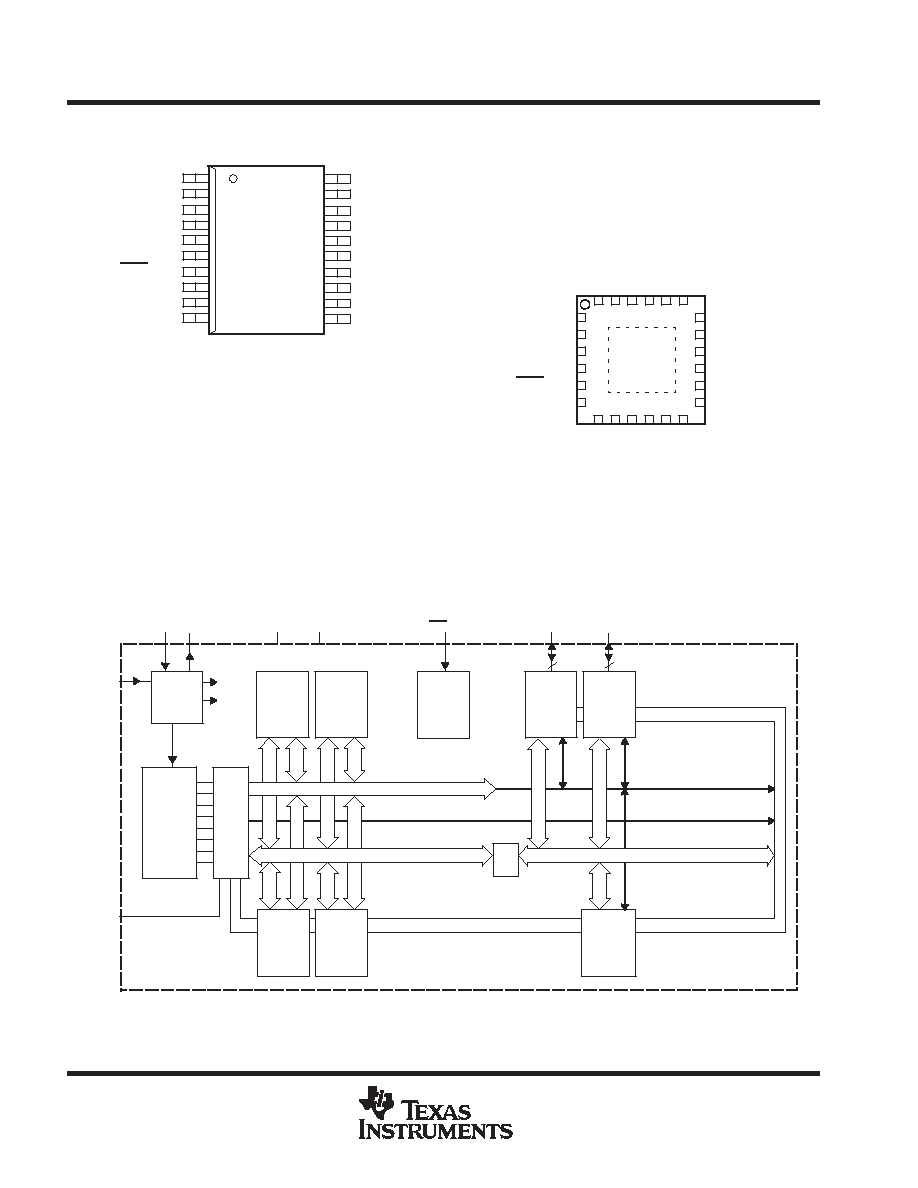

RGE PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

TEST

V

CC

P2.5/R

osc

V

SS

XOUT

XIN

RST/NMI

P2.0/ACLK

P2.1/INCLK

P2.2/CAOUT/TA0

P1.7/TA2/TDO/TDI

P1.6/TA1/TDI/TCLK

P1.5/TA0/TMS

P1.4/SMCLK/TCK

P1.3/TA2

P1.2/TA1

P1.1/TA0

P1.0/TACLK

P2.4/CA1/TA2

P2.3/CA0/TA1

DW, PW, or DGV PACKAGE

(TOP VIEW)

V

SS

P2.5/R

OSC

XOUT

V

CC

XIN

TEST

RST/NMI

P1.7/T

A2/TDO/TDI

P2.0/ACLK

P1.6/T

A1/TDI/TCLK

NC

NC

P1.4/SMCLK/TCK

P1.3/TA2

P1.2/TA1

P1.1/TA0

P1.0/TACLK

P1.5/TA0/TMS

Note: NC pins not internally connected

P2.1/INCLK

P2.2/CAOUT/T

A0

NC

P2.3/CA0/T

A1

P2.4/CA1/T

A2

NC

1

2

3

4

5

6

18

17

16

15

14

13

8 9 10 11

20

21

22

23

Power Pad connection to VSS recommended

functional block diagram

Oscillator

ACLK

SMCLK

CPU

Incl. 16 Reg.

Bus

Conv

MCB

XIN

XOUT

P2

MDB, 16 Bit

MAB, 16 Bit

MCLK

MAB,

4 Bit

VCC

VSS

RST/NMI

System

Clock

ROSC

P1/JTAG

Flash/ROM

4KB

2KB

1KB

RAM

256B

128B

128B

Watchdog

Timer

15/16-Bit

Timer_A3

3 CC Reg

I/O Port 1

8 I/Os, with

Interrupt

Capability

I/O Port 2

6 I/Os, with

Interrupt

Capability

POR

MDB, 16-Bit

MAB, 16-Bit

TEST

Test

JTAG

Emulation

Module

8

6

Comparator

A

MDB, 8 Bit

MSP430C11x1, MSP430F11x1A

MIXED SIGNAL MICROCONTROLLER

SLAS241H - SEPTEMBER 1999 - REVISED SEPTEMBER 2004

3

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

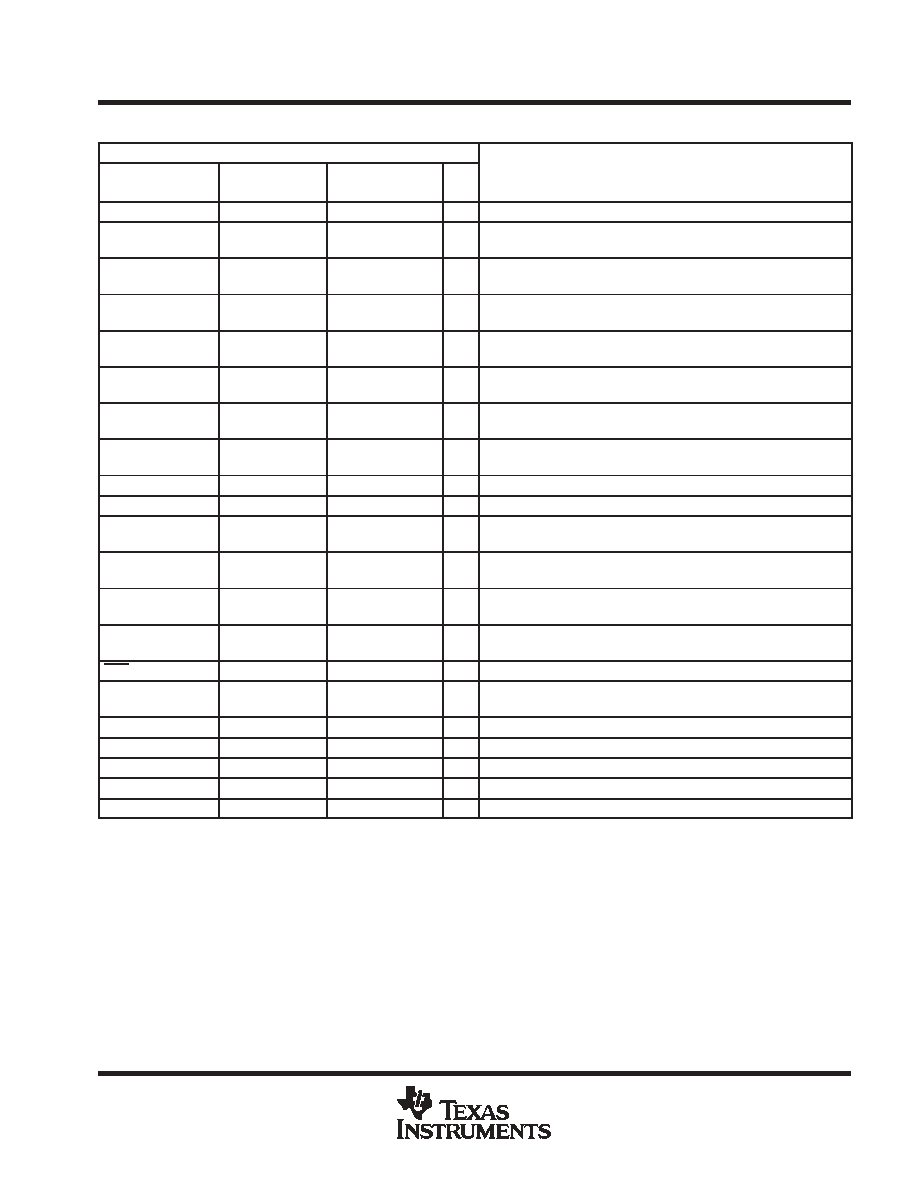

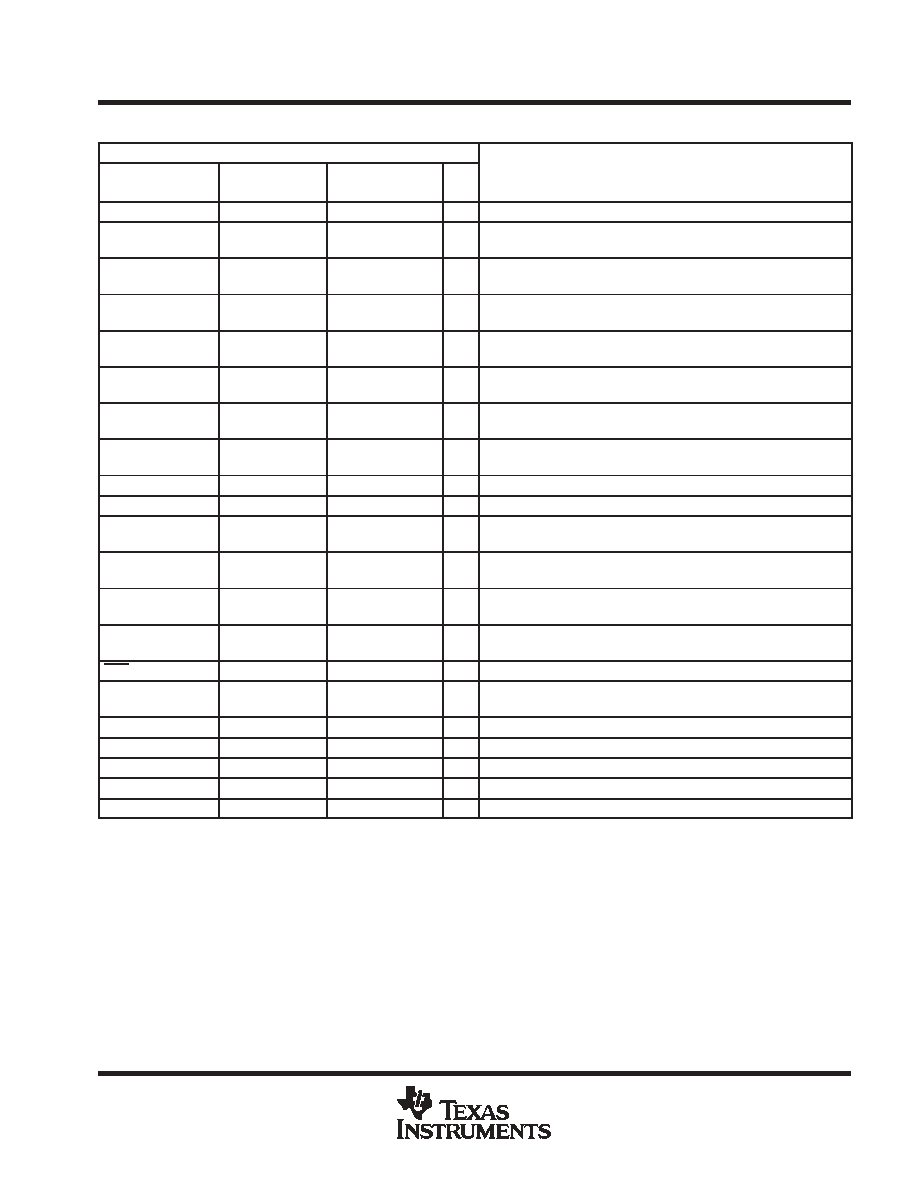

Terminal Functions

TERMINAL

NAME

DW, PW, or DGV

RGE

I/O

DESCRIPTION

NAME

NO.

NO.

I/O

DESCRIPTION

P1.0/TACLK

13

13

I/O

General-purpose digital I/O pin/Timer_A, clock signal TACLK input

P1.1/TA0

14

14

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI0A input,

compare: Out0 output/BSL transmit

P1.2/TA1

15

15

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI1A input,

compare: Out1 output

P1.3/TA2

16

16

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI2A input,

compare: Out2 output

P1.4/SMCLK/TCK

17

17

I/O

General-purpose digital I/O pin/SMCLK signal output/test clock, input

terminal for device programming and test

P1.5/TA0/TMS

18

18

I/O

General-purpose digital I/O pin/Timer_A, compare: Out0 output/test

mode select, input terminal for device programming and test

P1.6/TA1/TDI/TCLK

19

20

I/O

General-purpose digital I/O pin/Timer_A, compare: Out1 output/test

data input or test clock input

P1.7/TA2/TDO/TDI

20

21

I/O

General-purpose digital I/O pin/Timer_A, compare: Out2 output/test

data output terminal or data input during programming

P2.0/ACLK

8

6

I/O

General-purpose digital I/O pin/ACLK output

P2.1/INCLK

9

7

I/O

General-purpose digital I/O pin/Timer_A, clock signal at INCLK

P2.2/CAOUT/TA0

10

8

I/O

General-purpose digital I/O pin/Timer_A, capture: CCI0B input/

comparator_A, output/BSL receive

P2.3/CA0/TA1

11

10

I/O

General-purpose digital I/O pin/Timer_A, compare: Out1 output/

comparator_A, input

P2.4/CA1/TA2

12

11

I/O

General-purpose digital I/O pin/Timer_A, compare: Out2 output/

comparator_A, input

P2.5/ROSC

3

24

I/O

General-purpose digital I/O pin/input for external resistor that defines

the DCO nominal frequency

RST/NMI

7

5

I

Reset or nonmaskable interrupt input

TEST

1

22

I

Selects test mode for JTAG pins on Port1. The device protection fuse

is connected to TEST.

VCC

2

23

Supply voltage

VSS

4

2

Ground reference

XIN

6

4

I

Input terminal of crystal oscillator

XOUT

5

3

O

Output terminal of crystal oscillator

QFN Pad

NA

Package Pad

NA

QFN package pad connection to VSS recommended.

TDO or TDI is selected via JTAG instruction.

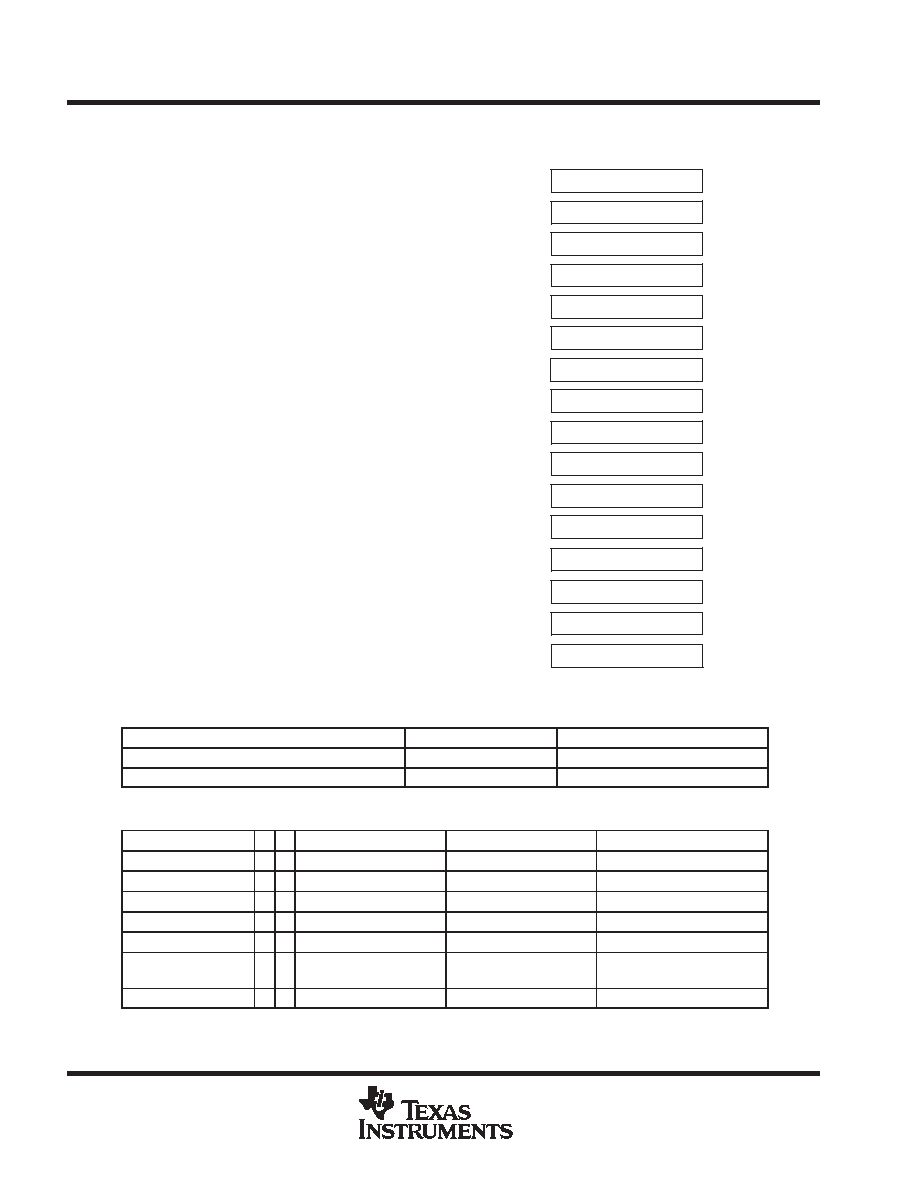

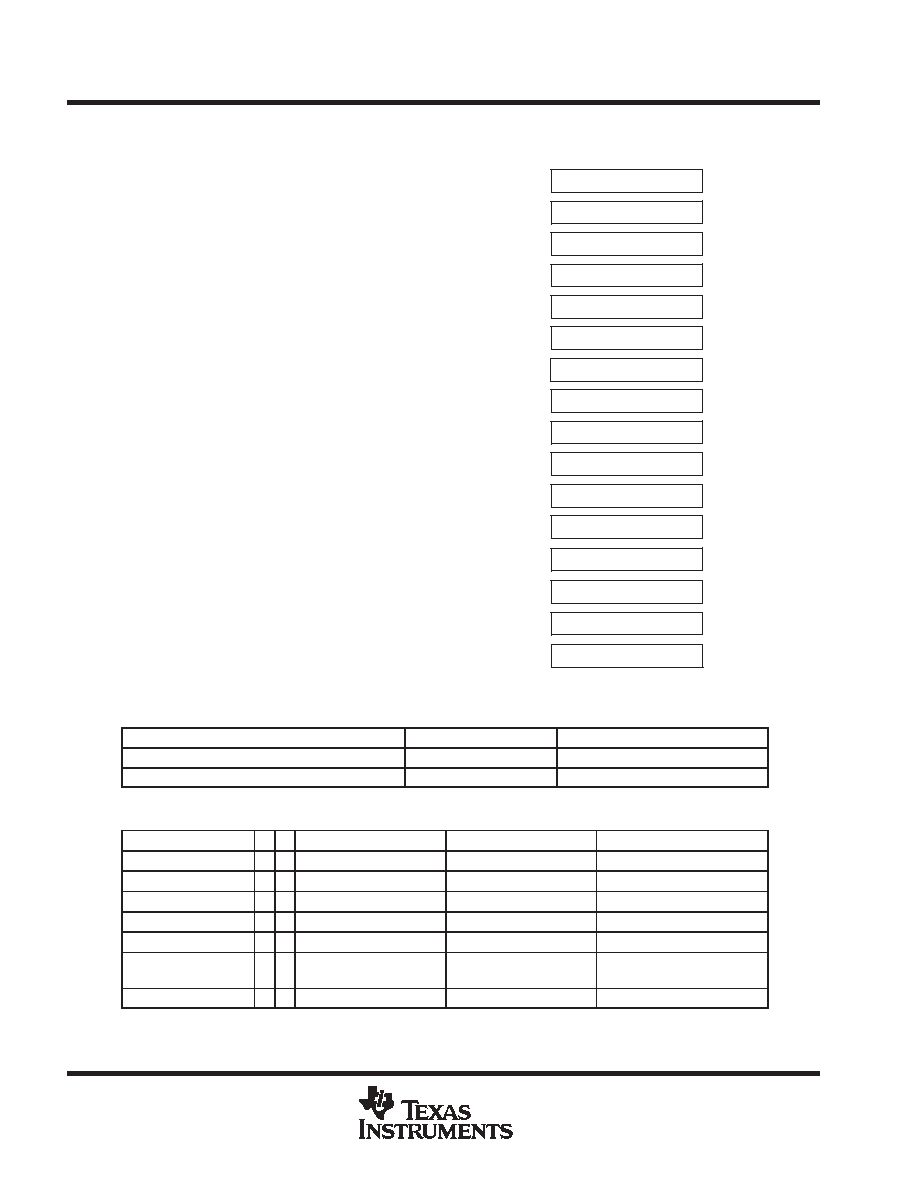

General-Purpose Register

Program Counter

Stack Pointer

Status Register

Constant Generator

General-Purpose Register

General-Purpose Register

General-Purpose Register

PC/R0

SP/R1

SR/CG1/R2

CG2/R3

R4

R5

R12

R13

General-Purpose Register

General-Purpose Register

R6

R7

General-Purpose Register

General-Purpose Register

R8

R9

General-Purpose Register

General-Purpose Register

R10

R11

General-Purpose Register

General-Purpose Register

R14

R15

MSP430C11x1, MSP430F11x1A

MIXED SIGNAL MICROCONTROLLER

SLAS241H - SEPTEMBER 1999 - REVISED SEPTEMBER 2004

4

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

short-form description

CPU

The MSP430 CPU has a 16-bit RISC architecture

that is highly transparent to the application. All

operations, other than program-flow instructions,

are performed as register operations in

conjunction with seven addressing modes for

source operand and four addressing modes for

destination operand.

The CPU is integrated with 16 registers that

provide reduced instruction execution time. The

register-to-register operation execution time is

one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as

program counter, stack pointer, status register,

and constant generator respectively. The

remaining registers are general-purpose

registers.

Peripherals are connected to the CPU using data,

address, and control buses, and can be handled

with all instructions.

instruction set

The instruction set consists of 51 instructions with

three formats and seven address modes. Each

instruction can operate on word and byte data.

Table 1 shows examples of the three types of

instruction formats; the address modes are listed

in Table 2.

Table 1. Instruction Word Formats

Dual operands, source-destination

e.g. ADD R4,R5

R4 + R5 ---> R5

Single operands, destination only

e.g. CALL R8

PC -->(TOS), R8--> PC

Relative jump, un/conditional

e.g. JNE

Jump-on-equal bit = 0

Table 2. Address Mode Descriptions

ADDRESS MODE

S

D

SYNTAX

EXAMPLE

OPERATION

Register

F F

MOV Rs,Rd

MOV R10,R11

R10 --> R11

Indexed

F F

MOV X(Rn),Y(Rm)

MOV 2(R5),6(R6)

M(2+R5)--> M(6+R6)

Symbolic (PC relative)

F F

MOV EDE,TONI

M(EDE) --> M(TONI)

Absolute

F F

MOV &MEM,&TCDAT

M(MEM) --> M(TCDAT)

Indirect

F

MOV @Rn,Y(Rm)

MOV @R10,Tab(R6)

M(R10) --> M(Tab+R6)

Indirect

autoincrement

F

MOV @Rn+,Rm

MOV @R10+,R11

M(R10) --> R11

R10 + 2--> R10

Immediate

F

MOV #X,TONI

MOV #45,TONI

#45 --> M(TONI)

NOTE: S = source D = destination

MSP430C11x1, MSP430F11x1A

MIXED SIGNAL MICROCONTROLLER

SLAS241H - SEPTEMBER 1999 - REVISED SEPTEMBER 2004

5

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

operating modes

The MSP430 has one active mode and five software selectable low-power modes of operation. An interrupt

event can wake up the device from any of the five low-power modes, service the request and restore back to

the low-power mode on return from the interrupt program.

The following six operating modes can be configured by software:

D

Active mode AM;

-

All clocks are active

D

Low-power mode 0 (LPM0);

-

CPU is disabled

ACLK and SMCLK remain active. MCLK is disabled

D

Low-power mode 1 (LPM1);

-

CPU is disabled

ACLK and SMCLK remain active. MCLK is disabled

DCO's dc-generator is disabled if DCO not used in active mode

D

Low-power mode 2 (LPM2);

-

CPU is disabled

MCLK and SMCLK are disabled

DCO's dc-generator remains enabled

ACLK remains active

D

Low-power mode 3 (LPM3);

-

CPU is disabled

MCLK and SMCLK are disabled

DCO's dc-generator is disabled

ACLK remains active

D

Low-power mode 4 (LPM4);

-

CPU is disabled

ACLK is disabled

MCLK and SMCLK are disabled

DCO's dc-generator is disabled

Crystal oscillator is stopped

Document Outline

- features

- description

- functional block diagram

- Terminal Functions

- short-form description

- CPU

- instruction set

- operating modes

- interrupt vector addresses

- special function registers

- interrupt enable 1 and 2

- interrupt flag register 1 and 2

- memory organization

- bootstrap loader (BSL)

- flash memory

- peripherals

- oscillator and system clock

- digital I/O

- watchdog timer

- comparator_A

- timer_A3

- peripheral file map

- absolute maximum ratings

- recommended operating conditions

- electrical characteristics over recommended ranges of supply voltage and operating free-air temperature ( unless otherwise noted)

- supply current (into VCC) excluding external current

- current consumption of active mode versus system frequency, C version, F version

- current consumption of active mode versus supply voltage, C version

- current consumption of active mode versus supply voltage, F version

- Schmitt-trigger inputs - Ports P1 and P2; (P1.0 to P1.7, P2.0 to P2.5)

- standard inputs - RST\/NMI, JTAG: TCK, TMS, TDI/TCLK

- inputs Px.x, TAx

- leakage current

- outputs - Ports P1 and P2; (P1.0 to P1.7, P2.0 to P2.5)

- output frequency

- optional resistors, individually programmable with ROM code (see Note 1)

- wake-up from lower power modes (LPMx)

- RAM

- Comparator_A (see Note 1)

- PUC/POR

- DCO

- main DCO characteristics

- DCO when using ROSC ( see Note 1)

- crystal oscillator, LFXT1

- Flash Memory

- JTAG Interface

- JTAG Fuse (see Note 1)

- APPLICATION INFORMATION

- input/output schematic

- Port P1, P1.0 to P1.3, input/output with Schmitt-trigger

- Port P1, P1.4 to P1.7, input/output with Schmitt-trigger and in-system access features

- Port P2, P2.0 to P2.2, input/output with Schmitt-trigger

- Port P2, P2.3 to P2.4, input/output with Schmitt-trigger

- Port P2, P2.5, input/output with Schmitt-trigger and ROSC function for the Basic Clock module

- Port P2, unbonded bits P2.6 and P2.7

- JTAG fuse check mode

- MECHANICAL DATA

- DW (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

- PW (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

- DGV (R-PDSO-G**) PLASTIC SMALL-OUTLINE

- RGE (S-PQFP-N24) PLASTIC QUAD FLATPACK

- IMPORTANT NOTICE