| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SN65518FN | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

SN65518, SN75518

VACUUM FLUORESCENT DISPLAY DRIVERS

SLDS004B ≠ MARCH 1983 ≠ REVISED MAY 1990

Copyright

©

1990, Texas Instruments Incorporated

4≠1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

∑

Each Device Drives 32 Lines

∑

60-V Output Voltage Swing Capability

∑

25-mA Output Source Current Capability

∑

High-Speed Serially Shifted Data Input

∑

Latches on All Driver Outputs

description

The SN65518 and SN75518 are monolithic

BIDFET

integrated circuits designed to drive a

dot matrix or segmented vacuum fluorescent

display.

Each device consists of a 32-bit shift register, 32

latches, and 32 output AND gates. Serial data is

entered into the shift register on the low-to-high

transition of CLOCK. While LATCH ENABLE is

high, parallel data is transferred to the output

buffers through a 32-bit latch. Data present in the

latch during the high-to-low transition of LATCH

ENABLE is latched. When STROBE is low, all Q

outputs are enabled. When STROBE is high, all Q

outputs are low.

Serial data output from the shift register may be

used to cascade additional devices. This output is

not affected by LATCH ENABLE or STROBE.

The SN65518 is characterized for operation from

≠ 40

∞

C to 85

∞

C. The SN75518 is characterized for

operation from 0

∞

C to 70

∞

C.

BIDFET ≠ Bipolar, double-diffused, N-channel and P-channel MOS transistors on same chip. This is a patented process.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

V

CC2

SERIAL OUT

Q32

Q31

Q30

Q29

Q28

Q27

Q26

Q25

Q24

Q23

Q22

Q21

Q20

Q19

Q18

Q17

STROBE

GND

V

CC1

DATA IN

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

Q12

Q13

Q14

Q15

Q16

LATCH ENABLE

CLOCK

N PACKAGE

(TOP VIEW)

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

Q12

Q13

NC

39

38

37

36

35

34

33

32

31

30

29

18 19

7

8

9

10

11

12

13

14

15

16

17

Q29

Q28

Q27

Q26

Q25

Q24

Q23

Q22

Q21

Q20

Q19

20 21 22 23

FN PACKAGE

(TOP VIEW)

DA

T

A

IN

Q1

Q2

Q3

5 4

3

2

1

6

44

NC

Q30

Q31

Q32

SERIAL

OUT

Q16

Q15

Q14

NC

NC

Q18

Q17

STROBE

GND

CLOCK

LA

TCH ENABLE

42 41 40

43

24 25 26 27 28

NC ≠ No internal connection

CC1

V

CC2

V

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN65518, SN75518

VACUUM FLUORESCENT DISPLAY DRIVERS

SLDS004B ≠ MARCH 1983 ≠ REVISED MAY 1990

4≠2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

logic symbol

2D

3

STROBE

LATCH

ENABLE

CLOCK

DATA IN

CMOS/ VAC

FLUOR DISP

SRG32

C1/

EN3

C2

19

22

21

39

2D

3

2D

3

2D

3

2D

3

2D

3

38

37

23

18

4

3

2

Q1

Q2

Q16

Q17

Q31

Q32

SERIAL OUT

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the N package.

logic diagram (positive logic)

1D

C1

1D

C1

1D

C1

1D

C1

2D

C2

2D

C2

2D

C2

2D

C2

28 Stages

(Q3 thru Q30)

Not Shown

Q1

Q2

Q31

Q32

LC1

LC2

LC31

LC32

SERIAL OUT

Shift

Register

Latches

R1

R2

R31

R32

STROBE

LATCH

ENABLE

DATA IN

CLOCK

SN65518, SN75518

VACUUM FLUORESCENT DISPLAY DRIVERS

SLDS004B ≠ MARCH 1983 ≠ REVISED MAY 1990

4≠3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

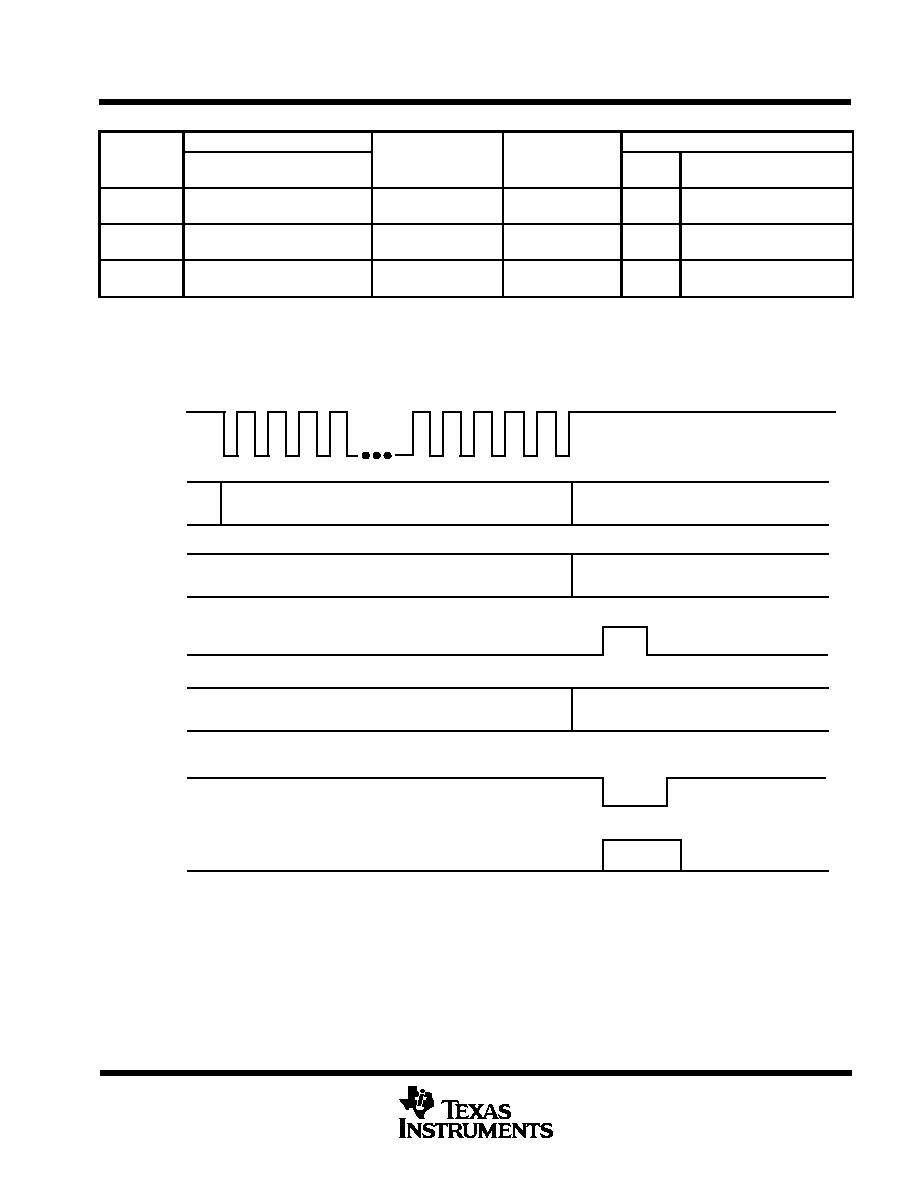

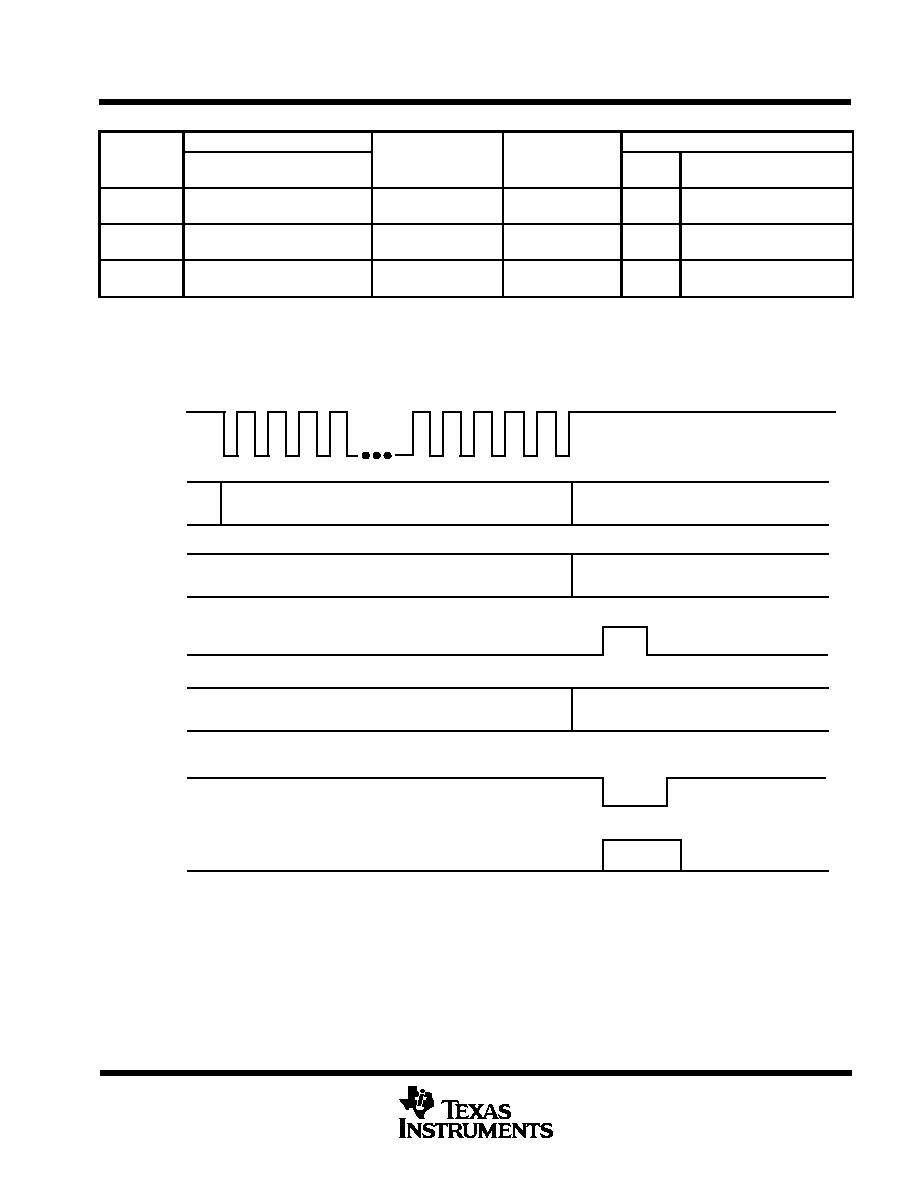

FUNCTION TABLE

CONTROL INPUTS

SHIFT REGISTERS

LATCHES

OUTPUTS

FUNCTION

CLOCK

LATCH

ENABLE

STROBE

SHIFT REGISTERS

R1 THRU R32

LATCHES

LC1 THRU LC32

SERIAL

Q1 THRU Q32

Load

No

X

X

X

X

Load and shift

No change

Determined by

LATCH ENABLE

R32

Determined by STROBE

Latch

X

X

L

H

X

X

As determined

above

Stored data

New data

R32

Determined by STROBE

Strobe

X

X

X

X

H

L

As determined

above

Determined by

LATCH ENABLE

R32

All L

LC1 thru LC32, respectively

H = high level, L = low level, X = irrelevant,

= low-to-high-level transition.

R32 and the serial output take on the state of R31, R31 takes on the state of R30, ... R2 takes on the state of R1, and R1 takes on the state of

the data input.

New data enter the latches while LATCH ENABLE is high. These data are stored while LATCH ENABLE is low.

typical operating sequence

CLOCK

Valid

Irrelevant

DATA IN

Invalid

SR

Contents

LATCH

ENABLE

Previously Stored Data

New Data Valid

Latch

Contents

STROBE

Valid

Q Outputs

Valid

SN65518, SN75518

VACUUM FLUORESCENT DISPLAY DRIVERS

SLDS004B ≠ MARCH 1983 ≠ REVISED MAY 1990

4≠4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

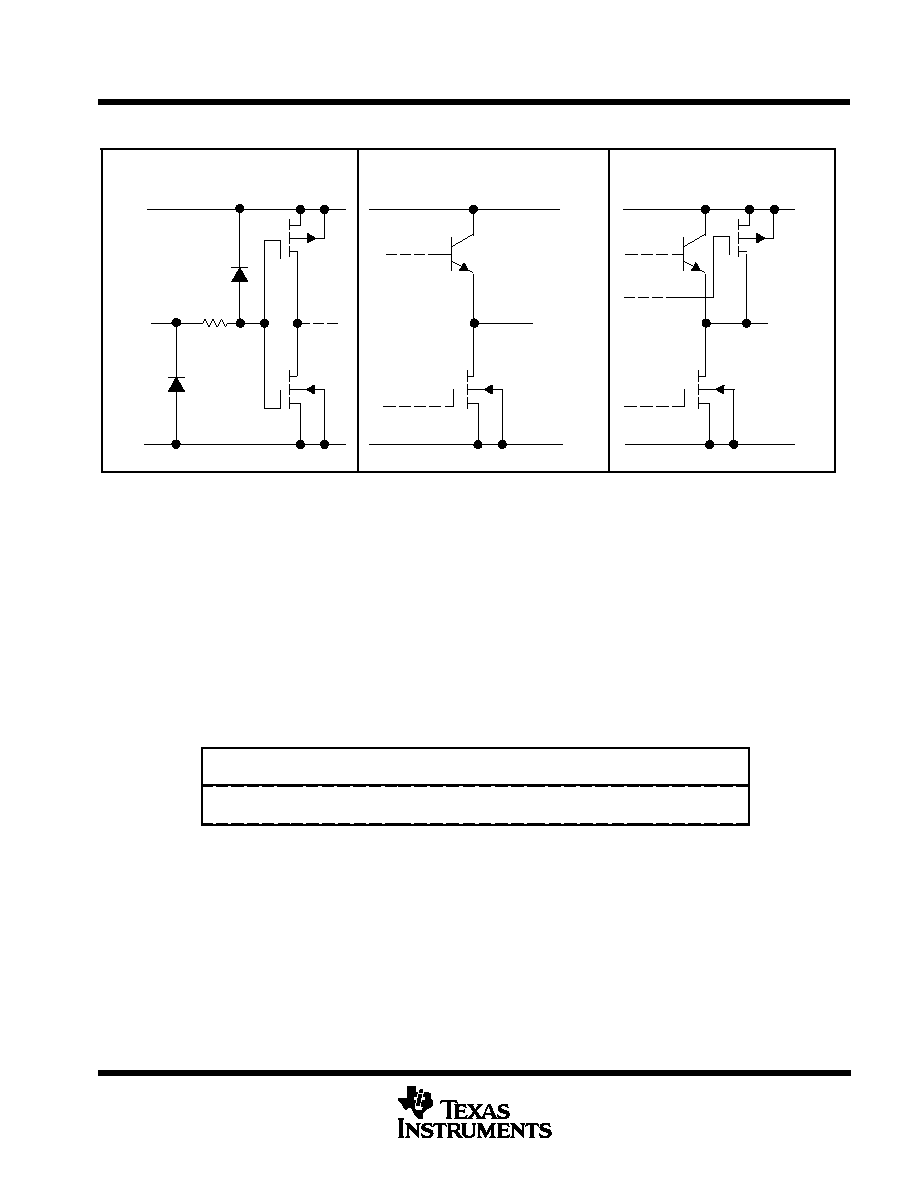

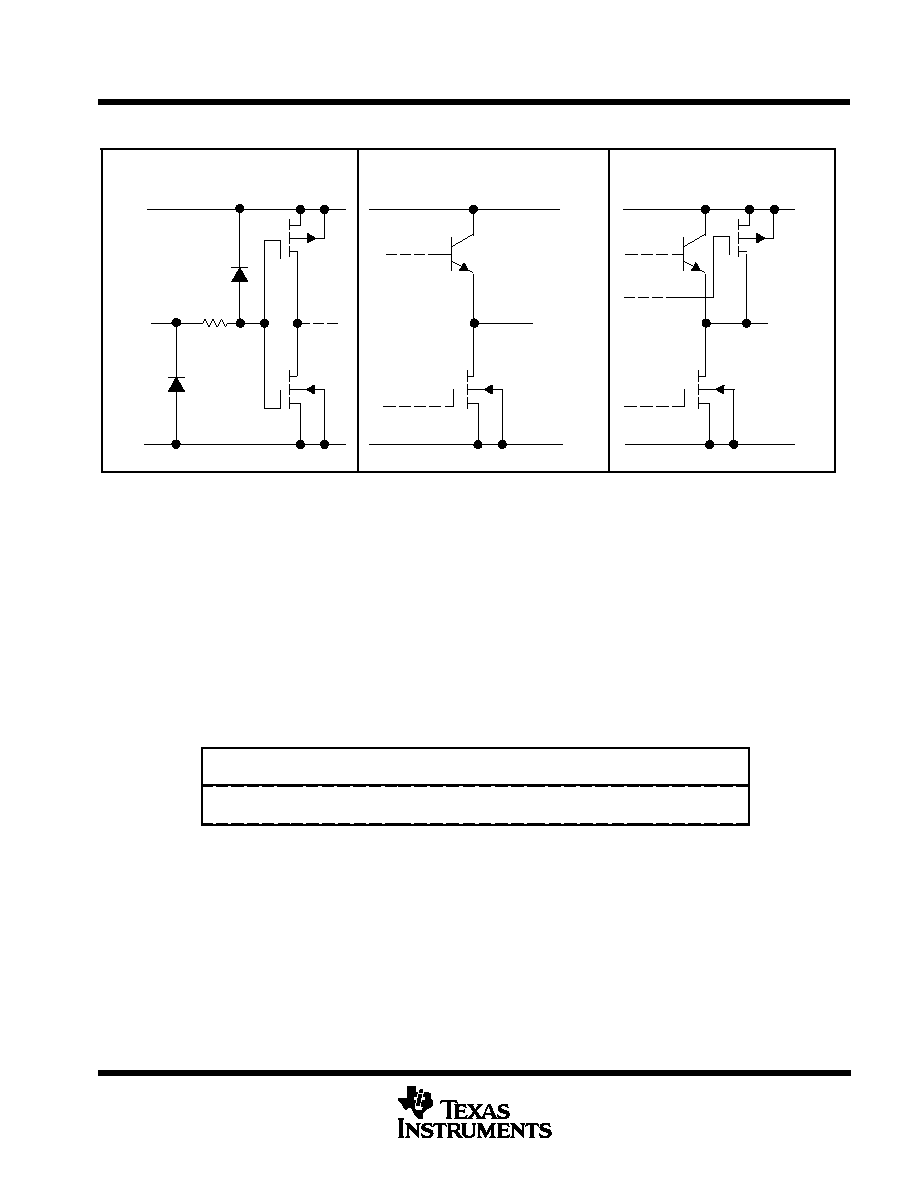

schematic of inputs and outputs

EQUIVALENT OF EACH INPUT

TYPICAL OF ALL Q OUTPUTS

TYPICAL OF SERIAL OUTPUT

VCC1

Input

GND

GND

VCC2

Output

VCC1

GND

Output

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, V

CC1

(see Note 1)

15 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage, V

CC2

70 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage, V

I

V

CC1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation

See Dissipation Rating Table

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: SN65518

≠ 40

∞

C to 85

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SN75518

0

∞

C to 70

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

≠ 65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Case temperature for 10 seconds: FN package

260

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N package

260

∞

C

. . . . . . . . . . . . . . . . . . . . .

NOTE 1: Voltage values are with respect to network ground terminal.

DISSIPATION RATING TABLE

PACKAGE

TA

25

∞

C

DERATING FACTOR

TA = 70

∞

C

TA = 85

∞

C

PACKAGE

A

POWER RATING

ABOVE TA = 25

∞

C

A

POWER RATING

A

POWER RATING

FN

1700 mW

13.6 mW/

∞

C

1088 mW

884 mW

N

1250 mW

10.0 mW/

∞

C

800 mW

650 mW

SN65518, SN75518

VACUUM FLUORESCENT DISPLAY DRIVERS

SLDS004B ≠ MARCH 1983 ≠ REVISED MAY 1990

4≠5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

recommended operating conditions, T

A

= 25

∞

C (unless otherwise noted)

MIN

MAX

UNIT

Supply voltage, VCC1

4.5

15

V

Supply voltage, VCC2

0

60

V

High level input voltage VIH (see Figure 1)

VCC1 = 4.5 V

3.5

V

High-level input voltage, VIH (see Figure 1)

VCC1 = 15 V

12

V

Low-level input voltage, VIL (see Figure 1)

≠ 0.3

0.8

V

High-level output current, IOH

≠ 25

mA

Low-level output current, IOL

2

mA

Clock frequency f l k (see Figure 2)

VCC1 = 10 V to 15 V

0

5

MHz

Clock frequency, fclock (see Figure 2)

VCC1 = 4.5 V

0

1

MHz

Pulse duration CLOCK high t (CKH)

VCC1 = 10 V to 15 V

100

ns

Pulse duration, CLOCK high, tw(CKH)

VCC1 = 4.5 V

500

ns

Pulse duration CLOCK low t (CKL)

VCC1 = 10 V to 15 V

100

ns

Pulse duration, CLOCK low, tw(CKL)

VCC1 = 4.5 V

500

ns

Setup time DATA IN before CLOCK

t

VCC1 = 10 V to 15 V

75

ns

Setup time, DATA IN before CLOCK

, tsu

VCC1 = 4.5 V

150

ns

Hold time DATA IN after CLOCK

th

VCC1 = 10 V to 15 V

75

ns

Hold time, DATA IN after CLOCK

, th

VCC1 = 4.5 V

150

ns

Operating free air temperature TA

SN65518

≠ 40

85

∞

C

Operating free-air temperature, TA

SN75518

0

70

∞

C

electrical characteristics over recommended ranges of operating free-air temperature and V

CC1

,

V

CC2

= 60 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VIK

Input clamp voltage

II = ≠ 12 mA

≠ 1.5

V

VOH

High level output voltage

Q outputs

IOH = ≠ 25 mA

57.5

58

V

VOH

High-level output voltage

SERIAL OUT

VCC1 = 5 V,

IOH = ≠ 20

µ

A

4.5

4.9

5

V

VOL

Low level output voltage

Q outputs

IOL = 1 mA

5

V

VOL

Low-level output voltage

SERIAL OUT

IOL = 20

µ

A

0.06

0.8

V

IIH

High-level input current

VCC1 = 15 V,

VI = 15 V

0.1

1

µ

A

IIL

Low-level input current

VCC1 = 15 V,

VI = 0 V

≠ 0.1

≠ 1

µ

A

ICC1

Supply current

VCC1 = 4.5 V

1.8

4

mA

ICC1

Supply current

VCC1 = 15 V

2

5

mA

SN65518

Outputs high,

TA = ≠ 40

∞

C

12

ICC2

Supply current

SN65518,

Outputs high,

TA = 0

∞

C to MAX

7

10

mA

SN75518

Outputs low

0.01

0.5

All typical values are at TA = 25

∞

C.