SN54HC132, SN74HC132 (Rev. E)

SN54HC132, SN74HC132

QUADRUPLE POSITIVE NAND GATES

WITH SCHMITT TRIGGER INPUTS

SCLS034E - DECEMBER 1982 - REVISED JULY 2003

1

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

D

Wide Operating Voltage Range of 2 V to 6 V

D

Outputs Can Drive Up To 10 LSTTL Loads

D

Low Power Consumption, 20-

µ

A Max I

CC

D

Typical t

pd

= 14 ns

D

±

4-mA Output Drive at 5 V

D

Low Input Current of 1

µ

A Max

D

Operation From Very Slow Input

Transitions

D

Temperature-Compensated Threshold

Levels

D

High Noise Immunity

D

Same Pinouts as 'HC00

description/ordering information

Each circuit functions as a NAND gate, but

because of the Schmitt action, it has different input

threshold levels for positive- and negative-going

signals. The 'HC132 devices perform the Boolean

function Y = A

·

B or Y = A + B in positive logic.

These circuits are temperature compensated and

can be triggered from the slowest of input ramps

and still give clean jitter-free output signals.

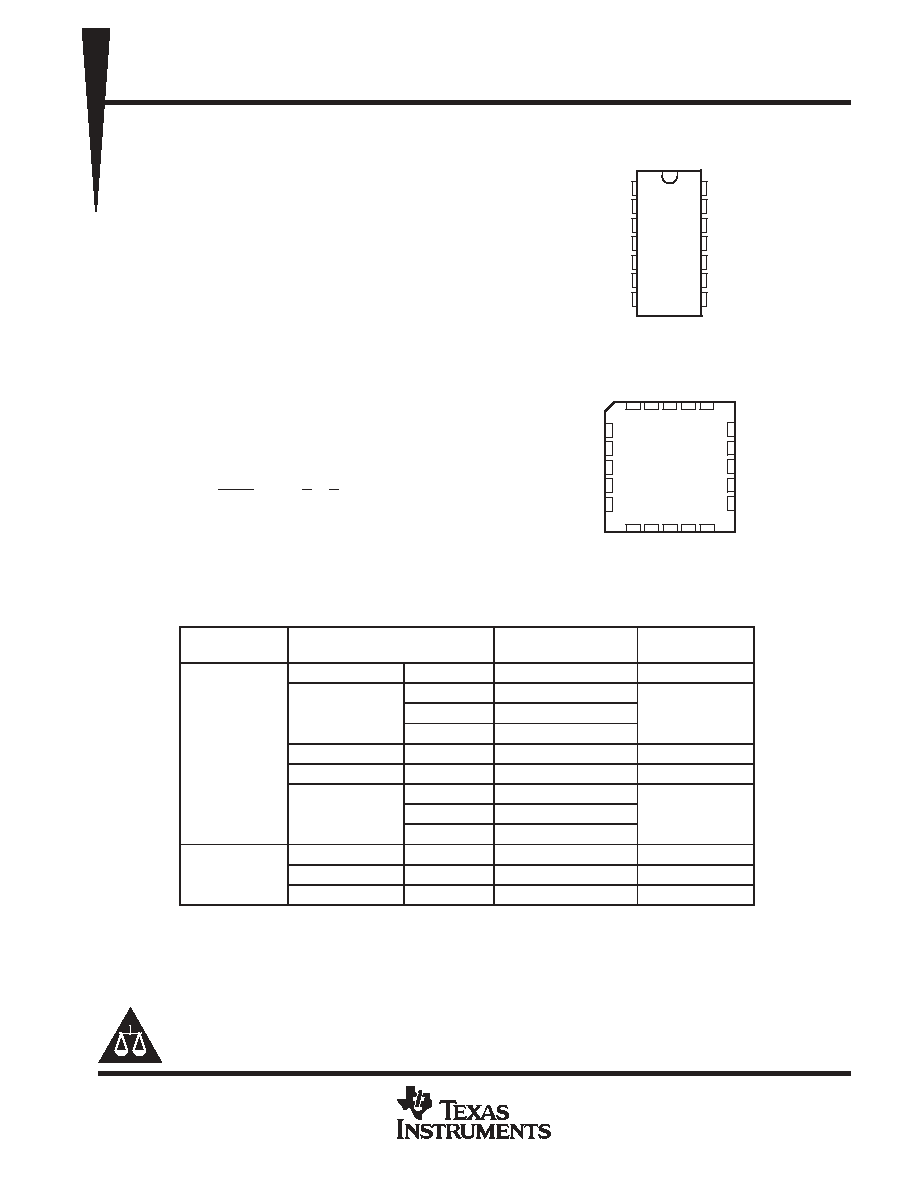

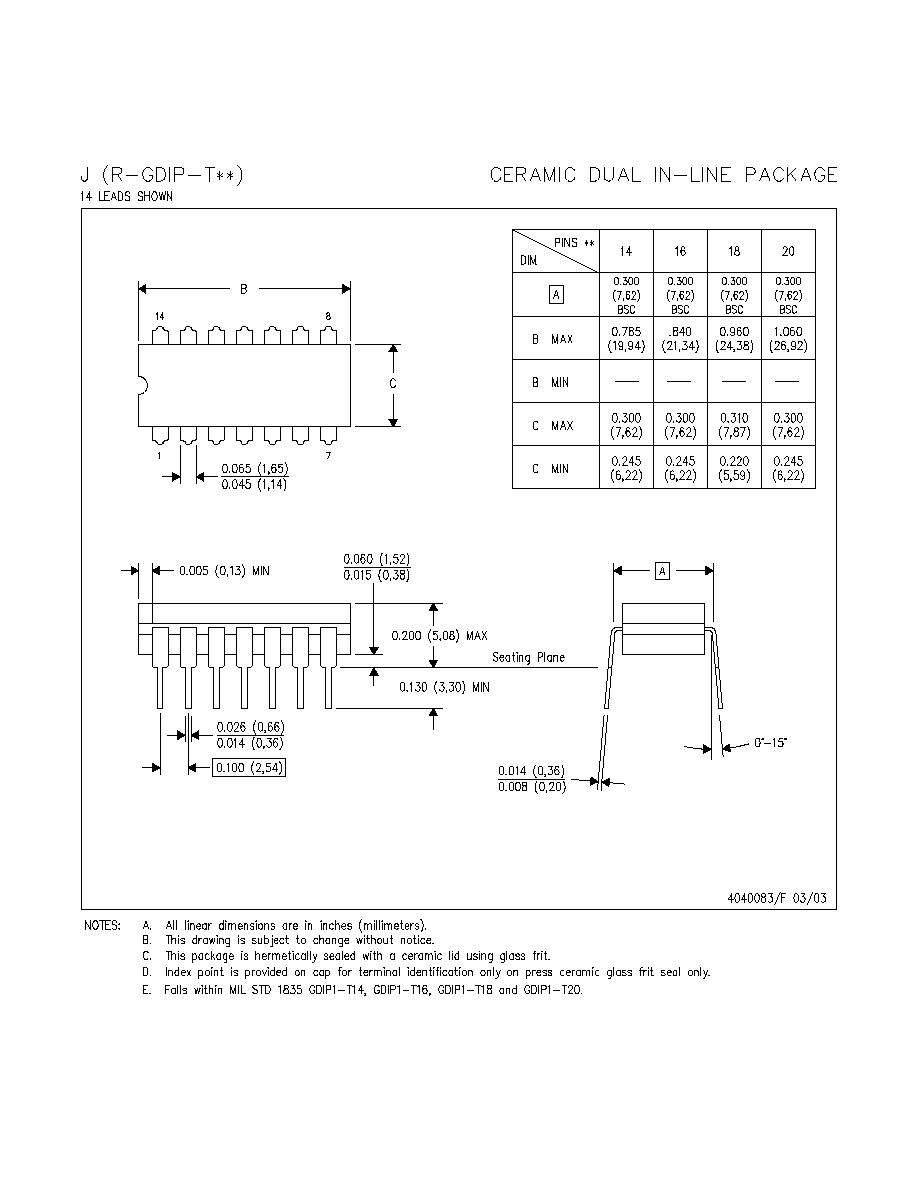

ORDERING INFORMATION

TA

PACKAGE

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

PDIP - N

Tube of 25

SN74HC132N

SN74HC132N

Tube of 50

SN74HC132D

SOIC - D

Reel of 2500

SN74HC132DR

HC132

SOIC - D

Reel of 250

SN74HC132DT

HC132

-40

°

C to 85

°

C

SOP - NS

Reel of 2000

SN74HC132NSR

HC132

-40 C to 85 C

SSOP - DB

Reel of 2000

SN74HC132DBR

HC132

Tube of 90

SN74HC132PW

TSSOP - PW

Reel of 2000

SN74HC132PWR

HC132

TSSOP - PW

Reel of 250

SN74HC132PWT

HC132

CDIP - J

Tube of 25

SNJ54HC132J

SNJ54HC132J

-55

°

C to 125

°

C

CFP - W

Tube of 150

SNJ54HC132W

SNJ54HC132W

-55 C to 125 C

LCCC - FK

Tube of 55

SNJ54HC132FK

SNJ54HC132FK

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are

available at www.ti.com/sc/package.

Copyright

2003, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

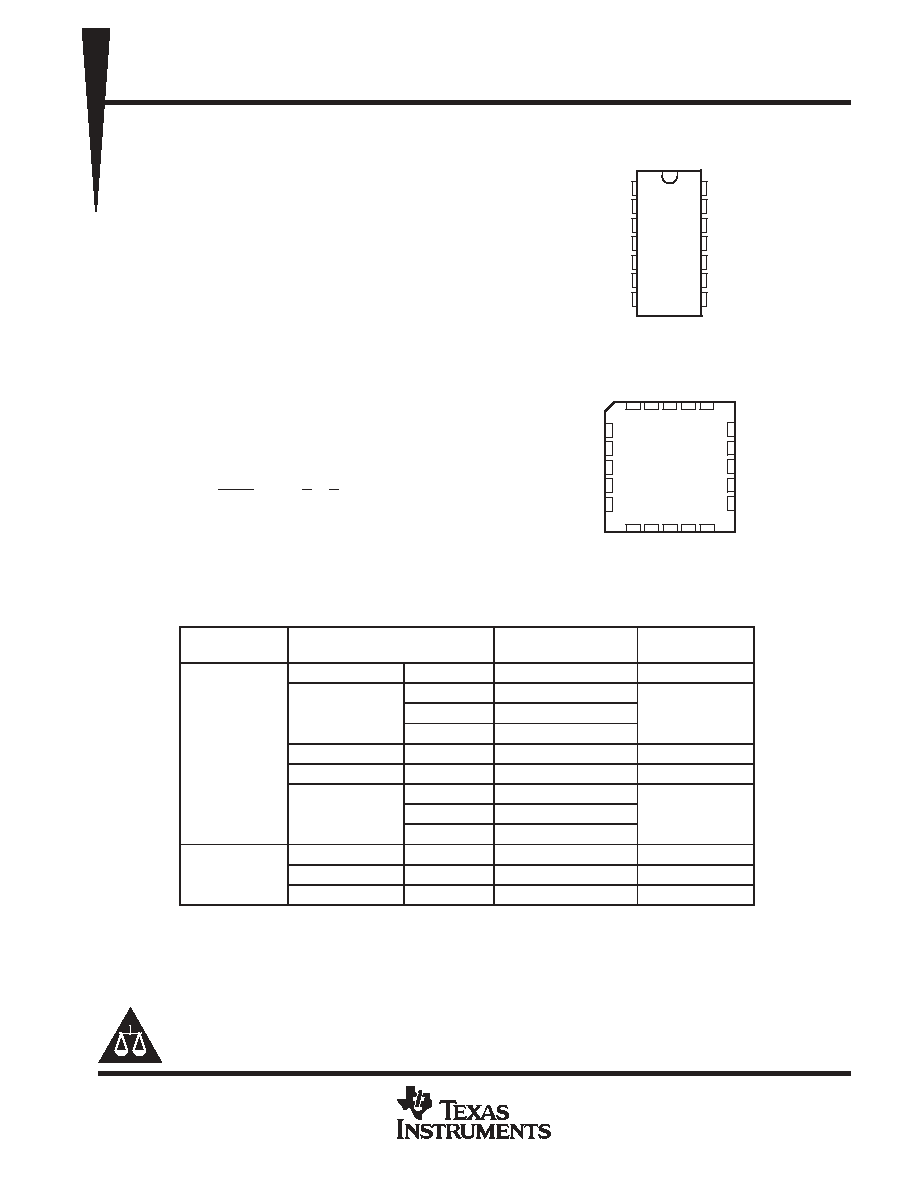

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2A

2B

2Y

GND

V

CC

4B

4A

4Y

3B

3A

3Y

SN54HC132 . . . J OR W PACKAGE

SN74HC132 . . . D, DB, N, NS, OR PW PACKAGE

(TOP VIEW)

3

2 1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

4A

NC

4Y

NC

3B

1Y

NC

2A

NC

2B

1B

1A

NC

3Y

3A

V

4B

2Y

GND

NC

SN54HC132 . . . FK PACKAGE

(TOP VIEW)

CC

NC - No internal connection

On products compliant to MIL PRF 38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

SN54HC132, SN74HC132

QUADRUPLE POSITIVE NAND GATES

WITH SCHMITT TRIGGER INPUTS

SCLS034E - DECEMBER 1982 - REVISED JULY 2003

2

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

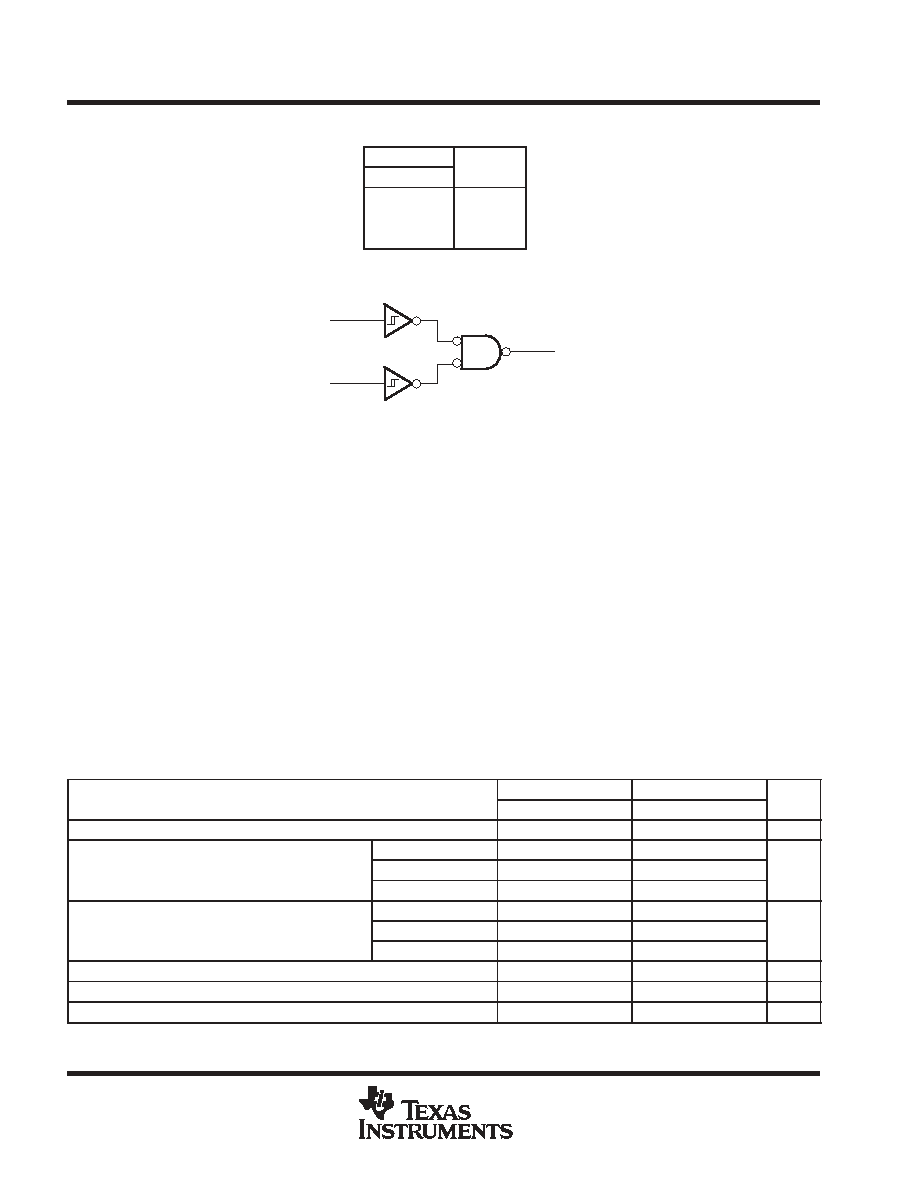

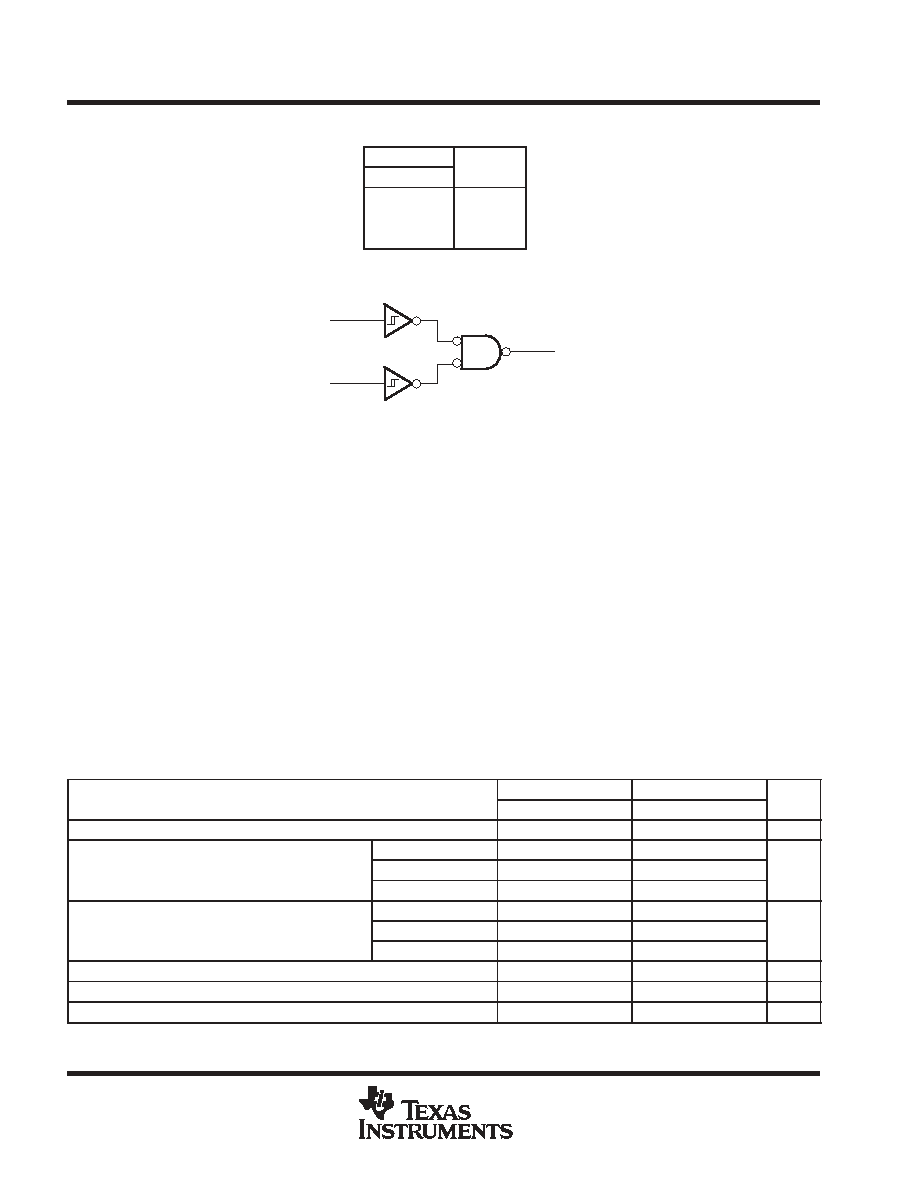

FUNCTION TABLE

(each gate)

INPUTS

OUTPUT

A

B

OUTPUT

Y

H

H

L

L

X

H

X

L

H

logic diagram (positive logic)

A

B

Y

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

CC

-0.5 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, I

IK

(V

I

< 0 or V

I

> V

CC

) (see Note 1)

±

20 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, I

OK

(V

O

< 0 or V

O

> V

CC

) (see Note 1)

±

20 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous output current, I

O

(V

O

= 0 to V

CC

)

±

25 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous current through V

CC

or GND

±

50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance,

JA

(see Note 2): D package

86

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DB package

96

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

N package

80

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NS package

76

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PW package

113

°

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

-65

°

C to 150

°

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES:

1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51-7.

recommended operating conditions (see Note 3)

SN54HC132

SN74HC132

UNIT

MIN

NOM

MAX

MIN

NOM

MAX

UNIT

VCC

Supply voltage

2

5

6

2

5

6

V

VCC = 2 V

1.5

1.5

VIH

High-level input voltage

VCC = 4.5 V

3.15

3.15

V

VIH

High-level input voltage

VCC = 6 V

4.2

4.2

V

VCC = 2 V

0.5

0.5

VIL

Low-level input voltage

VCC = 4.5 V

1.35

1.35

V

VIL

Low-level input voltage

VCC = 6 V

1.8

1.8

V

VI

Input voltage

0

VCC

0

VCC

V

VO

Output voltage

0

VCC

0

VCC

V

TA

Operating free-air temperature

-55

125

-40

85

°

C

NOTE 3: All unused inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

SN54HC132, SN74HC132

QUADRUPLE POSITIVE NAND GATES

WITH SCHMITT TRIGGER INPUTS

SCLS034E - DECEMBER 1982 - REVISED JULY 2003

3

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

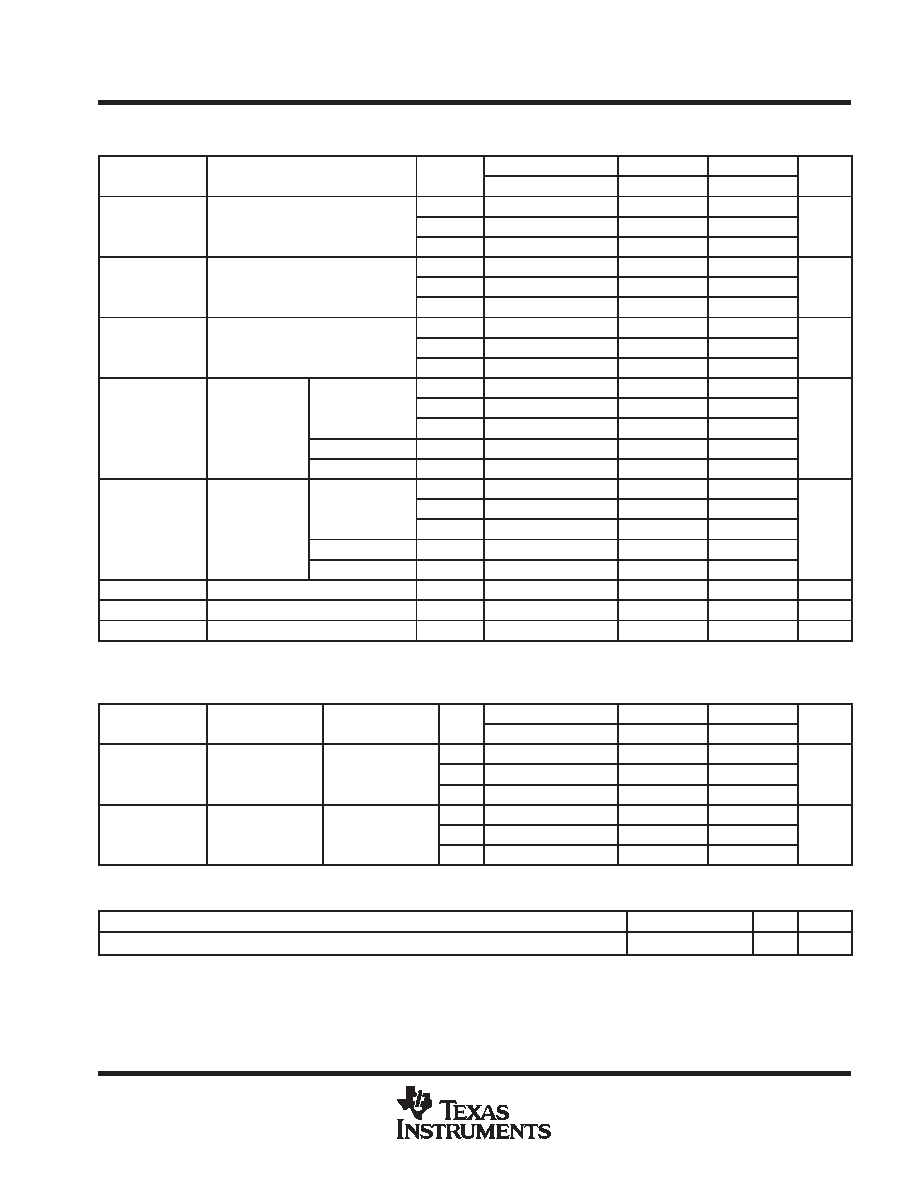

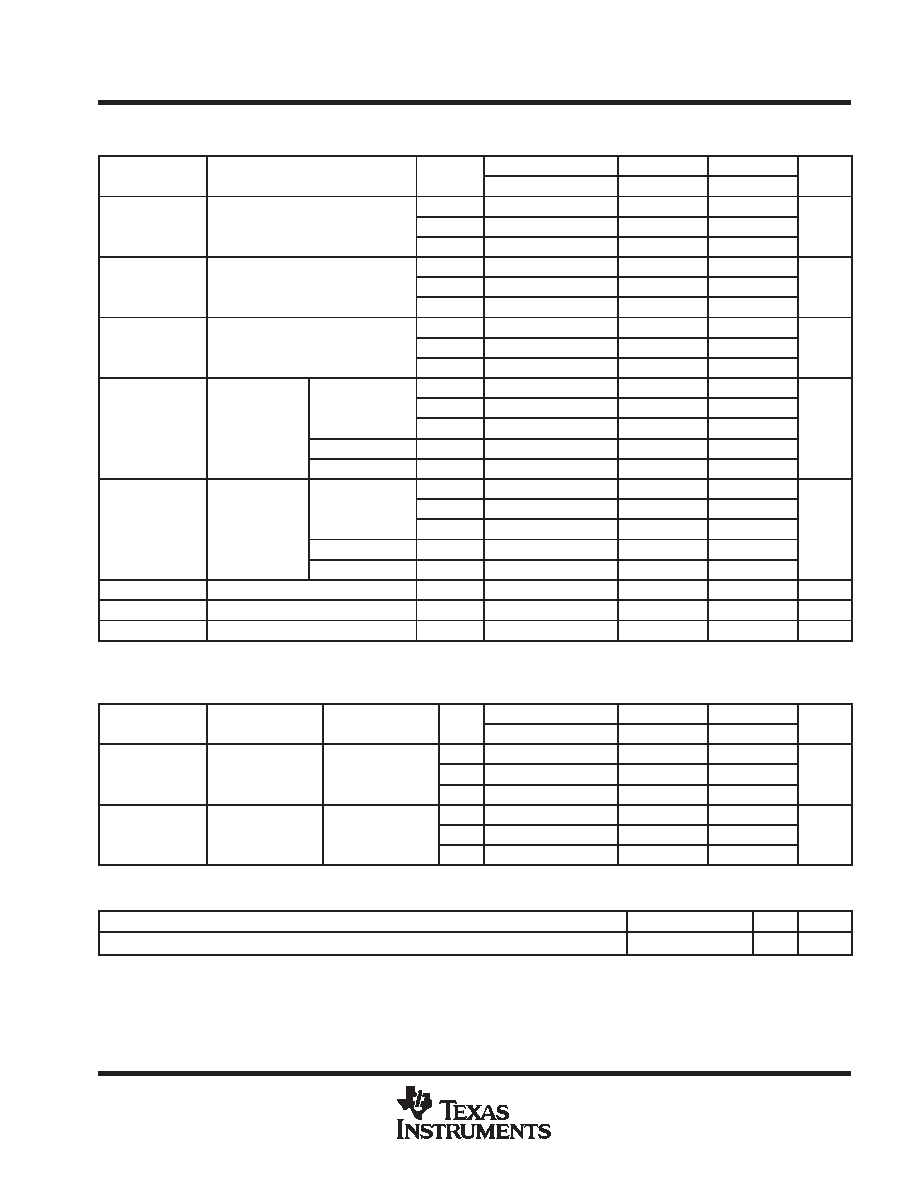

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

VCC

TA = 25

°

C

SN54HC132

SN74HC132

UNIT

PARAMETER

TEST CONDITIONS

VCC

MIN

TYP

MAX

MIN

MAX

MIN

MAX

UNIT

2 V

0.7

1.2

1.5

0.7

1.5

0.7

1.5

VT+

4.5 V

1.55

2.5

3.15

1.55

3.15

1.55

3.15

V

VT+

6 V

2.1

3.3

4.2

2.1

4.2

2.1

4.2

V

2 V

0.3

0.6

1

0.3

1

0.3

1

VT-

4.5 V

0.9

1.6

2.45

0.9

2.45

0.9

2.45

V

VT-

6 V

1.2

2

3.2

1.2

3.2

1.2

3.2

V

2 V

0.2

0.6

1.2

0.2

1.2

0.2

1.2

VT+ - VT-

4.5 V

0.4

0.9

2.1

0.4

2.1

0.4

2.1

V

VT+ - VT-

6 V

0.5

1.3

2.5

0.5

2.5

0.5

2.5

V

2 V

1.9

1.998

1.9

1.9

IOH = -20

µ

A

4.5 V

4.4

4.499

4.4

4.4

VOH

VI = VIH or VIL

IOH = -20

µ

A

6 V

5.9

5.999

5.9

5.9

V

VOH

VI = VIH or VIL

IOH = -4 mA

4.5 V

3.98

4.3

3.7

3.84

V

IOH = -5.2 mA

6 V

5.48

5.8

5.2

5.34

2 V

0.002

0.1

0.1

0.1

IOL = 20

µ

A

4.5 V

0.001

0.1

0.1

0.1

VOL

VI = VIH or VIL

IOL = 20

µ

A

6 V

0.001

0.1

0.1

0.1

V

VOL

VI = VIH or VIL

IOL = 4 mA

4.5 V

0.17

0.26

0.4

0.33

V

IOL = 5.2 mA

6 V

0.15

0.26

0.4

0.33

II

VI = VCC or 0

6 V

±

0.1

±

100

±

1000

±

1000

nA

ICC

VI = VCC or 0,

IO = 0

6 V

2

40

20

µ

A

Ci

2 V to 6 V

3

10

10

10

pF

switching characteristics over recommended operating free-air temperature range, C

L

= 50 pF

(unless otherwise noted) (see Figure 1)

PARAMETER

FROM

TO

VCC

TA = 25

°

C

SN54HC132

SN74HC132

UNIT

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

VCC

MIN

TYP

MAX

MIN

MAX

MIN

MAX

UNIT

2 V

60

120

186

156

tpd

A or B

Y

4.5 V

18

25

37

31

ns

tpd

A or B

Y

6 V

14

21

32

27

ns

2 V

28

75

110

95

tt

Any

4.5 V

8

15

22

19

ns

tt

Any

6 V

6

13

19

16

ns

operating characteristics, T

A

= 25

°

C

PARAMETER

TEST CONDITIONS

TYP

UNIT

Cpd

Power dissipation capacitance per gate

No load

20

pF

SN54HC132, SN74HC132

QUADRUPLE POSITIVE NAND GATES

WITH SCHMITT TRIGGER INPUTS

SCLS034E - DECEMBER 1982 - REVISED JULY 2003

4

POST OFFICE BOX 655303

·

DALLAS, TEXAS 75265

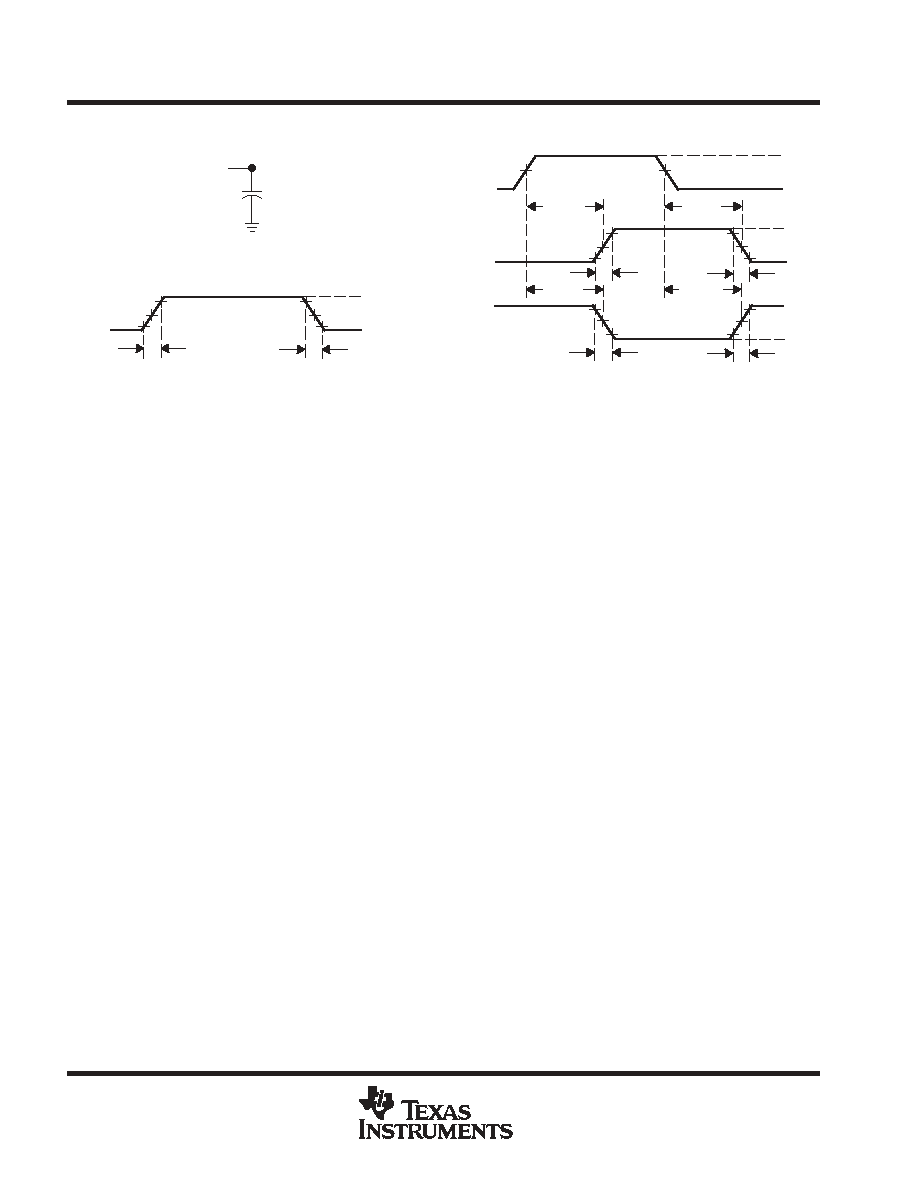

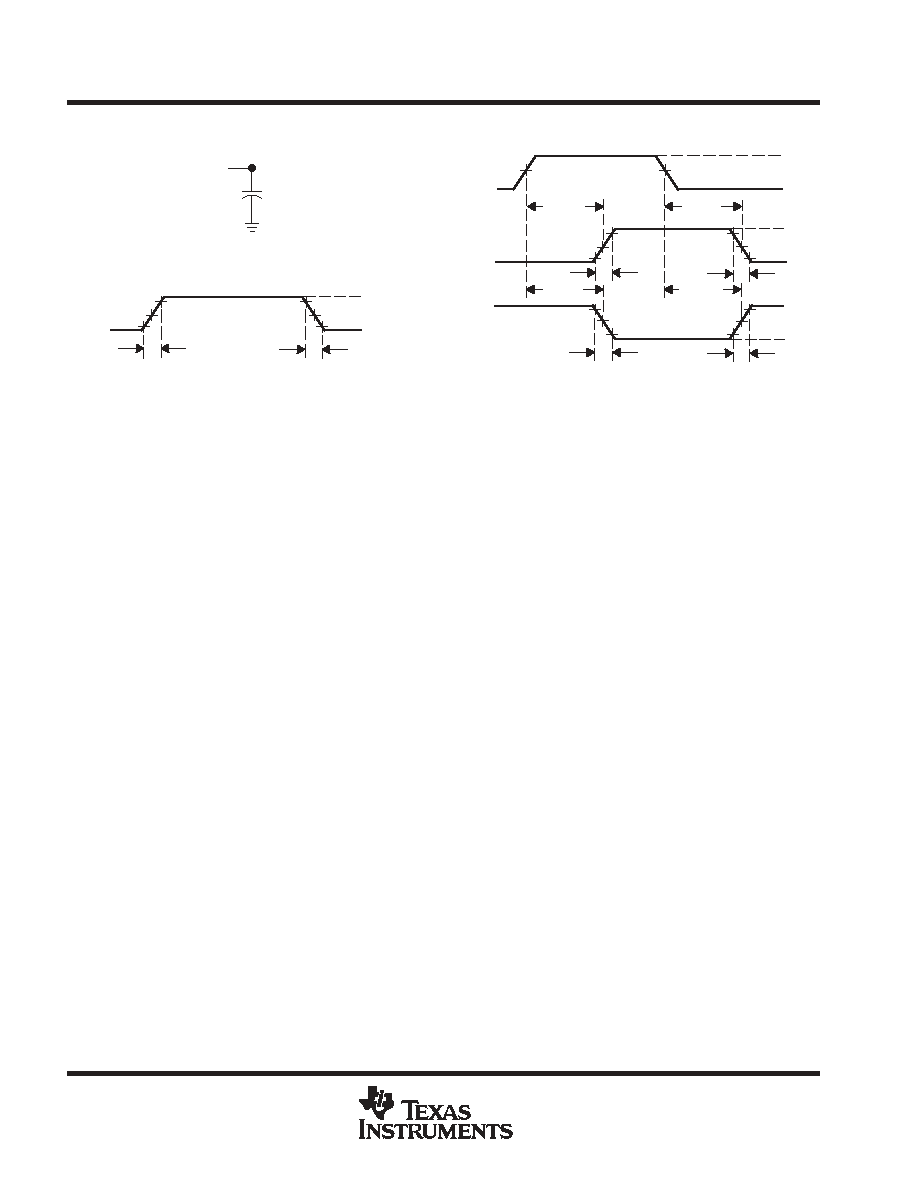

PARAMETER MEASUREMENT INFORMATION

VOLTAGE WAVEFORM

INPUT RISE AND FALL TIMES

50%

50%

10%

10%

90%

90%

VCC

0 V

tr

tf

Input

VOLTAGE WAVEFORMS

PROPAGATION DELAY AND OUTPUT TRANSITION TIMES

50%

50%

50%

10%

10%

90%

90%

VCC

VOH

VOL

0 V

tr

tf

Input

In-Phase

Output

50%

tPLH

tPHL

50%

50%

10%

10%

90%

90%

VOH

VOL

tr

tf

tPHL

tPLH

Out-of-Phase

Output

Test

Point

From Output

Under Test

CL = 50 pF

(see Note A)

LOAD CIRCUIT

NOTES: A. CL includes probe and test-fixture capacitance.

B. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following

characteristics: PRR

1 MHz, ZO = 50

, tr = 6 ns, tf = 6 ns.

C. The outputs are measured one at a time with one input transition per measurement.

D. tPLH and tPHL are the same as tpd.

Figure 1. Load Circuit and Voltage Waveforms