Document Outline

- FEATURES

- APPLICATIONS

- DESCRIPTION

- RELATED DEVICES

- ABSOLUTE MAXIMUM RATINGS

- PACKAGE DISSIPATION RATINGS

- RECOMMENDED OPERATING CONDITIONS

- PACKAGE/ORDERING INFORMATION

- PIN ASSIGNMENTS

- ELECTRICAL CHARACTERISTICS VS = +/-5V

- ELECTRICAL CHARACTERISTICS VS = 5V

- TYPICAL CHARACTERISTICS

- Table of Graphs (+/-5 V)

- Table of Graphs (5 V)

- TYPICAL CHARACTERISTICS (+/-5 V Graphs)

- TYPICAL CHARACTERISTICS (5 V Graphs)

- APPLICATION INFORMATION

- FULLY DIFFERENTIAL AMPLIFIERS

- FULLY DIFFERENTIAL AMPLIFIER TERMINAL FUNCTIONS

- INPUT COMMON-MODE VOLTAGE RANGE AND THE THS4500 FAMILY

- CHOOSING THE PROPER VALUE FOR THE FEEDBACK AND GAIN RESISTORS

- APPLICATION CIRCUITS USING FULLY DIFFERENTIAL AMPLIFIERS

- BASIC DESIGN CONSIDERATIONS

- INTERFACING TO AN ANALOG-TO-DIGITAL CONVERTER

- EXAMPLE ANALOG-TO-DIGITAL CONVERTER DRIVER CIRCUITS

- FULLY DIFFERENTIAL LINE DRIVERS

- FILTERING WITH FULLY DIFFERENTIAL AMPLIFIERS

- SETTING THE OUTPUT COMMON-MODE VOLTAGE WITH THE VOCM INPUT

- SAVING POWER WITH POWER-DOWN FUNCTIONALITY

- LINEARITY: DEFINITIONS, TERMINOLOGY, CIRCUIT TECHNIQUES, AND DESIGN TRADEOFFS

- AN ANALYSIS OF NOISE IN FULLY DIFFERENTIAL AMPLIFIERS

- PRINTED-CIRCUIT BOARD LAYOUT TECHNIQUES FOR OPTIMAL PERFORMANCE

- PowerPAD DESIGN CONSIDERATIONS

- PowerPAD PCB LAYOUT CONSIDERATIONS

- POWER DISSIPATION AND THERMAL CONSIDERATIONS

- DRIVING CAPACITIVE LOADS

- POWER SUPPLY DECOUPLING TECHNIQUES AND RECOMMENDATIONS

- EVALUATION FIXTURES, SPICE MODELS, AND APPLICATIONS SUPPORT

- ADDITIONAL REFERENCE MATERIAL

THS4500

THS4501

SLOS350D - APRIL 2002 - REVISED JANUARY 2004

WIDEBAND, LOW DISTORTION FULLY DIFFERENTIAL AMPLIFIERS

DGK-8

DGN-8

D-8

FEATURES

D

Fully Differential Architecture

D

Bandwidth: 370 MHz

D

Slew Rate: 2800 V/

µ

s

D

IMD

3

: -90 dBc at 30 MHz

D

OIP

3

: 49 dBm at 30 MHz

D

Output Common-Mode Control

D

Wide Power Supply Voltage Range: 5 V,

±

5 V,

12 V, 15 V

D

Input Common-Mode Range Shifted to

Include the Negative Power Supply Rail

D

Power-Down Capability (THS4500)

D

Evaluation Module Available

DESCRIPTION

The THS4500 and THS4501 are high-performance fully

differential amplifiers from Texas Instruments. The

THS4500, featuring power-down capability, and the

THS4501, without power-down capability, set new

performance standards for fully differential amplifiers

with unsurpassed linearity, supporting 14-bit operation

through 40 MHz. Package options include the 8-pin

SOIC and the 8-pin MSOP with PowerPAD

for a

smaller footprint, enhanced ac performance, and

improved thermal dissipation capability.

APPLICATIONS

D

High Linearity Analog-to-Digital Converter

Preamplifier

D

Wireless Communication Receiver Chains

D

Single-Ended to Differential Conversion

D

Differential Line Driver

D

Active Filtering of Differential Signals

1

2

3

4

8

7

6

5

VIN-

VIN+

VOCM

VS+

VOUT+

PD

VS-

VOUT-

RELATED DEVICES

DEVICE(1)

DESCRIPTION

THS4500/1

370 MHz, 2800 V/

µ

s, VICR Includes VS-

THS4502/3

370 MHz, 2800 V/

µ

s, Centered VICR

THS4120/1

3.3 V, 100 MHz, 43 V/

µ

s, 3.7 nV

Hz

THS4130/1

±

15 V, 150 MHz, 51 V/

µ

s, 1.3 nV

Hz

THS4140/1

±

15 V, 160 MHz, 450 V/

µ

s, 6.5 nV

Hz

THS4150/1

±

15 V, 150 MHz, 650 V/

µ

s, 7.6 nV

Hz

(1) Even numbered devices feature power-down capability

APPLICATION CIRCUIT DIAGRAM

f - Frequency - MHz

-80

-92

10

20

40

60

- Third-Order Intermodulation Distortion - dBc

-74

THIRD-ORDER INTERMODULATION

DISTORTION

-62

80

100

-68

-86

-98

12

10

14

16

IMD

3

Bits

V

S

392

+

-

-

+

800

V

S+

V

OUT

392

402

56.2

50

374

VOCM

2.5 V

V

S-

30

50

70

90

VS = 5 V

VS =

±

5 V

-

+

-

+

VOCM

12 Bit/80 MSps

IN

IN

5 V

Vref

5 V

VS

0.1

µ

F

10

µ

F

392

10 pF

1

µ

F

56.2

ADC

374

50

402

392

10 pF

24.9

24.9

PowerPAD is a trademark of Texas Instruments.

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA

information current as of publication date. Products conform to specifications per

the terms of Texas Instruments standard warranty. Production processing does

not necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

semiconductor products and disclaimers thereto appears at the end of this data sheet.

www.ti.com

Copyright

2002-2004, Texas Instruments Incorporated

THS4500

THS4501

SLOS350D - APRIL 2002 - REVISED JANUARY 2004

www.ti.com

2

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted(1)

UNIT

Supply voltage, V

S

16.5 V

Input voltage, V

I

±

V

S

Output current, I

O

(2)

150 mA

Differential input voltage, V

ID

4 V

Continuous power dissipation See Dissipation Rating Table

Maximum junction temperature, T

J

(3)

150

∞

C

Maximum junction temperature, continuous

operation, long term reliability T

J

(4)

125

∞

C

Operating free-air temperature

C suffix

0

∞

C to 70

∞

C

Operating free-air temperature

range, T

A

I suffix

-40

∞

C to 85

∞

C

Storage temperature range, T

stg

-65

∞

C to 150

∞

C

Lead temperature

1,6 mm (1/16 inch) from case for 10 seconds

300

∞

C

HBM

4000 V

ESD ratings:

CDM

2000 V

ESD ratings:

MM

100 V

(1)

Stresses above these ratings may cause permanent damage.

Exposure to absolute maximum conditions for extended periods

may degrade device reliability. These are stress ratings only, and

functional operation of the device at these or any other conditions

beyond those specified is not implied.

(2)

The THS4500/1 may incorporate a PowerPAD

on the underside

of the chip. This acts as a heat sink and must be connected to a

thermally dissipative plane for proper power dissipation. Failure

to do so may result in exceeding the maximum junction

temperature which could permanently damage the device. See TI

technical briefs SLMA002 and SLMA004 for more information

about utilizing the PowerPAD thermally enhanced package.

(3)

The absolute maximum temperature under any condition is

limited by the constraints of the silicon process.

(4)

The maximum junction temperature for continuous operation is

limited by package constraints. Operation above this temperature

may result in reduced reliability and/or lifetime of the device.

This integrated circuit can be damaged by ESD. Texas

Instruments recommends that all integrated circuits be

handled with appropriate precautions. Failure to observe

proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to

complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could

cause the device not to meet its published specifications.

PACKAGE DISSIPATION RATINGS

PACKAGE

JC

JA

(1)

POWER RATING(2)

PACKAGE

JC

(

∞

C/W)

JA

(1)

(

∞

C/W)

TA

25

∞

C

TA = 85

∞

C

D (8 pin)

38.3

97.5

1.02 W

410 mW

DGN (8 pin)

4.7

58.4

1.71 W

685 mW

DGK (8 pin)

54.2

260

385 mW

154 mW

(1) This data was taken using the JEDEC standard High-K test PCB.

(2) Power rating is determined with a junction temperature of 125

∞

C.

This is the point where distortion starts to substantially increase.

Thermal management of the final PCB should strive to keep the

junction temperature at or below 125

∞

C for best performance and

long term reliability.

RECOMMENDED OPERATING CONDITIONS

MIN

NOM

MAX

UNIT

Supply voltage

Dual supply

±

5

±

7.5

V

Supply voltage

Single supply

4.5

5

15

V

Operating free-

air temperature,

C suffix

0

70

∞

C

air temperature,

T

A

I suffix

-40

85

∞

C

PACKAGE/ORDERING INFORMATION

ORDERABLE PACKAGE AND NUMBER

TEMPERATURE

PLASTIC

SMALL OUTLINE

PLASTIC MSOP(1)

PowerPad

PLASTIC MSOP(1)

SMALL OUTLINE

(D)

(DGN)

SYMBOL

(DGK)

SYMBOL

0

∞

C to 70

∞

C

THS4500CD

THS4500CDGN

BFB

THS4500CDGK

ATV

0

∞

C to 70

∞

C

THS4501CD

THS4501CDGN

BFD

THS4501CDGK

ATW

-40

∞

C to 85

∞

C

THS4500ID

THS4500IDGN

BFC

THS4500IDGK

ASV

-40

∞

C to 85

∞

C

THS4501ID

THS4501IDGN

BFE

THS4501IDGK

ASW

(1) All packages are available taped and reeled. The R suffix standard quantity is 2500. The T suffix standard quantity is 250 (e.g., THS4501DT).

THS4500

THS4501

SLOS350D - APRIL 2002 - REVISED JANUARY 2004

www.ti.com

3

PIN ASSIGNMENTS

THS4501

(TOP VIEW)

V

IN-

1

2

3

4

8

7

6

5

V

OCM

V

S+

V

OUT+

V

IN+

V

S-

V

OUT-

PD

D, DGN, DGK

THS4500

(TOP VIEW)

D, DGN, DGK

V

IN-

1

2

3

4

8

7

6

5

V

OCM

V

S+

V

OUT+

V

IN+

V

S-

V

OUT-

NC

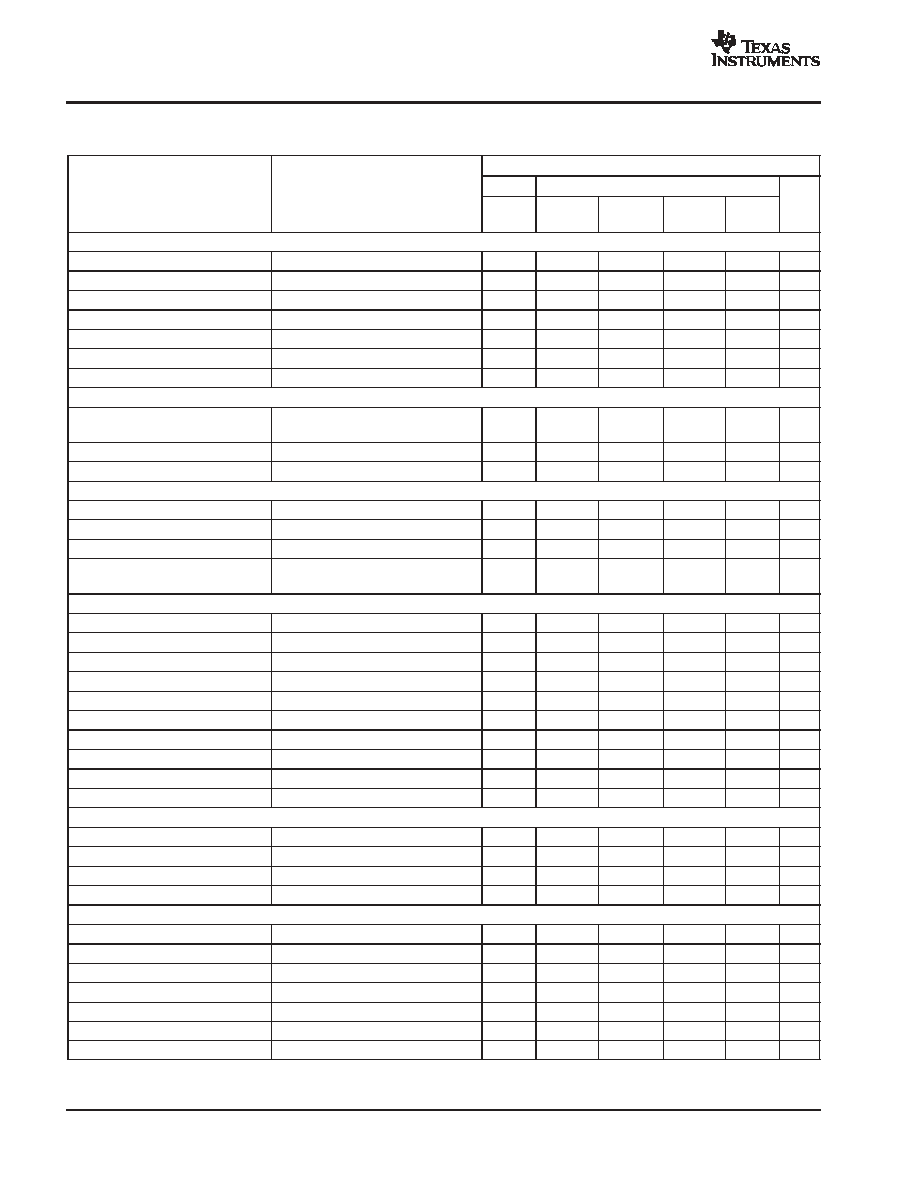

ELECTRICAL CHARACTERISTICS V

S

=

±

5 V

R

f

= R

g

= 392

, R

L

= 800

, G = +1, Single-ended input unless otherwise noted.

THS4500 AND THS4501

PARAMETER

TEST CONDITIONS

TYP

OVER TEMPERATURE

MIN/

PARAMETER

TEST CONDITIONS

25

∞

C

25

∞

C

0

∞

C to

70

∞

C

-40

∞

C to

85

∞

C

UNITS

MIN/

TYP/

MAX

AC PERFORMANCE

G = +1, PIN= -20 dBm, Rf = 392

370

MHz

Typ

Small-signal bandwidth

G = +2, PIN= -30 dBm, Rf = 1 k

175

MHz

Typ

Small-signal bandwidth

G = +5, PIN= -30 dBm, Rf = 2.4 k

70

MHz

Typ

G = +10, PIN = -30 dBm, Rf = 5.1 k

30

MHz

Typ

Gain-bandwidth product

G > +10

300

MHz

Typ

Bandwidth for 0.1dB flatness

PIN = -20 dBm

150

MHz

Typ

Large-signal bandwidth

VP = 2 V

220

MHz

Typ

Slew rate

4 VPP Step

2800

V/

µ

s

Typ

Rise time

2 VPP Step

0.4

ns

Typ

Fall time

2 VPP Step

0.5

ns

Typ

Settling time to 0.01%

VO = 4 VPP

8.3

ns

Typ

0.1%

VO = 4 VPP

6.3

ns

Typ

Harmonic distortion

G = +1, VO = 2 VPP

Typ

2nd harmonic

f = 8 MHz

-82

dBc

Typ

2nd harmonic

f = 30 MHz

-71

dBc

Typ

3rd harmonic

f = 8 MHz

-97

dBc

Typ

3rd harmonic

f = 30 MHz

-74

dBc

Typ

Third-order intermodulation

distortion

VO = 2 VPP, fc = 30 MHz,

Rf = 392

, 200 kHz tone spacing

-90

dBc

Typ

Third-order output intercept point

fc = 30 MHz, Rf = 392

,

Referenced to 50

49

dBm

Typ

Input voltage noise

f > 1 MHz

7

nV/

Hz

Typ

Input current noise

f > 100 kHz

1.7

pA/

Hz

Typ

Overdrive recovery time

Overdrive = 5.5 V

60

ns

Typ

THS4500

THS4501

SLOS350D - APRIL 2002 - REVISED JANUARY 2004

www.ti.com

4

ELECTRICAL CHARACTERISTICS V

S

=

±

5 V

R

f

= R

g

= 392

, R

L

= 800

, G = +1, Single-ended input unless otherwise noted (continued).

THS4500 AND THS4501

PARAMETER

TEST CONDITIONS

TYP

OVER TEMPERATURE

MIN/

PARAMETER

TEST CONDITIONS

25

∞

C

25

∞

C

0

∞

C to

70

∞

C

-40

∞

C to

85

∞

C

UNITS

MIN/

TYP/

MAX

DC PERFORMANCE

Open-loop voltage gain

55

52

50

50

dB

Min

Input offset voltage

-4

-7 / -1

-8 / 0

-9 / +1

mV

Max

Average offset voltage drift

±

10

±

10

µ

V/

∞

C

Typ

Input bias current

4

4.6

5

5.2

µ

A

Max

Average bias current drift

±

10

±

10

nA/

∞

C

Typ

Input offset current

0.5

1

2

2

µ

A

Max

Average offset current drift

±

40

±

40

nA/

∞

C

Typ

INPUT

Common-mode input range

-5.7/2.

6

-5.4 / 2.3

-5.1 / 2

-5.1 / 2

V

Min

Common-mode rejection ratio

80

74

70

70

dB

Min

Input impedance

107 || 1

|| pF

Typ

OUTPUT

Differential output voltage swing

RL = 1 k

±

8

±

7.6

±

7.4

±

7.4

V

Min

Differential output current drive

RL = 20

120

110

100

100

mA

Min

Output balance error

PIN = -20 dBm, f = 100 kHz

-58

dB

Typ

Closed-loop output impedance

(single-ended)

f = 1 MHz

0.1

Typ

OUTPUT COMMON-MODE VOLTAGE CONTROL

Small-signal bandwidth

RL = 400

180

MHz

Typ

Slew rate

2 VPP step

92

V/

µ

s

Typ

Minimum gain

1

0.98

0.98

0.98

V/V

Min

Maximum gain

1

1.02

1.02

1.02

V/V

Max

Common-mode offset voltage

-0.4

-4.6/+3.8

-6.6/+5.8

-7.6/+6.8

mV

Max

Input bias current

VOCM = 2.5 V

100

150

170

170

µ

A

Max

Input voltage range

±

4

±

3.7

±

3.4

±

3.4

V

Min

Input impedance

25 || 1

k

|| pF

Typ

Maximum default voltage

VOCM left floating

0

0.05

0.10

0.10

V

Max

Minimum default voltage

VOCM left floating

0

-0.05

-0.10

-0.10

V

Min

POWER SUPPLY

Specified operating voltage

±

5

7.5

7.5

7.5

V

Max

Maximum quiescent current

23

28

32

34

mA

Max

Minimum quiescent current

23

18

14

12

mA

Min

Power supply rejection (

±

PSRR)

80

76

73

70

dB

Min

POWER DOWN (THS4500 ONLY)

Enable voltage threshold

Device enabled ON above ≠2.9 V

-2.9

V

Min

Disable voltage threshold

Device disabled OFF below ≠4.3 V

-4.3

V

Max

Power-down quiescent current

800

1000

1200

1200

µ

A

Max

Input bias current

200

240

260

260

µ

A

Max

Input impedance

50 || 1

k

|| pF

Typ

Turnon time delay

1000

ns

Typ

Turnoff time delay

800

ns

Typ

THS4500

THS4501

SLOS350D - APRIL 2002 - REVISED JANUARY 2004

www.ti.com

5

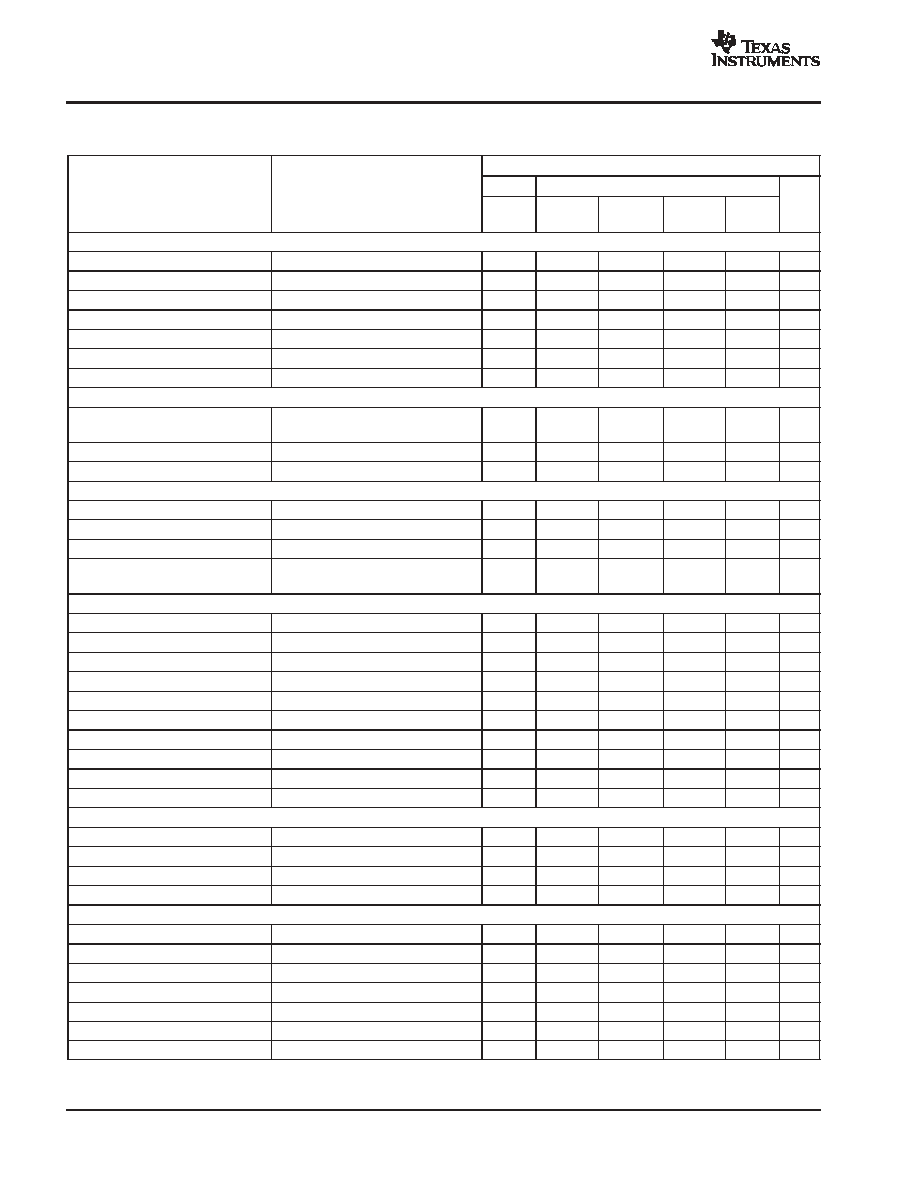

ELECTRICAL CHARACTERISTICS V

S

= 5 V

R

f

= R

g

= 392

, R

L

= 800

, G = +1, Single-ended input unless otherwise noted.

THS4500 AND THS4501

PARAMETER

TEST CONDITIONS

TYP

OVER TEMPERATURE

MIN/

PARAMETER

TEST CONDITIONS

25

∞

C

25

∞

C

0

∞

C to

70

∞

C

-40

∞

C to

85

∞

C

UNITS

MIN/

TYP/

MAX

AC PERFORMANCE

G = +1, PIN = -20 dBm, Rf = 392

320

MHz

Typ

Small-signal bandwidth

G = +2, PIN = -30 dBm, Rf = 1 k

160

MHz

Typ

Small-signal bandwidth

G = +5, PIN = -30 dBm, Rf = 2.4 k

60

MHz

Typ

G = +10, PIN = -30 dBm, Rf = 5.1 k

30

MHz

Typ

Gain-bandwidth product

G > +10

300

MHz

Typ

Bandwidth for 0.1 dB flatness

PIN = -20 dBm

180

MHz

Typ

Large-signal bandwidth

VP = 1 V

200

MHz

Typ

Slew rate

2 VPP Step

1300

V/

µ

s

Typ

Rise time

2 VPP Step

0.5

ns

Typ

Fall time

2 VPP Step

0.6

ns

Typ

Settling time to 0.01%

VO = 2 V Step

13.1

ns

Typ

0.1%

VO = 2 V Step

8.3

ns

Typ

Harmonic distortion

G = +1, VO = 2 VPP

Typ

2nd harmonic

f = 8 MHz,

-80

dBc

Typ

2nd harmonic

f = 30 MHz

-55

dBc

Typ

3rd harmonic

f = 8 MHz

-76

dBc

Typ

3rd harmonic

f = 30 MHz

-60

dBc

Typ

Input voltage noise

f > 1 MHz

7

nV/

Hz

Typ

Input current noise

f > 100 kHz

1.7

pA/

Hz

Typ

Overdrive recovery time

Overdrive = 5.5 V

60

ns

Typ

DC PERFORMANCE

Open-loop voltage gain

54

51

49

49

dB

Min

Input offset voltage

-4

-7 / -1

-8 / 0

-9 / +1

mV

Max

Average offset voltage drift

±

10

±

10

µ

V/

∞

C

Typ

Input bias current

4

4.6

5

5.2

µ

A

Max

Average bias current drift

±

10

±

10

nA/

∞

C

Typ

Input offset current

0.5

0.7

1.2

1.2

µ

A

Max

Average offset current drift

±

20

±

20

nA/

∞

C

Typ

INPUT

Common-mode input range

-0.7/2.

6

-0.4 / 2.3

-0.1 / 2

-0.1 / 2

V

Min

Common-mode rejection ratio

80

74

70

70

dB

Min

Input Impedance

107 || 1

|| pF

Typ

OUTPUT

Differential output voltage swing

RL = 1 k

, Referenced to 2.5 V

±

3.3

±

3

±

2.8

±

2.8

V

Min

Output current drive

RL = 20

100

90

80

80

mA

Min

Output balance error

PIN = -20 dBm, f = 100 kHz

-58

dB

Typ

Closed-loop output impedance

(single-ended)

f = 1 MHz

0.1

Typ