TC51WHM516AXBN65,70

2002-08-22 1/11

∑ Access Times:

TC51WHM516AXBN

65 70

Access Time

65 ns

70 ns

CE1

Access Time

65 ns

70 ns

OE

Access Time

25 ns

25 ns

Page Access Time

30 ns

30 ns

∑ Package:

P-TFBGA48-0607-0.75AZ (Weight: g typ.)

TENTATIVE

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

2,097,152-WORD BY 16-BIT CMOS PSEUDO STATIC RAM

DESCRIPTION

The TC51WHM516AXBN is a 33,554,432-bit pseudo static random access memory(PSRAM) organized as

2,097,152 words by 16 bits. Using Toshiba's CMOS technology and advanced circuit techniques, it provides high

density, high speed and low power. The device operates single power supply. The device also features SRAM-like

W/R timing whereby the device is controlled by CE1 , OE , and WE on asynchronous. The device has the page

access operation. Page size is 8 words. The device also supports deep power-down mode, realizing low-power

standby.

FEATURES

∑ Organized as 2,097,152 words by 16 bits

∑ Single power supply voltage of 2.6 to 3.3 V

∑ Direct TTL compatibility for all inputs and outputs

∑ Deep power-down mode: Memory cell data invalid

∑ Page operation mode:

Page read operation by 8 words

∑ Logic compatible with SRAM R/W ( WE ) pin

∑ Standby current

Standby 70

µA

Deep power-down standby

5 µA

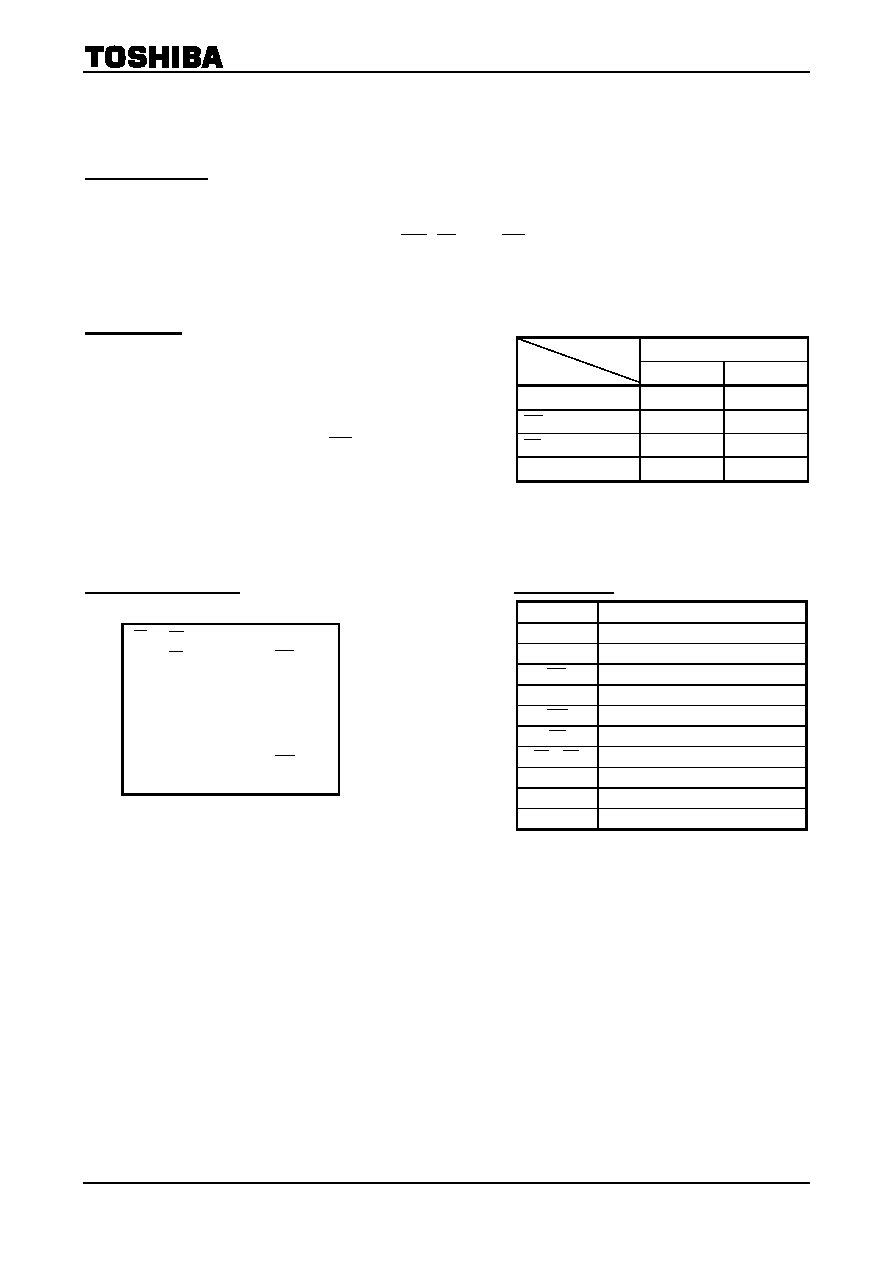

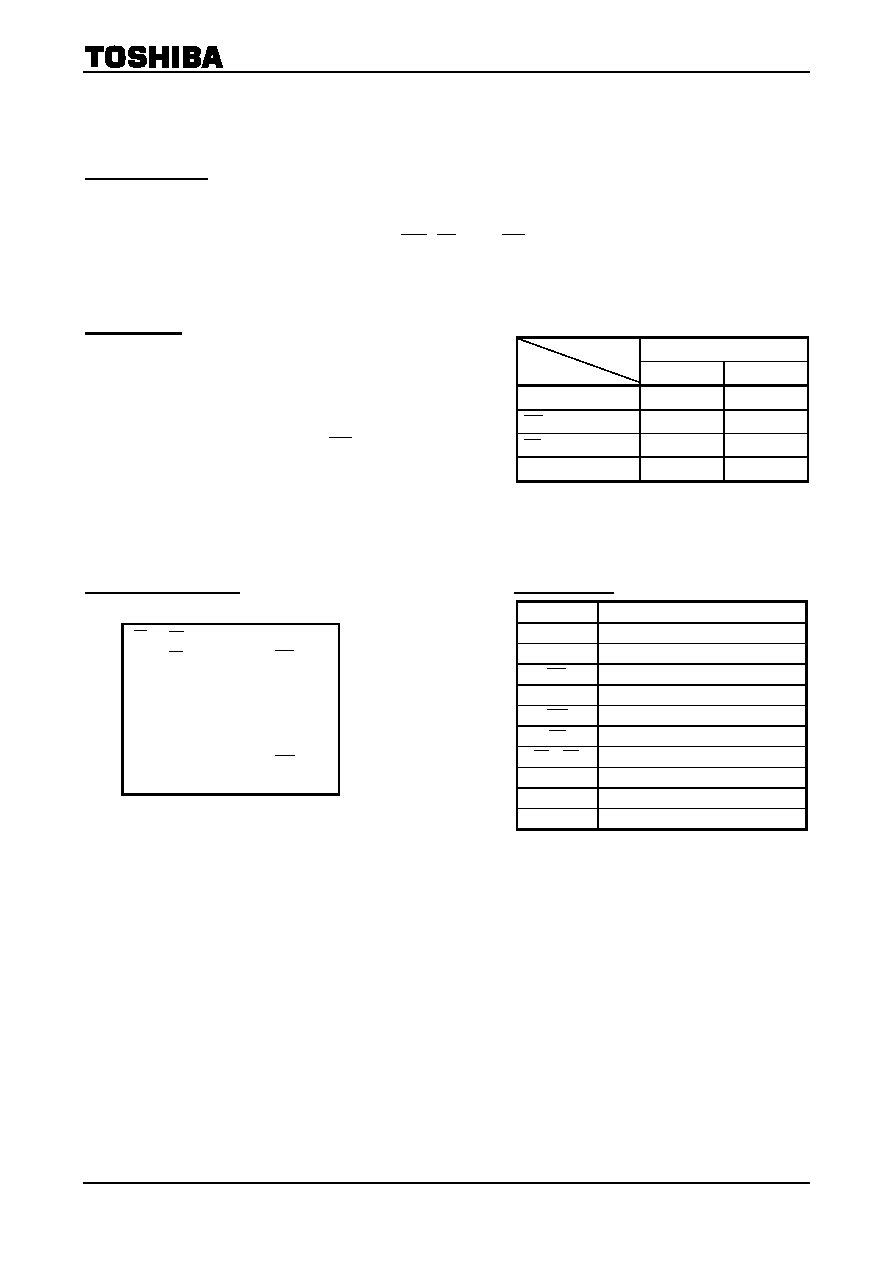

PIN ASSIGNMENT

(TOP VIEW)

PIN NAMES

1 2 3 4 5 6

A

LB

OE A0 A1 A2 CE2

B I/O9 UB A3 A4 CE1 I/O1

C I/O10 I/O11 A5 A6 I/O2 I/O3

D VSS I/O12 A17 A7 I/O4 VDD

E VDD I/O13 NC A16 I/O5 VSS

F I/O15 I/O14 A14 A15 I/O6 I/O7

G I/O16 A19 A12 A13

WE

I/O8

H A18 A8 A9 A10 A11 A20

(FBGA48)

A0 to A20

Address Inputs

A0 to A2

Page Address Inputs

I/O1 to I/O16 Data Inputs/Outputs

CE1

Chip

Enable

Input

CE2

Chip select Input

WE

Write Enable Input

OE

Output Enable Input

LB ,

UB

Data Byte Control Inputs

V

DD

Power

GND Ground

NC No

Connection

TC51WHM516AXBN65,70

2002-08-22 3/11

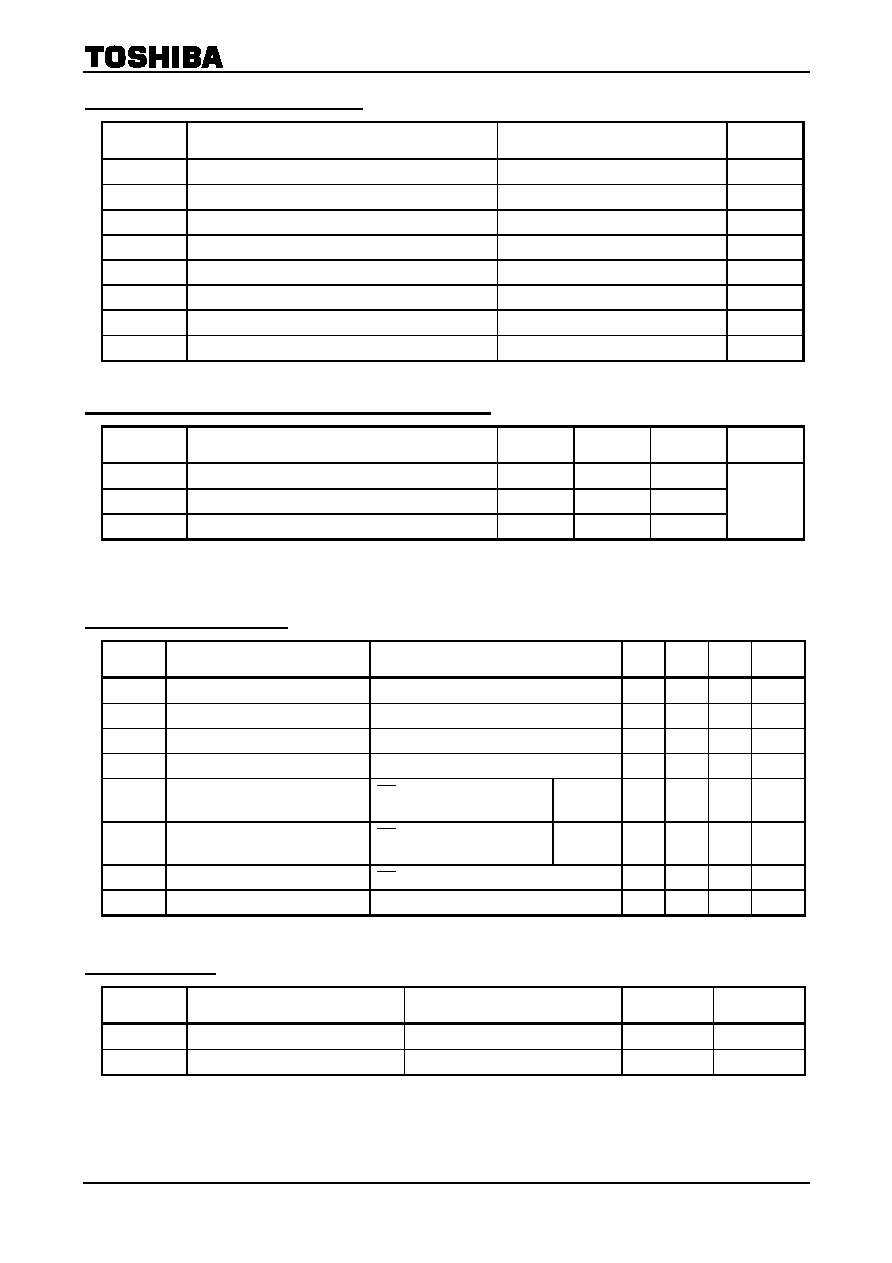

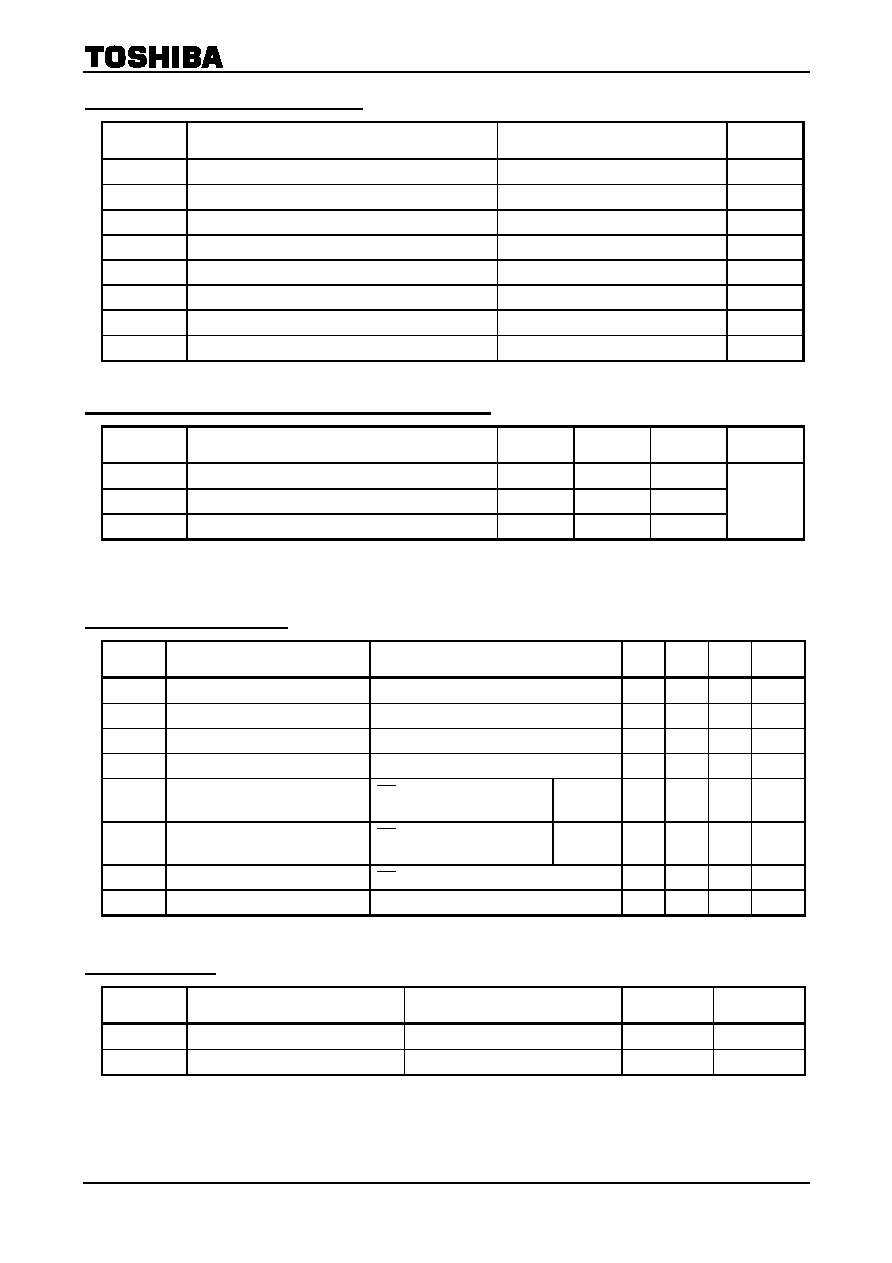

ABSOLUTE MAXIMUM RATINGS (See Note 1)

SYMBOL RATING

VALUE

UNIT

V

DD

Power Supply Voltage

-1.0 to 3.6

V

V

IN

Input Voltage

-1.0 to 3.6

V

V

OUT

Output Voltage

-1.0 to 3.6

V

T

opr.

Operating Temperature

-25 to 85

∞C

T

strg.

Storage Temperature

-55 to 150

∞C

T

solder

Soldering Temperature (10 s)

260

∞C

P

D

Power

Dissipation

0.6

W

I

OUT

Short Circuit Output Current

50

mA

DC RECOMMENDED OPERATING CONDITIONS

(Ta

=

=

=

= ----25∞C to 85∞C)

SYMBOL PARAMETER MIN

TYP.

MAX

UNIT

V

DD

Power Supply Voltage

2.6

2.75

3.3

V

IH

Input High Voltage

2.0

V

DD

+ 0.3*

V

IL

Input Low Voltage

-0.3*

0.4

V

* : V

IH

(Max) V

DD

+1.0 V with 10 ns pulse width

V

IL

(Min) -1.0 V with 10 ns pulse width

DC CHARACTERISTICS

(Ta

=

=

=

= ----25∞C to 85∞C, V

DD

=

=

=

= 2.6 to 3.3 V) (See Note 3 to 4)

SYMBOL PARAMETER

TEST

CONDITION

MIN

TYP.

MAX

UNIT

I

IL

Input Leakage Current

V

IN

= 0 V to V

DD

-1.0

+1.0

µA

I

LO

Output Leakage Current

Output disable, V

OUT

= 0 V to V

DD

-1.0

+1.0

µA

V

OH

Output High Voltage

I

OH

= - 0.5 mA

2.0

V

V

OL

Output Low Voltage

I

OL

= 1.0 mA

0.4 V

I

DDO1

Operating

Current

CE1

= V

IL

CE2

= V

IH

, I

OUT

= 0 mA

t

RC

= min

40 mA

I

DDO2

Page Access Operating Current

CE1

= V

IL

, CE2

= V

IH

,

Page add. cycling, I

OUT

= 0 mA

t

PC

= min

25 mA

I

DDS

Standby

Current(MOS)

CE1

= V

DD

- 0.2 V, CE2 = V

DD

- 0.2 V

70

µA

I

DDSD

Deep Power-down Standby Current

CE2

= 0.2 V

5

µA

CAPACITANCE

(Ta

=

=

=

= 25∞C, f ==== 1 MHz)

SYMBOL PARAMETER

TEST

CONDITION MAX

UNIT

C

IN

Input

Capacitance

V

IN

= GND

10

pF

C

OUT

Output

Capacitance

V

OUT

= GND

10

pF

Note: This parameter is sampled periodically and is not 100% tested.

TC51WHM516AXBN65,70

2002-08-22 4/11

AC CHARACTERISTICS AND OPERATING CONDITIONS

(Ta

=

=

=

= ----25∞C to 85∞C, V

DD

=

=

=

= 2.6 to 3.3 V) (See Note 5 to 11)

TC51WHM516AXBN

65

70

SYMBOL

PARAMETER

MIN

MAX

MIN

MAX

UNIT

t

RC

Read Cycle Time

65

10000

70

10000

ns

t

ACC

Address Access Time

65

70

ns

t

CO

Chip Enable (

CE1

) Access Time

65

70

ns

t

OE

Output Enable Access Time

25

25

ns

t

BA

Data Byte Control Access Time

25

25

ns

t

COE

Chip Enable Low to Output Active

10

10

ns

t

OEE

Output Enable Low to Output Active

0

0

ns

t

BE

Data Byte Control Low to Output Active

0

0

ns

t

OD

Chip Enable High to Output High-Z

20

20

ns

t

ODO

Output Enable High to Output High-Z

20

20

ns

t

BD

Data Byte Control High to Output High-Z

20

20

ns

t

OH

Output Data Hold Time

10

10

ns

t

PM

Page Mode Time

65

10000

70

10000

ns

t

PC

Page Mode Cycle Time

30

30

ns

t

AA

Page Mode Address Access Time

30

30

ns

t

AOH

Page Mode Output Data Hold Time

10

10

ns

t

WC

Write Cycle Time

65

10000

70

10000

ns

t

WP

Write Pulse Width

50

50

ns

t

CW

Chip Enable to End of Write

65

70

ns

t

BW

Data Byte Control to End of Write

60

60

ns

t

AW

Address Valid to End of Write

60

60

ns

t

AS

Address Set-up Time

0

0

ns

t

WR

Write Recovery Time

0

0

ns

t

ODW

WE Low to Output High-Z

20

20

ns

t

OEW

WE High to Output Active

0

0

ns

t

DS

Data Set-up Time

30

30

ns

t

DH

Data Hold Time

0

0

ns

t

CS

CE2 Set-up Time

0

0

ns

t

CH

CE2 Hold Time

300

300

µs

t

DPD

CE2 Pulse Width

10

10

ms

t

CHC

CE2 Hold from

CE1

0

0

ns

t

CHP

CE2 Hold from Power On

30

30

µs

AC TEST CONDITIONS

PARAMETER CONDITION

Output load

30 pF

+ 1 TTL Gate

Input pulse level

V

DD

- 0.2 V, 0.2 V

Timing measurements

V

DD

◊ 0.5

Reference level

V

DD

◊ 0.5

t

R

, t

F

5 ns