Loop Filter

Disable

Lock Detect

CS-300

Phase Freq

Detector

PECL

VCSO

VCXO Monitor

Frequency

Divider

Microprocessor

Frequency

Divider

Input

Frequency

Frequency

Select

Q

Q

Product Data Sheet

CS-300

Clock Smoother

Output frequencies up to 800 MHz

Ultra Low Jitter PECL Output

Locks to Input Frequency (i.e. 622.08 MHz)

3.3 Vdc or 5.0 Vdc supply

Lock / Loss of Signal Alarm

1" x 0.8" x 0.25", Surface Mount (FR4 base)

Clock Smoothing

SONET / SDH / ATM / DWDM / SFI-5

FEC (Forward Error Correction)

622.08 MHz to 622.08 MHz

Q

Q

4.75

3.135

Operating Temperature

Temp Range C = 0�C to +70�C

Temp Range F = -40�C to +85�C

Supply Voltage, C = 5 Vdc

D = 3.3 Vdc

Supply Current

5 Vdc

3.3 Vdc

Input Signal, F = Comp PECL

Output F = Comp PECL

Output Symmetry

Rise / Fall Time

(20% to 80% @ 622.08 MHz)

Jitter Generation, rms

(cycle to cycle method)

Input Frequency Tracking Capability

(Can translate a Stratum 1,2,3,3E,4

or SONET Min source)

See page 3 for outline Drawings and Dimensions

5.00

3.30

Vcc

Vcc

5.25

3.465

Vdc

Vdc

Icc

Icc

135

115

200

200

mA

mA

CLKIN

PECL

---

---

155.52 MHz

800 MHz

---

t

R

/t

F

400

ps

45

Sym

55

%

3

ps

APR

+/-40

ppm

Size

Vectron's CS-300 is a SAW based Clock Smoother and Frequency Translator which is used to

clean up noisy input frequencies. This series can accept any input frequency from 10 MHz to

700 MHz and then cleans up up the signal to provide an ultra low jitter output signal. The output

jitter of this unit is well below the requirements of OC-192.

The CS-300 also has the ability to translate either one or two different input frequencies between

10 MHz and 700 MHz to one common output frequency, such as input frequencies of 622.08 MHz

and 666.5143 MHz translated to an output frequency of 622.08 MHz. This unit is of particular

interest to those working with FEC applications or needing to switch between 10G and OC-192.

The "Input Frequency Tracking Capability" is the total amount of frequency deviation on the input

signal that the CS-300 is guaranteed to track. As an example, a typical input clock would be

622.08 MHz � 20 ppm. The CS-300 is guaranteed to track at least �40 ppm of error over

temperature/ aging/ power supply and is more than twice what most applications require.

250

V

OH

@ +25�C

V

OL

@ +25�C

V

OL

V

cc

-1.95

V

cc

-1.63

V

V

OH

V

cc

-0.98

V

cc

-0.75

V

Jitter Generation, rms

(12kHz to 20MHz)

0.23

ps

49/51

PECL

1.0

Jitter Transfer,

GR-253-CORE section 5.6.2.1.2

0.1

dB

10 MHz

700 MHz

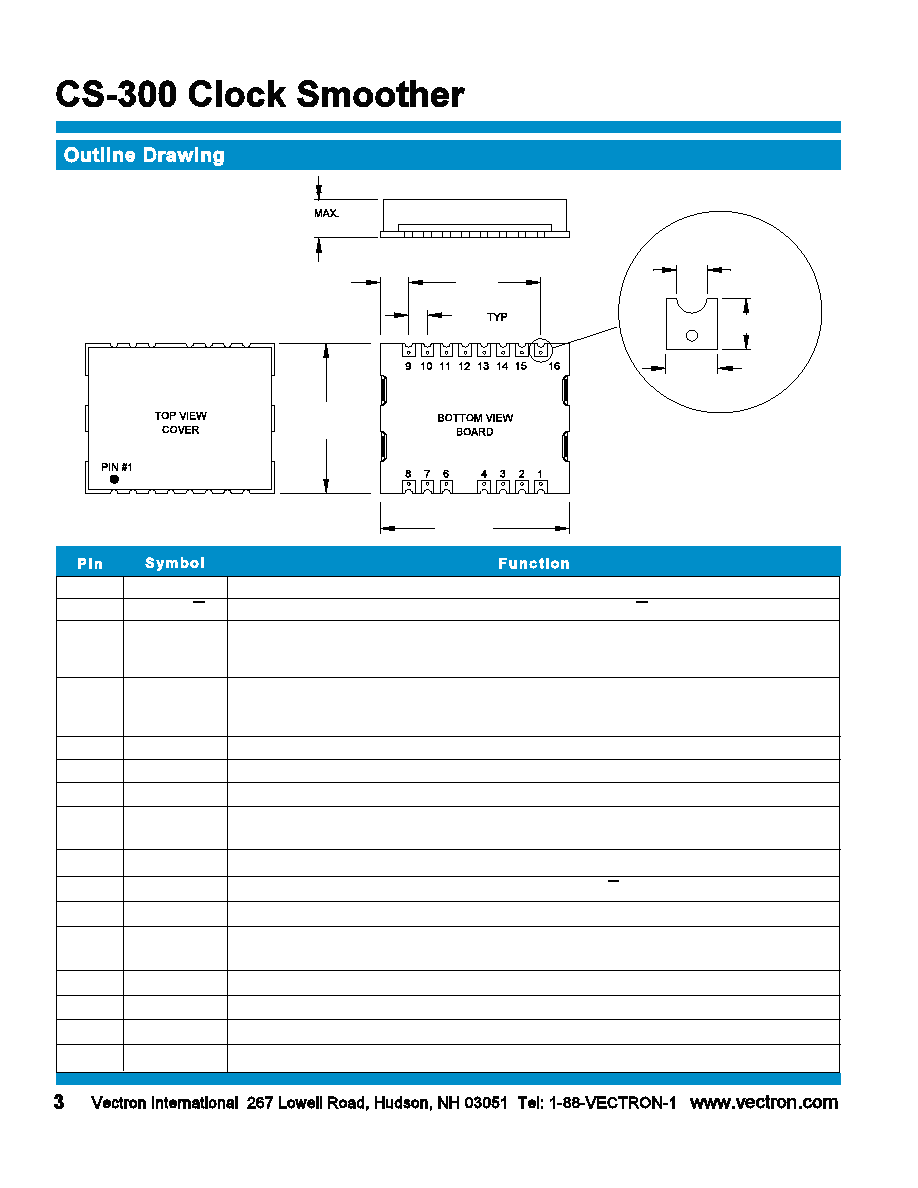

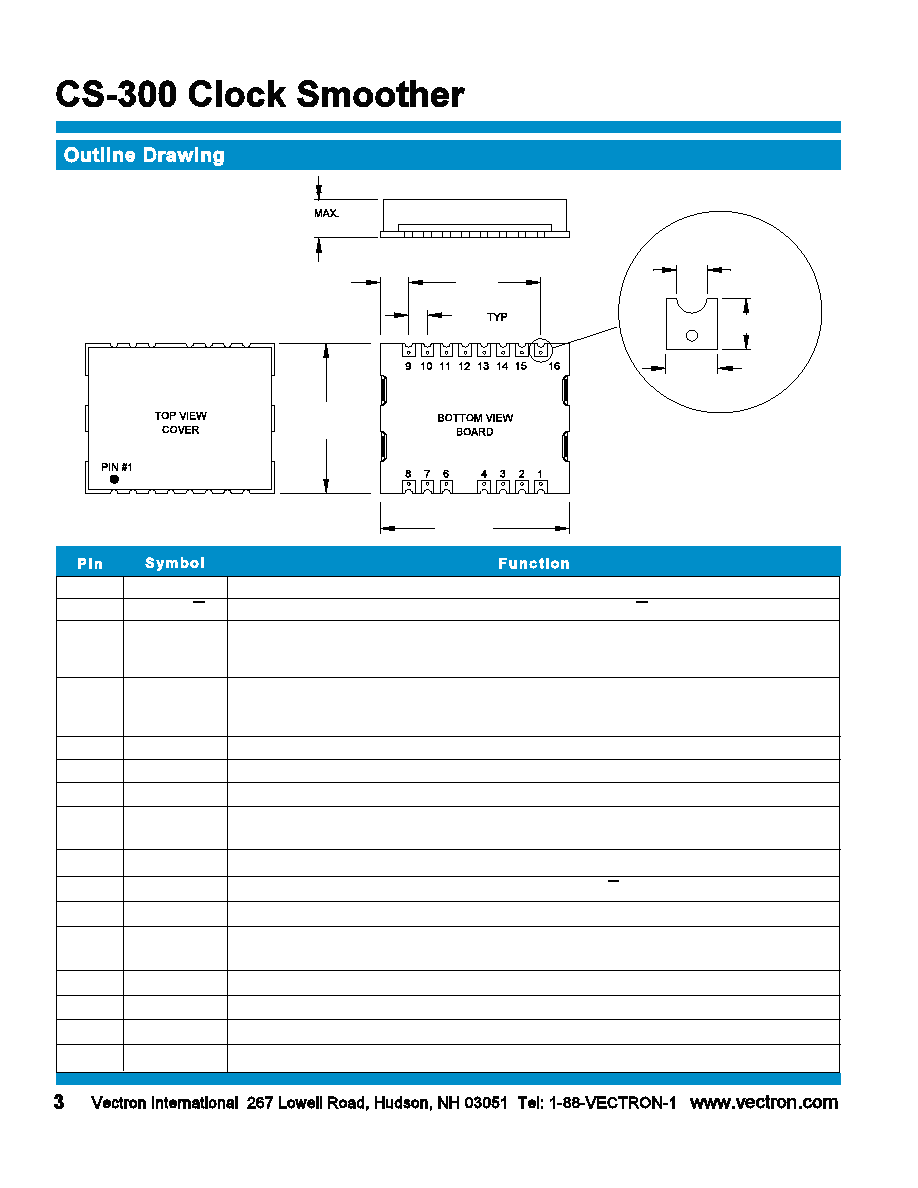

CLKIN Q

Input Frequency (Q)

1

CLKIN Q

Complementary Input Frequency (Q)

2

LD

(Output)

Lock Detect

Logic "1" indicates a locked condition.

Logic "0" indicates an out of lock condition.

3

Monitor

(Output)

PLL/ VCXO control voltage

Under locked conditions, should be >0.3V and <3.0V for the 3.3 volt option or >0.5V and <4.5V for

the 5 volt option. Input frequency may be out of range if voltage exceeds these limits.

4

----

Missing

5

NC

No Connection

6

GND

Ground

7

Disable

(Input)

Floating = Output enabled

Logic "0" = Output disabled

8

OUT

Output (Q)

9

COUT

Complementary Output (Q)

10

NC

No Connection

11

Freq. Select

0 = Primiary Frequncey

1 = Secondary Frequency (Do not Exceed Vdd)

12

NC

No Connection

13

NC

No Connection

14

GND

Ground

15

V

cc

5 Vdc or 3.3 Vdc

16

6.35

(0.25)

3.81

(0.15)

17.78

(0.70)

20.32

(0.80)

2.54

(0.10)

25.4

(1.00)

1.73

(0.068)

1.73

(0.068)

1.01

(0.040)

mm

(in)

pre-heating

60 to 90 sec.

@ 140�C to 160�C

reflow

40 to 60 sec.

@ >183�C

NOTE: The CS-300 should not be subjected to a wash process that will immerse it in solvents. NO CLEAN is the recommended

procedure.

The CS-300 has been designed for pick and place reflow soldering. The suggested reflow profile is shown above.

The CS-300 may be reflowed once, and should not be reflowed in the inverted position.

8.89

(0.35)

17.78

(0.70)

19.05

(0.75)

2.54

(0.10)

1.91

(0.075)

3.04

(0.12)

9.53

(0.375)

mm

(in)

Temperature ( �C)

The Standard ship method for volume production of the CS-300 series is in a matrix tray. These

trays are 100% recyclable. The trays also offer the added feature that they can be continuously

feed into a pick-n-place machine eliminating the down time required with tape-n-reel.

Although protection circuitry has been

designed into this device, proper precautions

should be taken to avoid exposure to

electrostatic discharge (ESD) during handling

and mounting. VI employs a human-body

model (HBM) and a charged-device model

(CDM) for ESD-susceptibility testing and

protection design evaluation. ESD voltage

thresholds are dependent on the circuit

parameters used to define the mode.

Although no industry-wide standard has been

adopted for the CDM, a standard HBM

(resistance = 1500 ohms, capacitance =

100pf) is widely used and therefore can be

used for comparison purposes. The HBM

ESD threshold presented here was obtained

by using these circuit parameters.

ESD Threshold Voltage

Model

Threshold

Unit

Human-Body (HBM)

Charged-Device

500

500

V min

V min

0.85

0.125

0.16

0.125

VI - Logo

This Cell only

4.00

0.125

12 15/16

0.235

0.235

3 x 12 Array / 36 units per tray

1.05

0.255 deep

Pin 1

This Corner

CS-300-DFC-P2XXP2

622.08 MHz in

622.08 MHz out

CS-300-DFC-P2XXP2

622.08 MHz in

622.08 MHz out

CS-300-DFC-P2XXP2

622.08 MHz in

622.08 MHz out

CS-300-DFC-P2XXP2

622.08 MHz in

622.08 MHz out